High Speed Cable Testing Twinax cable FPGA based

High Speed Cable Testing • Twinax cable • FPGA based test system – BERT – Eye diagrams • Upgrade to system • Spice simulations of eye diagrams • Outlook SLHC ID electronics Novermber '10 Tony Weidberg 1

Twinax Cable 30 AWG CCA Sample provided by Vitaliy Fadeyev (UCSC) Uses suitable radiation tolerant plastics for insulation and jacket. polyethylene and polyurethane. 2

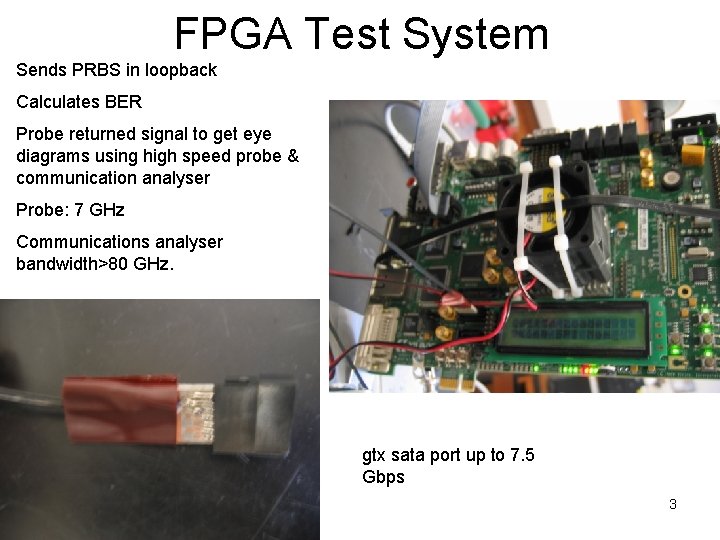

FPGA Test System Sends PRBS in loopback Calculates BER Probe returned signal to get eye diagrams using high speed probe & communication analyser Probe: 7 GHz Communications analyser bandwidth>80 GHz. gtx sata port up to 7. 5 Gbps 3

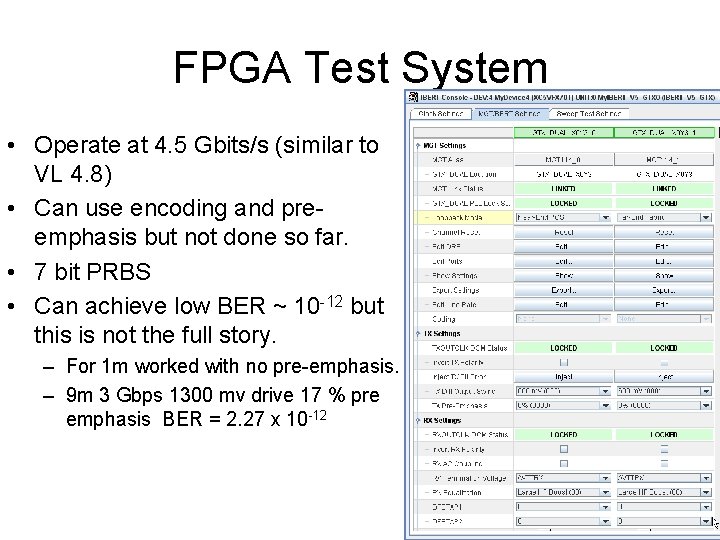

FPGA Test System • Operate at 4. 5 Gbits/s (similar to VL 4. 8) • Can use encoding and preemphasis but not done so far. • 7 bit PRBS • Can achieve low BER ~ 10 -12 but this is not the full story. – For 1 m worked with no pre-emphasis. – 9 m 3 Gbps 1300 mv drive 17 % pre emphasis BER = 2. 27 x 10 -12 4

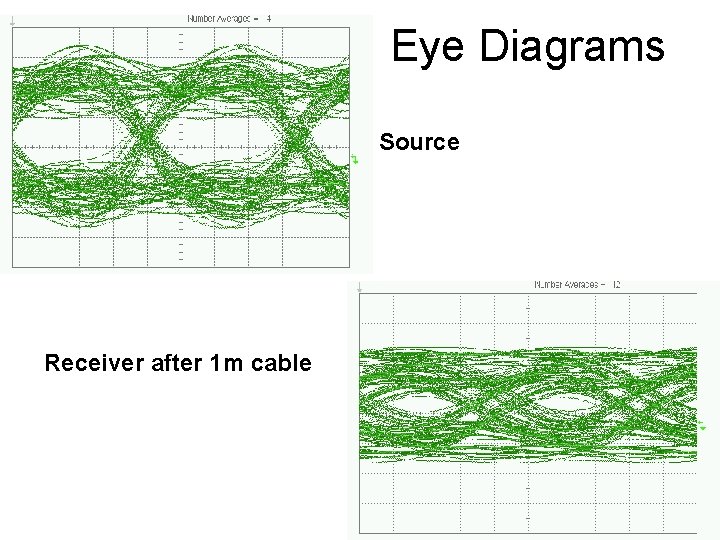

Eye Diagrams Source Receiver after 1 m cable 5

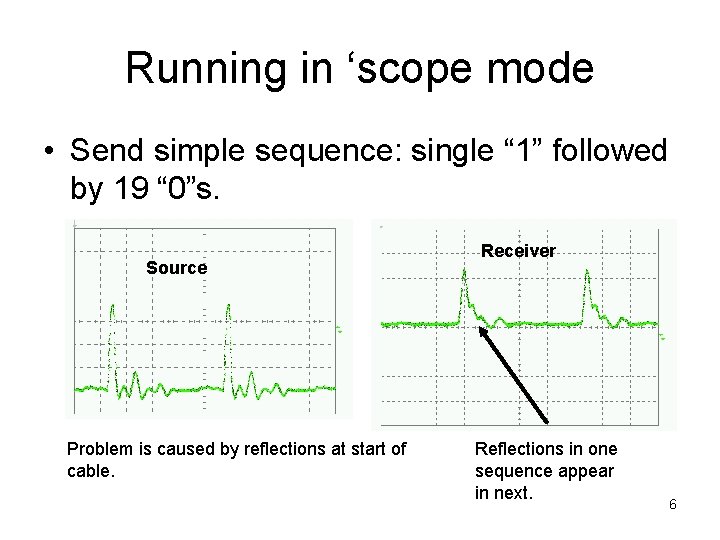

Running in ‘scope mode • Send simple sequence: single “ 1” followed by 19 “ 0”s. Source Problem is caused by reflections at start of cable. Receiver Reflections in one sequence appear in next. 6

Solutions • Fast buffer chip at edge of PCB • Two options being considered 7

Solution-1 • A CML Driver board is being developed which will plug into the sata connector and enable a clean reflection free signal to be driven. – The cable will be terminated at 100 W for eye diagram tests. – Once acceptable eye diagrams have been achieved the cable will be looped back to the FPGA for BER testing and eye diagrams for the end of the cable. – Start with 1 m cable and then try longer lengths. – Digital input. Reflection ignored 8

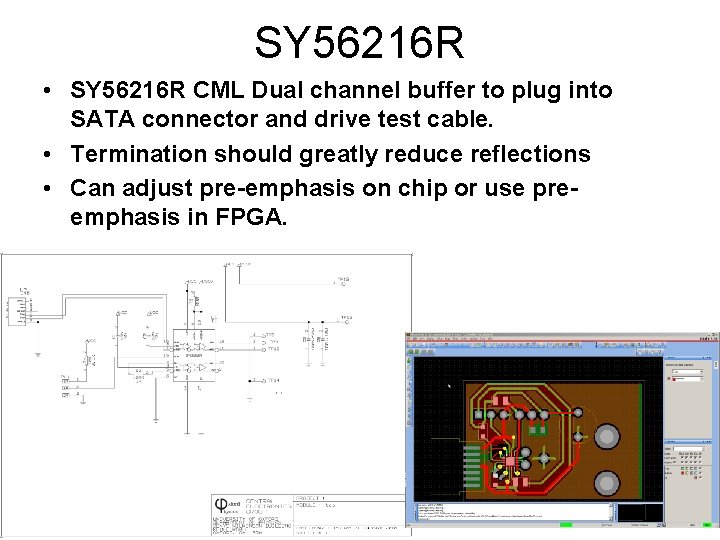

SY 56216 R • SY 56216 R CML Dual channel buffer to plug into SATA connector and drive test cable. • Termination should greatly reduce reflections • Can adjust pre-emphasis on chip or use preemphasis in FPGA. 9

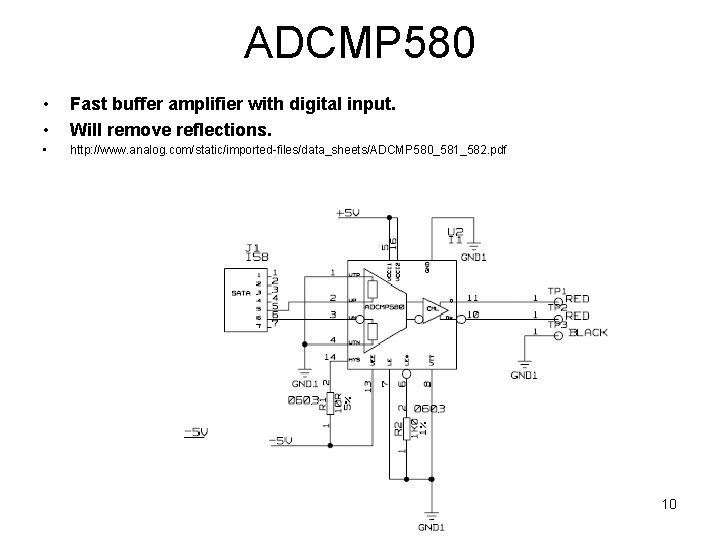

ADCMP 580 • • Fast buffer amplifier with digital input. Will remove reflections. • http: //www. analog. com/static/imported-files/data_sheets/ADCMP 580_581_582. pdf 10

Next Steps – The cable will be terminated at 100 W for eye diagram tests. – Once acceptable eye diagrams have been achieved the cable will be looped back to the FPGA for BER testing and eye diagrams for the end of the cable. – Start with 1 m cable and then try longer lengths. 11

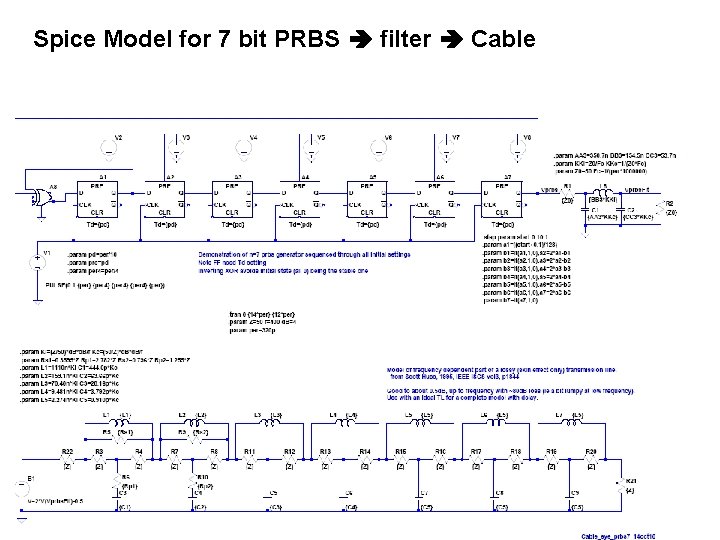

Spice Simulations • Simple cable model – Assumes skin loss dominant (ie dielectric losses negligible) – Model based on another cable with values scaled to our twin-ax cable. – 1 db/m attenuation – First look, so plots shown are indicative only. 12

Spice Model for 7 bit PRBS filter Cable 13

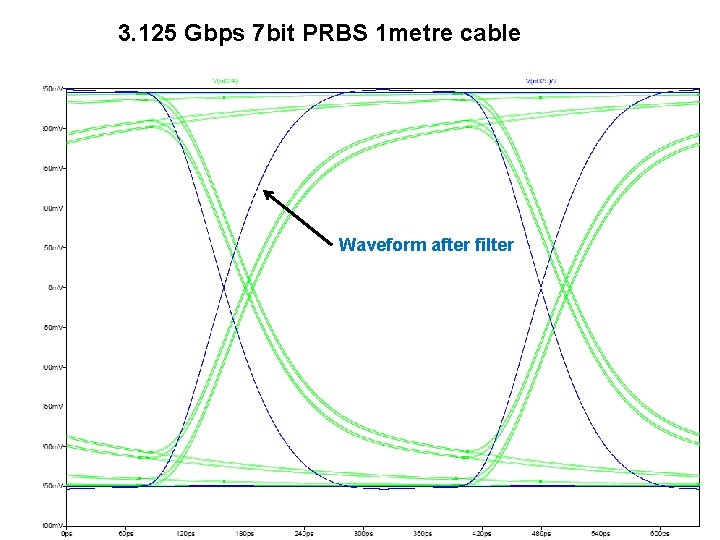

3. 125 Gbps 7 bit PRBS 1 metre cable Waveform after filter 14

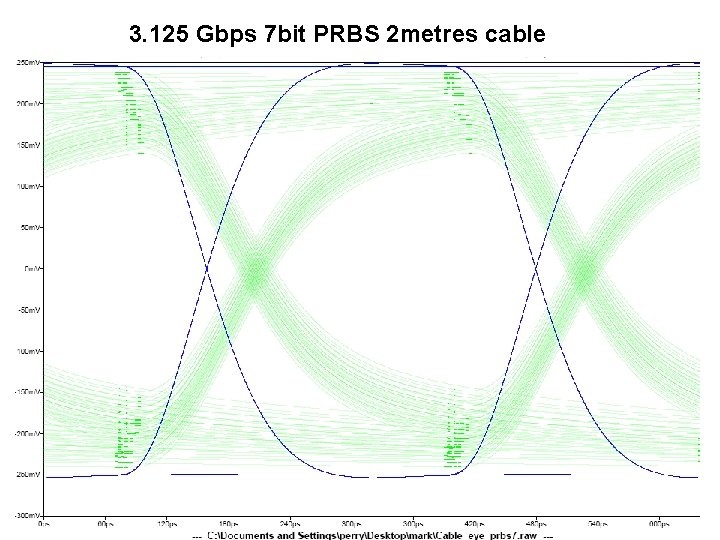

3. 125 Gbps 7 bit PRBS 2 metres cable 15

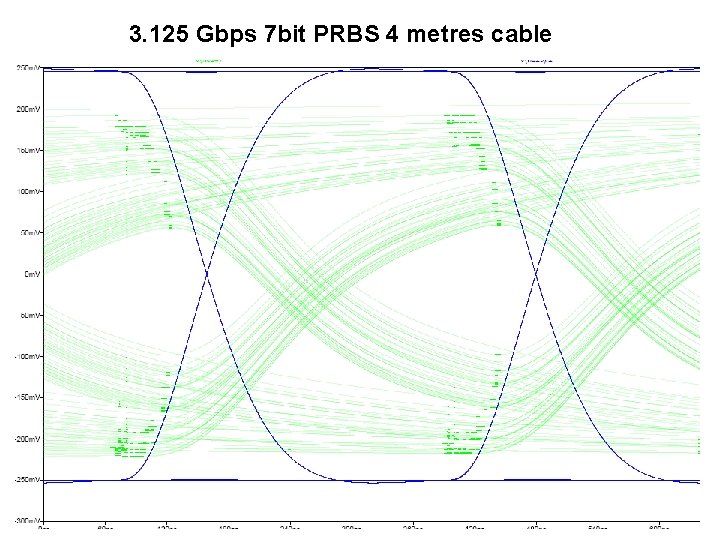

3. 125 Gbps 7 bit PRBS 4 metres cable 16

Outlook • Started to look at eye diagrams and BER for high speed cable testing. • Need to improve test system to eliminate reflections. • Optimise eye diagrams with preempahsis. • Should be able to understand eye diagrams with spice simulations. 17

- Slides: 17