High Performance Computer Architecture Lesson 60 Introduction to

- Slides: 14

High Performance Computer Architecture Lesson 60: Introduction to FPGAs http: //www. dii. unisi. it/~giorgi/teaching/hpca 2 All copyrighted figures are copyright of respective authors. Figures may be reproduced only for classroom or personal educational use only when the above copyright line is included. They may not be otherwise reproduced, distributed, or incorporated into other works without the prior written consent of the publisher. Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 1 di

FPGA: what is it? • FPGA stands for “Field Programmable Gate Array” • Yet Another Chip ! Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 2 di Courtesy XILINX

FPGA: what’s new • Temporal Computing (all chips we have seen so far) • Software controls how to process data in a FIXED architecture • Spatial Computing • Software defines the ARCHITECTURE to process data Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 3 di

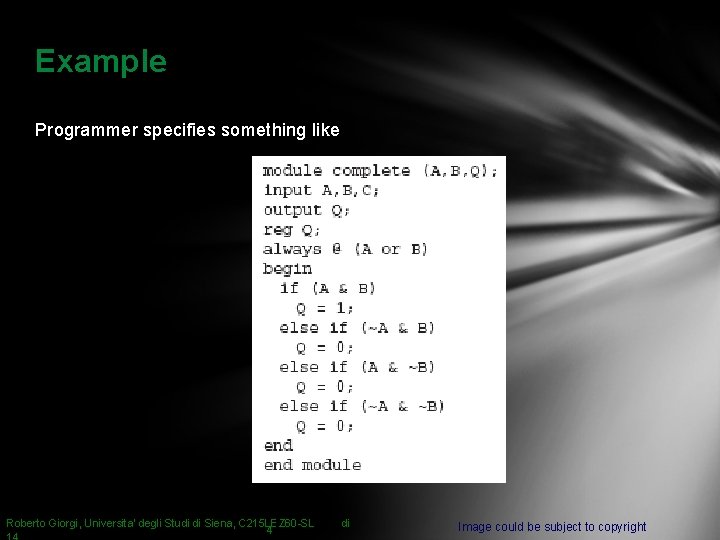

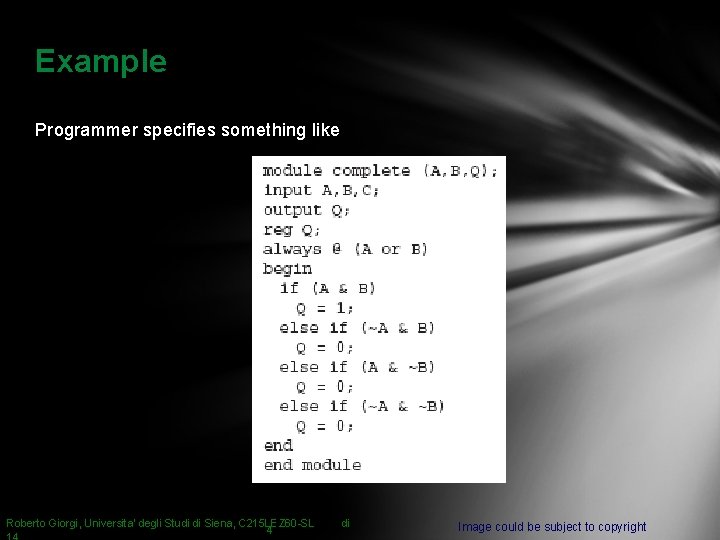

Example Programmer specifies something like Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 4 di Image could be subject to copyright

FPGA Synthesis Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 5 di Image could be subject to copyright

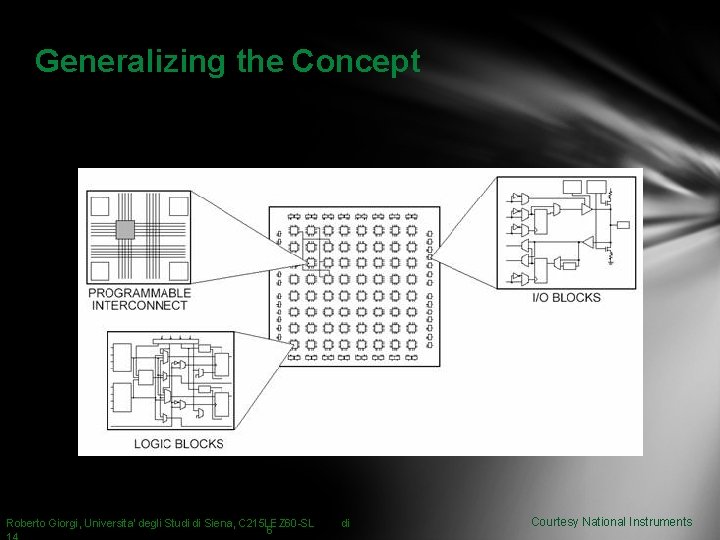

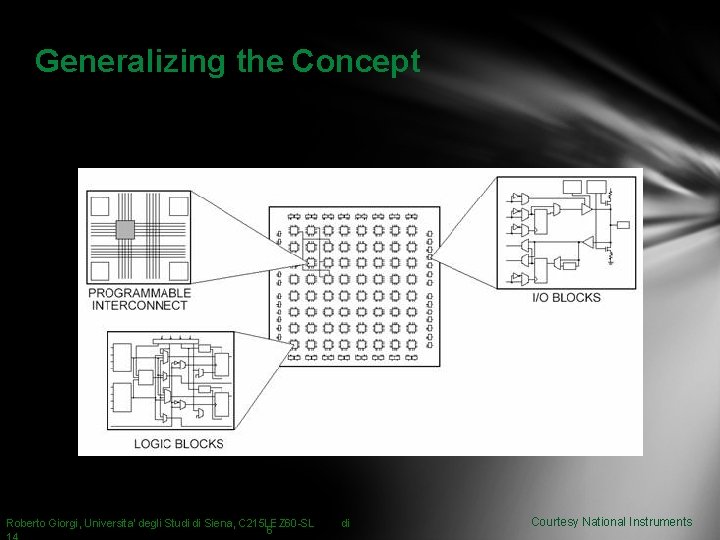

Generalizing the Concept Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 6 di Courtesy National Instruments

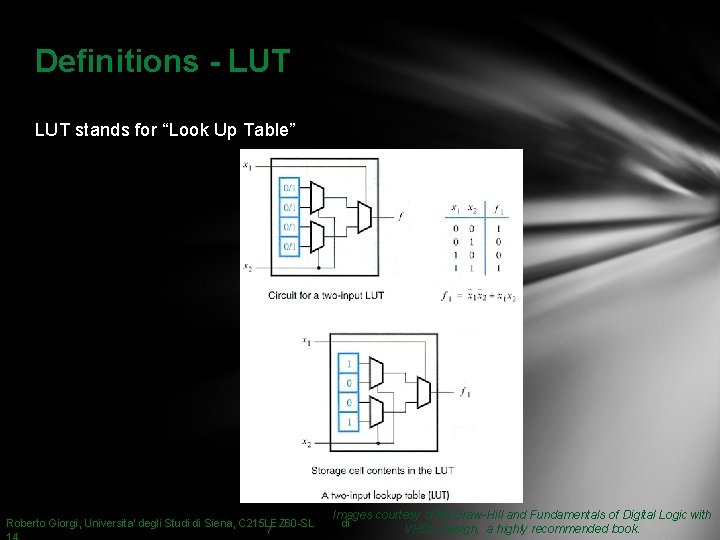

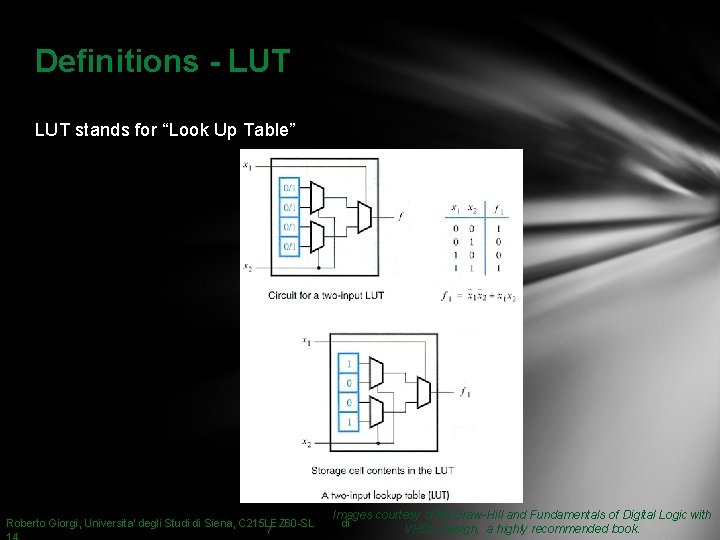

Definitions - LUT stands for “Look Up Table” Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 7 Images courtesy of Mc. Graw-Hill and Fundamentals of Digital Logic with di VHDL Design, a highly recommended book.

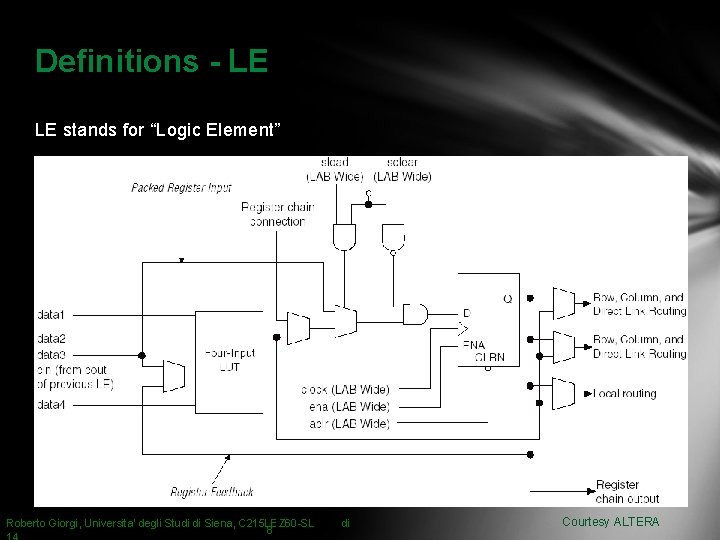

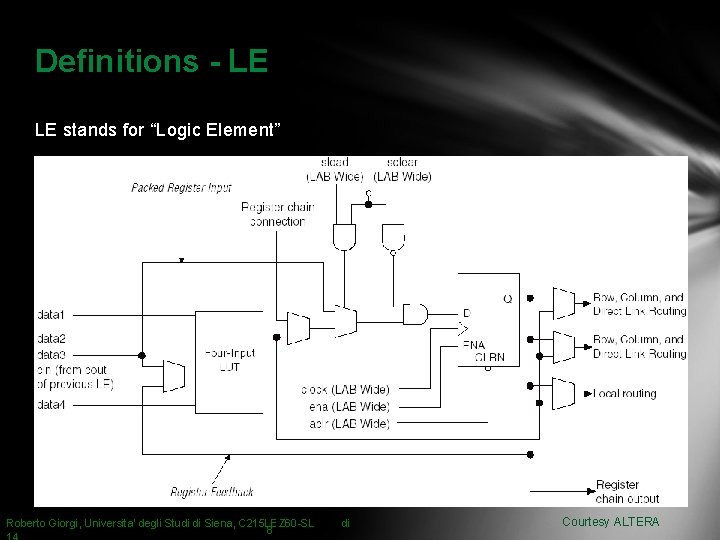

Definitions - LE LE stands for “Logic Element” Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 8 di Courtesy ALTERA

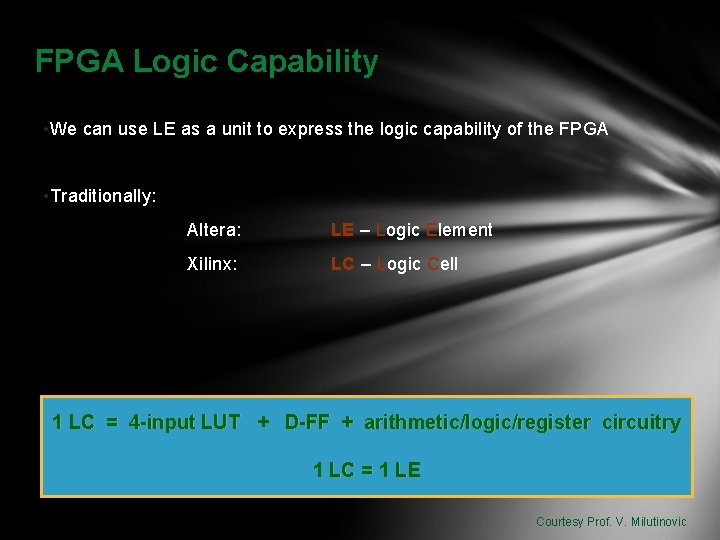

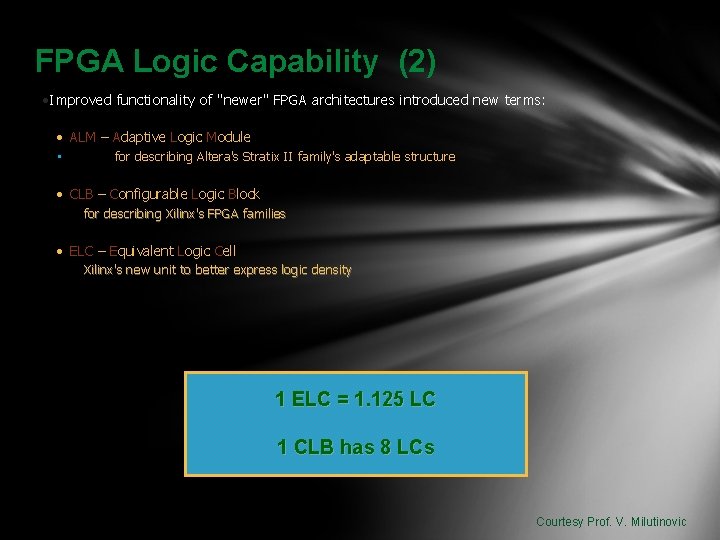

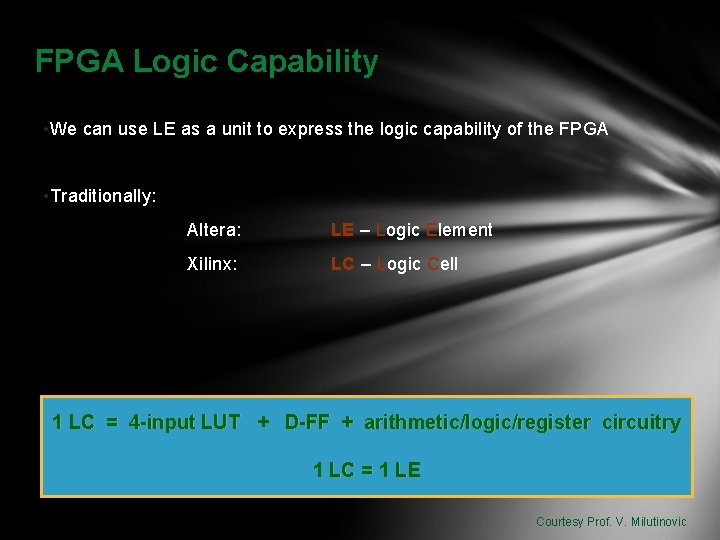

FPGA Logic Capability • We can use LE as a unit to express the logic capability of the FPGA • Traditionally: Altera: LE – Logic Element Xilinx: LC – Logic Cell 1 LC = 4 -input LUT + D-FF + arithmetic/logic/register circuitry 1 LC = 1 LE Courtesy Prof. V. Milutinovic

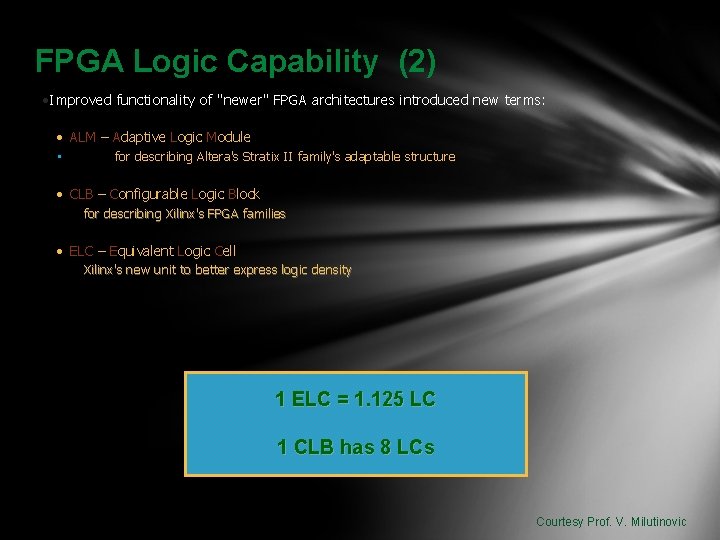

FPGA Logic Capability (2) • Improved functionality of "newer" FPGA architectures introduced new terms: • ALM – Adaptive Logic Module • for describing Altera's Stratix II family's adaptable structure • CLB – Configurable Logic Block for describing Xilinx's FPGA families • ELC – Equivalent Logic Cell Xilinx's new unit to better express logic density 1 ELC = 1. 125 LC 1 CLB has 8 LCs Courtesy Prof. V. Milutinovic

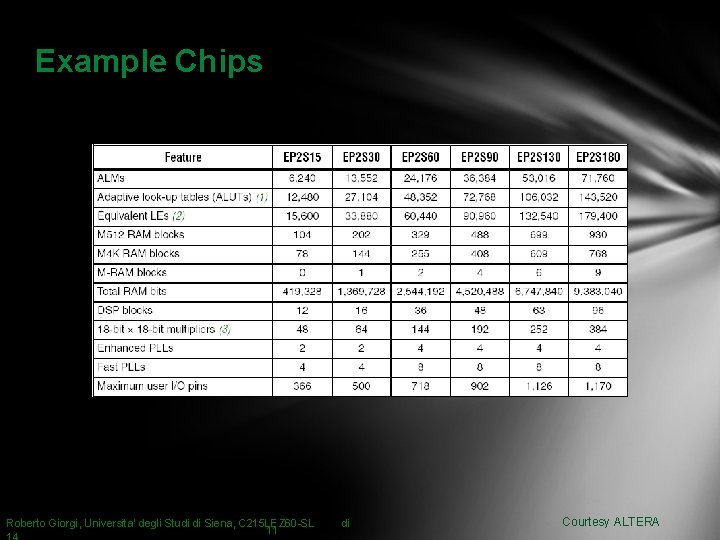

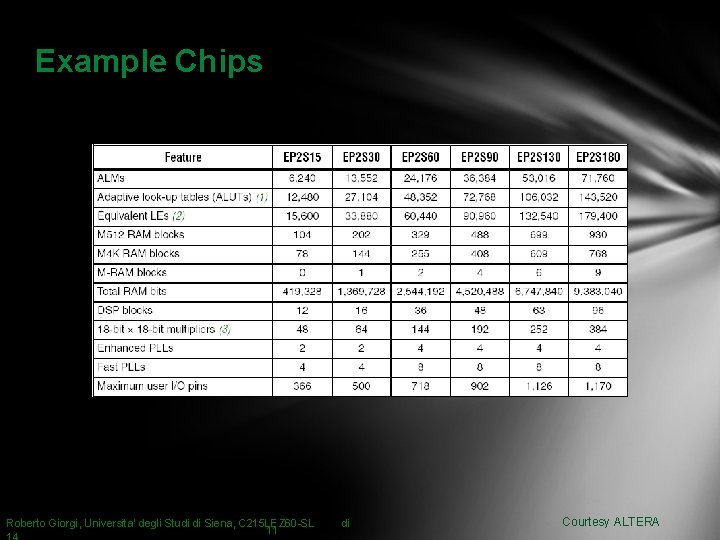

Example Chips Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 11 di Courtesy ALTERA

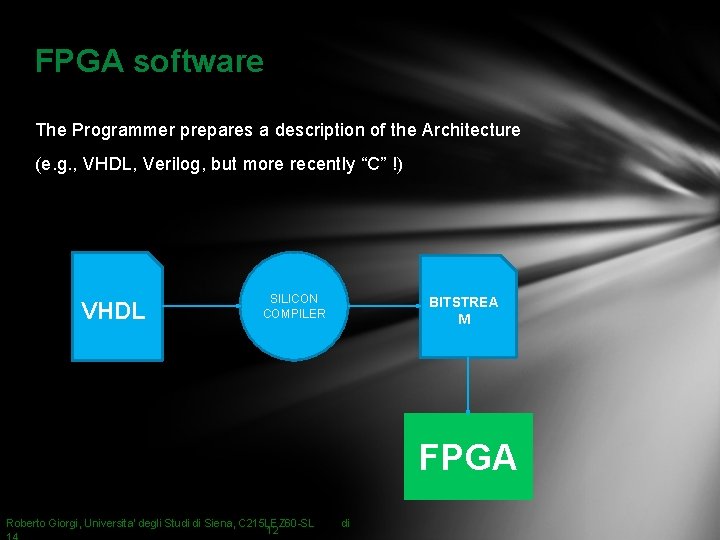

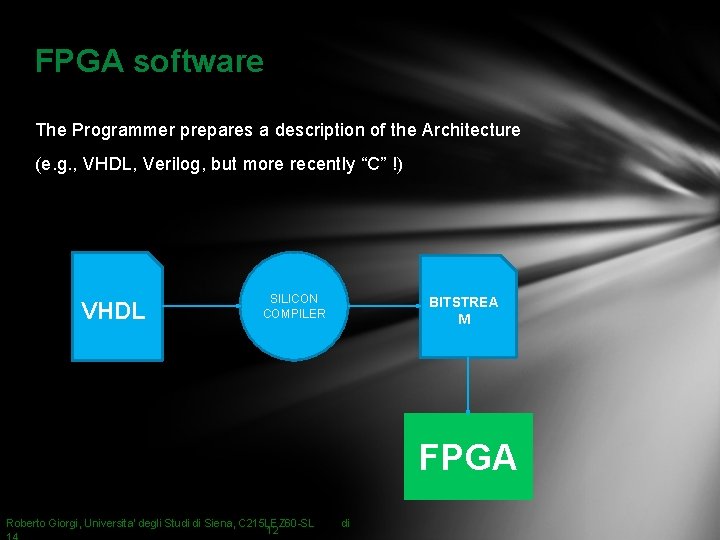

FPGA software The Programmer prepares a description of the Architecture (e. g. , VHDL, Verilog, but more recently “C” !) VHDL SILICON COMPILER BITSTREA M FPGA Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 12 di

FPGA at work INPUT DATA FPGA Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 13 di OUTPUT DATA

Further References Google “Prof VM” Click “teaching”, then VLSI, then PLD… Roberto Giorgi, Universita' degli Studi di Siena, C 215 LEZ 60 -SL 14 di