Hierarchical Floorplanning of Chip Multiprocessors using Subgraph Discovery

Hierarchical Floorplanning of Chip Multiprocessors using Subgraph Discovery Javier de San Pedro Jordi Cortadella Antoni Roca Universitat Politècnica de Catalunya (Barcelona) Graph-TA 2014 1

Outline • Introduction – Chip multiprocessors and floorplanning • Hierarchical floorplanning methodology • Results and conclusions Graph-TA 2014 2

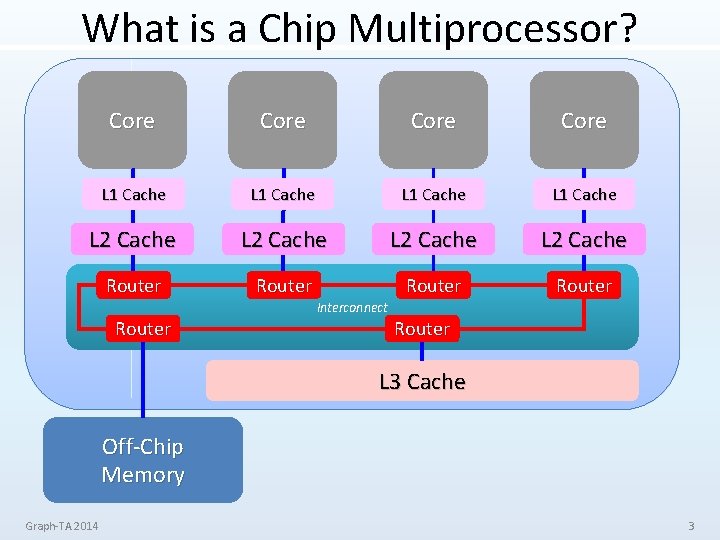

What is a Chip Multiprocessor? Core L 1 Cache L 2 Cache Router Interconnect Router L 3 Cache Off-Chip Memory Graph-TA 2014 3

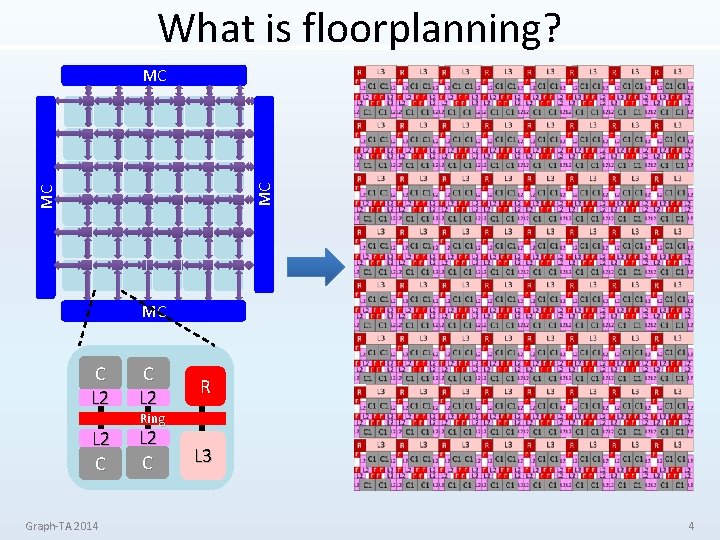

What is floorplanning? MC MC C L 2 R L 2 C L 3 Graph-TA 2014 Ring 4

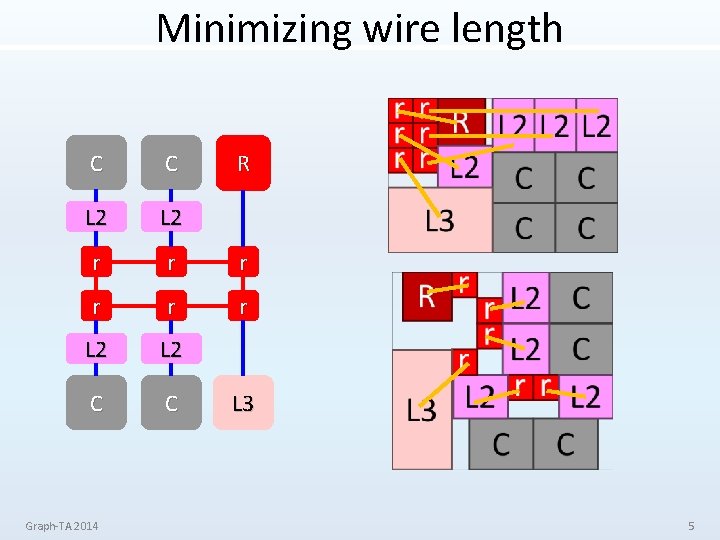

Minimizing wire length C C L 2 r r r L 2 C C Graph-TA 2014 R L 3 5

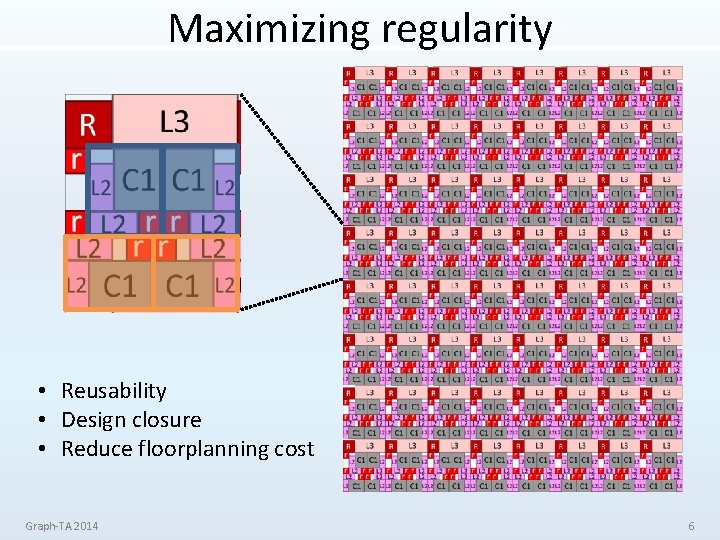

Maximizing regularity • Reusability • Design closure • Reduce floorplanning cost Graph-TA 2014 6

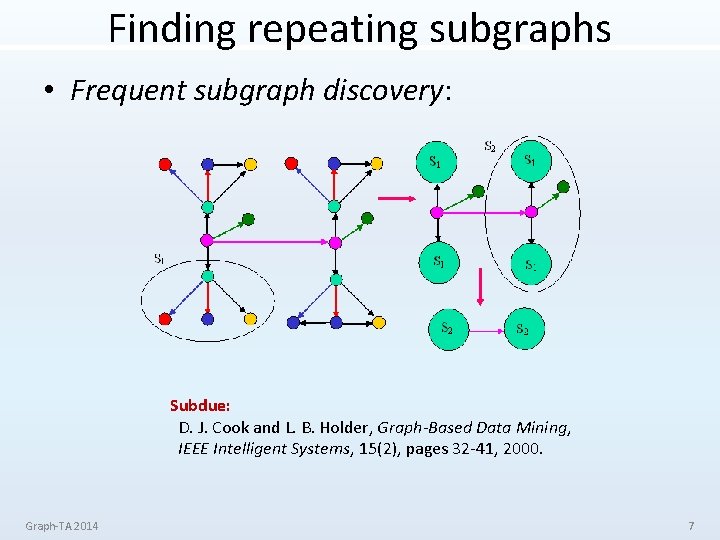

Finding repeating subgraphs • Frequent subgraph discovery: Subdue: D. J. Cook and L. B. Holder, Graph-Based Data Mining, IEEE Intelligent Systems, 15(2), pages 32 -41, 2000. Graph-TA 2014 7

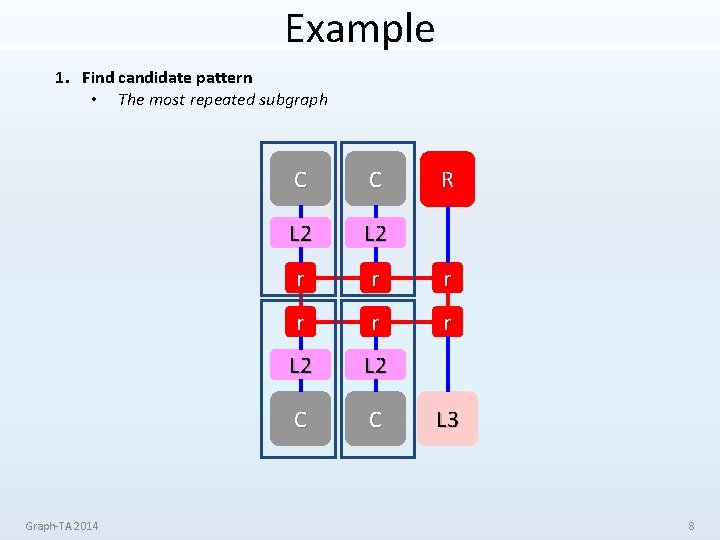

Example 1. Find candidate pattern • The most repeated subgraph Graph-TA 2014 C C L 2 r r r L 2 C C R L 3 8

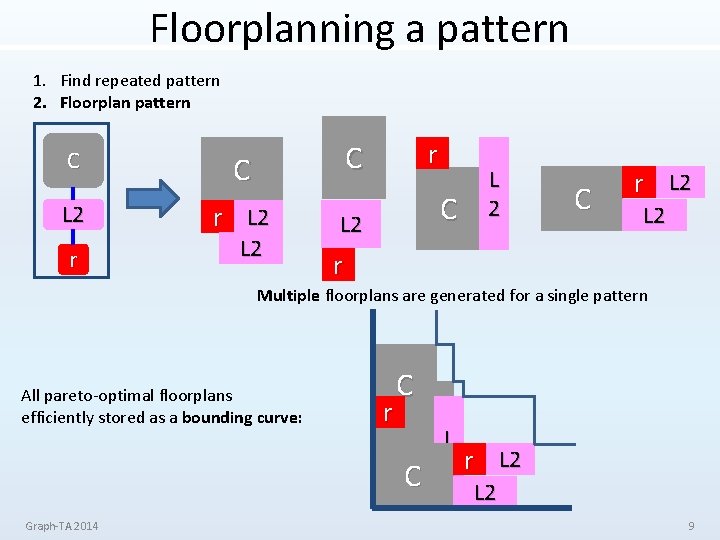

Floorplanning a pattern 1. Find repeated pattern 2. Floorplan pattern C L 2 r C C r L 2 L 2 r C L 2 C r L 2 r Multiple floorplans are generated for a single pattern All pareto-optimal floorplans efficiently stored as a bounding curve: Graph-TA 2014 C r. C L L 2 r C L 2 2 r L 2 C r L 2 9

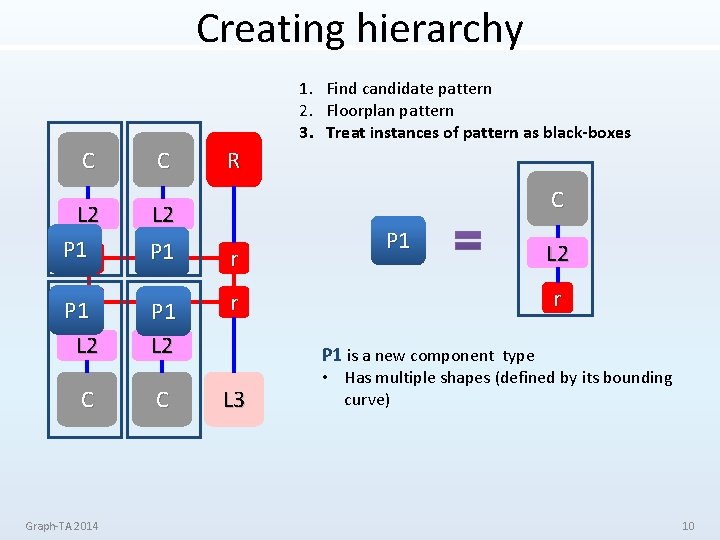

Creating hierarchy 1. Find candidate pattern 2. Floorplan pattern 3. Treat instances of pattern as black-boxes C C R C L 2 P 1 r P 1 r r P 1 r L 2 r P 1 L 2 r C Graph-TA 2014 L 2 C P 1 L 2 r P 1 is a new component type L 3 • Has multiple shapes (defined by its bounding curve) 10

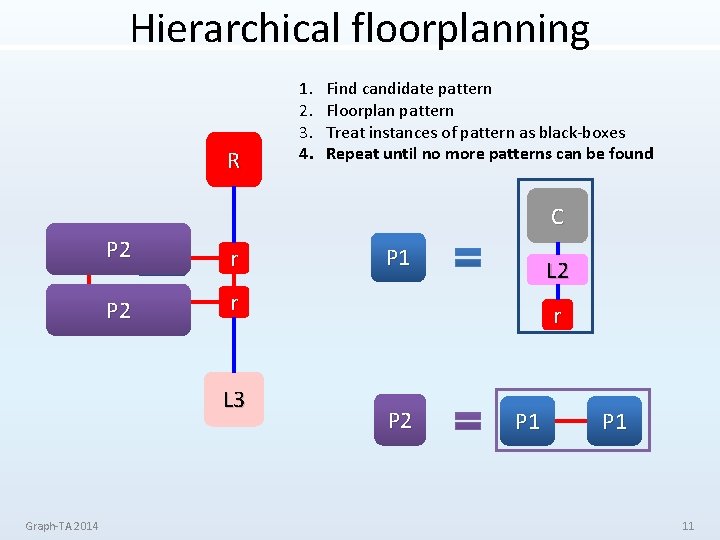

Hierarchical floorplanning R 1. 2. 3. 4. Find candidate pattern Floorplan pattern Treat instances of pattern as black-boxes Repeat until no more patterns can be found C P 1 P 2 P 1 r L 3 Graph-TA 2014 P 1 L 2 r P 2 P 1 11

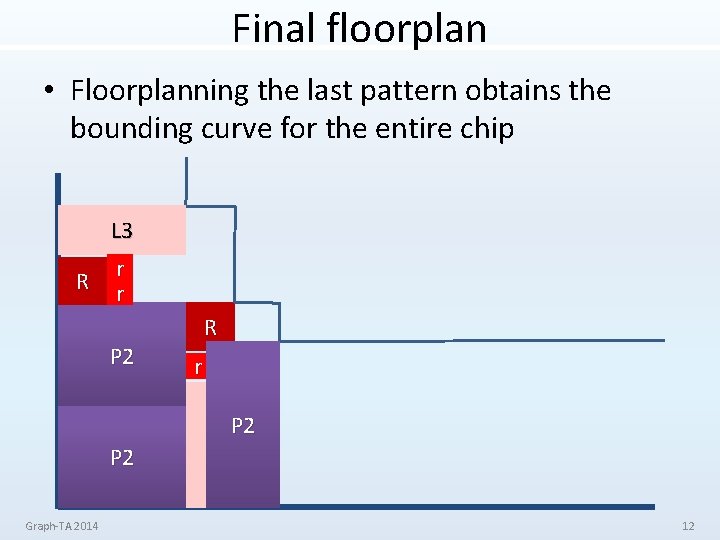

Final floorplan • Floorplanning the last pattern obtains the bounding curve for the entire chip L 3 R r r R P 2 Graph-TA 2014 P 2 R r r P 2 L 3 P 2 12

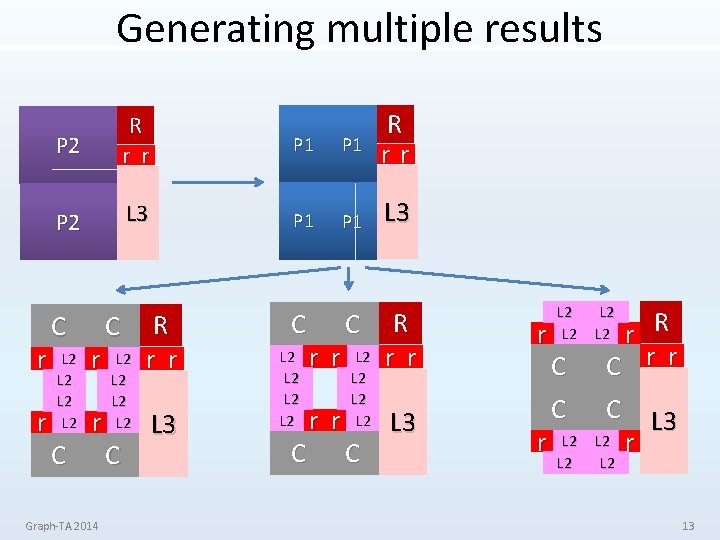

Generating multiple results r r P 2 R r r P 1 R rr P 2 L 3 P 1 L 3 C L 2 L 2 C r r Graph-TA 2014 C L 2 L 2 C R r r L 3 C L 2 L 2 C r r C L 2 L 2 C R r r L 3 r r L 2 C C L 2 L 2 r R C r r C L 2 r L 3 13

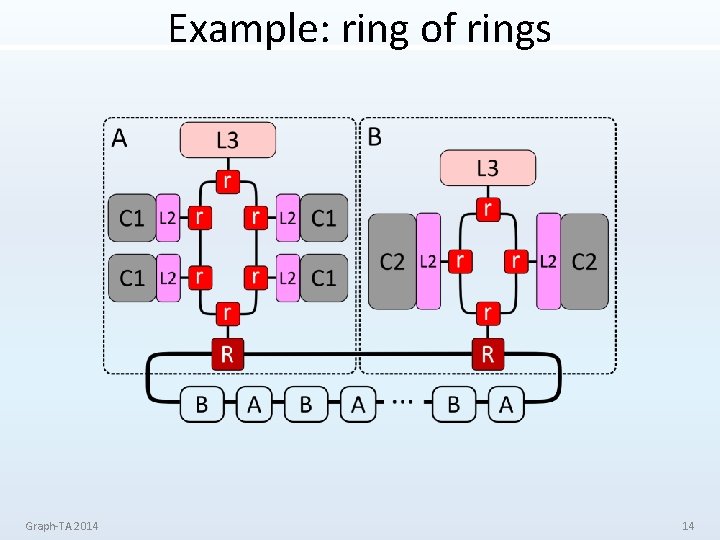

Example: ring of rings Graph-TA 2014 14

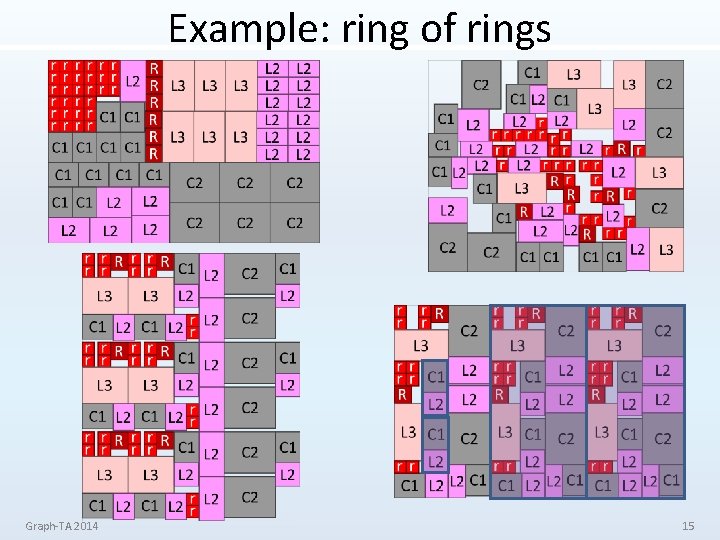

Example: ring of rings Graph-TA 2014 15

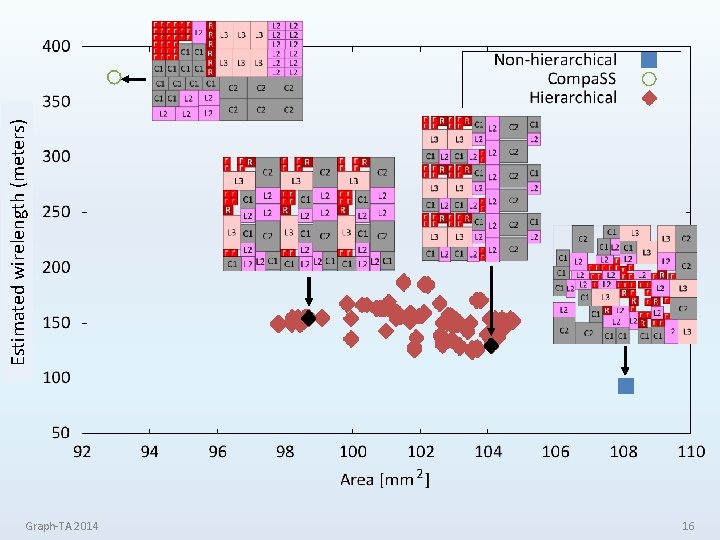

Graph-TA 2014 16 Estimated wirelength (meters)

Conclusions • We can extract regularity from a netlist and build regular floorplans – Competitive area, wire length results – Reduce design time • Future: application to other domains – High-level synthesis, logic synthesis, … Graph-TA 2014 17

- Slides: 17