HCC Analog Monitor HCC Design Review April 24

- Slides: 18

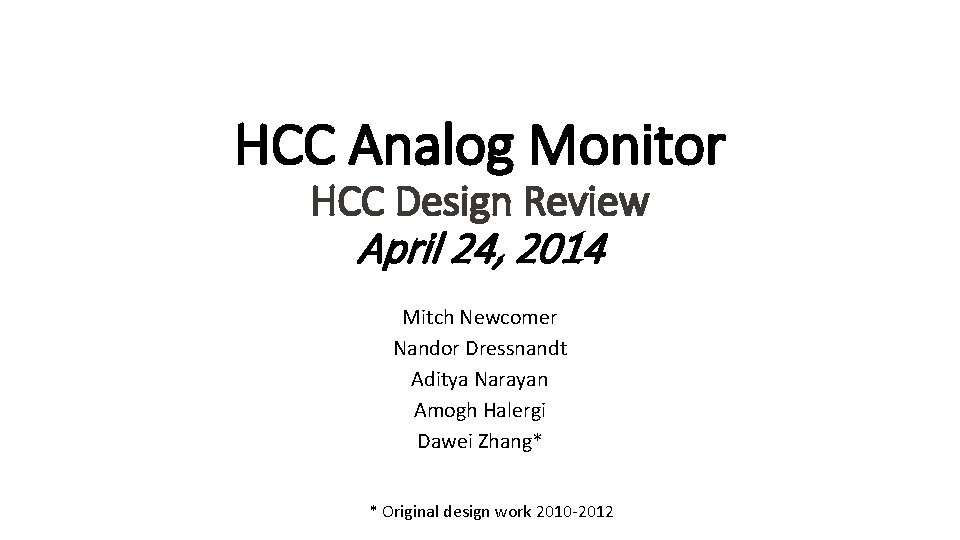

HCC Analog Monitor HCC Design Review April 24, 2014 Mitch Newcomer Nandor Dressnandt Aditya Narayan Amogh Halergi Dawei Zhang* * Original design work 2010 -2012

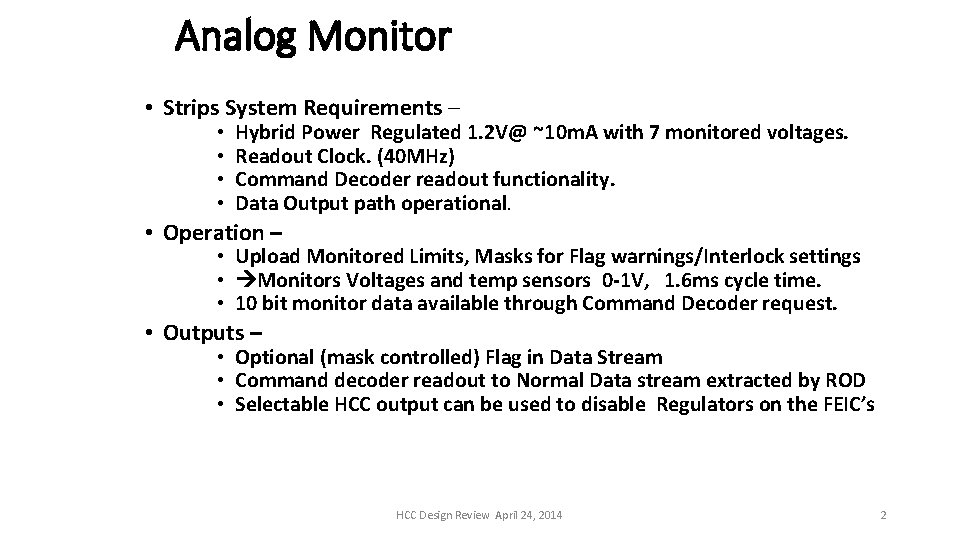

Analog Monitor • Strips System Requirements – • • Hybrid Power Regulated 1. 2 V@ ~10 m. A with 7 monitored voltages. Readout Clock. (40 MHz) Command Decoder readout functionality. Data Output path operational. • Operation – • Upload Monitored Limits, Masks for Flag warnings/Interlock settings • Monitors Voltages and temp sensors 0 -1 V, 1. 6 ms cycle time. • 10 bit monitor data available through Command Decoder request. • Outputs – • Optional (mask controlled) Flag in Data Stream • Command decoder readout to Normal Data stream extracted by ROD • Selectable HCC output can be used to disable Regulators on the FEIC’s HCC Design Review April 24, 2014 2

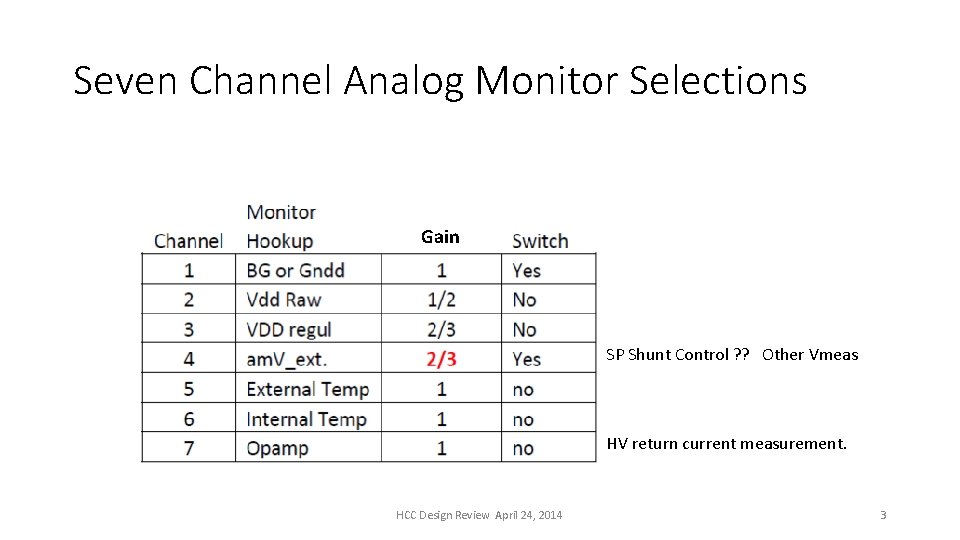

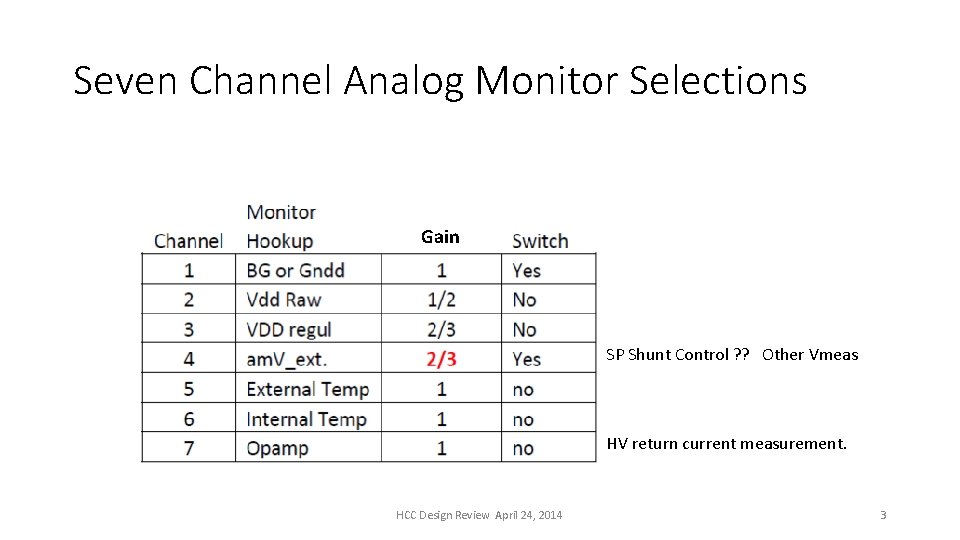

Seven Channel Analog Monitor Selections Gain SP Shunt Control ? ? Other Vmeas HV return current measurement. HCC Design Review April 24, 2014 3

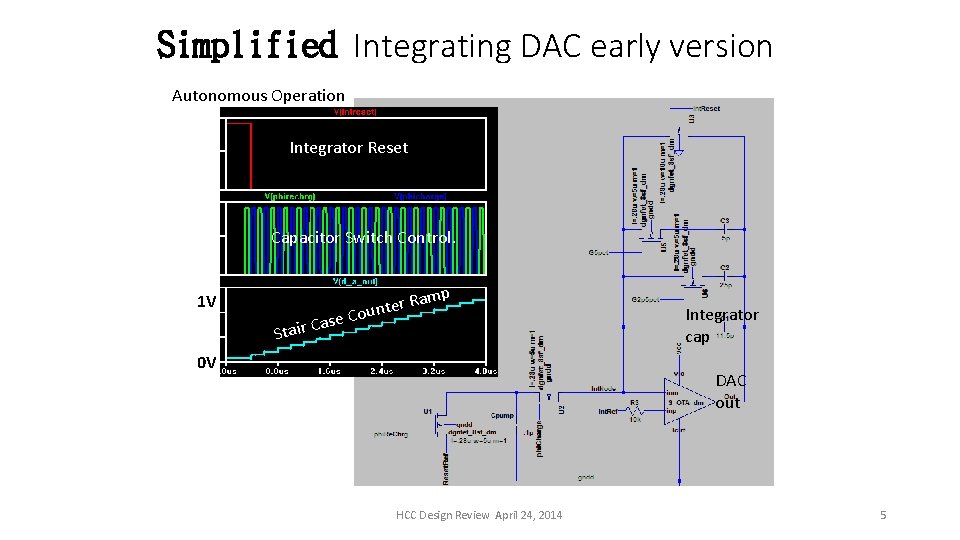

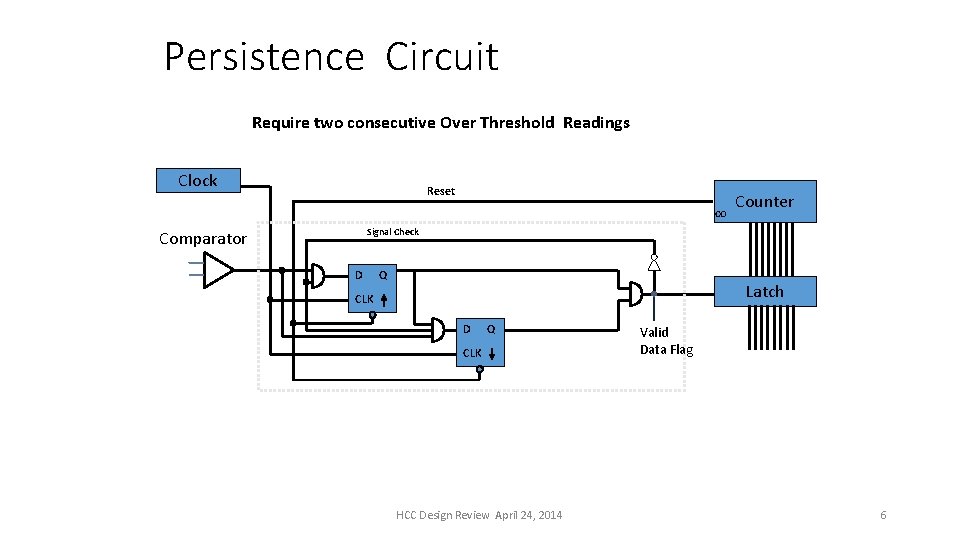

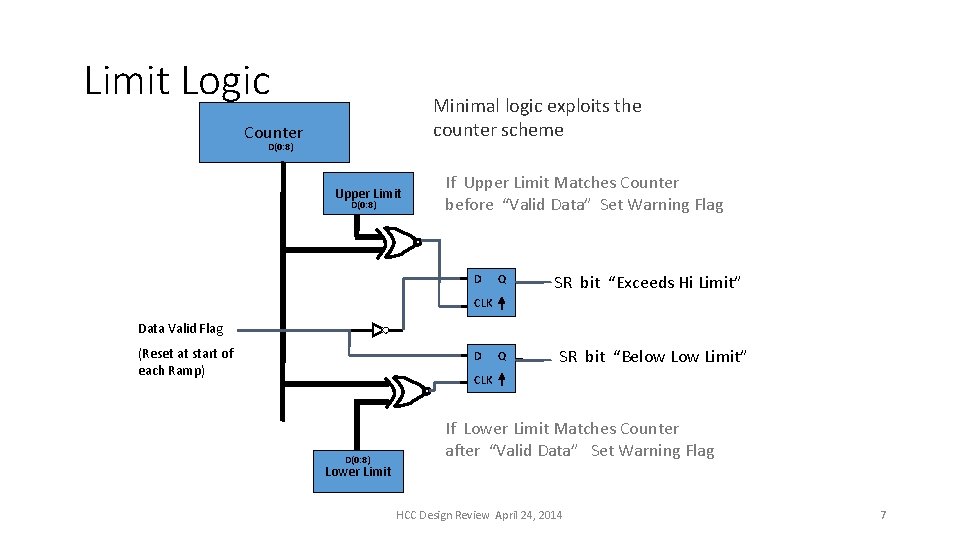

Functional Blocks in Words • State machine counter scaled 40 MHz clock gives 800 ns integrator steps (~1 m. V) • Zero Volt Reference pad to measure HCC reference. • Counter driven Integrating DAC 0 -1000 m. V provides a common ramp for all comparator voltage inputs. • When monitored voltage ≥ reference ramp on 2 consecutive steps. 10 bit Counter value Latched • High and Low limits downloaded to HCC registers. Flip flop based warning flag in status word downloaded with each data packet. • HCC may perform limit based Clock or Regulator Interlock function if enabled. HCC Design Review April 24, 2014 4

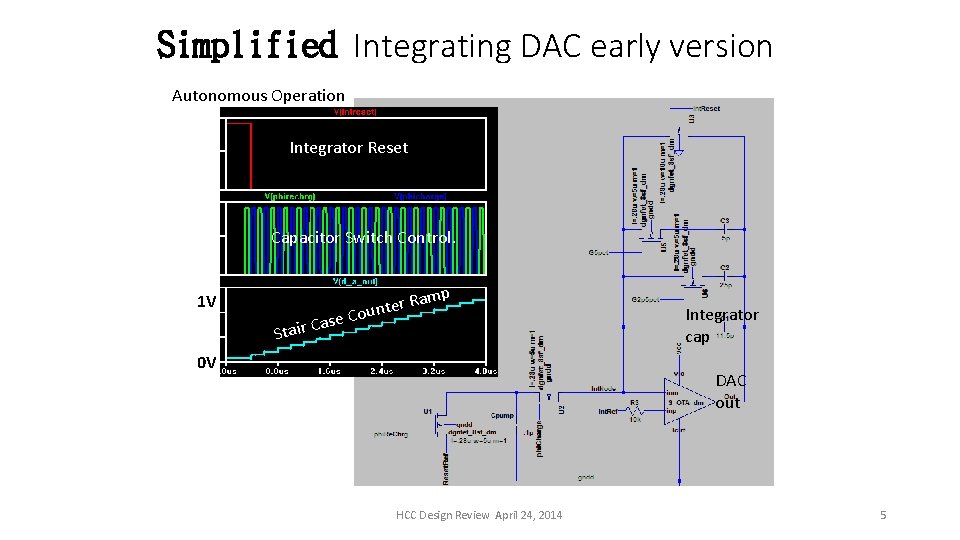

Simplified Integrating DAC early version Autonomous Operation Integrator Reset Capacitor Switch Control. 1 V p ase Stair C Ram r e t n Cou 0 V Integrator cap DAC out HCC Design Review April 24, 2014 5

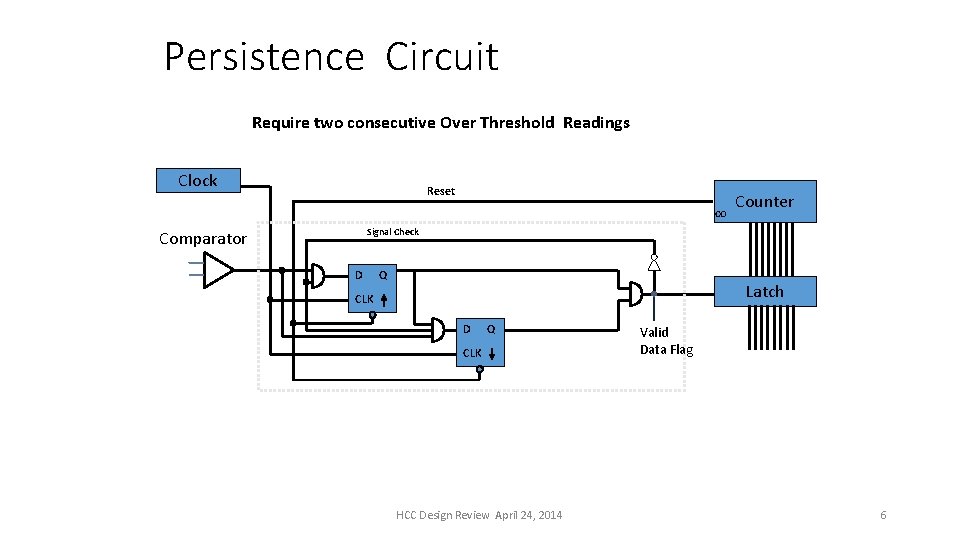

Persistence Circuit Require two consecutive Over Threshold Readings Clock Reset CO Counter Signal Check Comparator D Q Latch CLK D Q CLK HCC Design Review April 24, 2014 Valid Data Flag 6

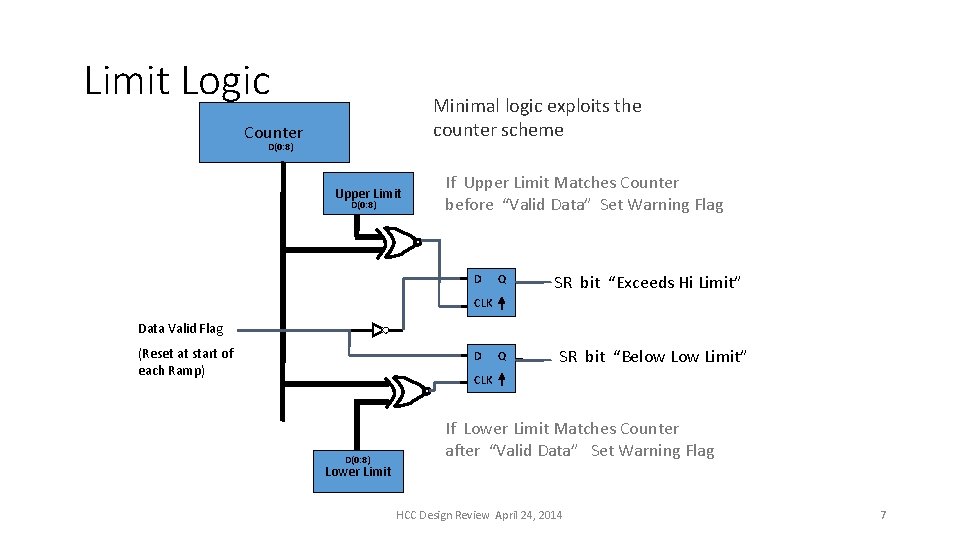

Limit Logic Minimal logic exploits the counter scheme Counter D(0: 8) Upper Limit D(0: 8) If Upper Limit Matches Counter before “Valid Data” Set Warning Flag D Q SR bit “Exceeds Hi Limit” CLK Data Valid Flag (Reset at start of each Ramp) D Q SR bit “Below Limit” CLK D(0: 8) If Lower Limit Matches Counter after “Valid Data” Set Warning Flag Lower Limit HCC Design Review April 24, 2014 7

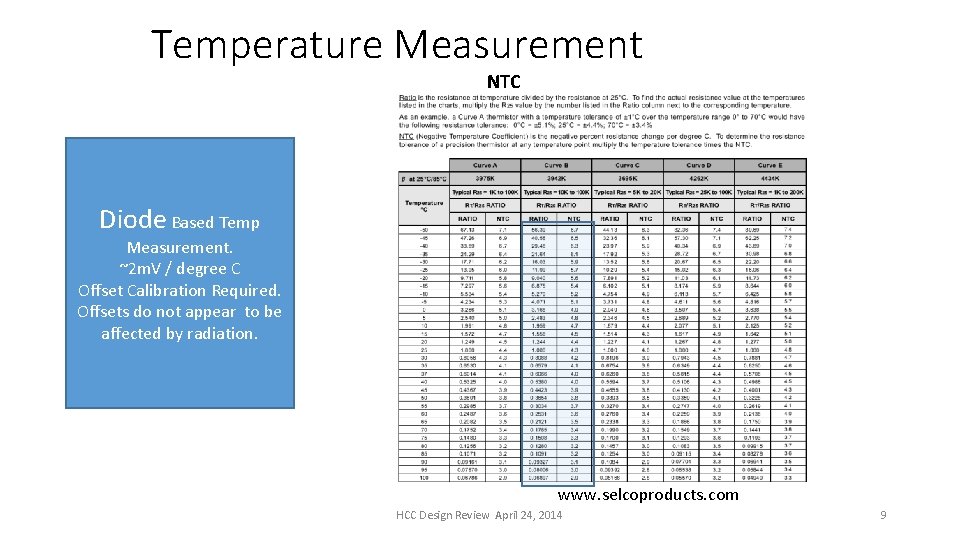

Measurement Accessories • NTC temp sensor • Diode Temp Sensor • HV return Current Measurement HCC Design Review April 24, 2014 8

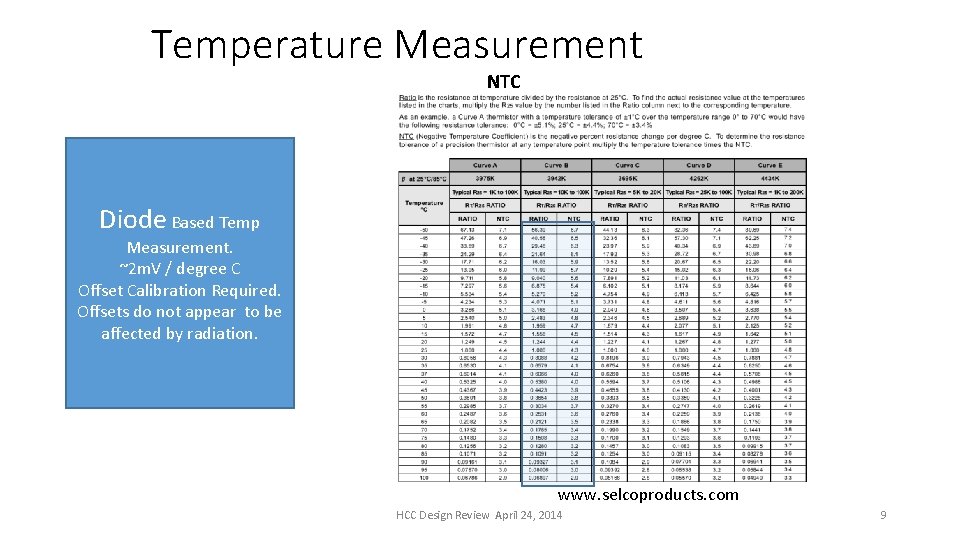

Temperature Measurement NTC Diode Based Temp Measurement. ~2 m. V / degree C Offset Calibration Required. Offsets do not appear to be affected by radiation. www. selcoproducts. com HCC Design Review April 24, 2014 9

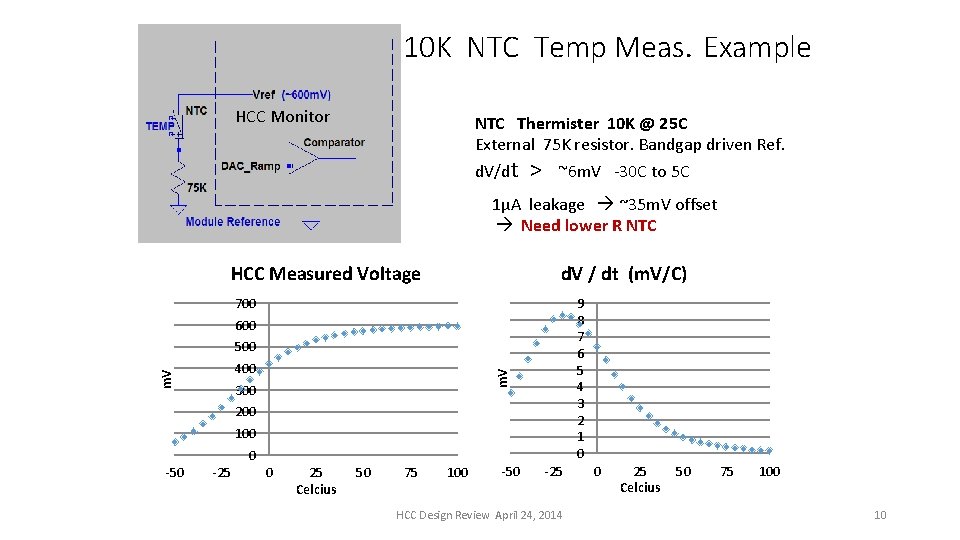

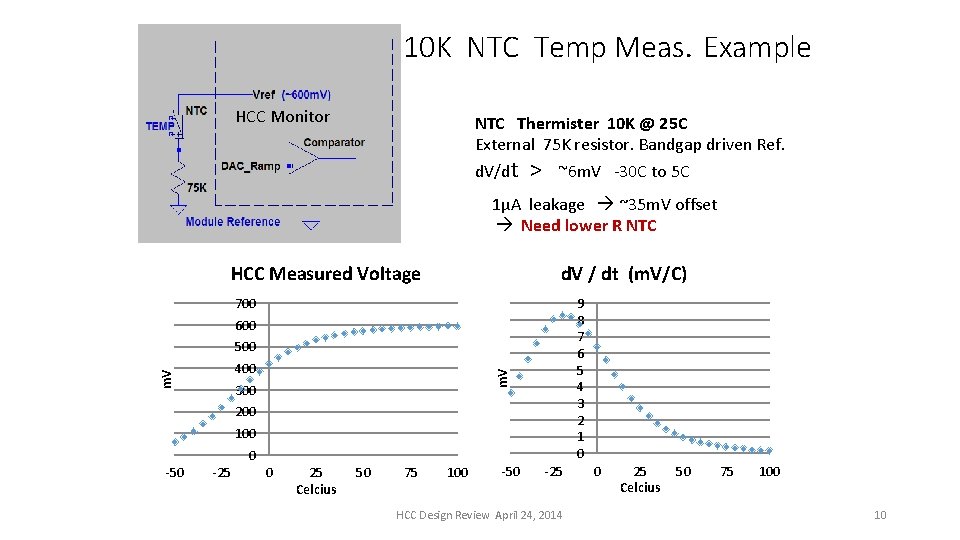

10 K NTC Temp Meas. Example HCC Monitor NTC Thermister 10 K @ 25 C External 75 K resistor. Bandgap driven Ref. d. V/dt > ~6 m. V -30 C to 5 C 1µA leakage ~35 m. V offset Need lower R NTC d. V / dt (m. V/C) HCC Measured Voltage 700 9 8 7 6 5 4 3 2 1 0 600 500 m. V 400 300 200 100 0 -50 -25 0 25 Celcius 50 75 100 -50 -25 HCC Design Review April 24, 2014 0 25 Celcius 50 75 100 10

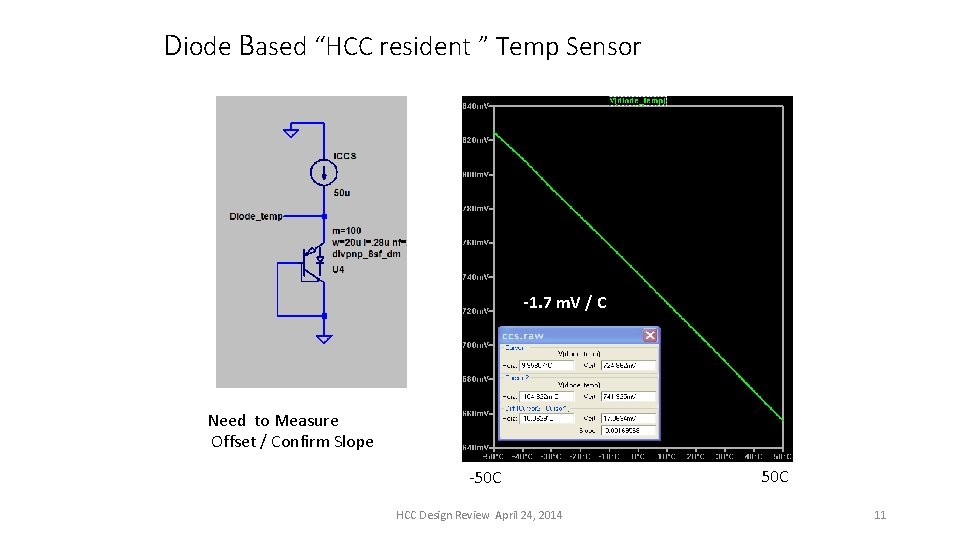

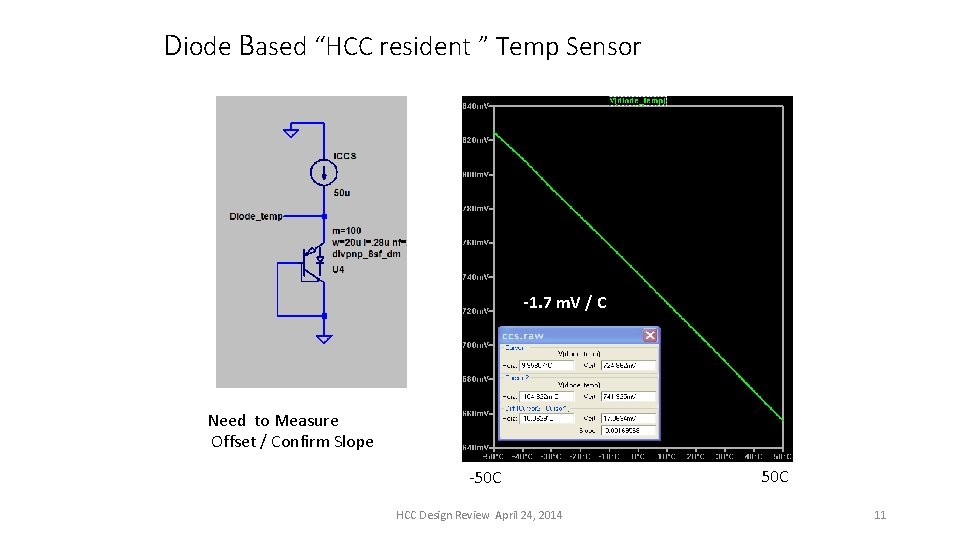

Diode Based “HCC resident ” Temp Sensor -1. 7 m. V / C Need to Measure Offset / Confirm Slope -50 C HCC Design Review April 24, 2014 50 C 11

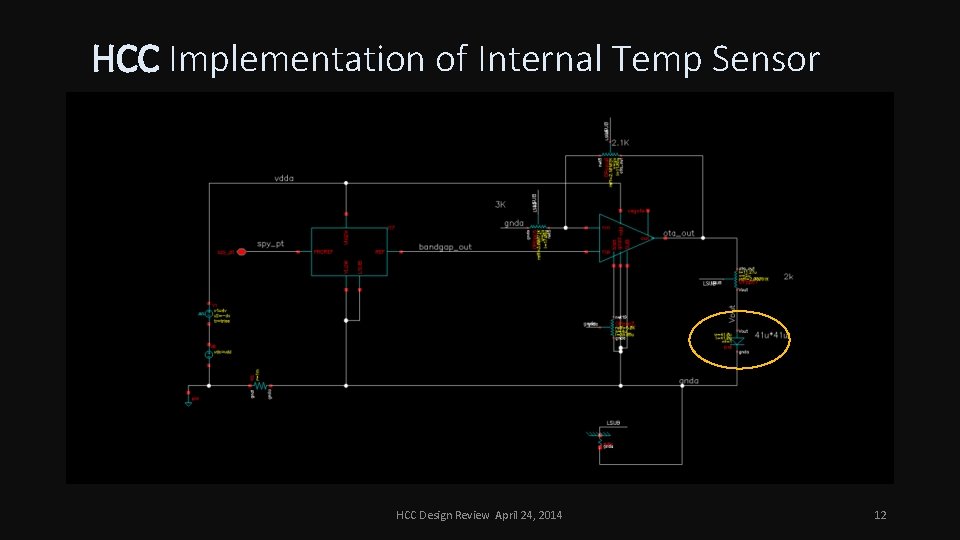

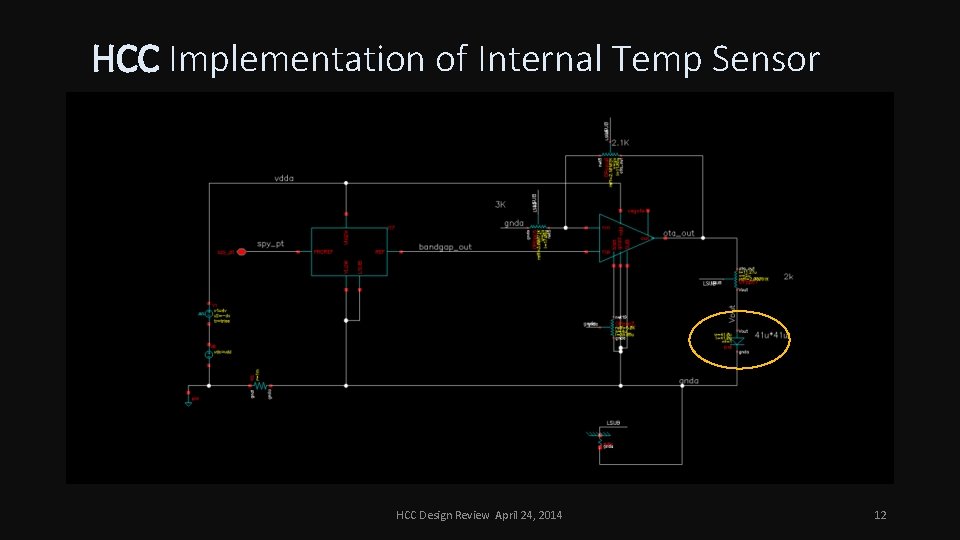

HCC Implementation of Internal Temp Sensor HCC Design Review April 24, 2014 12

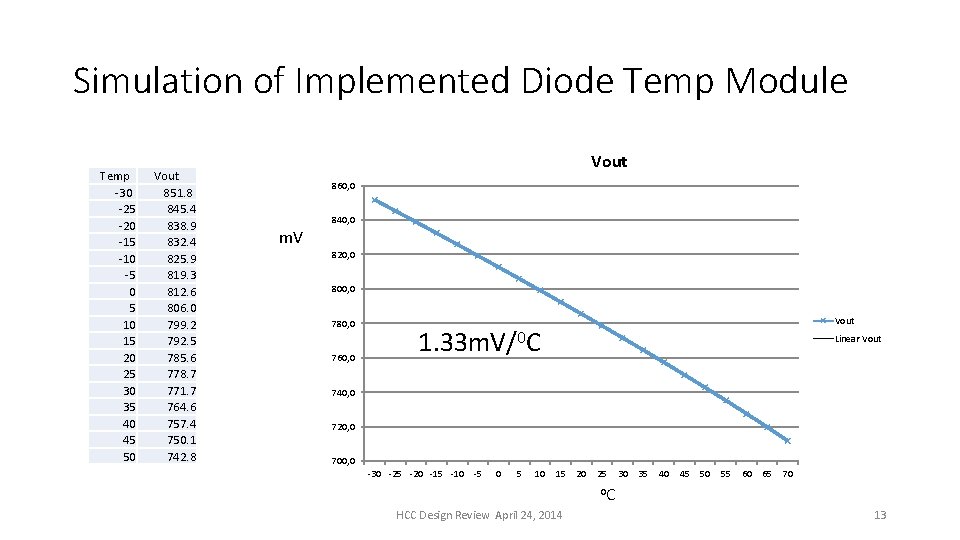

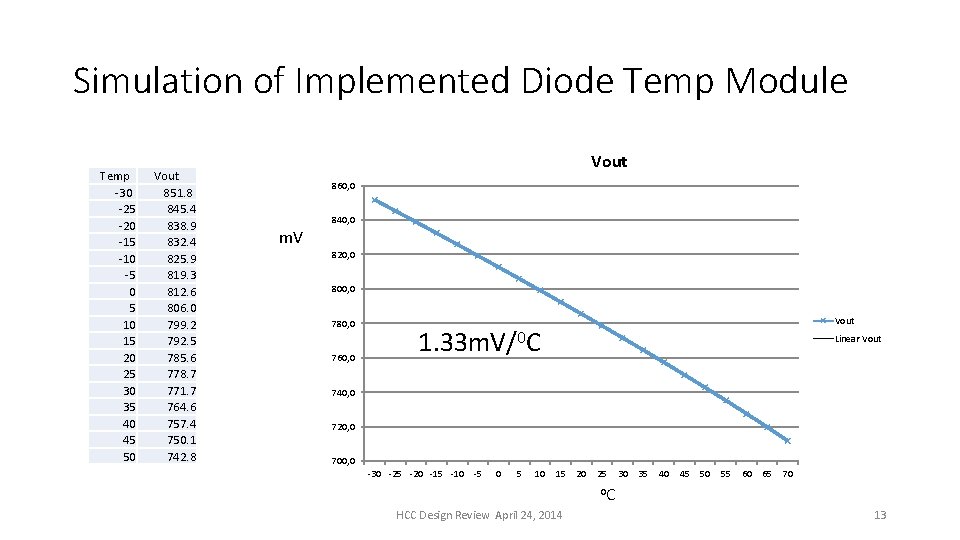

Simulation of Implemented Diode Temp Module Temp -30 -25 -20 -15 -10 -5 0 5 10 15 20 25 30 35 40 45 50 Vout 851. 8 845. 4 838. 9 832. 4 825. 9 819. 3 812. 6 806. 0 799. 2 792. 5 785. 6 778. 7 771. 7 764. 6 757. 4 750. 1 742. 8 Vout 860, 0 m. V 840, 0 820, 0 800, 0 780, 0 760, 0 Vout 1. 33 m. V/0 C Linear Vout 740, 0 720, 0 700, 0 -30 -25 -20 -15 -10 -5 0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 o. C HCC Design Review April 24, 2014 13

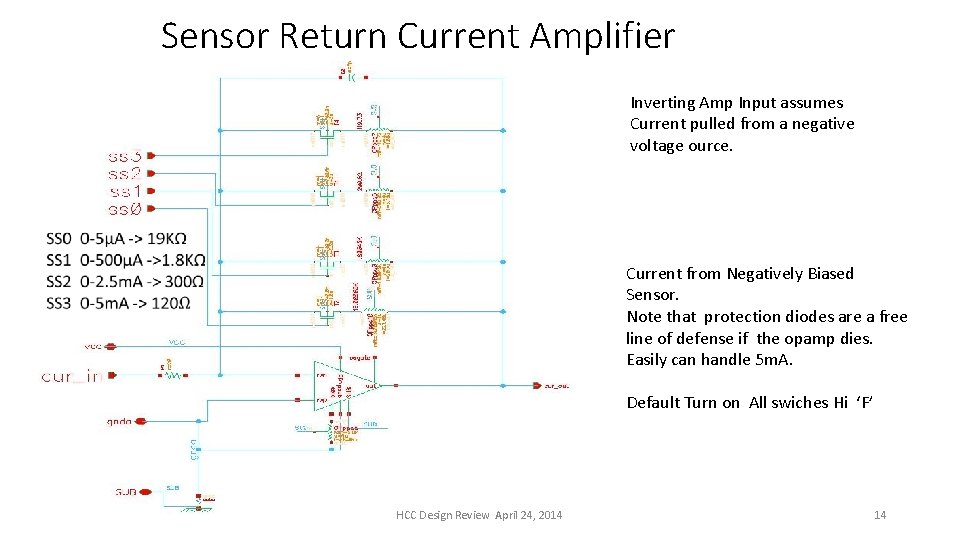

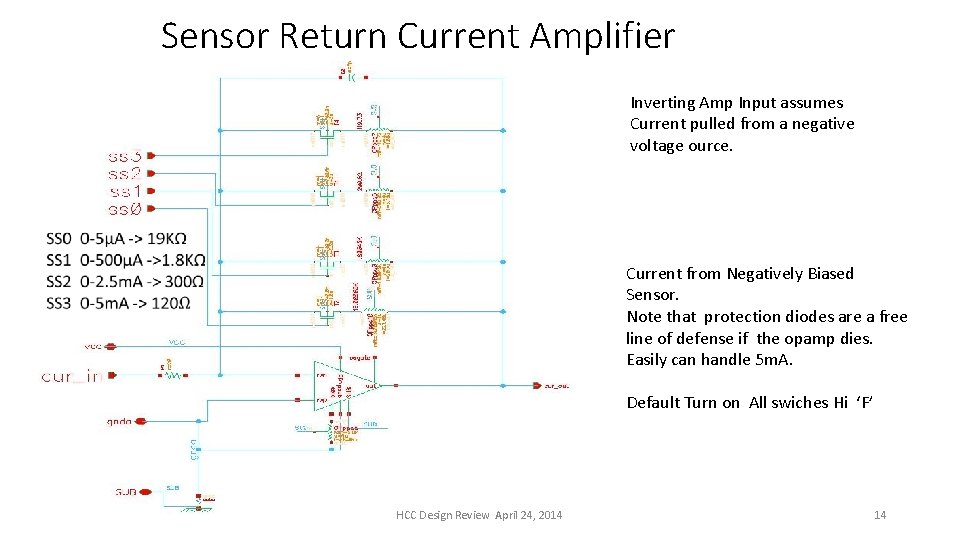

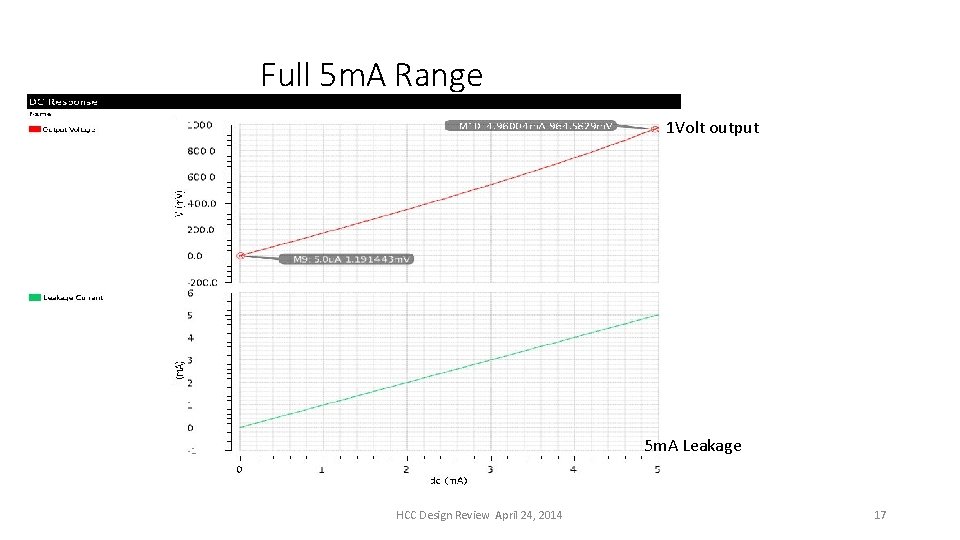

Sensor Return Current Amplifier Inverting Amp Input assumes Current pulled from a negative voltage ource. Current from Negatively Biased Sensor. Note that protection diodes are a free line of defense if the opamp dies. Easily can handle 5 m. A. Default Turn on All swiches Hi ‘F’ HCC Design Review April 24, 2014 14

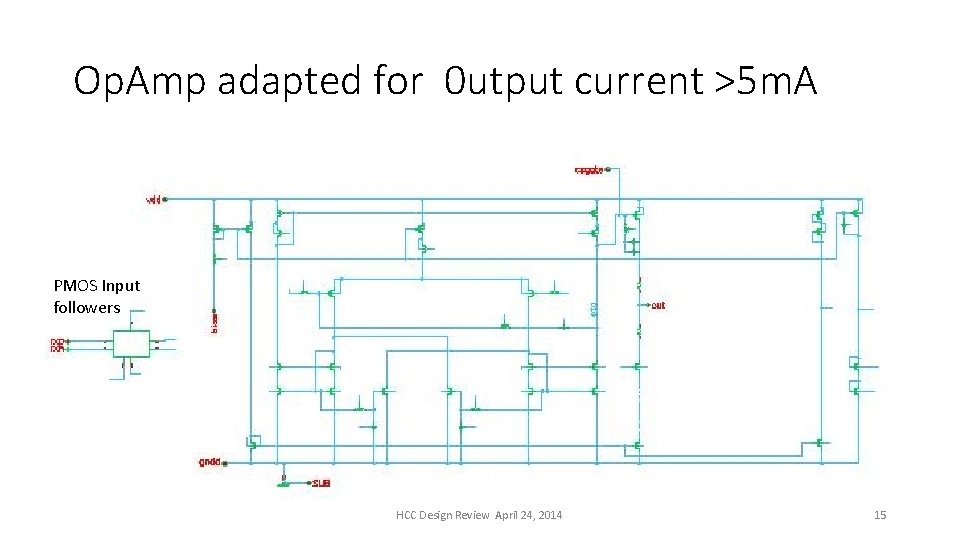

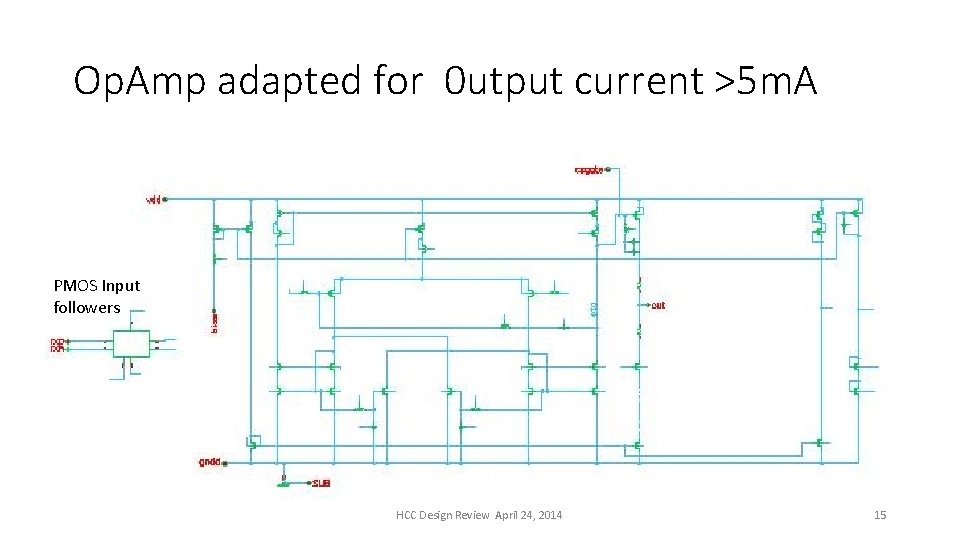

Op. Amp adapted for 0 utput current >5 m. A PMOS Input followers HCC Design Review April 24, 2014 15

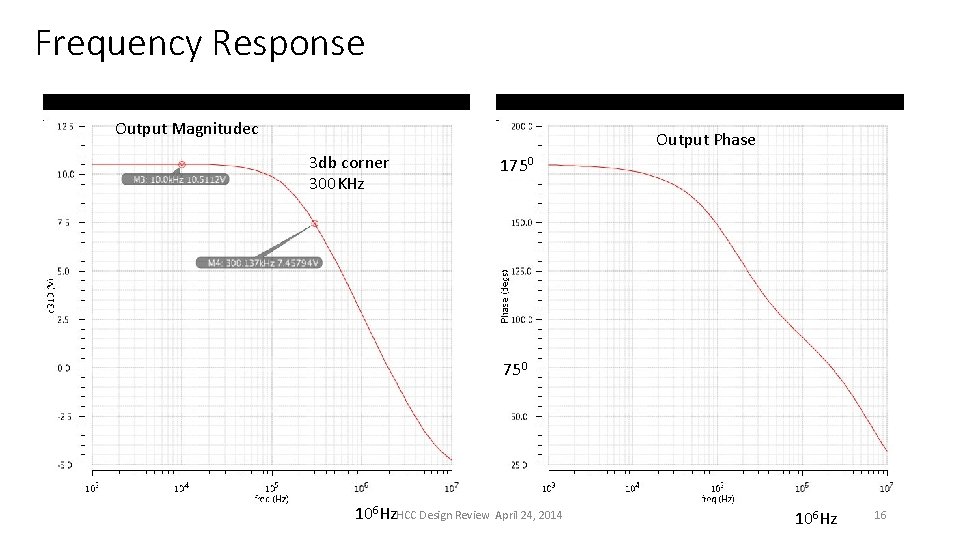

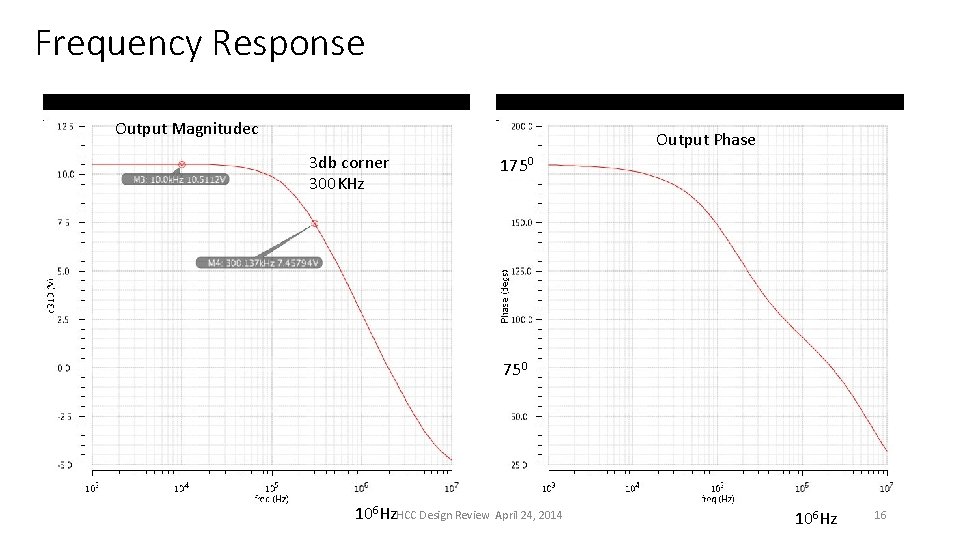

Frequency Response Output Magnitudec Output Phase 3 db corner 300 KHz 1750 106 Hz. HCC Design Review April 24, 2014 106 Hz 16

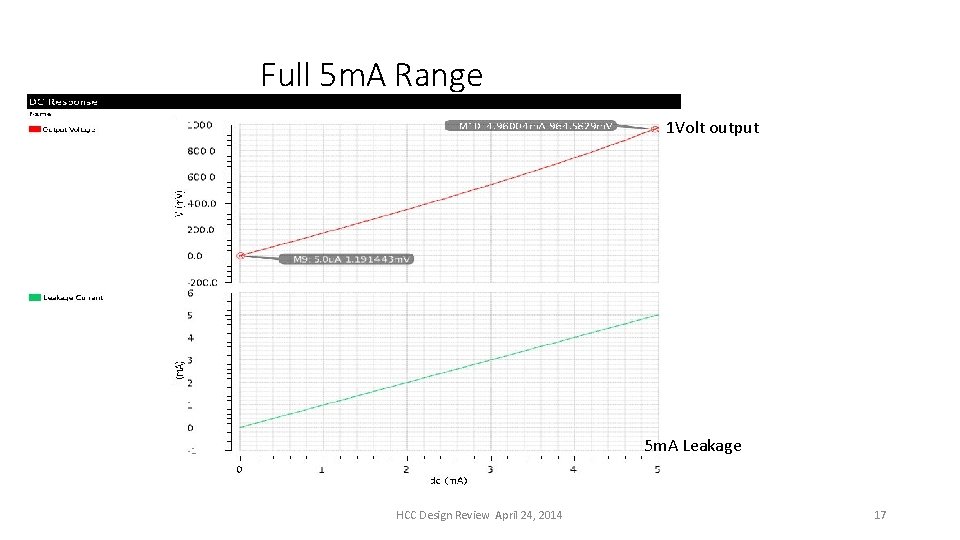

Full 5 m. A Range 1 Volt output 5 m. A Leakage HCC Design Review April 24, 2014 17

Summary The Autonomous monitor provides and automated measurement system able to monitor: HCC voltages Vraw, Vregulator, Vbandgap, 0 V hybrid, Internal and external temperature, current returned from the Sensor and an optional external input Programmed limit sensing can Provoke an Action error flag, turn off hybrid clocks or even the ABCn regulator (both require 2 different enable bits in the HCC). Each of the channels may be masked to eliminate Action. HCC Design Review April 24, 2014 18