HBK Tp HCMKhoa T BMT Ti liu Vi

ĐHBK Tp HCM-Khoa Đ-ĐT BMĐT Tài liệu: Vi xử lý - Hồ Trung Mỹ Chương 2 KIẾN TRÚC CPU VÀ TẬP LỆNH

Nô i dung 2. 1 SƠ ĐỒ KHỐI CPU 8 BIT CƠ BẢN 2. 2 TỔ CHỨC CÁC THANH GHI 2. 3 TỔ CHỨC BỘ NHỚ 2. 4 GHÉP NỐI BUS HỆ THỐNG 2. 5 CHU KỲ BUS, CHU KỲ MÁY 2. 6 CÁC PHƯƠNG PHÁP ĐỊNH ĐỊA CHỈ 2. 7 TẬP LỆNH

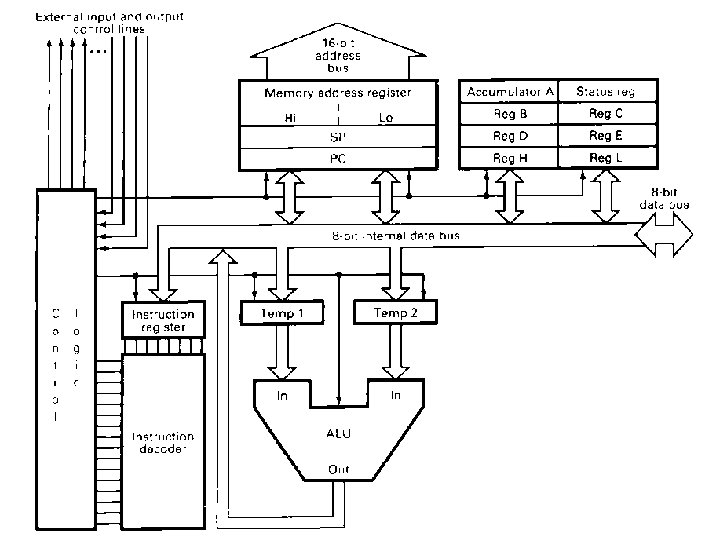

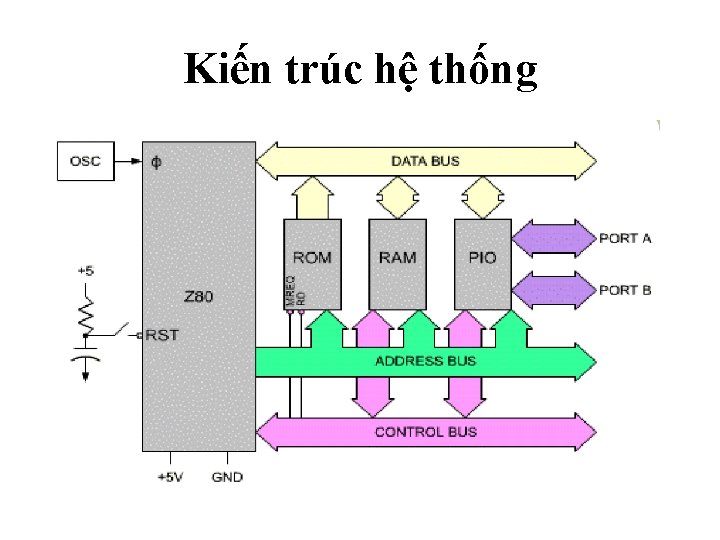

Vi xử lý • Có nhiều lọai vi xử lý từ rất đơn giản đến rất phức tạp • Phụ thuộc vào độ rộng bus dữ liệu, thanh ghi và ALU, ta có các vi xử lý 4 bit , 8 bit , 16 bit, 32 bit , 64 bit … • Thí dụ – Z 80 là vi xử lý 8 bit – 8086/88 là vi xử lý 16 bit • Tất cả các vi xử lý đều có: – Bus địa chỉ – Bus dữ liệu – Các tín hiệu điều khiển: RD, WR, CLK , RST, INT, . . .

Bus nội và ngoại • Bus nội (internal bus) là đường dẫn để truyền dữ liệu giữa các thanh ghi và ALU trong vi xử lý. • Bus ngoại (external bus) dùng cho bên ngoài nối đến RAM, ROM và các port I/O. • Độ rộng của bus nội và bus ngoại có thể khác nhau. • Thí dụ – 8088: bus nội là 16 bit, bus ngoại là 8 bit – 8086: bus nội là 16 bit, bus ngoại là 16 bit

2. 1 SƠ ĐỒ KHỐI CPU 8 BIT CƠ BẢN

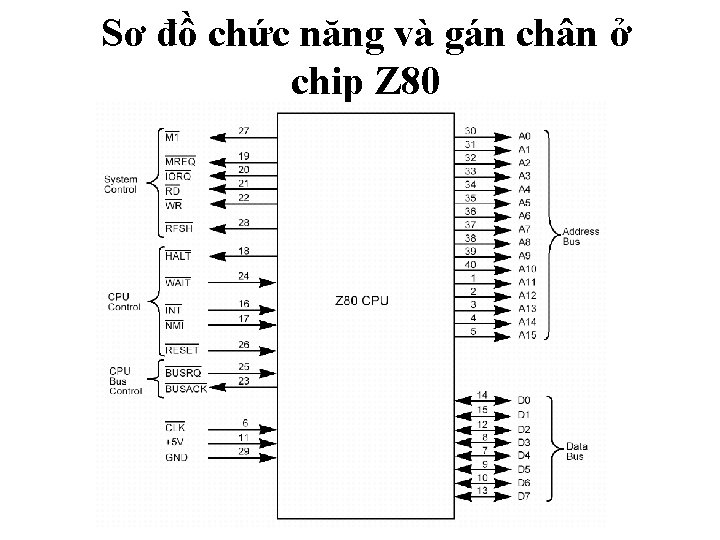

Sơ đồ chức năng và gán chân ở chip Z 80

Ca c đươ ng ti n hiê u • Có 6 nhóm tín hiệu: – Bus địa chỉ 16 đường (A 0 đến A 15) – Bus dữ liệu 8 đường (D 0 đến D 7) – 6 đường điều khiển hệ thống – 5 đường điều khiển CPU – 2 đường điều khiển bus CPU ( ) – 3 đường dành cho nguồn cấp điện và xung nhịp (+5 V, GND, và CLK)

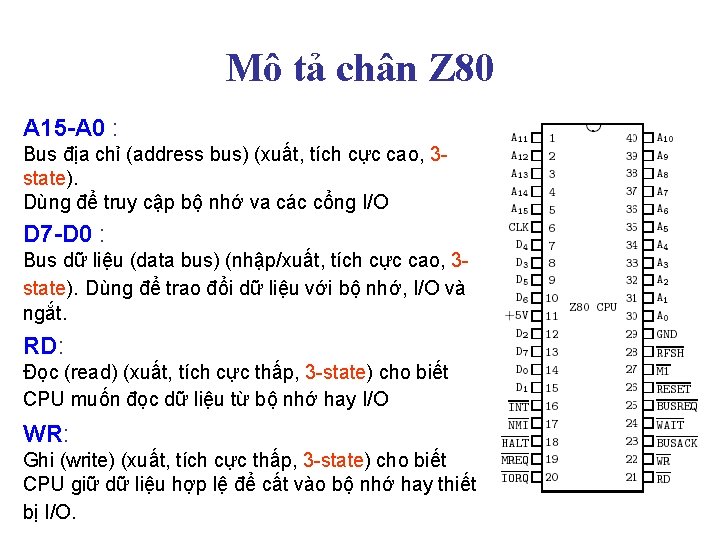

Mô tả chân Z 80 A 15 -A 0 : Bus địa chỉ (address bus) (xuất, tích cực cao, 3 state). Dùng để truy cập bộ nhớ va các cổng I/O D 7 -D 0 : Bus dữ liệu (data bus) (nhập/xuất, tích cực cao, 3 state). Dùng để trao đổi dữ liệu với bộ nhớ, I/O và ngắt. RD: Đọc (read) (xuất, tích cực thấp, 3 -state) cho biết CPU muốn đọc dữ liệu từ bộ nhớ hay I/O WR: Ghi (write) (xuất, tích cực thấp, 3 -state) cho biết CPU giữ dữ liệu hợp lệ để cất vào bộ nhớ hay thiết bị I/O.

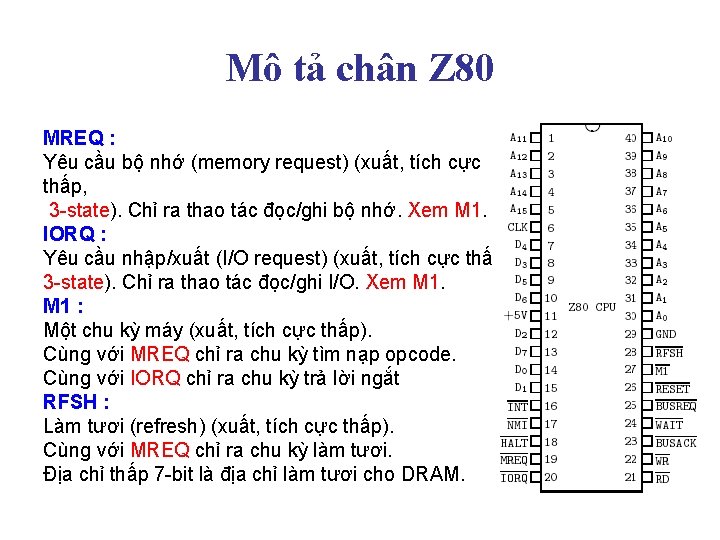

Mô tả chân Z 80 MREQ : Yêu cầu bộ nhớ (memory request) (xuất, tích cực thấp, 3 -state). Chỉ ra thao tác đọc/ghi bộ nhớ. Xem M 1. IORQ : Yêu cầu nhập/xuất (I/O request) (xuất, tích cực thấp, 3 -state). Chỉ ra thao tác đọc/ghi I/O. Xem M 1 : Một chu kỳ máy (xuất, tích cực thấp). Cùng với MREQ chỉ ra chu kỳ tìm nạp opcode. Cùng với IORQ chỉ ra chu kỳ trả lời ngắt RFSH : Làm tươi (refresh) (xuất, tích cực thấp). Cùng với MREQ chỉ ra chu kỳ làm tươi. Địa chỉ thấp 7 -bit là địa chỉ làm tươi cho DRAM.

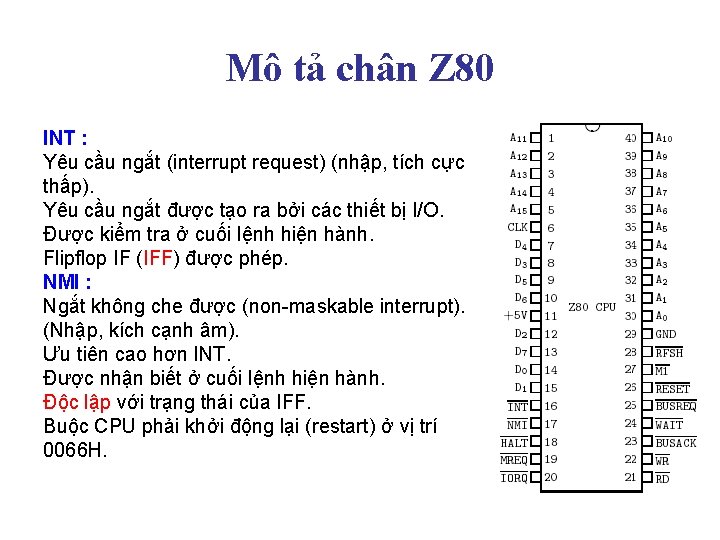

Mô tả chân Z 80 INT : Yêu cầu ngắt (interrupt request) (nhập, tích cực thấp). Yêu cầu ngắt được tạo ra bởi các thiết bị I/O. Được kiểm tra ở cuối lệnh hiện hành. Flipflop IF (IFF) được phép. NMI : Ngắt không che được (non-maskable interrupt). (Nhập, kích cạnh âm). Ưu tiên cao hơn INT. Được nhận biết ở cuối lệnh hiện hành. Độc lập với trạng thái của IFF. Buộc CPU phải khởi động lại (restart) ở vị trí 0066 H.

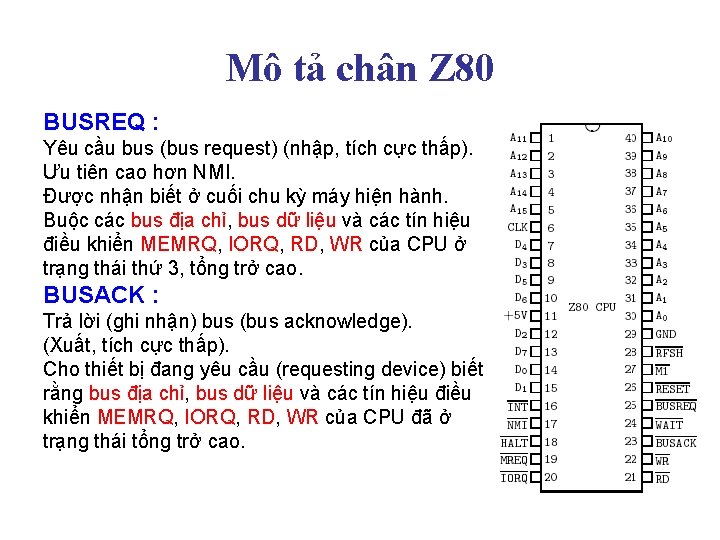

Mô tả chân Z 80 BUSREQ : Yêu cầu bus (bus request) (nhập, tích cực thấp). Ưu tiên cao hơn NMI. Được nhận biết ở cuối chu kỳ máy hiện hành. Buộc các bus địa chỉ, bus dữ liệu và các tín hiệu điều khiển MEMRQ, IORQ, RD, WR của CPU ở trạng thái thứ 3, tổng trở cao. BUSACK : Trả lời (ghi nhận) bus (bus acknowledge). (Xuất, tích cực thấp). Cho thiết bị đang yêu cầu (requesting device) biết rằng bus địa chỉ, bus dữ liệu và các tín hiệu điều khiển MEMRQ, IORQ, RD, WR của CPU đã ở trạng thái tổng trở cao.

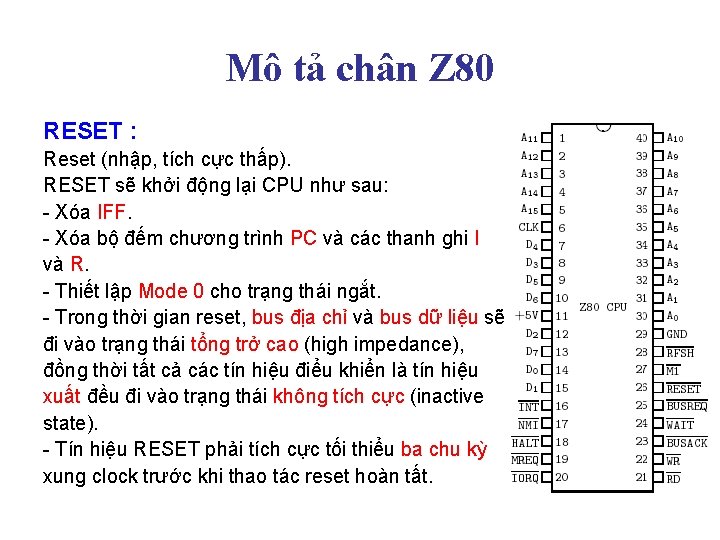

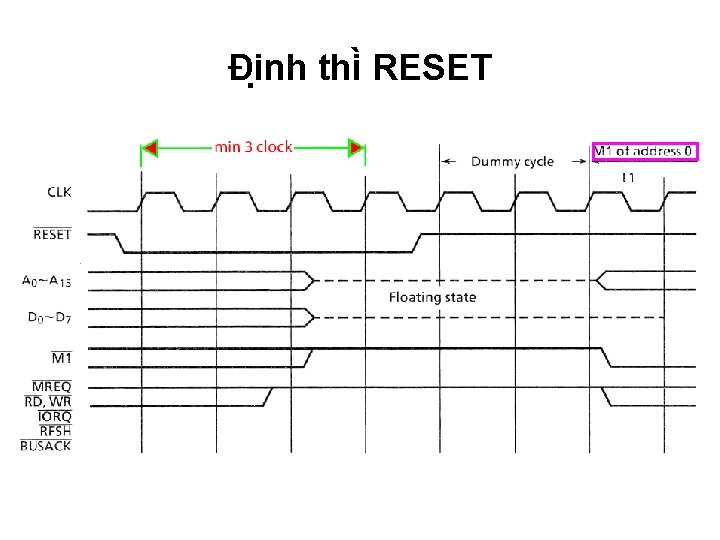

Mô tả chân Z 80 RESET : Reset (nhập, tích cực thấp). RESET sẽ khởi động lại CPU như sau: - Xóa IFF. - Xóa bộ đếm chương trình PC và các thanh ghi I và R. - Thiết lập Mode 0 cho trạng thái ngắt. - Trong thời gian reset, bus địa chỉ và bus dữ liệu sẽ đi vào trạng thái tổng trở cao (high impedance), đồng thời tất cả các tín hiệu điểu khiển là tín hiệu xuất đều đi vào trạng thái không tích cực (inactive state). - Tín hiệu RESET phải tích cực tối thiểu ba chu kỳ xung clock trước khi thao tác reset hoàn tất.

Kiến trúc hệ thống

2. 2 TỔ CHỨC CÁC THANH GHI

Z 80 CPU

Mô hình lập trình Z 80

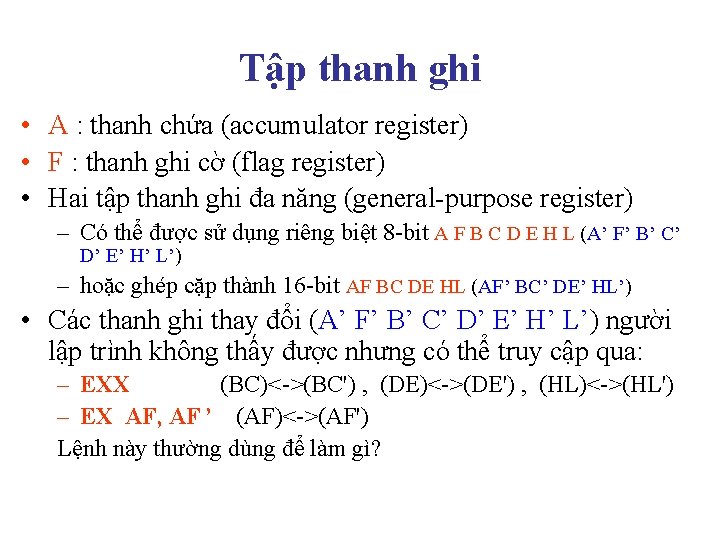

Tập thanh ghi • A : thanh chứa (accumulator register) • F : thanh ghi cờ (flag register) • Hai tập thanh ghi đa năng (general-purpose register) – Có thể được sử dụng riêng biệt 8 -bit A F B C D E H L (A’ F’ B’ C’ D’ E’ H’ L’) – hoặc ghép cặp thành 16 -bit AF BC DE HL (AF’ BC’ DE’ HL’) • Các thanh ghi thay đổi (A’ F’ B’ C’ D’ E’ H’ L’) người lập trình không thấy được nhưng có thể truy cập qua: – EXX (BC)<->(BC') , (DE)<->(DE') , (HL)<->(HL') – EX AF, AF ’ (AF)<->(AF') Lệnh này thường dùng để làm gì?

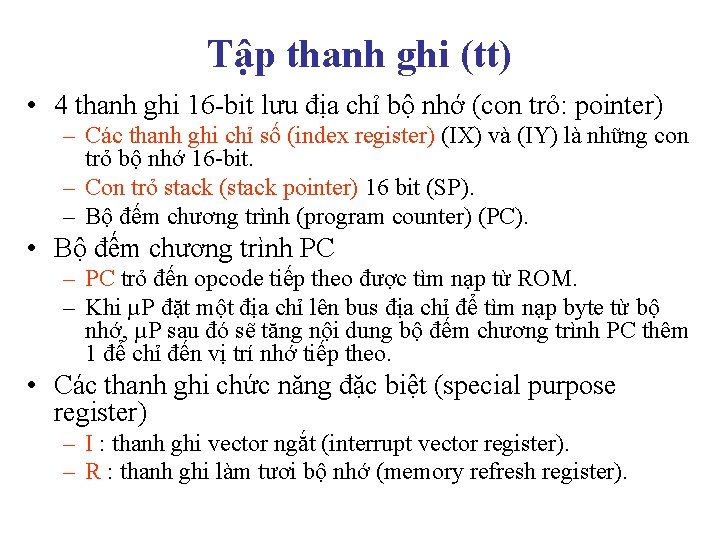

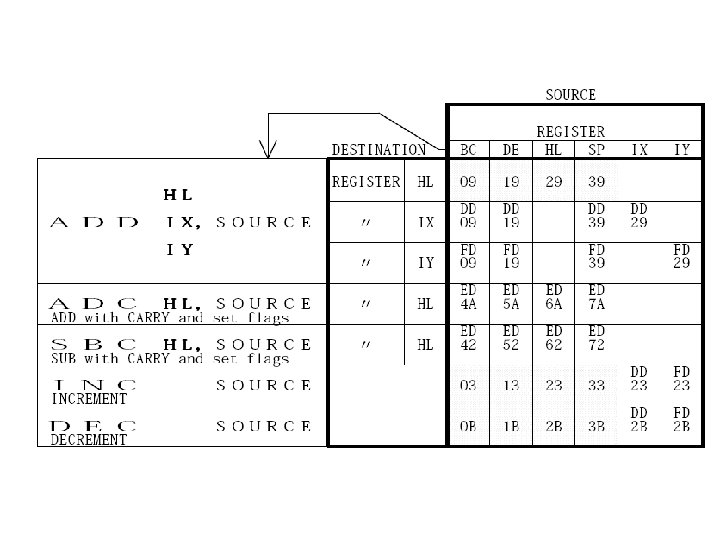

Tập thanh ghi (tt) • 4 thanh ghi 16 -bit lưu địa chỉ bộ nhớ (con trỏ: pointer) – Các thanh ghi chỉ số (index register) (IX) và (IY) là những con trỏ bộ nhớ 16 -bit. – Con trỏ stack (stack pointer) 16 bit (SP). – Bộ đếm chương trình (program counter) (PC). • Bộ đếm chương trình PC – PC trỏ đến opcode tiếp theo được tìm nạp từ ROM. – Khi µP đặt một địa chỉ lên bus địa chỉ để tìm nạp byte từ bộ nhớ, µP sau đó sẽ tăng nội dung bộ đếm chương trình PC thêm 1 để chỉ đến vị trí nhớ tiếp theo. • Các thanh ghi chức năng đặc biệt (special purpose register) – I : thanh ghi vector ngắt (interrupt vector register). – R : thanh ghi làm tươi bộ nhớ (memory refresh register).

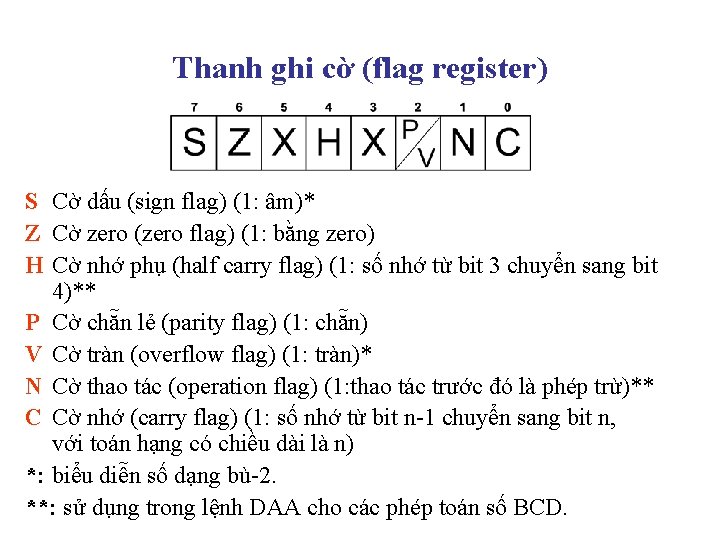

Thanh ghi cờ (flag register) S Cờ dấu (sign flag) (1: âm)* Z Cờ zero (zero flag) (1: bằng zero) H Cờ nhớ phụ (half carry flag) (1: số nhớ từ bit 3 chuyển sang bit 4)** P Cờ chẵn lẻ (parity flag) (1: chẵn) V Cờ tràn (overflow flag) (1: tràn)* N Cờ thao tác (operation flag) (1: thao tác trước đó là phép trừ)** C Cờ nhớ (carry flag) (1: số nhớ từ bit n-1 chuyển sang bit n, với toán hạng có chiều dài là n) *: biểu diễn số dạng bù-2. **: sử dụng trong lệnh DAA cho các phép toán số BCD.

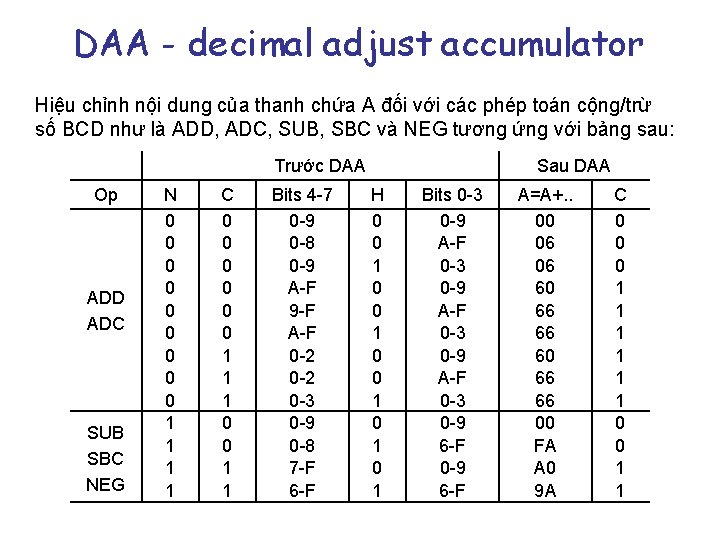

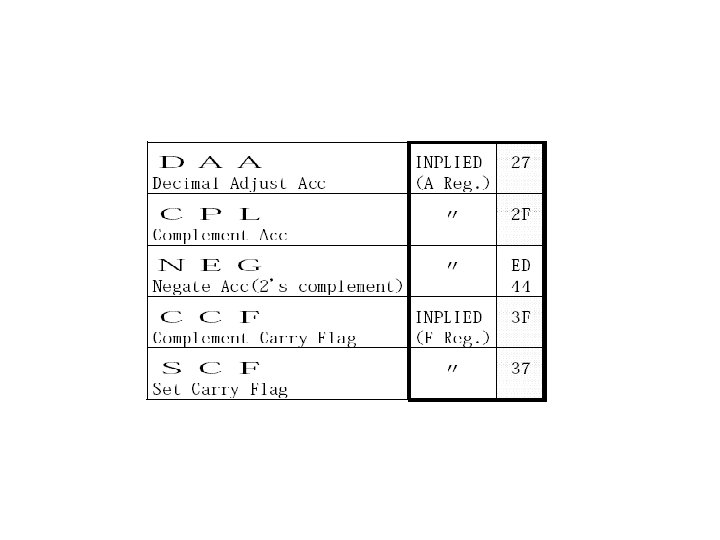

DAA - decimal adjust accumulator Hiệu chỉnh nội dung của thanh chứa A đối với các phép toán cộng/trừ số BCD như là ADD, ADC, SUB, SBC và NEG tương ứng với bảng sau: Trước DAA Op ADD ADC SUB SBC NEG N 0 0 0 0 0 1 1 C 0 0 0 1 1 1 0 0 1 1 Bits 4 -7 0 -9 0 -8 0 -9 A-F 9 -F A-F 0 -2 0 -3 0 -9 0 -8 7 -F 6 -F Sau DAA H 0 0 1 0 1 Bits 0 -3 0 -9 A-F 0 -3 0 -9 6 -F A=A+. . 00 06 06 60 66 66 00 FA A 0 9 A C 0 0 0 1 1 1 0 0 1 1

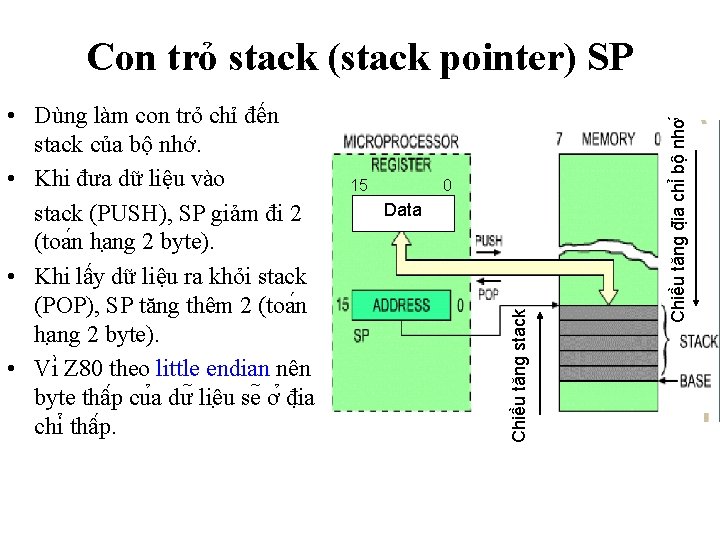

15 0 Data Chiê u tăng stack • Dùng làm con trỏ chỉ đến stack của bộ nhớ. • Khi đưa dữ liệu vào stack (PUSH), SP giảm đi 2 (toa n ha ng 2 byte). • Khi lấy dữ liệu ra khỏi stack (POP), SP tăng thêm 2 (toa n ha ng 2 byte). • Vi Z 80 theo little endian nên byte thâ p cu a dư liê u se ơ đi a chi thâ p. Chiê u tăng đi a chi bô nhơ Con trỏ stack (stack pointer) SP

2. 3 TỔ CHỨC BỘ NHỚ

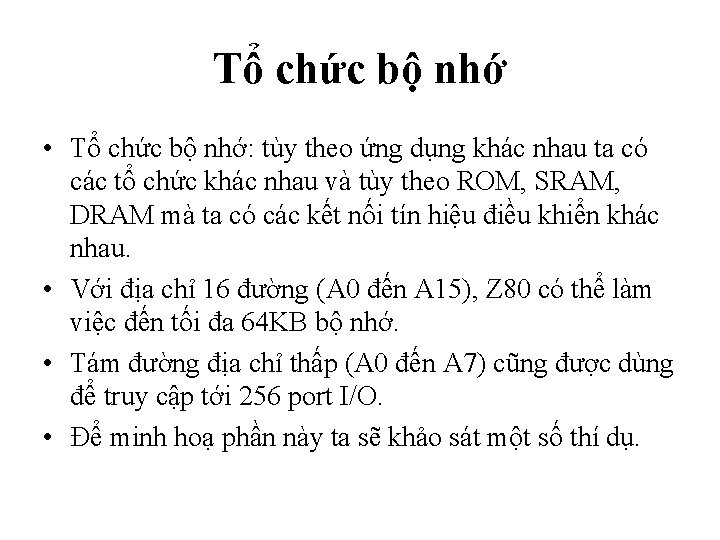

Tổ chức bộ nhớ • Tổ chức bộ nhớ: tùy theo ứng dụng khác nhau ta có các tổ chức khác nhau và tùy theo ROM, SRAM, DRAM mà ta có các kết nối tín hiệu điều khiển khác nhau. • Với địa chỉ 16 đường (A 0 đến A 15), Z 80 có thể làm việc đến tối đa 64 KB bộ nhớ. • Tám đường địa chỉ thấp (A 0 đến A 7) cũng được dùng để truy cập tới 256 port I/O. • Để minh hoạ phần này ta sẽ khảo sát một số thí dụ.

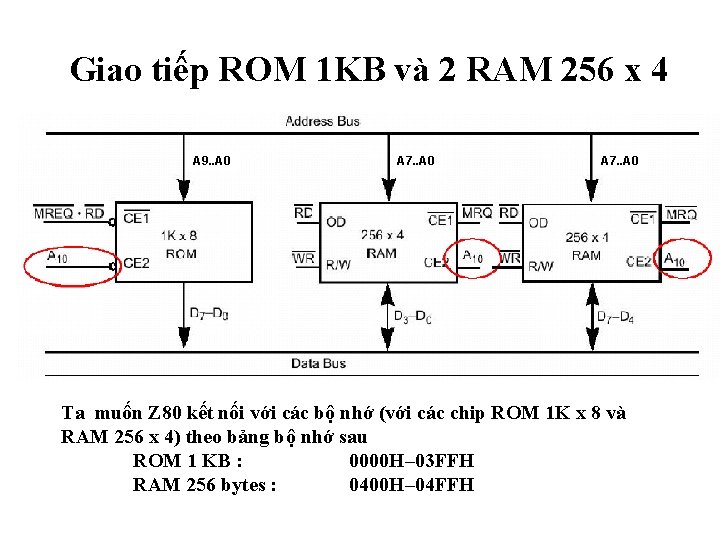

Giao tiếp ROM 1 KB và 2 RAM 256 x 4 A 9. . A 0 A 7. . A 0 Ta muốn Z 80 kết nối với các bộ nhớ (với các chip ROM 1 K x 8 và RAM 256 x 4) theo bảng bộ nhớ sau ROM 1 KB : 0000 H– 03 FFH RAM 256 bytes : 0400 H– 04 FFH

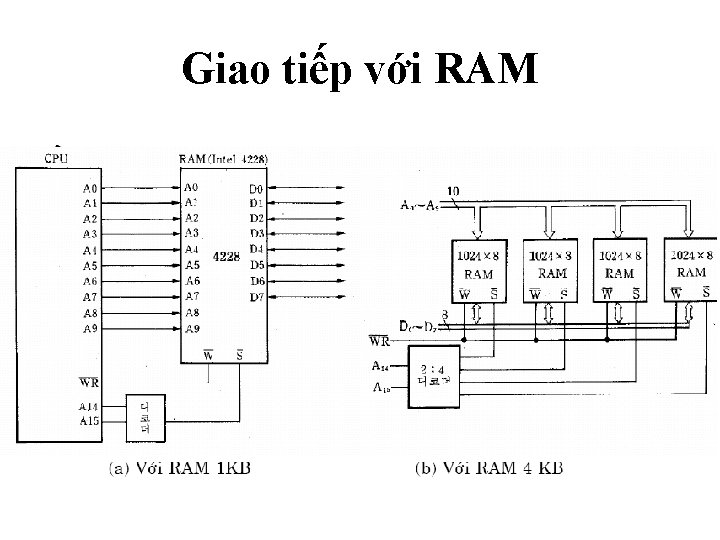

Giao tiếp với RAM

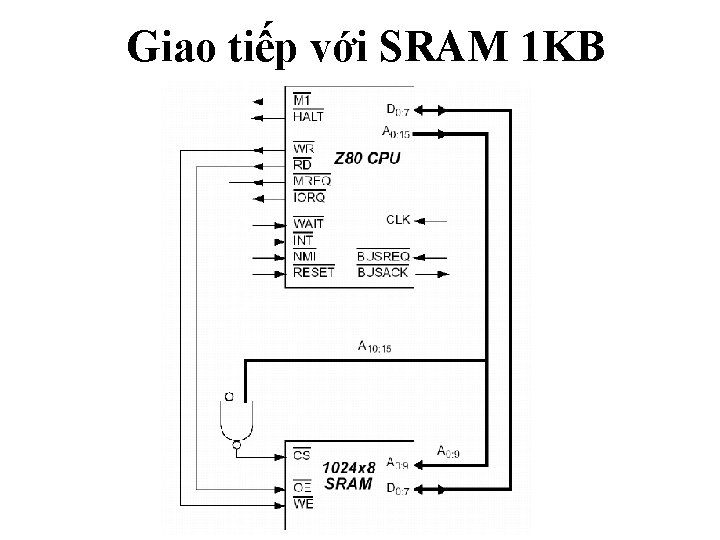

Giao tiếp với SRAM 1 KB

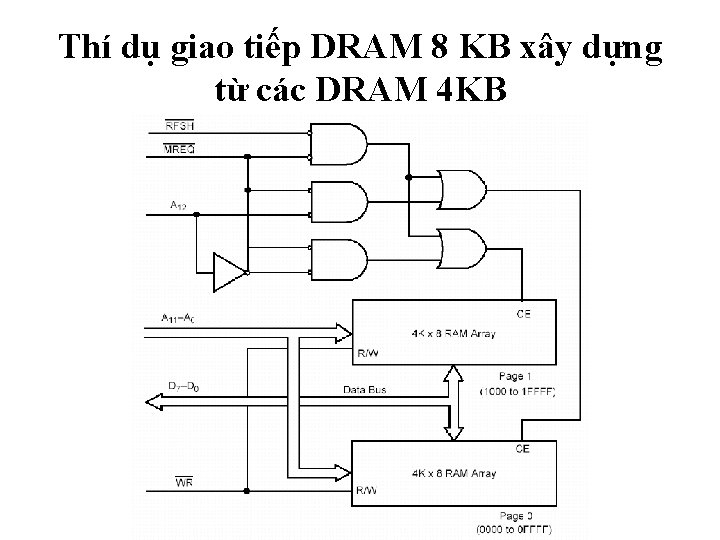

Thí dụ giao tiếp DRAM 8 KB xây dựng từ các DRAM 4 KB

2. 4 GHÉP NỐI BUS HỆ THỐNG

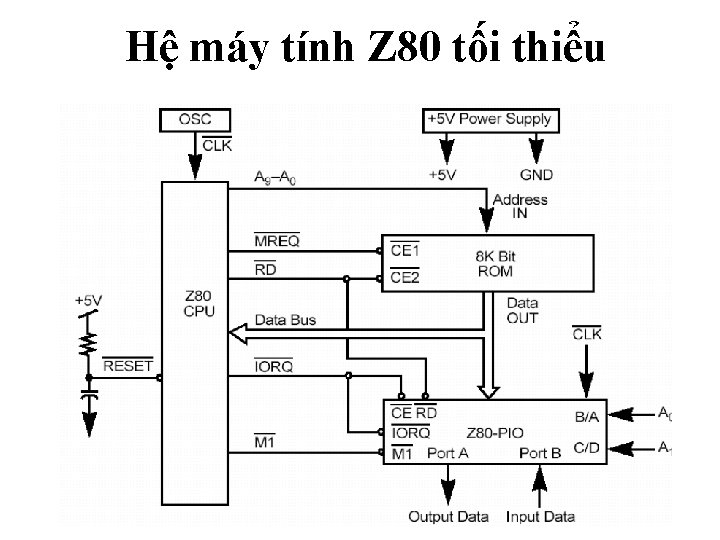

Hệ máy tính Z 80 tối thiểu

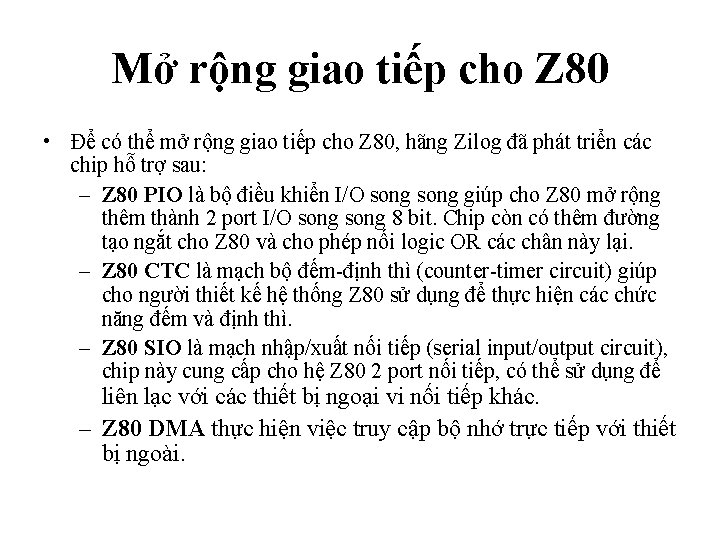

Mở rộng giao tiếp cho Z 80 • Để có thể mở rộng giao tiếp cho Z 80, hãng Zilog đã phát triển các chip hỗ trợ sau: – Z 80 PIO là bộ điều khiển I/O song giúp cho Z 80 mở rộng thêm thành 2 port I/O song 8 bit. Chip còn có thêm đường tạo ngắt cho Z 80 và cho phép nối logic OR các chân này lại. – Z 80 CTC là mạch bộ đếm-định thì (counter-timer circuit) giúp cho người thiết kế hệ thống Z 80 sử dụng để thực hiện các chức năng đếm và định thì. – Z 80 SIO là mạch nhập/xuất nối tiếp (serial input/output circuit), chip này cung cấp cho hệ Z 80 2 port nối tiếp, có thể sử dụng để liên lạc với các thiết bị ngoại vi nối tiếp khác. – Z 80 DMA thực hiện việc truy cập bộ nhớ trực tiếp với thiết bị ngoài.

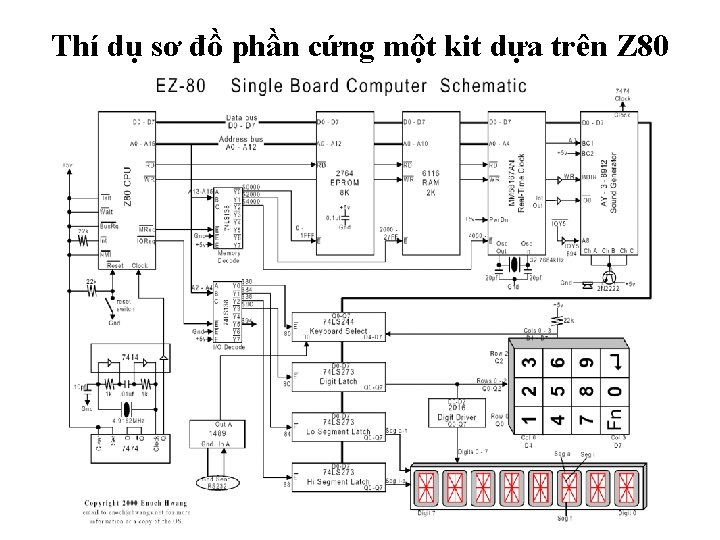

Thí dụ sơ đồ phần cứng một kit dựa trên Z 80

2. 5 CHU KỲ BUS, CHU KỲ MÁY

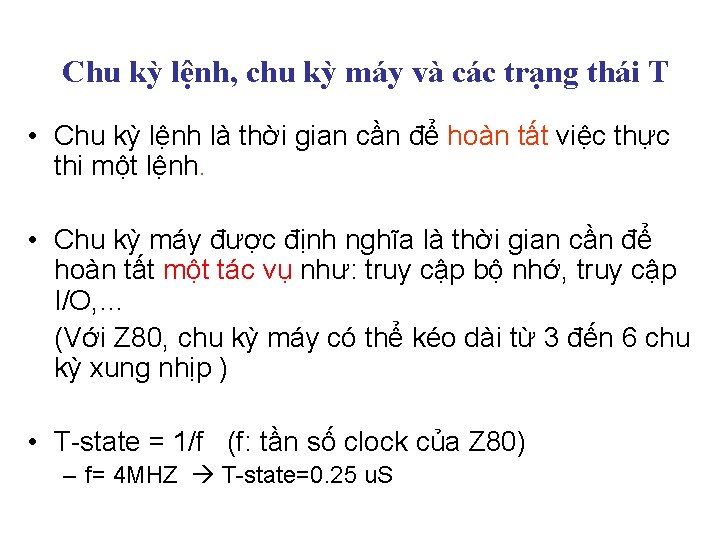

Chu kỳ lệnh, chu kỳ máy và các trạng thái T • Chu kỳ lệnh là thời gian cần để hoàn tất việc thực thi một lệnh. • Chu kỳ máy được định nghĩa là thời gian cần để hoàn tất một tác vụ như: truy cập bộ nhớ, truy cập I/O, … (Với Z 80, chu kỳ máy có thể kéo dài từ 3 đến 6 chu kỳ xung nhịp ) • T-state = 1/f (f: tần số clock của Z 80) – f= 4 MHZ T-state=0. 25 u. S

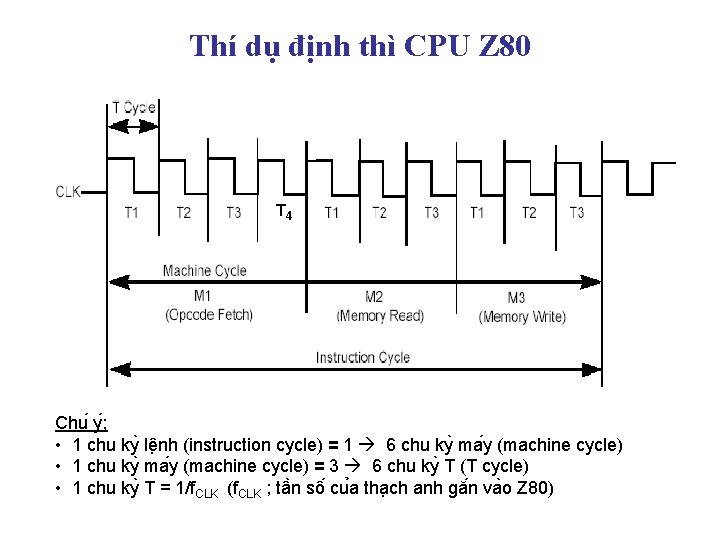

Thí dụ định thì CPU Z 80 T 4 Chu y ; • 1 chu ky lê nh (instruction cycle) = 1 6 chu ky ma y (machine cycle) • 1 chu ky ma y (machine cycle) = 3 6 chu ky T (T cycle) • 1 chu ky T = 1/f. CLK (f. CLK ; tâ n sô cu a tha ch anh gă n va o Z 80)

Chu kỳ máy Có 7 chu kỳ máy với Z 80: 1. Nhận mã lệnh (chu kỳ M 1) 2. Đọc hoặc ghi dữ liệu bộ nhớ 3. Đọc hoặc ghi I/O 4. Yêu cầu/ghi nhận bus (bus request/acknowledge) 5. Yêu cầu/ghi nhận INT 6. Yêu cầu/ghi nhận NMI 7. Thoát khỏi lệnh HALT

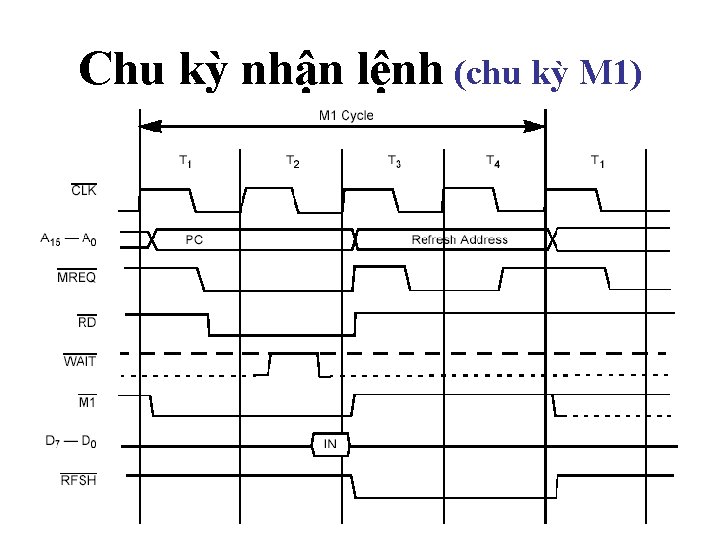

Chu kỳ nhận lệnh (chu kỳ M 1)

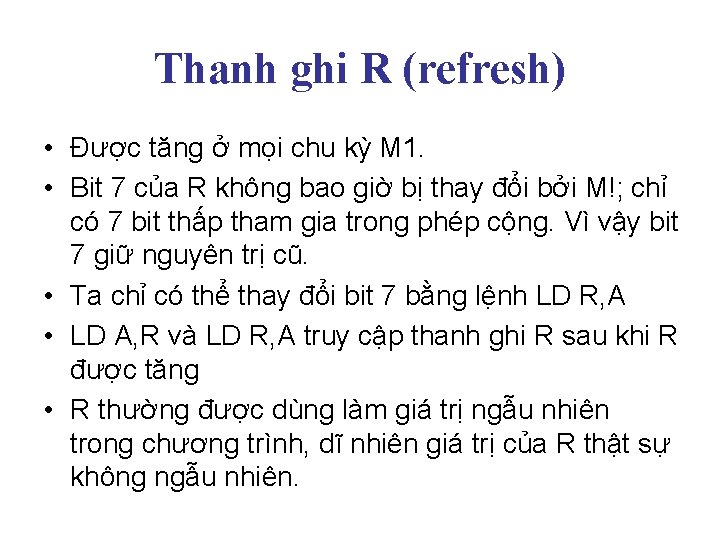

Thanh ghi R (refresh) • Được tăng ở mọi chu kỳ M 1. • Bit 7 của R không bao giờ bị thay đổi bởi M!; chỉ có 7 bit thấp tham gia trong phép cộng. Vì vậy bit 7 giữ nguyên trị cũ. • Ta chỉ có thể thay đổi bit 7 bằng lệnh LD R, A • LD A, R và LD R, A truy cập thanh ghi R sau khi R được tăng • R thường được dùng làm giá trị ngẫu nhiên trong chương trình, dĩ nhiên giá trị của R thật sự không ngẫu nhiên.

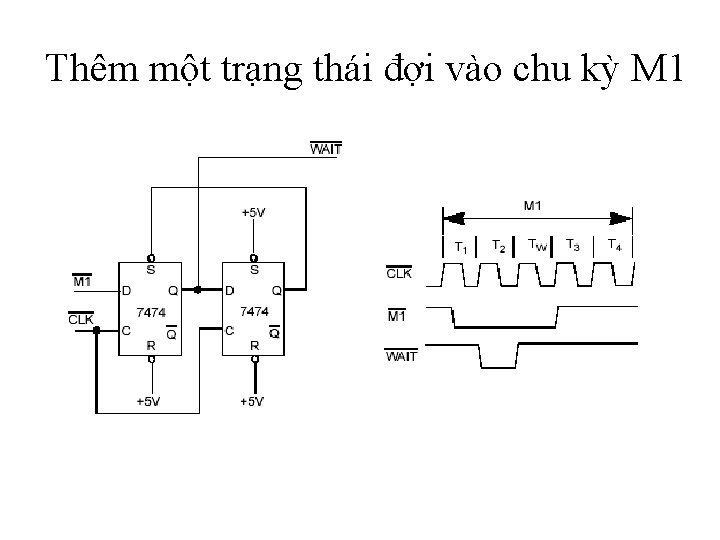

Thêm một trạng thái đợi vào chu kỳ M 1

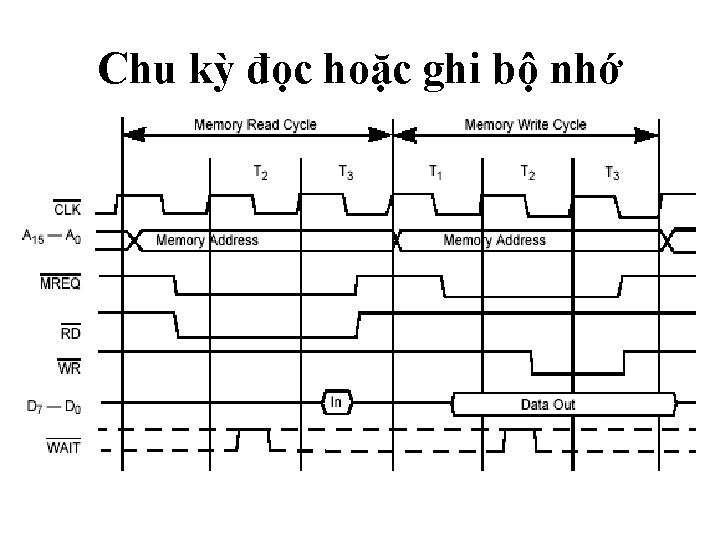

Chu kỳ đọc hoặc ghi bộ nhớ

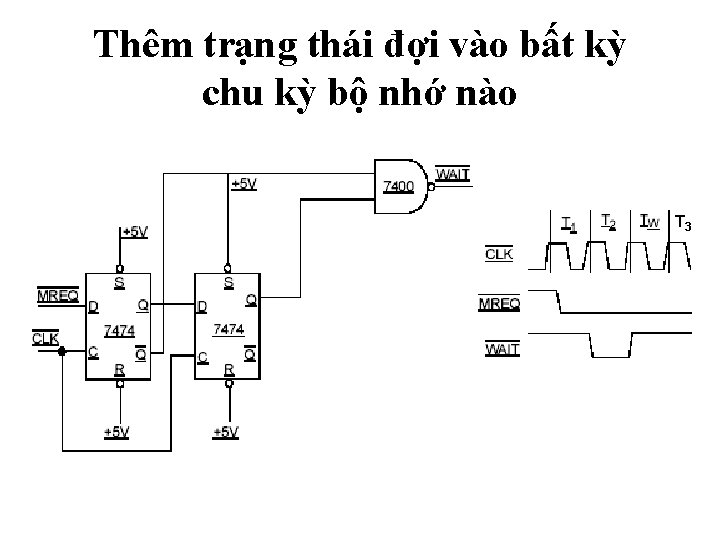

Thêm trạng thái đợi vào bất kỳ chu kỳ bộ nhớ nào T 3

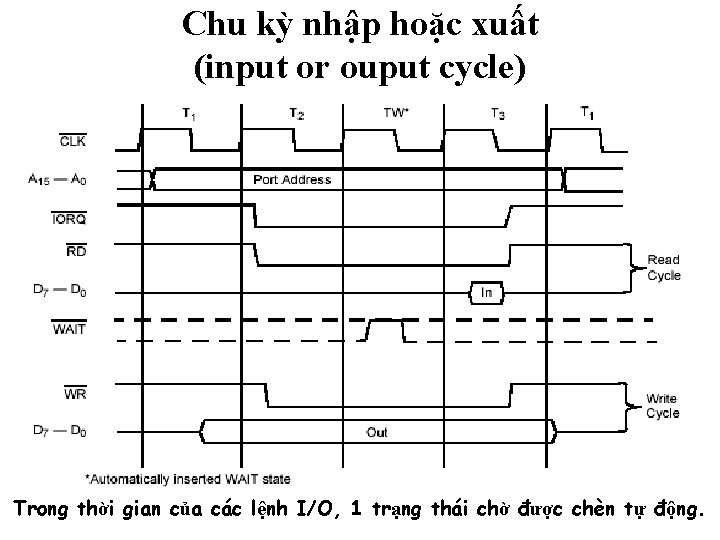

Chu kỳ nhập hoặc xuất (input or ouput cycle) Trong thời gian của các lệnh I/O, 1 trạng thái chờ được chèn tự động.

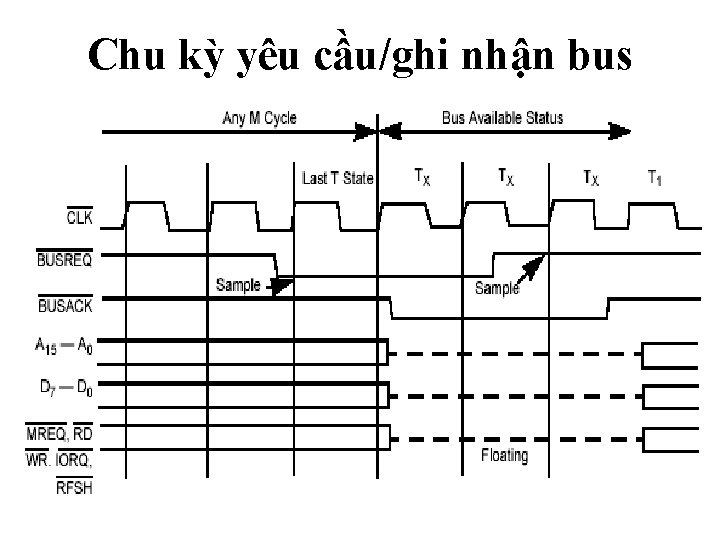

Chu kỳ yêu cầu/ghi nhận bus

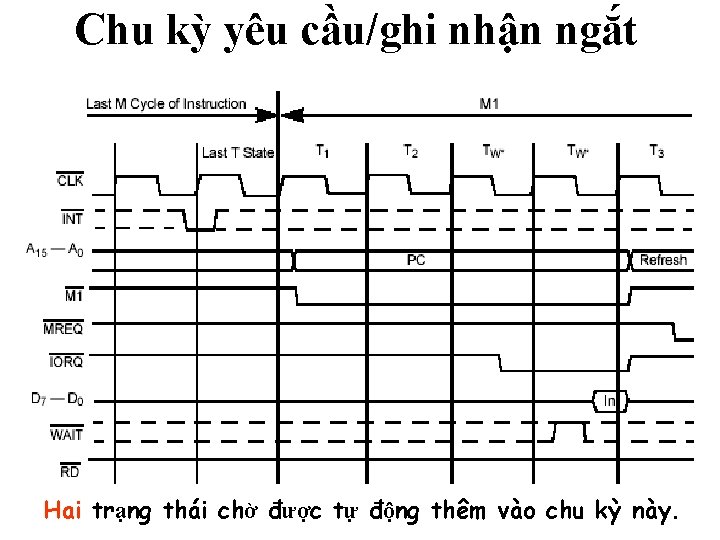

Chu kỳ yêu cầu/ghi nhận ngắt Hai trạng thái chờ được tự động thêm vào chu kỳ này.

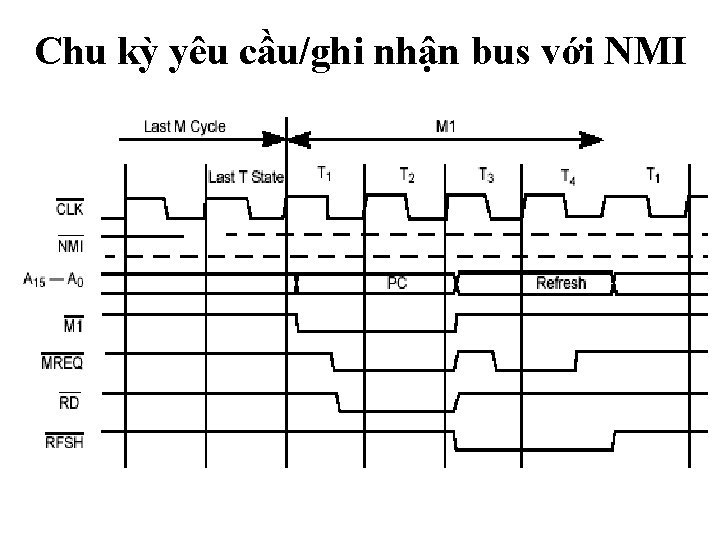

Chu kỳ yêu cầu/ghi nhận bus với NMI

Chu kỳ làm tươi M 1 • Chiếm 4 T đến 6 Ts • Z 80 chứa mạch cài đặt sẵn (built in circuitry) để làm tươi DRAM • Điều này giúp đơn giản phần cứng giao diện bên ngoài. • DRAM được cấu tạo từ các transistor MOS, lưu thông tin dưới dạng điện tích nạp cho điện dung; mỗi cell DRAM cần được làm tươi có chu kỳ. • Trong T 3 và T 4 (khi Z 80 đang thực hiện các lệnh nội), địa chỉ thấp được sử dụng để cung cấp địa chỉ 7 -bit cho việc làm tươi.

Tín hiệu Wait • Z 80 lấy mẫu tín hiệu wait trong thời gian T 2, nếu thấp (low), Z 80 sẽ thêm trạng thái wait. • dùng để mở rộng chu kỳ máy. • được sử dụng để giao diện bộ nhớ có thời gian đáp ứng chậm (slow response time). • Bộ nhớ chậm có giá thành thấp.

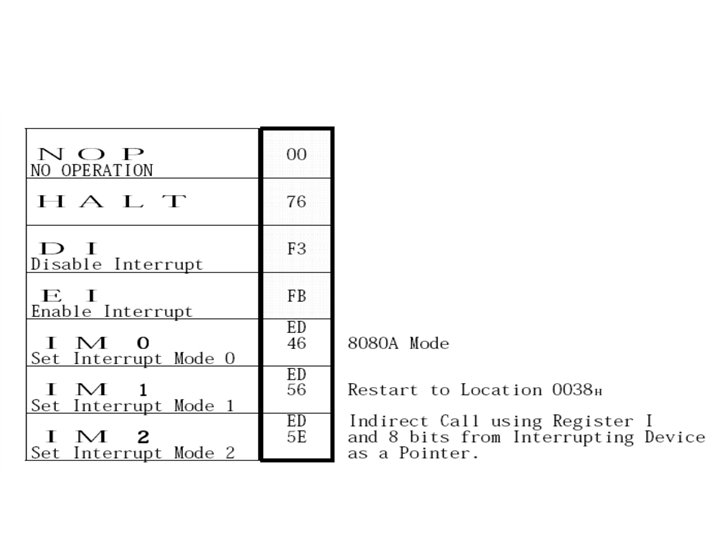

Ngắt (Interrupt) Có hai loại ngắt: • Không che được (NMI) – Không thể bị che. – Nhảy đến địa chỉ 0066 H của bộ nhớ. • Che được (INT) – Có 3 chế độ. – Có thể được thiết lập bằng IM x Instruction – IM 0 thiết lập ngắt chế độ 0 (Interrupt mode 0) – IM 1 thiết lập ngắt chế độ 1 (Interrupt mode 1) – IM 2 thiết lập ngắt chế độ 2 (Interrupt mode 2)

Các chế độ ngắt • Mode 0: – Một 8 bit opcode được tìm nạp từ bus dữ liệu và thực thi. – Thiết bị tạo ngắt (source interrupt device) phải đặt 8 bit opcode ở bus dữ liệu. – 8 bit opcode thường là các lệnh RST p. • Mode 1: – Nhảy đến địa chỉ 0038 h. – Không có giá trị nào được yêu cầu ở bus dữ liệu. • Mode 2: – Nhảy đến địa chỉ (register I × 256 + value từ thiết bị tạo ngắt [interrupting device] đặt trên bus) – I là 8 bit cao (high 8 bit) của vector ngắt (interrupt vector) – Value là 8 bit thấp (low 8 bit) của vector ngắt

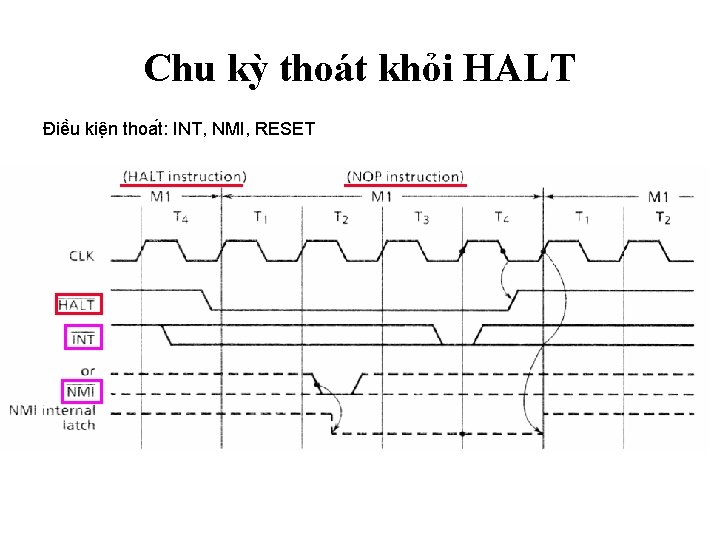

Chu kỳ thoát khỏi HALT Điê u kiê n thoa t: INT, NMI, RESET

Đi nh thi RESET

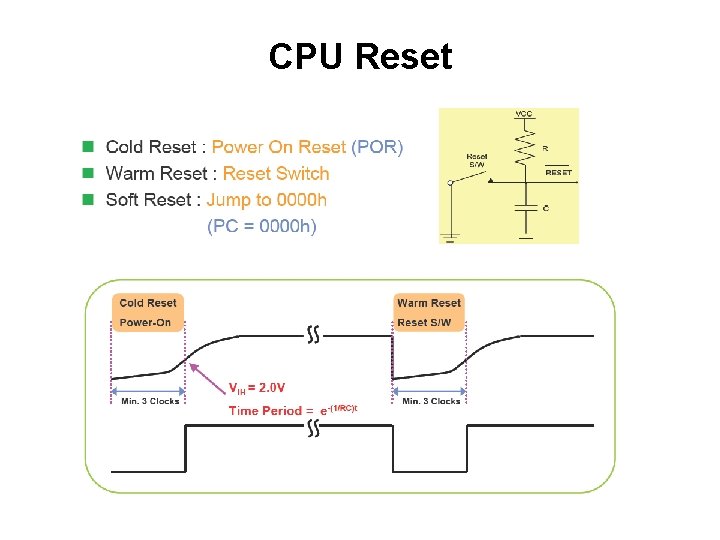

CPU Reset

2. 6 CÁC PHƯƠNG PHÁP ĐỊNH ĐỊA CHỈ

Định địa chỉ trong Z 80 • Phần lớn các lệnh Z 80 làm việc với dữ liệu được lưu trữ trong các thanh ghi CPU, bộ nhớ ngoài, hoặc trong các cổng I/O. Z 80 có cách định địa chỉ sau: – Định địa chỉ tức thời (hă ng sô 8 bit) – Định địa chỉ tức thời mở rộng (hă ng sô 16 bit) – Định địa chỉ trực tiếp (đi a chi 8 bit) – Định địa chỉ trực tiếp mở rộng (đi a chi 16 bit) – Định địa chỉ trang 0 (có sửa đổi) – Định địa chỉ tương đối – Định địa chỉ theo chỉ số – Định địa chỉ thanh ghi – Định địa chỉ hiểu ngầm – Định địa chỉ gián tiếp qua thanh ghi – Định địa chỉ cho bit

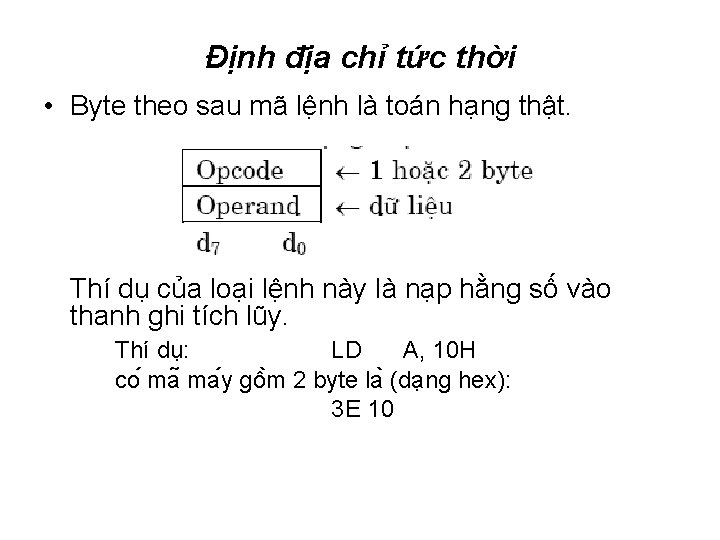

Định địa chỉ tức thời • Byte theo sau mã lệnh là toán hạng thật. Thí dụ của loại lệnh này là nạp hằng số vào thanh ghi tích lũy. Thí dụ: LD A, 10 H co ma ma y gô m 2 byte la (da ng hex): 3 E 10

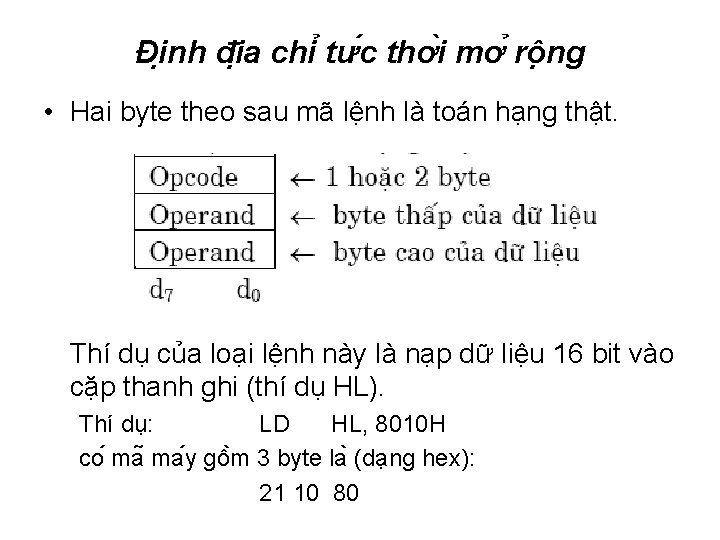

Đi nh đi a chi tư c thơ i mơ rô ng • Hai byte theo sau mã lệnh là toán hạng thật. Thí dụ của loại lệnh này là nạp dữ liệu 16 bit vào cặp thanh ghi (thí dụ HL). Thí dụ: LD HL, 8010 H co ma ma y gô m 3 byte la (da ng hex): 21 10 80

Định địa chỉ trực tiếp • Cung cấp địa chỉ 8 bit của toán hạng ngay sau mã lệnh Thí dụ: IN A, (20 H) ma ma y la (dạng hex): DB 20

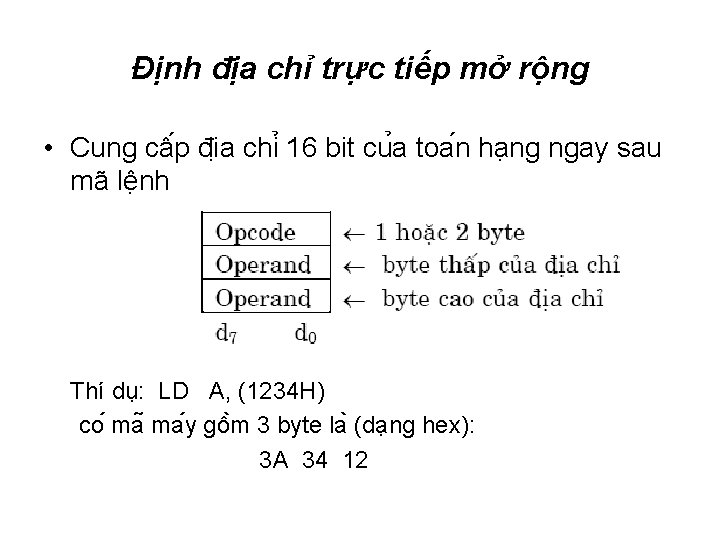

Định địa chỉ trực tiếp mở rộng • Cung câ p đi a chi 16 bit cu a toa n ha ng ngay sau mã lê nh Thí dụ: LD A, (1234 H) co ma ma y gô m 3 byte la (da ng hex): 3 A 34 12

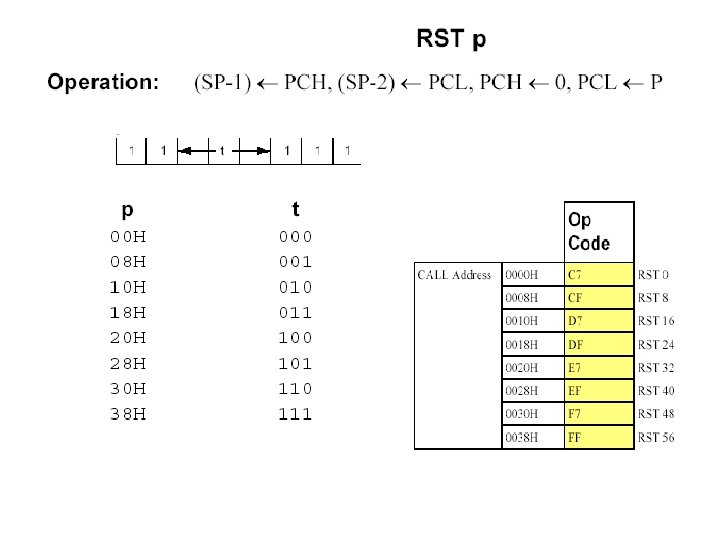

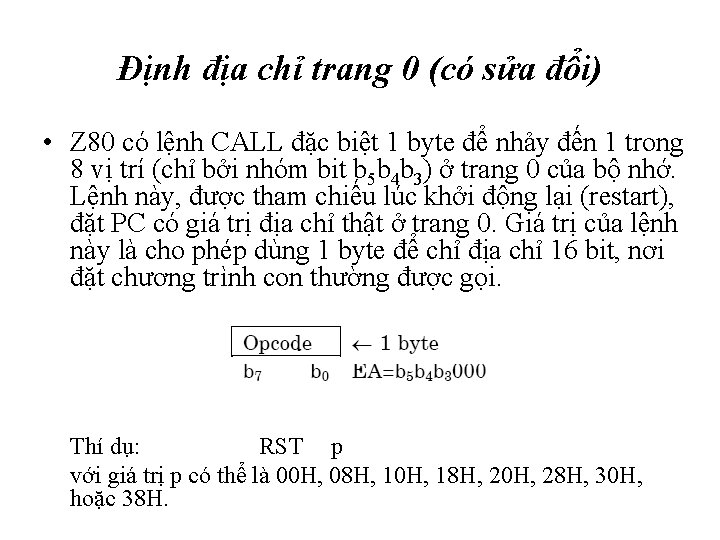

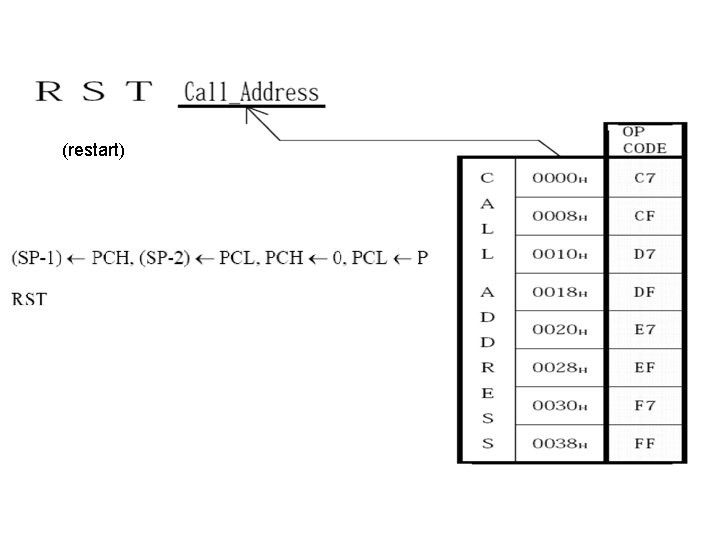

Định địa chỉ trang 0 (có sửa đổi) • Z 80 có lệnh CALL đặc biệt 1 byte để nhảy đến 1 trong 8 vị trí (chỉ bởi nhóm bit b 5 b 4 b 3) ở trang 0 của bộ nhớ. Lệnh này, được tham chiếu lúc khởi động lại (restart), đặt PC có giá trị địa chỉ thật ở trang 0. Giá trị của lệnh này là cho phép dùng 1 byte để chỉ địa chỉ 16 bit, nơi đặt chương trình con thường được gọi. Thí dụ: RST p với giá trị p có thể là 00 H, 08 H, 10 H, 18 H, 20 H, 28 H, 30 H, hoặc 38 H.

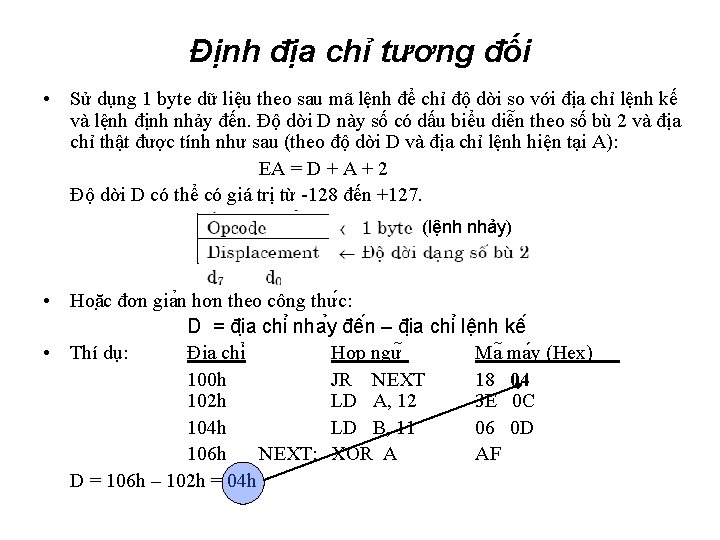

Định địa chỉ tương đối • Sử dụng 1 byte dữ liệu theo sau mã lệnh để chỉ độ dời so với địa chỉ lệnh kế và lệnh định nhảy đến. Độ dời D này số có dấu biểu diễn theo số bù 2 và địa chỉ thật được tính như sau (theo độ dời D và địa chỉ lệnh hiện tại A): EA = D + A + 2 Độ dời D có thể có giá trị từ -128 đến +127. (lệnh nhảy) • Hoă c đơn gia n hơn theo công thư c: D = đi a chi nha y đê n – đi a chi lê nh kê • Thí dụ: Đi a chi Hơ p ngư Ma ma y (Hex) 100 h JR NEXT 18 04 102 h LD A, 12 3 E 0 C 104 h LD B, 11 06 0 D 106 h NEXT: XOR A AF D = 106 h – 102 h = 04 h

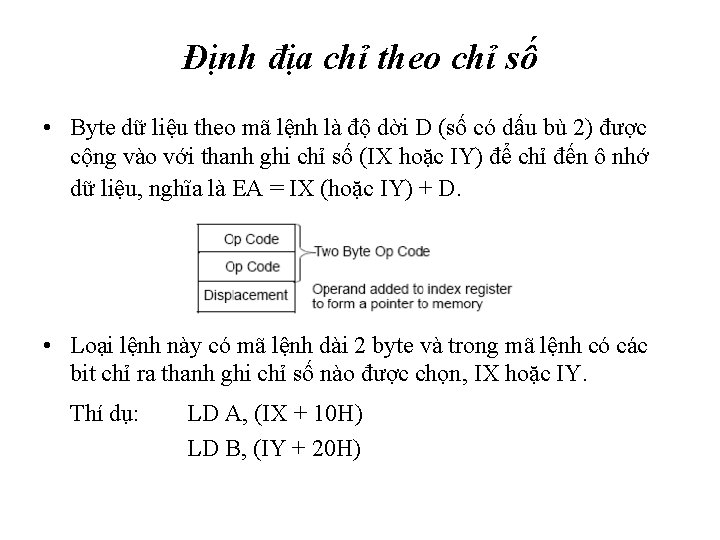

Định địa chỉ theo chỉ số • Byte dữ liệu theo mã lệnh là độ dời D (số có dấu bù 2) được cộng vào với thanh ghi chỉ số (IX hoặc IY) để chỉ đến ô nhớ dữ liệu, nghĩa là EA = IX (hoặc IY) + D. • Loại lệnh này có mã lệnh dài 2 byte và trong mã lệnh có các bit chỉ ra thanh ghi chỉ số nào được chọn, IX hoặc IY. Thí dụ: LD A, (IX + 10 H) LD B, (IY + 20 H)

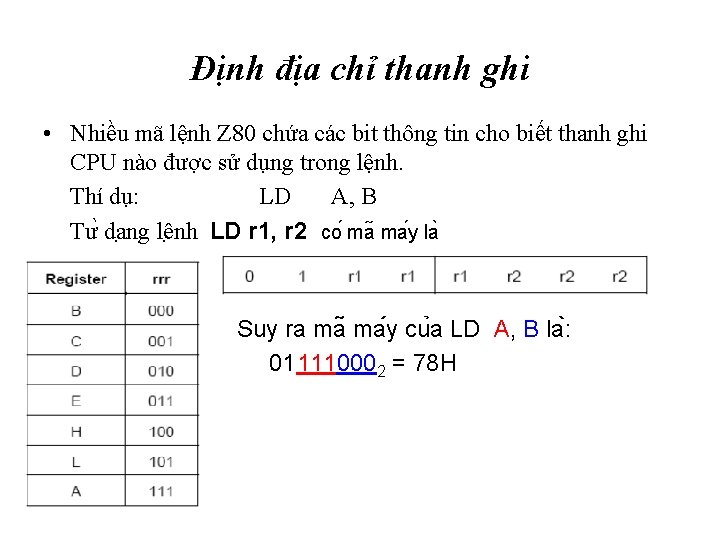

Định địa chỉ thanh ghi • Nhiều mã lệnh Z 80 chứa các bit thông tin cho biết thanh ghi CPU nào được sử dụng trong lệnh. Thí dụ: LD A, B Tư da ng lê nh LD r 1, r 2 co ma ma y la Suy ra ma ma y cu a LD A, B la : 011110002 = 78 H

Định địa chỉ hiểu ngầm • Mã lệnh cho biết 1 hay nhiều thanh ghi CPU chứa toán hạng. Thí dụ có một số lệnh hiểu ngâ m toán hạng để ở thanh ghi tích lũy A hoă c stack hoă c cờ carry C. Thí dụ: CPL AND 0 FH PUSH AF SCF ; A NOT(A) ; A A AND 0 FH ; câ t nô i dung că p thanh ghi AF va o stack ; CF 1 (đă t cờ C lên 1)

Định địa chỉ gián tiếp qua thanh ghi • Loại định địa chỉ này cho biết cặp thanh ghi 16 bit nào (như HL chẳng hạn) được dùng làm con trỏ chỉ tới vị trí ô nhớ. Thí dụ: LD LD A, (HL), 10 H

Định địa chỉ cho bit • Z 80 có nhiều lệnh đặt bit, xóa bit và kiểm tra bit. Các lệnh này cho phép bất kỳ vị trí bộ nhớ nào hoặc thanh ghi CPU sẽ được sử dụng cho các phép toán bit qua một trong 3 cách định địa chỉ (thanh ghi, gián tiếp qua thanh ghi và theo chỉ số) và 3 bit trong mã lệnh sẽ cho biết bit nào trong 8 bit được xử lý. Thí dụ: BIT SET RES 3, A 0, (HL) 7, (IX + 10 H) Chú ý là có những lệnh kết hợp một số cách địa chỉ chung trong một lệnh.

2. 7 TẬP LỆNH

• Tập lệnh Z 80 gồm có 158 lệnh, trong đó đã bao gồm 78 lệnh của 8080. Các lệnh được chia làm các nhóm chính sau: – Nạp 8 bit và nạp 16 bit – Hoán đổi, chuyển khối và tìm kiếm – Số học và logic 8 bit – Số học 16 bit – Số học đa dụng và điều khiển CPU – Xoay và dịch bit – Xử lý bit (Các phép toán trên bit) – Nhập và xuất – Nhảy, rẽ nhánh chương trình – Gọi chương trình và quay về chương trình gọi.

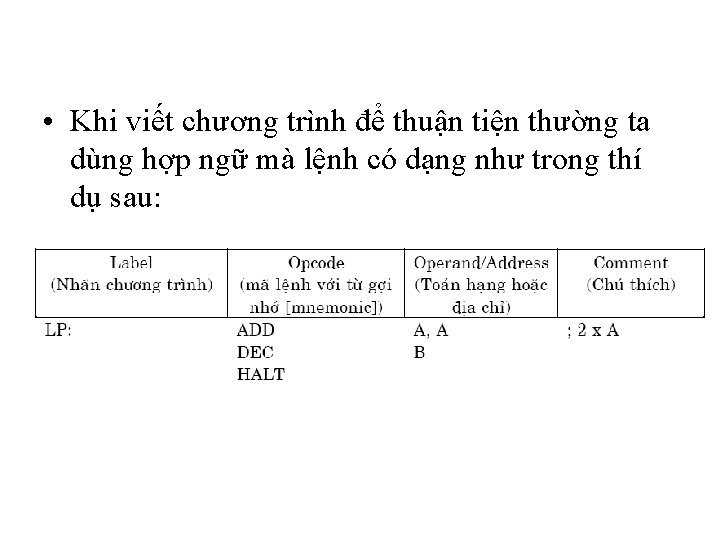

• Khi viết chương trình để thuận tiện thường ta dùng hợp ngữ mà lệnh có dạng như trong thí dụ sau:

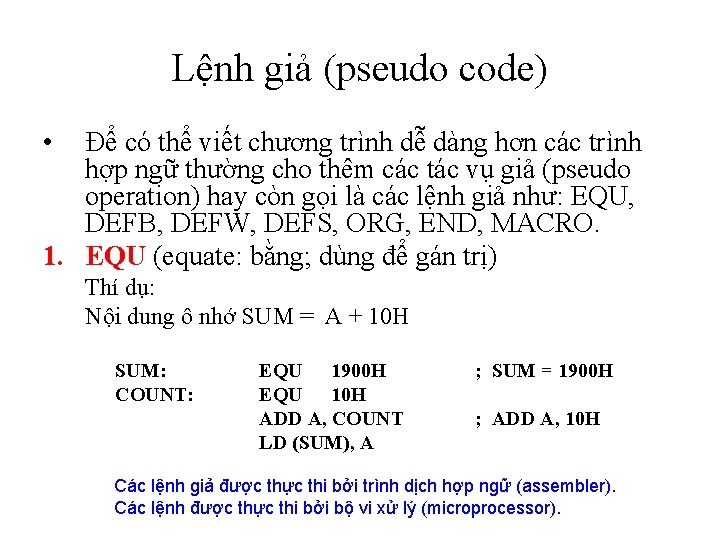

Lệnh giả (pseudo code) • Để có thể viết chương trình dễ dàng hơn các trình hợp ngữ thường cho thêm các tác vụ giả (pseudo operation) hay còn gọi là các lệnh giả như: EQU, DEFB, DEFW, DEFS, ORG, END, MACRO. 1. EQU (equate: bằng; dùng để gán trị) Thí dụ: Nội dung ô nhớ SUM = A + 10 H SUM: COUNT: EQU 1900 H EQU 10 H ADD A, COUNT LD (SUM), A ; SUM = 1900 H ; ADD A, 10 H Các lệnh giả được thực thi bởi trình dịch hợp ngữ (assembler). Các lệnh được thực thi bởi bộ vi xử lý (microprocessor).

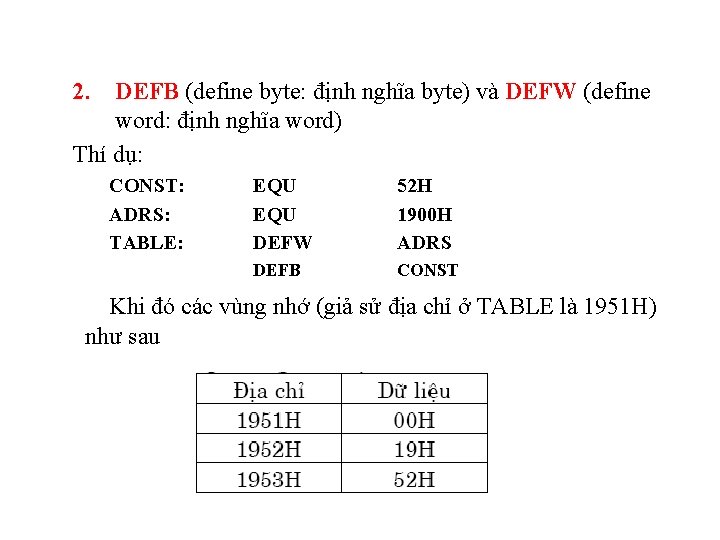

2. DEFB (define byte: định nghĩa byte) và DEFW (define word: định nghĩa word) Thí dụ: CONST: ADRS: TABLE: EQU DEFW 52 H 1900 H ADRS DEFB CONST Khi đó các vùng nhớ (giả sử địa chỉ ở TABLE là 1951 H) như sau

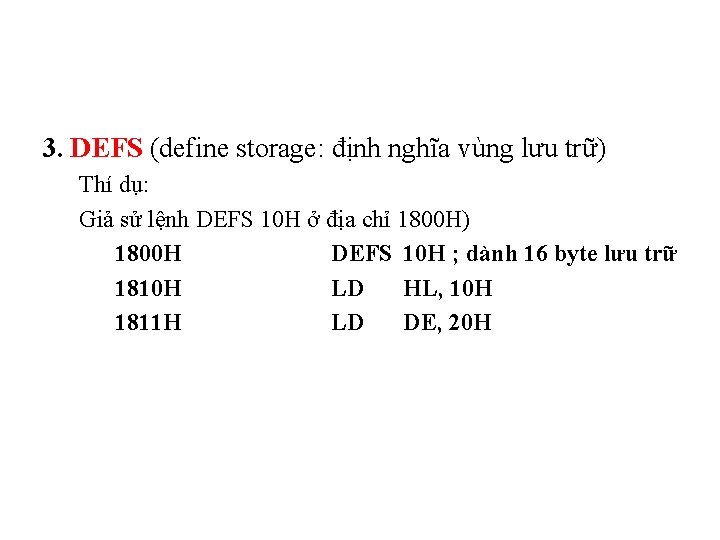

3. DEFS (define storage: định nghĩa vùng lưu trữ) Thí dụ: Giả sử lệnh DEFS 10 H ở địa chỉ 1800 H) 1800 H DEFS 10 H ; dành 16 byte lưu trữ 1810 H LD HL, 10 H 1811 H LD DE, 20 H

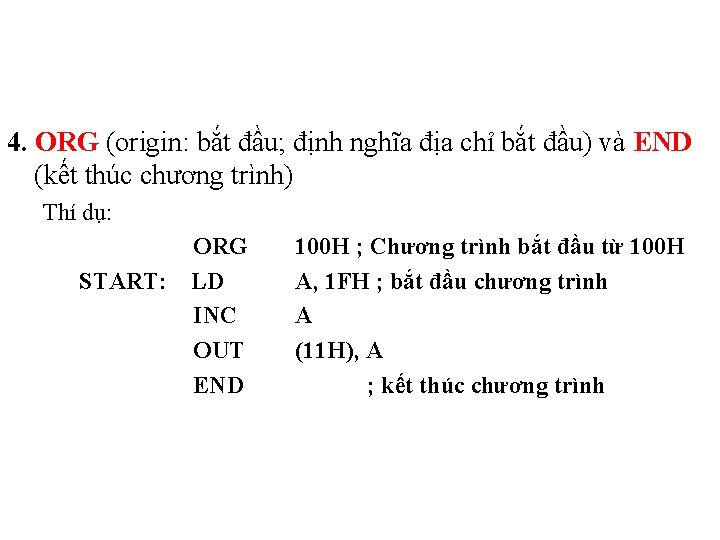

4. ORG (origin: bắt đầu; định nghĩa địa chỉ bắt đầu) và END (kết thúc chương trình) Thí dụ: START: ORG LD INC OUT END 100 H ; Chương trình bắt đầu từ 100 H A, 1 FH ; bắt đầu chương trình A (11 H), A ; kết thúc chương trình

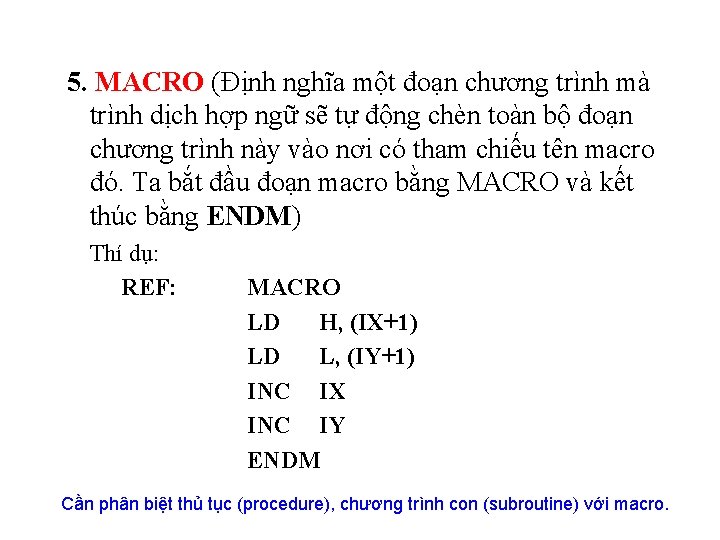

5. MACRO (Định nghĩa một đoạn chương trình mà trình dịch hợp ngữ sẽ tự động chèn toàn bộ đoạn chương trình này vào nơi có tham chiếu tên macro đó. Ta bắt đầu đoạn macro bằng MACRO và kết thúc bằng ENDM) Thí dụ: REF: MACRO LD H, (IX+1) LD L, (IY+1) INC IX INC IY ENDM Cần phân biệt thủ tục (procedure), chương trình con (subroutine) với macro.

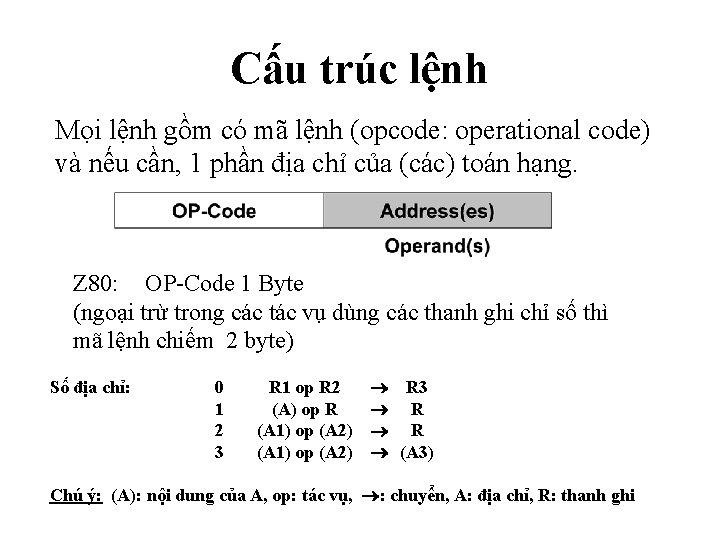

Cấu trúc lệnh Mọi lệnh gồm có mã lệnh (opcode: operational code) và nếu cần, 1 phần địa chỉ của (các) toán hạng. Z 80: OP-Code 1 Byte (ngoại trừ trong các tác vụ dùng các thanh ghi chỉ số thì mã lệnh chiếm 2 byte) Số địa chỉ: 0 1 2 3 R 1 op R 2 (A) op R (A 1) op (A 2) R 3 R R (A 3) Chú ý: (A): nội dung của A, op: tác vụ, : chuyển, A: địa chỉ, R: thanh ghi

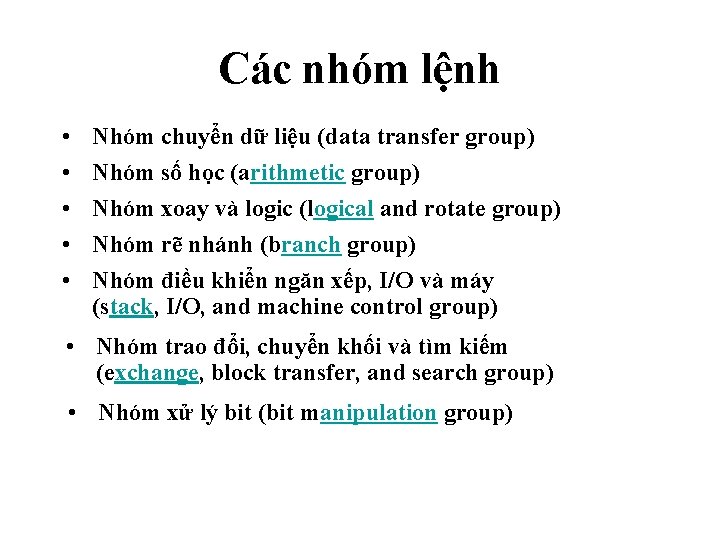

Các nhóm lệnh • • • Nhóm chuyển dữ liệu (data transfer group) Nhóm số học (arithmetic group) Nhóm xoay và logic (logical and rotate group) Nhóm rẽ nhánh (branch group) Nhóm điều khiển ngăn xếp, I/O và máy (stack, I/O, and machine control group) • Nhóm trao đổi, chuyển khối và tìm kiếm (exchange, block transfer, and search group) • Nhóm xử lý bit (bit manipulation group)

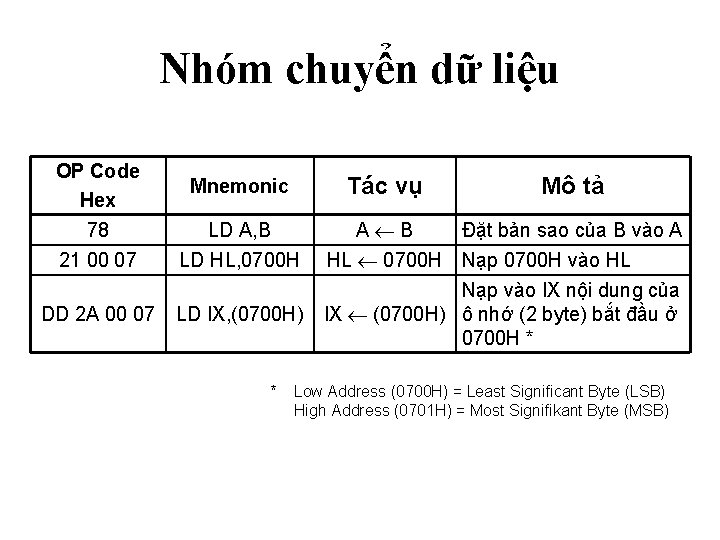

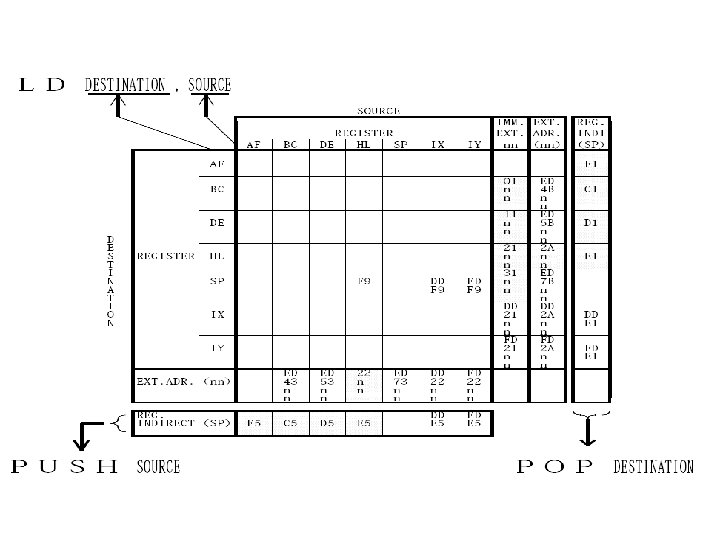

Nhóm chuyển dữ liệu OP Code Hex 78 Mnemonic Tác vụ Mô tả LD A, B A B Đặt bản sao của B vào A 21 00 07 LD HL, 0700 H DD 2 A 00 07 LD IX, (0700 H) * HL 0700 H Nạp 0700 H vào HL Nạp vào IX nội dung của IX (0700 H) ô nhớ (2 byte) bắt đầu ở 0700 H * Low Address (0700 H) = Least Significant Byte (LSB) High Address (0701 H) = Most Signifikant Byte (MSB)

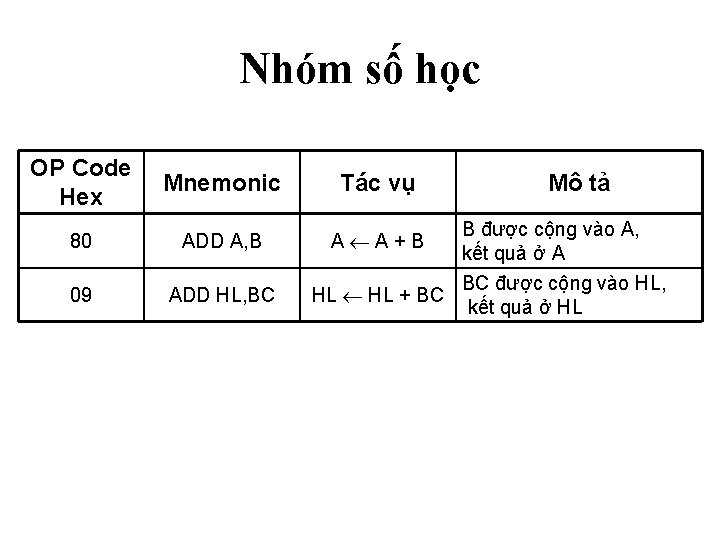

Nhóm số học OP Code Hex Mnemonic 80 ADD A, B 09 ADD HL, BC Tác vụ Mô tả B được cộng vào A, kết quả ở A BC được cộng vào HL, HL + BC kết quả ở HL A A+B

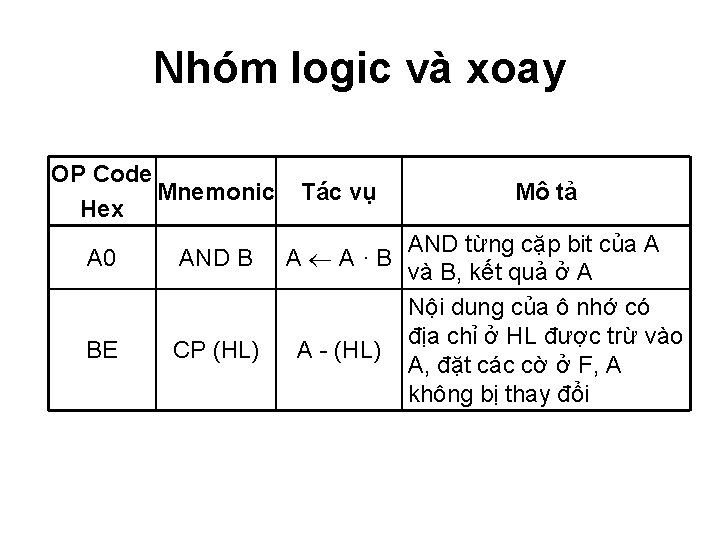

Nhóm logic và xoay OP Code Mnemonic Hex A 0 AND B BE CP (HL) Tác vụ Mô tả AND từng cặp bit của A A A·B và B, kết quả ở A Nội dung của ô nhớ có địa chỉ ở HL được trừ vào A - (HL) A, đặt các cờ ở F, A không bị thay đổi

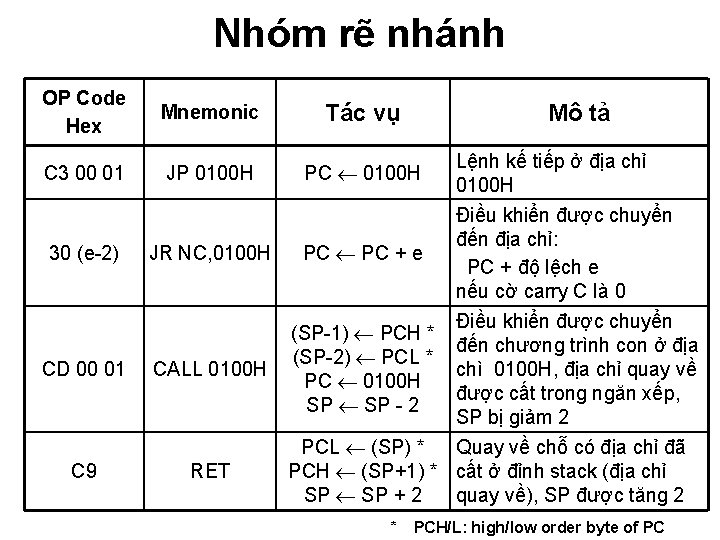

Nhóm rẽ nhánh OP Code Hex C 3 00 01 30 (e-2) CD 00 01 C 9 Mnemonic Tác vụ Mô tả Lệnh kế tiếp ở địa chỉ 0100 H Điều khiển được chuyển đến địa chỉ: JR NC, 0100 H PC + e PC + độ lệch e nếu cờ carry C là 0 Điều khiển được chuyển (SP-1) PCH * đến chương trình con ở địa (SP-2) PCL * CALL 0100 H chì 0100 H, địa chỉ quay về PC 0100 H được cất trong ngăn xếp, SP - 2 SP bị giảm 2 PCL (SP) * Quay về chỗ có địa chỉ đã RET PCH (SP+1) * cất ở đỉnh stack (địa chỉ SP + 2 quay về), SP được tăng 2 JP 0100 H PC 0100 H * PCH/L: high/low order byte of PC

(restart)

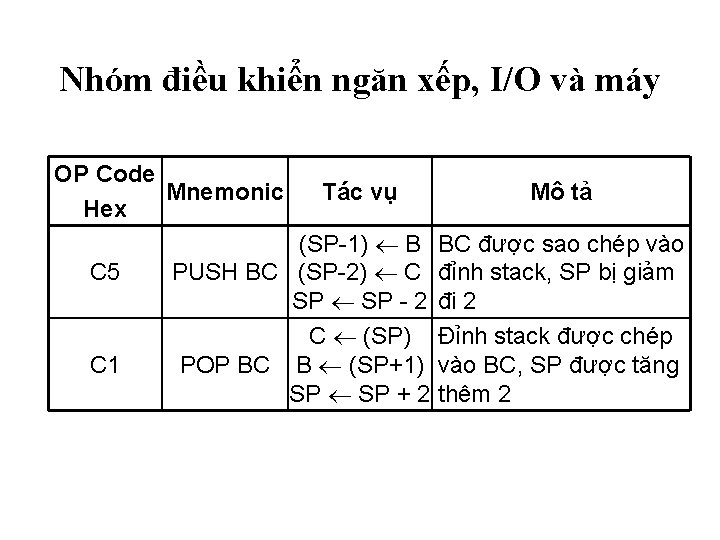

Nhóm điều khiển ngăn xếp, I/O và máy OP Code Mnemonic Hex C 5 C 1 Tác vụ (SP-1) B PUSH BC (SP-2) C SP - 2 C (SP) POP BC B (SP+1) SP + 2 Mô tả BC được sao chép vào đỉnh stack, SP bị giảm đi 2 Đỉnh stack được chép vào BC, SP được tăng thêm 2

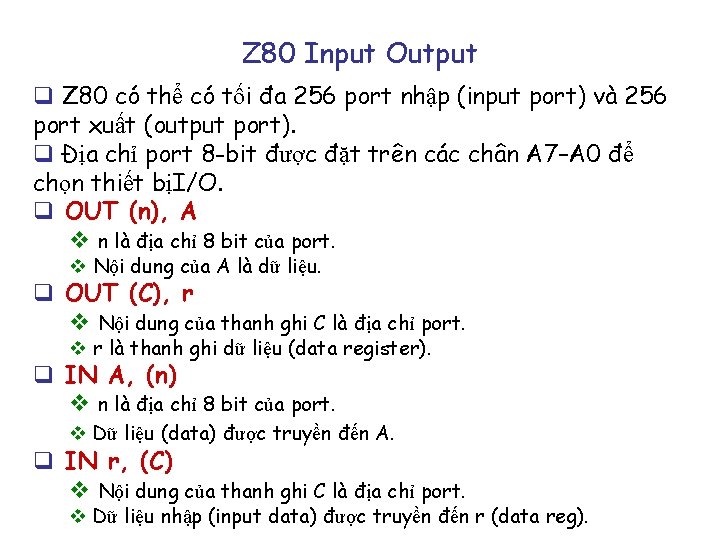

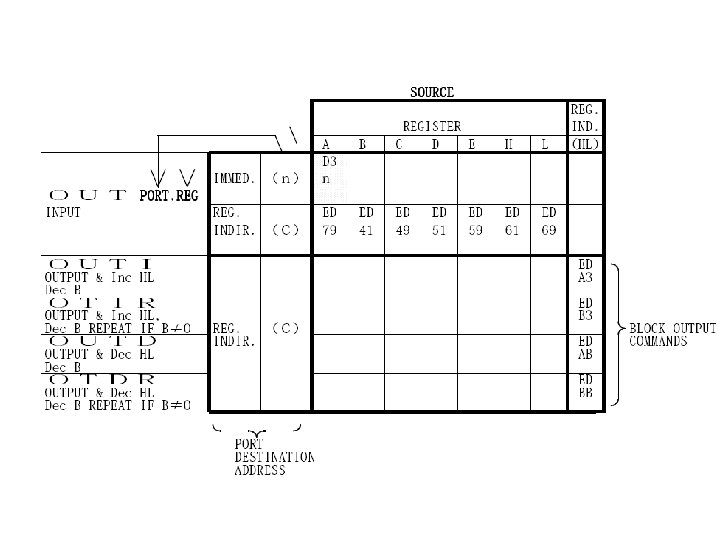

Z 80 Input Output q Z 80 có thể có tối đa 256 port nhập (input port) và 256 port xuất (output port). q Địa chỉ port 8 -bit được đặt trên các chân A 7–A 0 để chọn thiết bịI/O. q OUT (n), A v n là địa chỉ 8 bit của port. v Nội dung của A là dữ liệu. q OUT (C), r v Nội dung của thanh ghi C là địa chỉ port. v r là thanh ghi dữ liệu (data register). q IN A, (n) v n là địa chỉ 8 bit của port. v Dữ liệu (data) được truyền đến A. q IN r, (C) v Nội dung của thanh ghi C là địa chỉ port. v Dữ liệu nhập (input data) được truyền đến r (data reg).

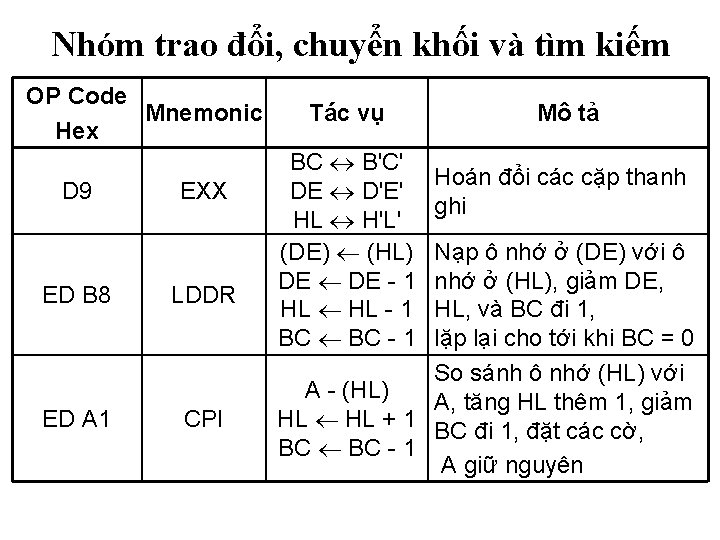

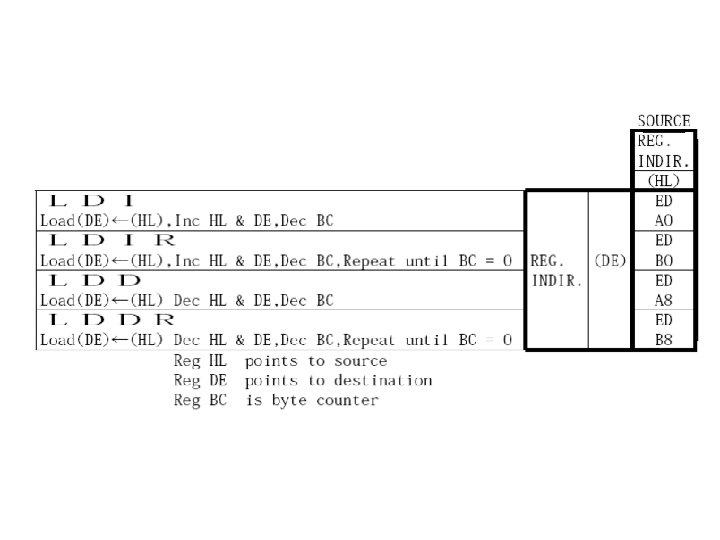

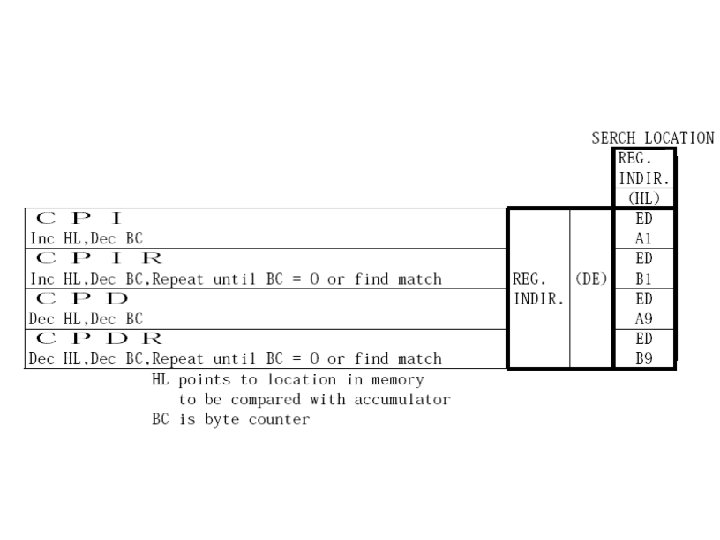

Nhóm trao đổi, chuyển khối và tìm kiếm OP Code Mnemonic Hex D 9 EXX ED B 8 LDDR ED A 1 CPI Tác vụ BC B'C' DE D'E' HL H'L' (DE) (HL) DE - 1 HL - 1 BC - 1 Mô tả Hoán đổi các cặp thanh ghi Nạp ô nhớ ở (DE) với ô nhớ ở (HL), giảm DE, HL, và BC đi 1, lặp lại cho tới khi BC = 0 So sánh ô nhớ (HL) với A - (HL) A, tăng HL thêm 1, giảm HL + 1 BC đi 1, đặt các cờ, BC - 1 A giữ nguyên

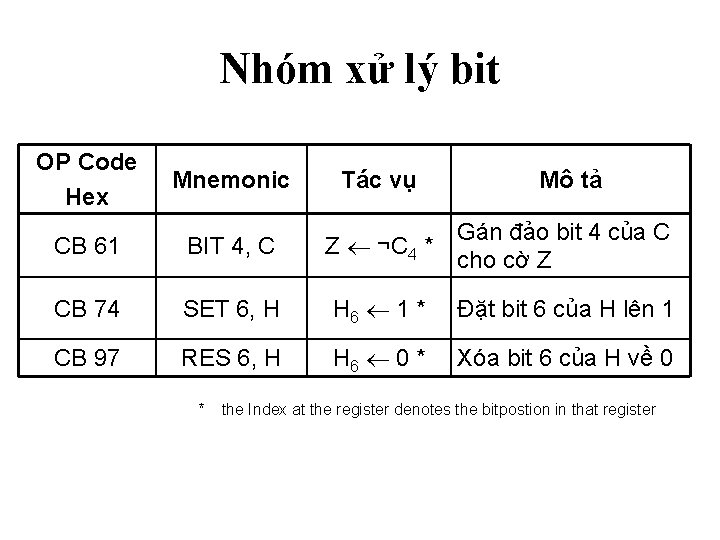

Nhóm xử lý bit OP Code Hex Mnemonic Tác vụ Mô tả CB 61 BIT 4, C Z ¬C 4 * Gán đảo bit 4 của C cho cờ Z CB 74 SET 6, H H 6 1 * Đặt bit 6 của H lên 1 CB 97 RES 6, H H 6 0 * Xóa bit 6 của H về 0 * the Index at the register denotes the bitpostion in that register

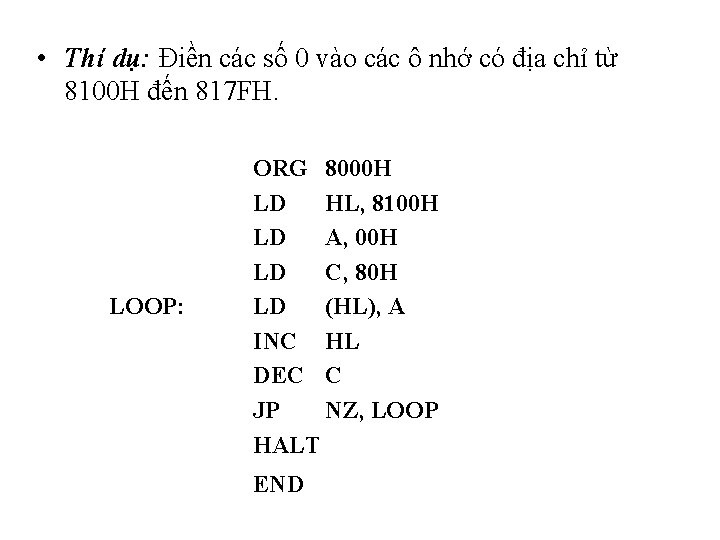

• Thí dụ: Điền các số 0 vào các ô nhớ có địa chỉ từ 8100 H đến 817 FH. LOOP: ORG 8000 H LD HL, 8100 H LD A, 00 H LD C, 80 H LD (HL), A INC HL DEC C JP NZ, LOOP HALT END

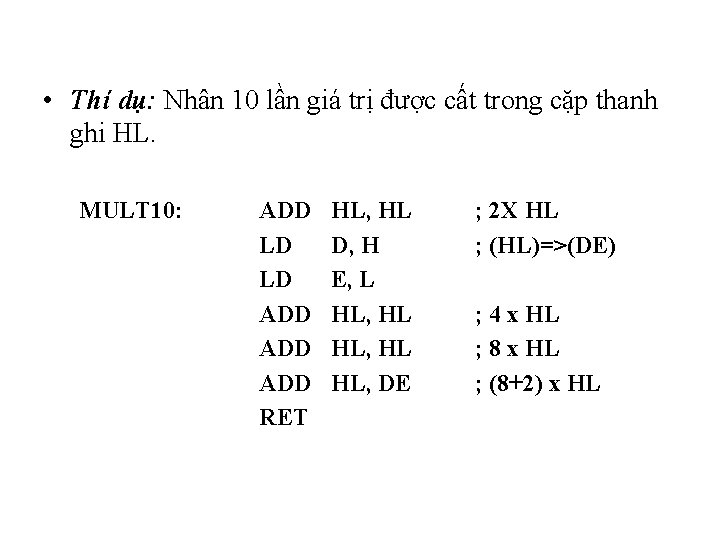

• Thí dụ: Nhân 10 lần giá trị được cất trong cặp thanh ghi HL. MULT 10: ADD LD LD ADD ADD RET HL, HL D, H E, L HL, HL HL, DE ; 2 X HL ; (HL)=>(DE) ; 4 x HL ; 8 x HL ; (8+2) x HL

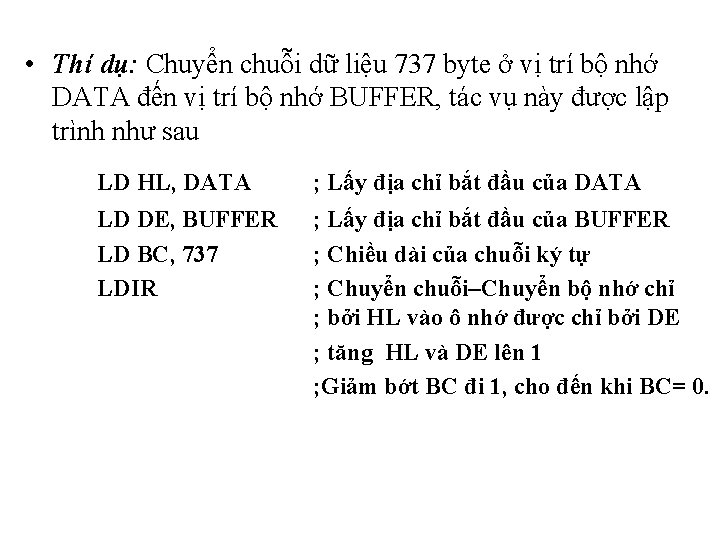

• Thí dụ: Chuyển chuỗi dữ liệu 737 byte ở vị trí bộ nhớ DATA đến vị trí bộ nhớ BUFFER, tác vụ này được lập trình như sau LD HL, DATA ; Lấy địa chỉ bắt đầu của DATA LD DE, BUFFER LD BC, 737 LDIR ; Lấy địa chỉ bắt đầu của BUFFER ; Chiều dài của chuỗi ký tự ; Chuyển chuỗi–Chuyển bộ nhớ chỉ ; bởi HL vào ô nhớ được chỉ bởi DE ; tăng HL và DE lên 1 ; Giảm bớt BC đi 1, cho đến khi BC= 0.

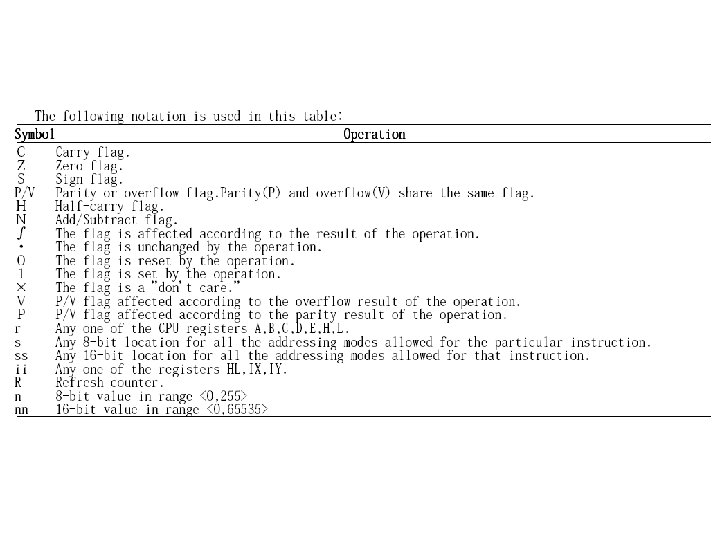

Tóm tắt tập lệnh Z 80

- Slides: 106