hardwarebasic163 com 8086 8088 v 6 5394 H

计算机硬件技术基础 hardwarebasic@163. com

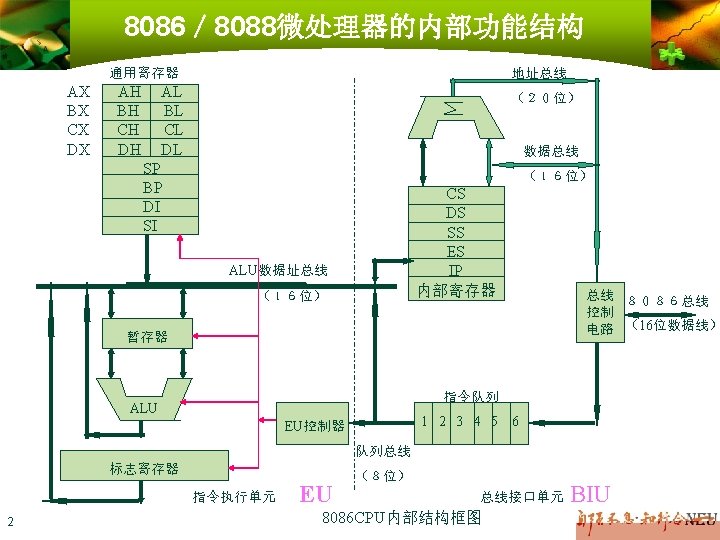

![8086/ 8088微处理器的编程结构 v 6个状态标志的判断 例: (5394 H) + (-777 FH) [5394 H]补 + [-777 8086/ 8088微处理器的编程结构 v 6个状态标志的判断 例: (5394 H) + (-777 FH) [5394 H]补 + [-777](http://slidetodoc.com/presentation_image_h2/d6f0c77cf52e16ccc6a13388287afd6c/image-13.jpg)

8086/ 8088微处理器的编程结构 v 6个状态标志的判断 例: (5394 H) + (-777 FH) [5394 H]补 + [-777 FH]补 -----------+ [-23 EBH]补 0101 0011 1001 0100 1000 0001 ----------------1101 1100 0001 0101 CF=0 AF=0 SF=1 ZF=0 PF=1 OF=0 0 – [23 EB]补 = [0010 0011 1110 1011] + 1 = 1101 1100 0001 0101 13

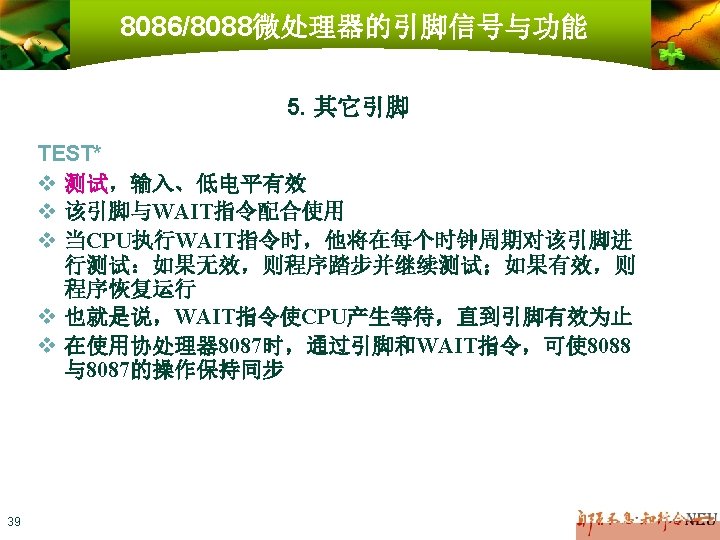

8086/8088微处理器的引脚信号与功能 GND AD 14 AD 13 AD 12 AD 11 AD 10 AD 9 AD 8 AD 7 AD 6 AD 5 AD 4 AD 3 AD 2 AD 1 AD 0 NMI INTR CLK GND 18 1 2 3 4 5 6 7 8 9 10 8086 11 12 CPU 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 VCC(+5 V) AD 15 A 16/S 3 A 17/S 4 A 18/S 5 A 19/S 6 BHE/S 7 MN/MX RD HOLD(RQ/GT 0 ) HLDA(RQ/GT 1 ) WR(LOCK) M/IO(S 2) DT/R(S 1) DEN(S 0) ALE(QS 1) INTA(QS 0) TEST READY RESET GND A 14 A 13 A 12 A 11 A 10 A 9 A 8 AD 7 AD 6 AD 5 AD 4 AD 3 AD 2 AD 1 AD 0 NMI INTR CLK GND 1 2 3 4 5 6 7 8 9 10 8088 11 12 CPU 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 通常在信号名称加 上划线(如:MX)或星号(如:MX*) 表示低电平有效 VCC(+5 V) A 15 A 16/S 3 A 17/S 4 A 18/S 5 A 19/S 6 SS 0(HIGH) MN/MX RD HOLD(RQ/GT 0 ) HLDA(RQ/GT 1 ) WR(LOCK) M/IO(S 2) DT/R(S 1) DEN(S 0) ALE(QS 1) INTA(QS 0) TEST READY RESET

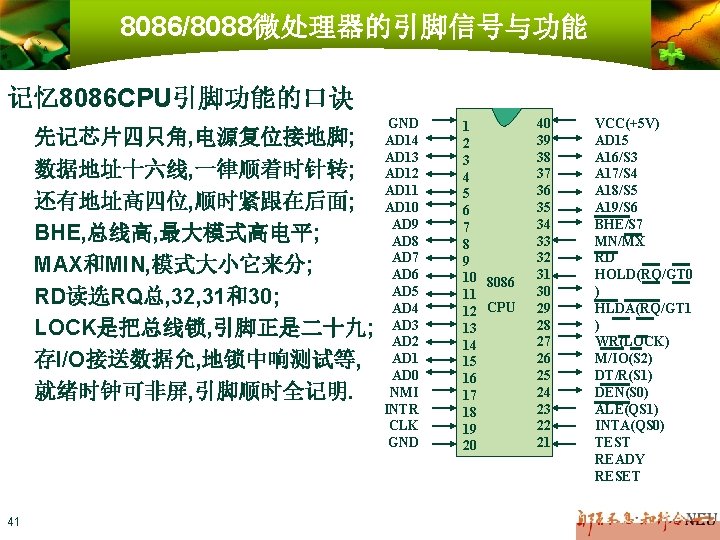

8086/8088微处理器的引脚信号与功能 记忆8086 CPU引脚功能的口诀 先记芯片四只角, 电源复位接地脚; 数据地址十六线, 一律顺着时针转; 还有地址高四位, 顺时紧跟在后面; BHE, 总线高, 最大模式高电平; MAX和MIN, 模式大小它来分; RD读选RQ总, 32, 31和30; LOCK是把总线锁, 引脚正是二十九; 存I/O接送数据允, 地锁中响测试等, 就绪时钟可非屏, 引脚顺时全记明. 41 GND AD 14 AD 13 AD 12 AD 11 AD 10 AD 9 AD 8 AD 7 AD 6 AD 5 AD 4 AD 3 AD 2 AD 1 AD 0 NMI INTR CLK GND 1 2 3 4 5 6 7 8 9 10 8086 11 12 CPU 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 VCC(+5 V) AD 15 A 16/S 3 A 17/S 4 A 18/S 5 A 19/S 6 BHE/S 7 MN/MX RD HOLD(RQ/GT 0 ) HLDA(RQ/GT 1 ) WR(LOCK) M/IO(S 2) DT/R(S 1) DEN(S 0) ALE(QS 1) INTA(QS 0) TEST READY RESET

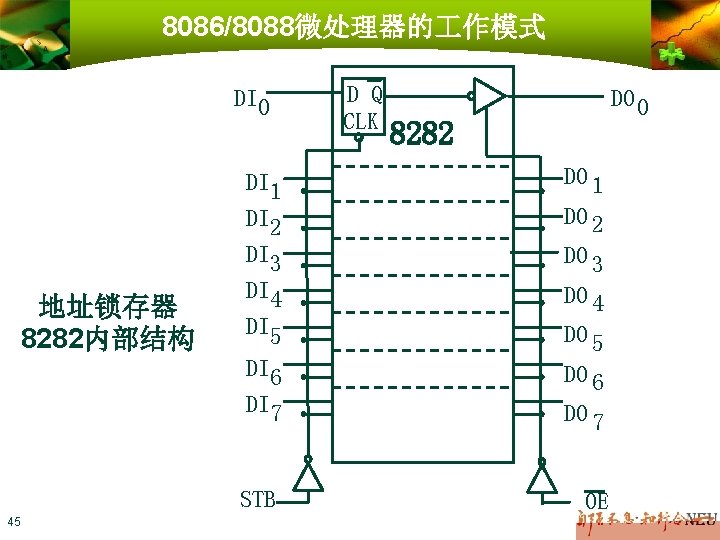

8086/8088微处理器的 作模式 8284 A CLK RESET READY S 6~S 3/A 19~A 16 AD 15~AD 0 ALE CLK RESET READY MN/MX +5 V VCC 8086 CPU GND 43 DEN DT/R IO/M WR RD HOLD HLDA INTR INTA NMI TEST 8086 在最小模式下的典型配置 地址锁存器 地址总线 8282(3片) STB 内 存 OE 数据收发器 OE 8286 T 数据总线 控制总线 I/O 接口

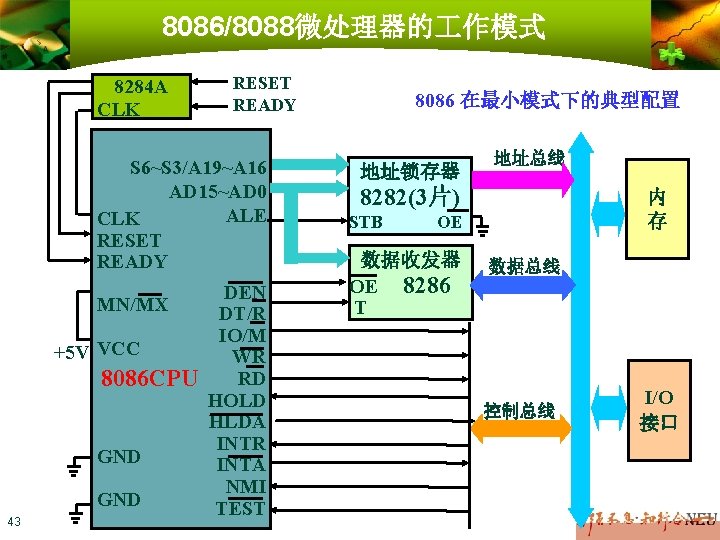

8086/8088微处理器的 作模式 DI 0 地址锁存器 8282内部结构 45 D Q CLK DO 0 8282 DI 1 DI 2 DO 1 DI 3 DI 4 DI 5 DO 3 DI 6 DI 7 DO 6 STB OE DO 2 DO 4 DO 5 DO 7

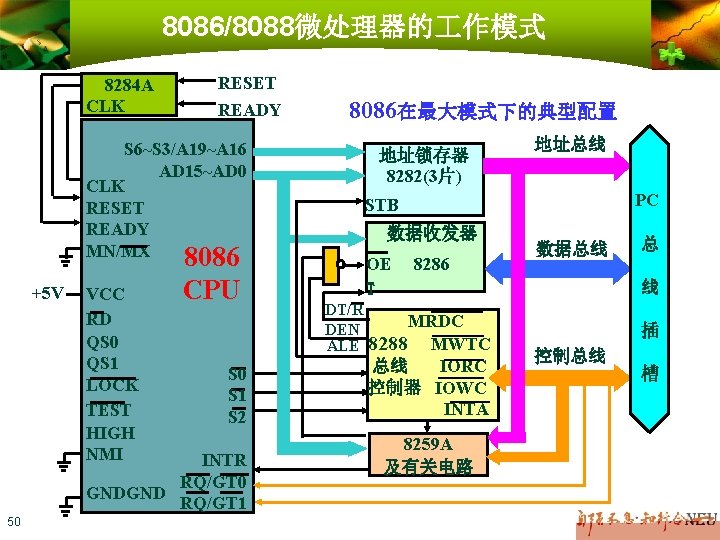

8086/8088微处理器的 作模式 8284 A CLK RESET READY S 6~S 3/A 19~A 16 AD 15~AD 0 CLK RESET READY MN/MX 8086 +5 V VCC RD QS 0 QS 1 LOCK TEST HIGH NMI CPU S 0 S 1 S 2 INTR RQ/GT 0 GNDGND RQ/GT 1 50 8086在最大模式下的典型配置 地址锁存器 8282(3片) 地址总线 PC STB 数据收发器 OE T 8286 DT/R MRDC DEN ALE 8288 MWTC 总线 IORC 控制器 IOWC INTA 8259 A 及有关电路 数据总线 总 线 插 控制总线 槽

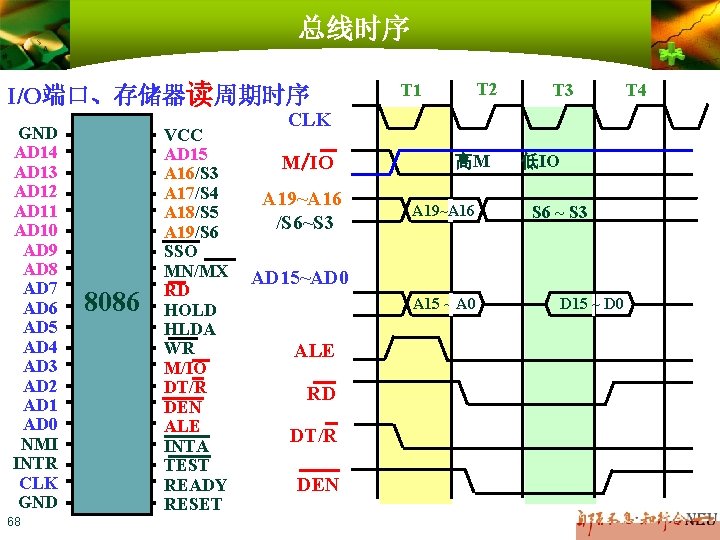

总线时序 I/O端口、存储器读周期时序 GND AD 14 AD 13 AD 12 AD 11 AD 10 AD 9 AD 8 AD 7 AD 6 AD 5 AD 4 AD 3 AD 2 AD 1 AD 0 NMI INTR CLK GND 68 8086 VCC AD 15 A 16/S 3 A 17/S 4 A 18/S 5 A 19/S 6 SSO MN/MX RD HOLD HLDA WR M/IO DT/R DEN ALE INTA TEST READY RESET T 2 T 1 T 3 CLK M/IO A 19~A 16 /S 6~S 3 高M A 19~A 16 低IO S 6 ~ S 3 AD 15~AD 0 A 15 ~ A 0 ALE RD DT/R DEN D 15 ~ D 0 T 4

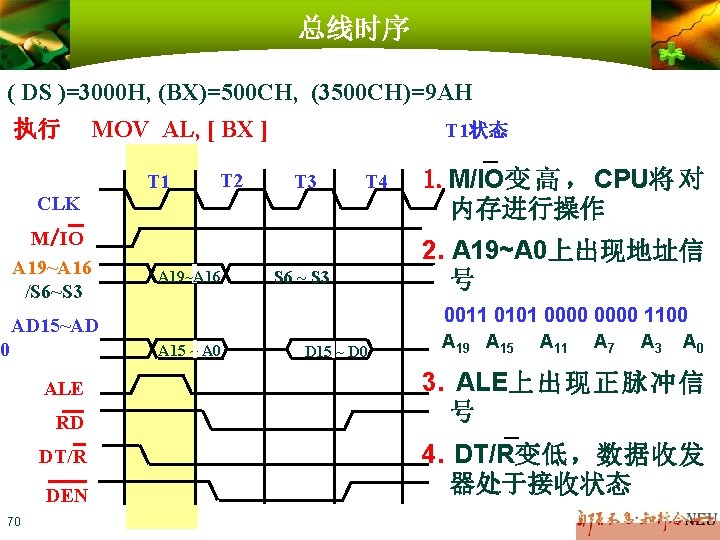

总线时序 ( DS )=3000 H, (BX)=500 CH, (3500 CH)=9 AH 执行 MOV AL, [ BX ] T 1 T 2 T 1状态 T 3 T 4 CLK M/IO A 19~A 16 /S 6~S 3 A 19~A 16 S 6 ~ S 3 A 15 ~ A 0 ALE RD DT/R DEN 70 2. A 19~A 0上出现地址信 号 0011 0101 0000 1100 AD 15~AD 0 1. M/IO变 高 , CPU将 对 内存进行操作 D 15 ~ D 0 A 19 A 15 A 11 A 7 A 3 A 0 3. ALE上出现正脉冲信 号 4. DT/R变低,数据收发 器处于接收状态

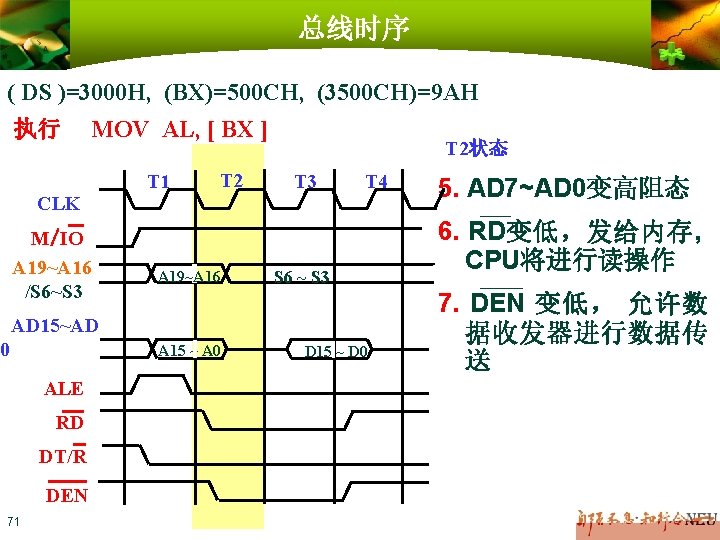

总线时序 ( DS )=3000 H, (BX)=500 CH, (3500 CH)=9 AH 执行 MOV AL, [ BX ] T 1 T 2状态 T 3 T 4 CLK M/IO A 19~A 16 /S 6~S 3 A 19~A 16 S 6 ~ S 3 AD 15~AD 0 A 15 ~ A 0 ALE RD DT/R DEN 71 D 15 ~ D 0 5. AD 7~AD 0变高阻态 6. RD变低,发给内存, CPU将进行读操作 7. DEN 变低, 允许数 据收发器进行数据传 送

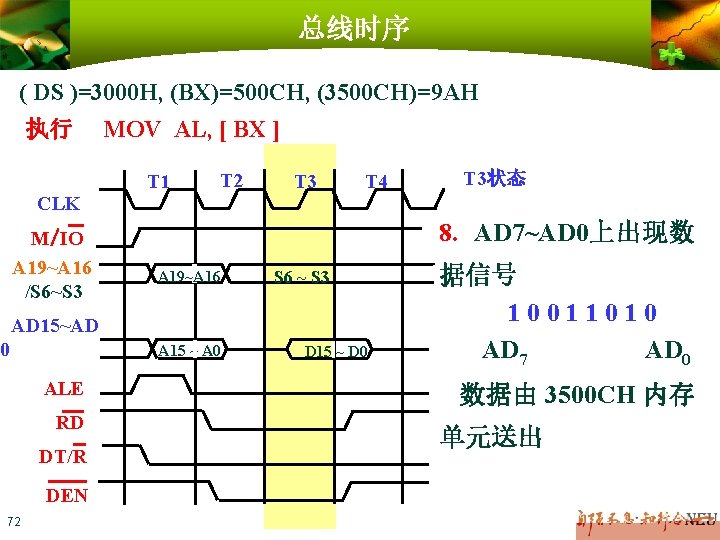

总线时序 ( DS )=3000 H, (BX)=500 CH, (3500 CH)=9 AH 执行 MOV AL, [ BX ] T 1 T 2 T 3 T 4 T 3状态 CLK M/IO A 19~A 16 /S 6~S 3 8. AD 7~AD 0上出现数 A 19~A 16 S 6 ~ S 3 AD 15~AD 0 A 15 ~ A 0 ALE RD DT/R DEN 72 D 15 ~ D 0 据信号 10011010 AD 7 AD 0 数据由 3500 CH 内存 单元送出

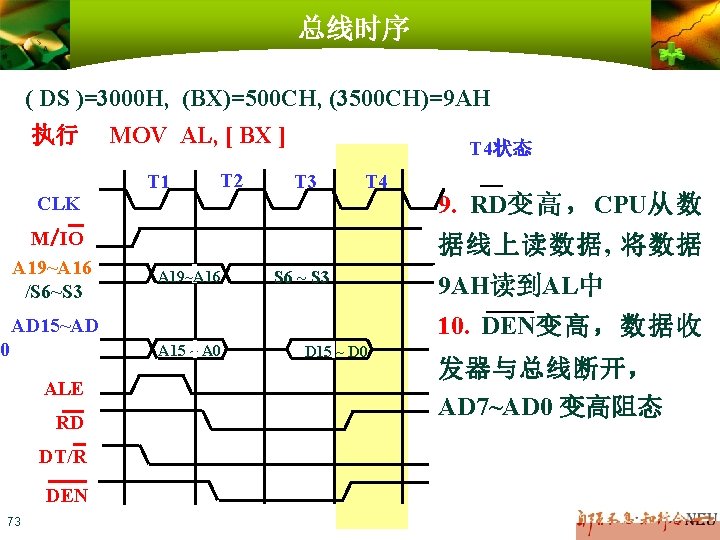

总线时序 ( DS )=3000 H, (BX)=500 CH, (3500 CH)=9 AH 执行 MOV AL, [ BX ] T 1 T 2 T 4状态 T 3 T 4 CLK M/IO A 19~A 16 /S 6~S 3 据线上读数据, 将数据 A 19~A 16 S 6 ~ S 3 A 15 ~ A 0 ALE RD DT/R DEN 73 9 AH读到AL中 10. DEN变高,数据收 AD 15~AD 0 9. RD变 高 , CPU从 数 D 15 ~ D 0 发器与总线断开, AD 7~AD 0 变高阻态

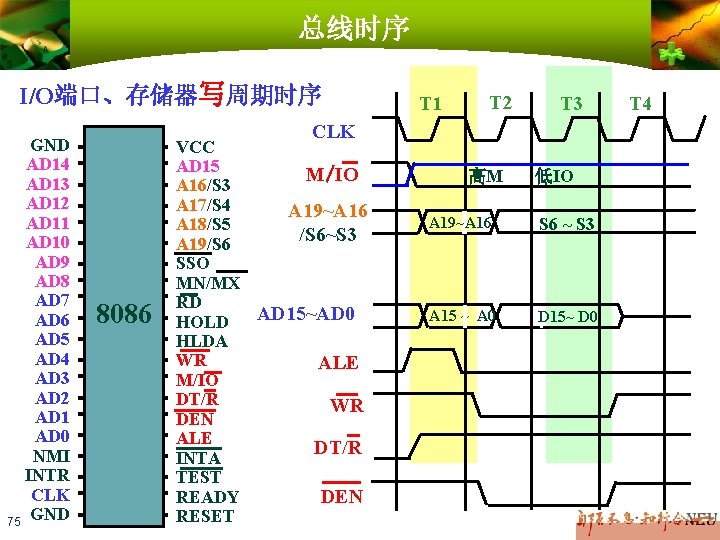

总线时序 I/O端口、存储器写周期时序 GND AD 14 AD 13 AD 12 AD 11 AD 10 AD 9 AD 8 AD 7 AD 6 AD 5 AD 4 AD 3 AD 2 AD 1 AD 0 NMI INTR CLK GND 75 T 1 T 2 T 3 CLK 8086 VCC AD 15 M/IO A 16/S 3 A 17/S 4 A 19~A 16 A 18/S 5 /S 6~S 3 A 19/S 6 SSO MN/MX RD AD 15~AD 0 HOLD HLDA WR ALE M/IO DT/R WR DEN ALE DT/R INTA TEST READY DEN RESET 高M 低IO A 19~A 16 S 6 ~ S 3 A 15 ~ A 0 D 15~ D 0 T 4

![总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ], 总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ],](http://slidetodoc.com/presentation_image_h2/d6f0c77cf52e16ccc6a13388287afd6c/image-75.jpg)

总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ], BL T 1 T 2 T 1状态 T 3 CLK M/IO A 19~A 16 /S 6~S 3 AD 15~AD 0 A 19~A 16 S 6 ~ S 3 A 15 ~ A 0 D 15~ D 0 T 4 1. M/IO变 高 , CPU将 对 内 存 进 行操作 2. A 19~A 0上出现地址信号 0110 0011 0000 1010 A 19 A 15 A 11 A 7 A 3 A 0 3. ALE上出现正脉冲信号 4. DT/R变高,数据收发器发送 ALE WR DT/R 77 DEN

![总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ], 总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ],](http://slidetodoc.com/presentation_image_h2/d6f0c77cf52e16ccc6a13388287afd6c/image-76.jpg)

总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ], BL T 1 T 2状态 T 3 CLK AD 15~AD 0 ALE WR DT/R 78 DEN 5. WR变低,发给内存, CPU 将进行读操作 6. DEN 变低,允许数据收发器 M/IO A 19~A 16 /S 6~S 3 T 4 A 19~A 16 S 6 ~ S 3 A 15 ~ A 0 D 15~ D 0 进行数据传送 7. AD 7~AD 0上出现数据信号 即BL的内容 0111 1100 AD 7 AD 0

![总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ], 总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ],](http://slidetodoc.com/presentation_image_h2/d6f0c77cf52e16ccc6a13388287afd6c/image-77.jpg)

总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ], BL T 1 T 2 T 3 T 4 T 3状态 CLK 8. 继续提供数据信号D 7~D 0 M/IO A 19~A 16 /S 6~S 3 AD 15~AD 0 ALE WR DT/R 79 DEN 9. 维持有关控制信号不变 A 19~A 16 S 6 ~ S 3 A 15 ~ A 0 D 15~ D 0

![总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ], 总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ],](http://slidetodoc.com/presentation_image_h2/d6f0c77cf52e16ccc6a13388287afd6c/image-78.jpg)

总线时序 ( DS )=6000 H, (DI)=300 AH, (BL)=7 CH 执行 MOV [ DI ], BL T 1 T 2 T 3 CLK AD 15~AD 0 ALE WR DT/R 80 DEN T 4状态 10. WR变高,将数据线上的 M/IO A 19~A 16 /S 6~S 3 T 4 数据 7 CH写到 6300 AH 内存单 A 19~A 16 S 6 ~ S 3 元中 11. DEN变高,数据收发器与 A 15 ~ A 0 D 15~ D 0 总线断开,AD 7~AD 0 变高阻 态

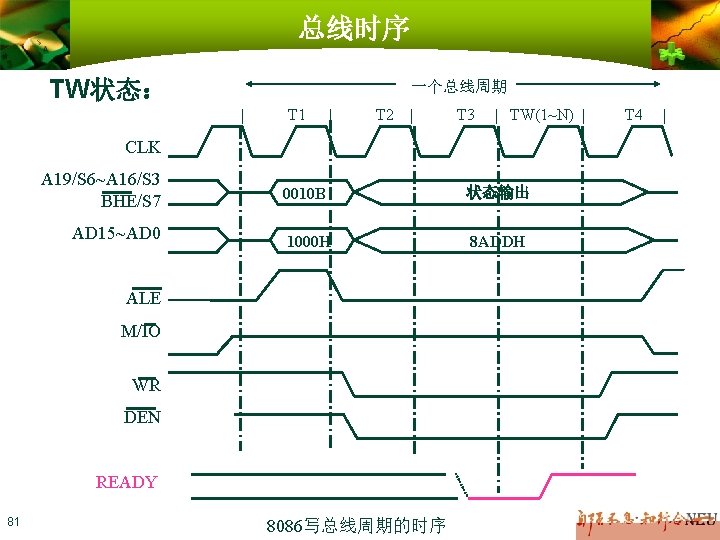

总线时序 TW状态: 一个总线周期 | T 1 | T 2 | T 3 | TW(1~N) | CLK A 19/S 6~A 16/S 3 BHE/S 7 AD 15~AD 0 0010 B 状态输出 1000 H 8 ADDH ALE M/IO WR DEN READY 81 8086写总线周期的时序 T 4 |

Pentium系列微处理器的发展 v Pentium 4微处理器 Pentium 4是第 1个基于Intel Net. Burst微结构的处理 器。2000年intel发布第 1代Pentium 4(Willamette), 2001年发布第 2代Pentium 4(Northwood),内部晶 体管数目增加到 4200万个,采用 478针引脚。 104

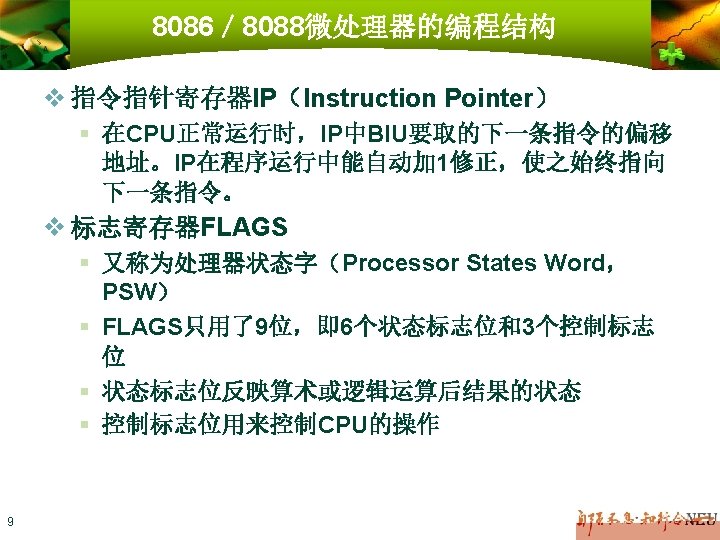

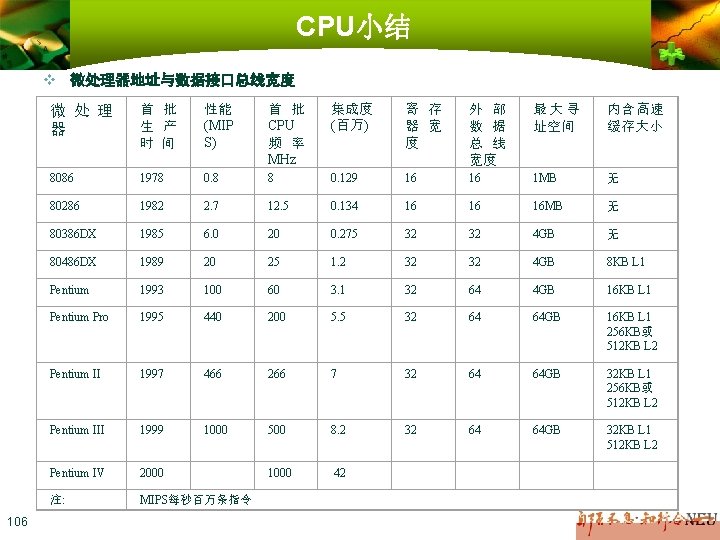

CPU小结 v 微处理器地址与数据接口总线宽度 106 微 处 理 器 首 批 生 产 时 间 性能 (MIP S) 首 批 CPU 频 率 MHz 集成度 (百万) 寄 存 器 宽 度 外 部 数 据 总 线 宽度 最大寻 址空间 内含高速 缓存大小 8086 1978 0. 8 8 0. 129 16 16 1 MB 无 80286 1982 2. 7 12. 5 0. 134 16 16 16 MB 无 80386 DX 1985 6. 0 20 0. 275 32 32 4 GB 无 80486 DX 1989 20 25 1. 2 32 32 4 GB 8 KB L 1 Pentium 1993 100 60 3. 1 32 64 4 GB 16 KB L 1 Pentium Pro 1995 440 200 5. 5 32 64 64 GB 16 KB L 1 256 KB或 512 KB L 2 Pentium II 1997 466 266 7 32 64 64 GB 32 KB L 1 256 KB或 512 KB L 2 Pentium III 1999 1000 500 8. 2 32 64 64 GB 32 KB L 1 512 KB L 2 Pentium IV 2000 1000 42 注: MIPS每秒百万条指令

- Slides: 104