HardwareBased Speculation cslabntua 2018 2019 1 CPI Pipeline

Υποθετική Εκτέλεση Εντολών (Hardware-Based Speculation) cslab@ntua 2018 -2019 1

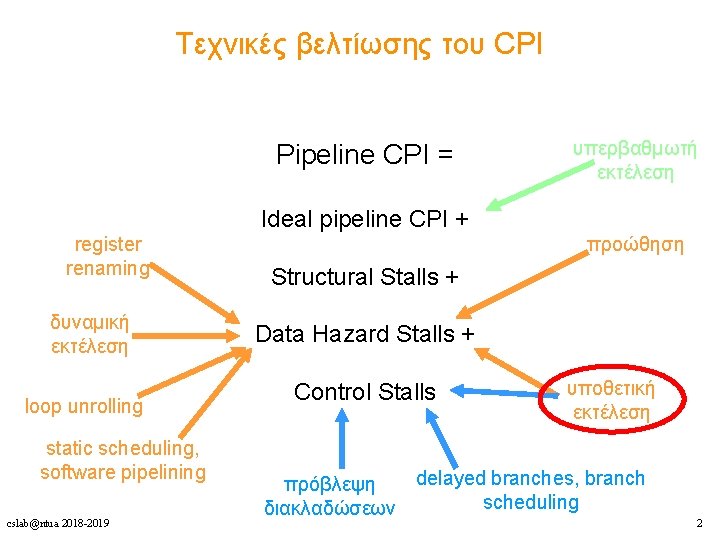

Τεχνικές βελτίωσης του CPI Pipeline CPI = υπερβαθμωτή εκτέλεση Ideal pipeline CPI + register renaming δυναμική εκτέλεση loop unrolling static scheduling, software pipelining cslab@ntua 2018 -2019 προώθηση Structural Stalls + Data Hazard Stalls + Control Stalls υποθετική εκτέλεση delayed branches, branch πρόβλεψη scheduling διακλαδώσεων 2

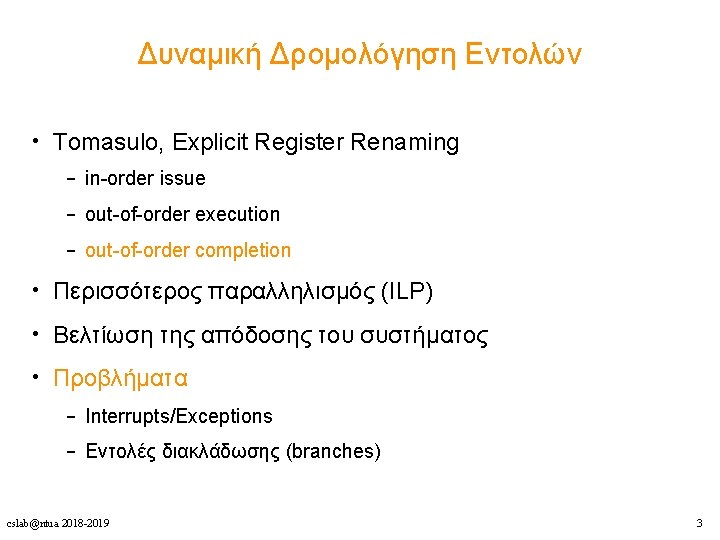

Network Interrupt Device Interrupt add r 1, r 2, r 3 subi r 4, r 1, #4 slli r 4, #2 C ts P ε. In de σ o γ Σώ νερ r M ε iso π Α erv p u S (!) lw r 2, 0(r 4) lw r 3, 4(r 4) add r 2, r 3 sw 8(r 4), r 2 cslab@ntua 2018 -2019 Επ α Us νέφ er ερ M εP od C e Μεγάλωσε priority Ενεργοποίηση Ints Σώσε registers lw r 1, 20(r 0) lw r 2, 0(r 1) addi r 3, r 0, #5 sw 0(r 1), r 3 Επανέφερε registers Καθάρισε Int Απενεργ. Ints Επανέφερε priority RTE 4

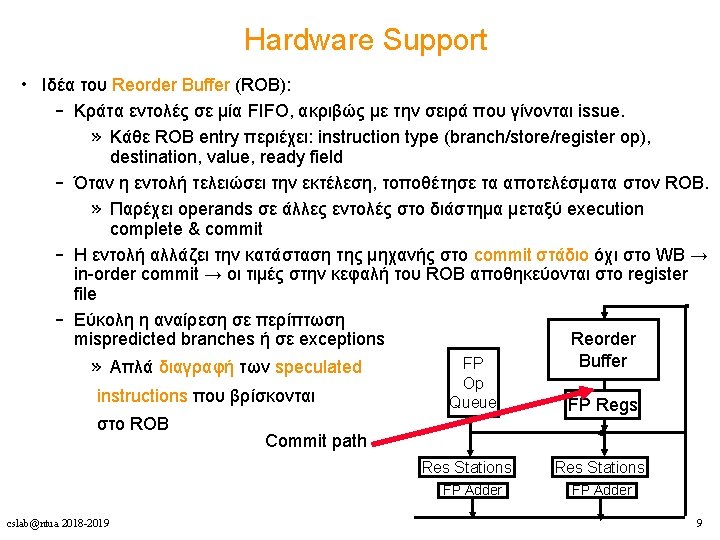

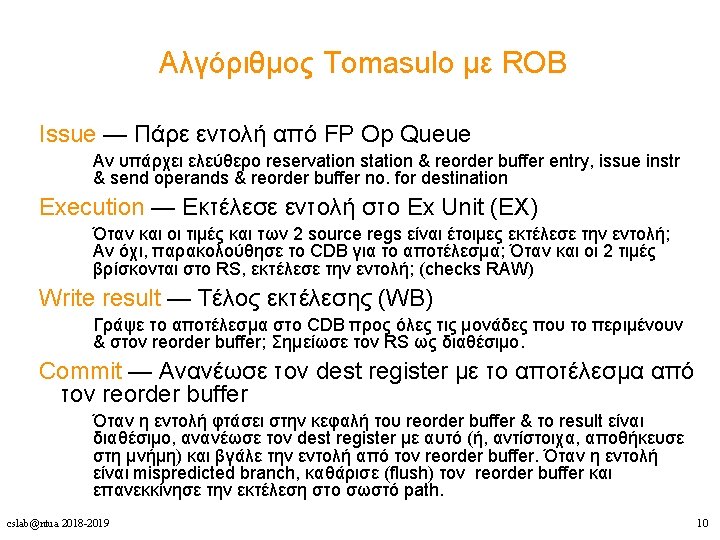

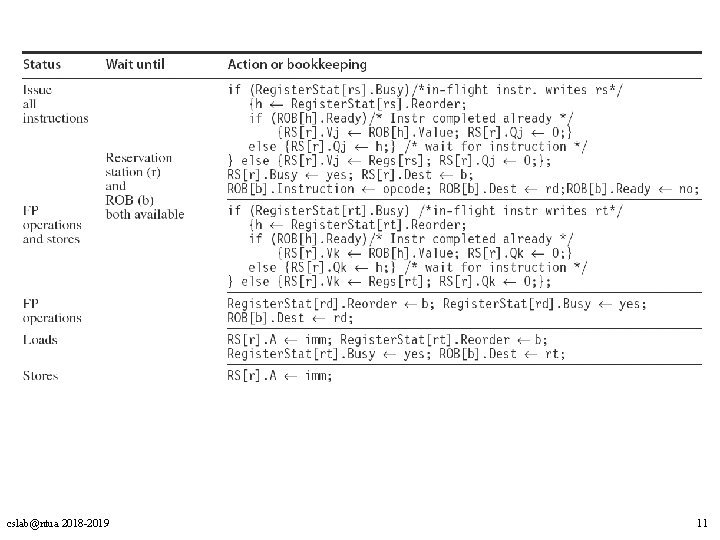

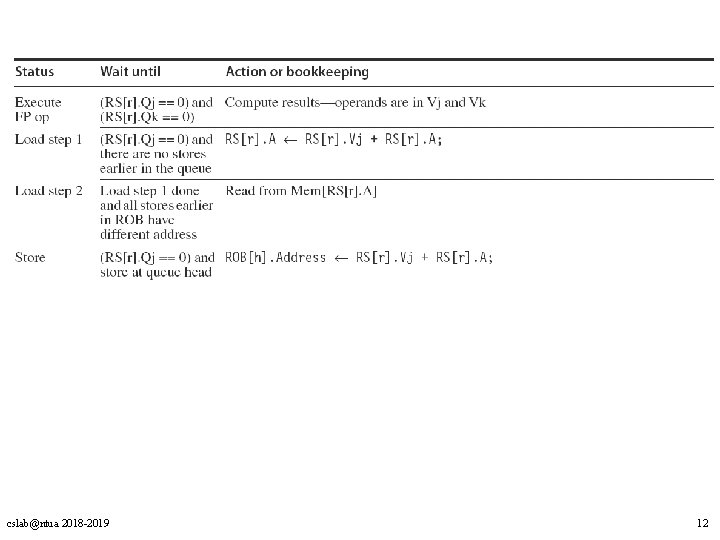

cslab@ntua 2018 -2019 11

cslab@ntua 2018 -2019 12

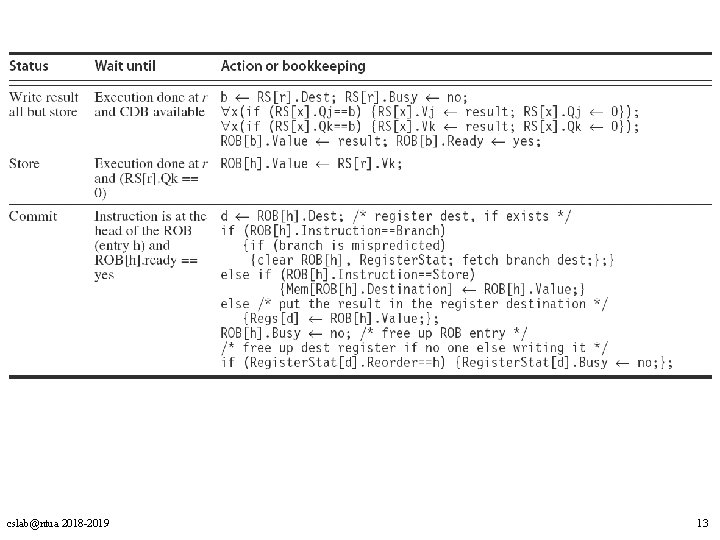

cslab@ntua 2018 -2019 13

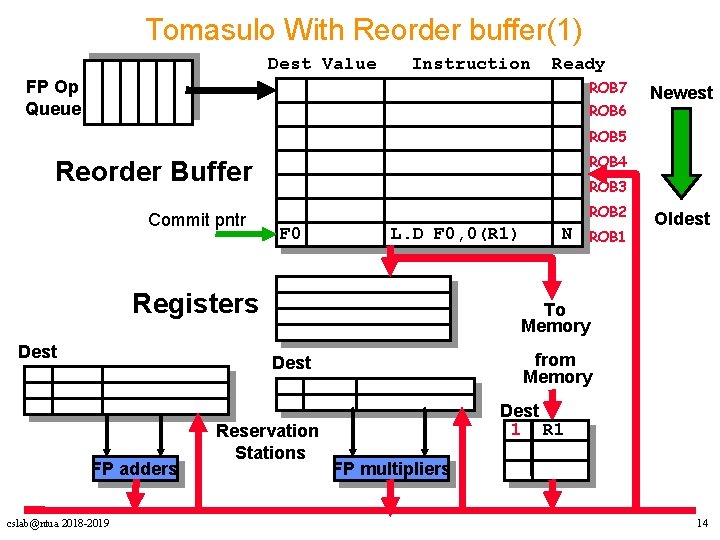

Tomasulo With Reorder buffer(1) Dest Value Instruction Ready FP Op Queue ROB 7 ROB 6 Newest ROB 5 ROB 4 Reorder Buffer Commit pntr ROB 3 ROB 2 F 0 L. D F 0, 0(R 1) Registers Dest cslab@ntua 2018 -2019 ROB 1 Oldest To Memory from Memory Dest FP adders N Reservation Stations Dest 1 R 1 FP multipliers 14

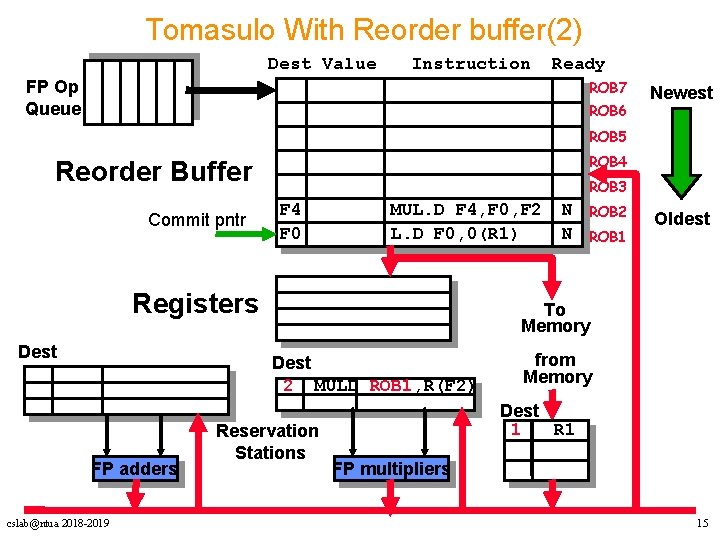

Tomasulo With Reorder buffer(2) Dest Value Instruction Ready FP Op Queue ROB 7 ROB 6 Newest ROB 5 ROB 4 Reorder Buffer Commit pntr ROB 3 F 4 F 0 MUL. D F 4, F 0, F 2 L. D F 0, 0(R 1) Registers Dest cslab@ntua 2018 -2019 ROB 2 ROB 1 Oldest To Memory Dest 2 MULD ROB 1, R(F 2) FP adders N N Reservation Stations from Memory Dest 1 R 1 FP multipliers 15

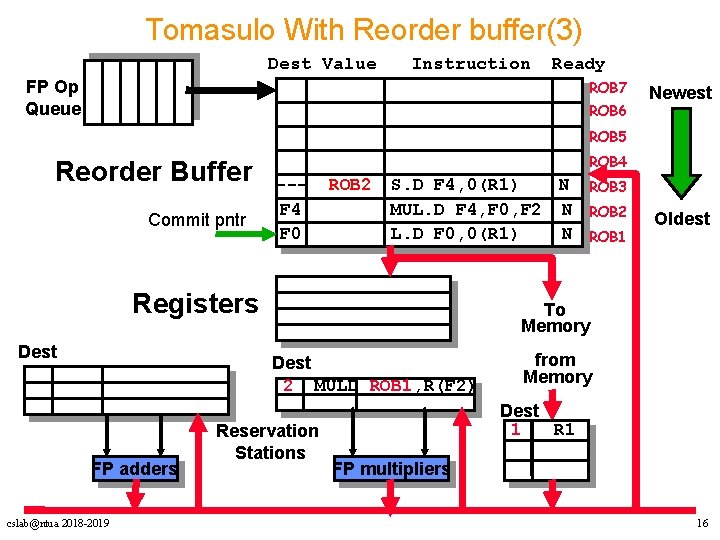

Tomasulo With Reorder buffer(3) Dest Value Instruction Ready FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer Commit pntr ROB 4 --F 4 F 0 ROB 2 S. D F 4, 0(R 1) N MUL. D F 4, F 0, F 2 N L. D F 0, 0(R 1) N Registers Dest cslab@ntua 2018 -2019 ROB 2 ROB 1 Oldest To Memory Dest 2 MULD ROB 1, R(F 2) FP adders ROB 3 Reservation Stations from Memory Dest 1 R 1 FP multipliers 16

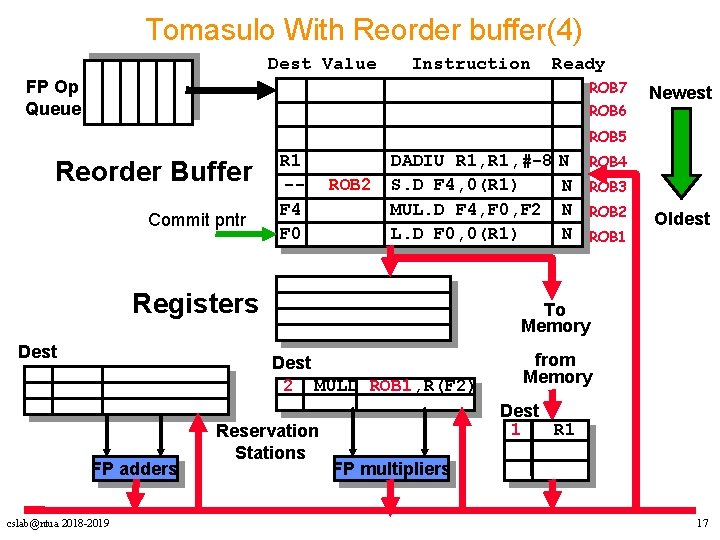

Tomasulo With Reorder buffer(4) Dest Value Instruction Ready FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer Commit pntr R 1 -F 4 F 0 ROB 2 DADIU R 1, #-8 S. D F 4, 0(R 1) MUL. D F 4, F 0, F 2 L. D F 0, 0(R 1) Registers Dest cslab@ntua 2018 -2019 ROB 4 ROB 3 ROB 2 ROB 1 Oldest To Memory Dest 2 MULD ROB 1, R(F 2) FP adders N N Reservation Stations from Memory Dest 1 R 1 FP multipliers 17

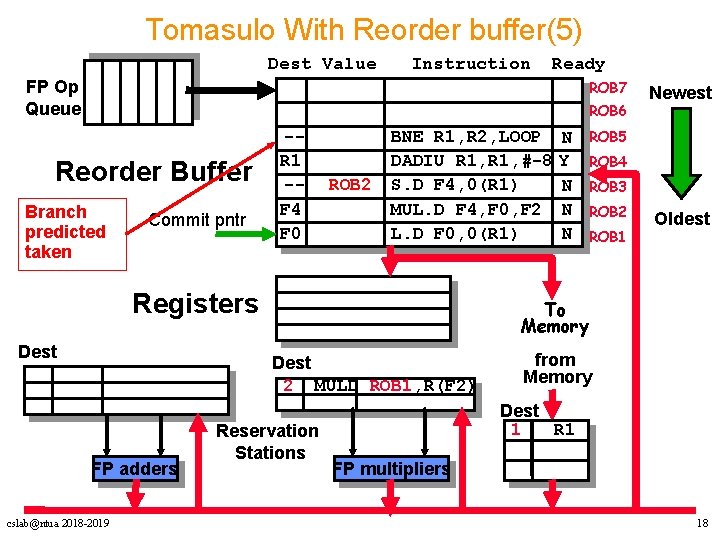

Tomasulo With Reorder buffer(5) Dest Value Instruction Ready FP Op Queue ROB 7 ROB 6 Reorder Buffer Branch predicted taken Commit pntr -R 1 -F 4 F 0 ROB 2 BNE R 1, R 2, LOOP DADIU R 1, #-8 S. D F 4, 0(R 1) MUL. D F 4, F 0, F 2 L. D F 0, 0(R 1) Registers Dest cslab@ntua 2018 -2019 ROB 5 ROB 4 ROB 3 ROB 2 ROB 1 Oldest To Memory Dest 2 MULD ROB 1, R(F 2) FP adders N Y N Newest Reservation Stations from Memory Dest 1 R 1 FP multipliers 18

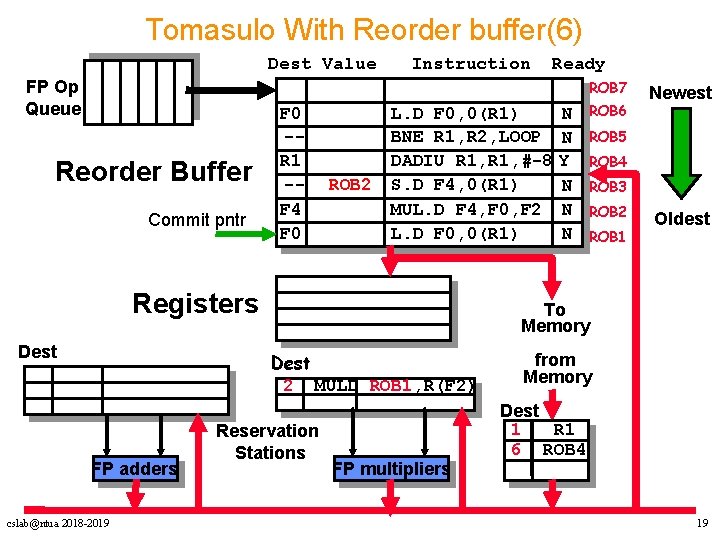

Tomasulo With Reorder buffer(6) Dest Value FP Op Queue Instruction Ready ROB 7 Reorder Buffer Commit pntr F 0 -R 1 -F 4 F 0 ROB 2 L. D F 0, 0(R 1) BNE R 1, R 2, LOOP DADIU R 1, #-8 S. D F 4, 0(R 1) MUL. D F 4, F 0, F 2 L. D F 0, 0(R 1) Registers Dest cslab@ntua 2018 -2019 ROB 6 ROB 5 ROB 4 ROB 3 ROB 2 ROB 1 Oldest To Memory Dest 2 MULD ROB 1, R(F 2) FP adders N N Y N Newest Reservation Stations FP multipliers from Memory Dest 1 R 1 6 ROB 4 19

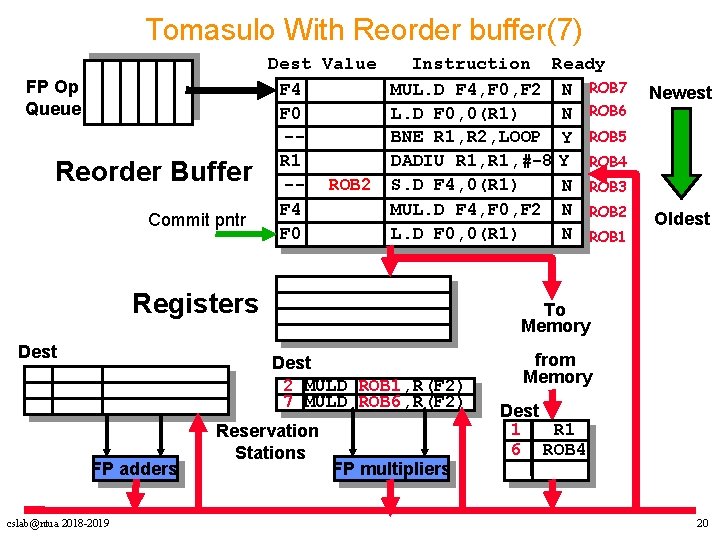

Tomasulo With Reorder buffer(7) FP Op Queue Reorder Buffer Commit pntr Dest Value Instruction Ready F 4 MUL. D F 4, F 0, F 2 N ROB 7 F 0 L. D F 0, 0(R 1) N ROB 6 -BNE R 1, R 2, LOOP Y ROB 5 R 1 DADIU R 1, #-8 Y ROB 4 -- ROB 2 S. D F 4, 0(R 1) N ROB 3 F 4 MUL. D F 4, F 0, F 2 N ROB 2 F 0 L. D F 0, 0(R 1) N ROB 1 Registers Dest cslab@ntua 2018 -2019 Oldest To Memory Dest 2 MULD ROB 1, R(F 2) 7 MULD ROB 6, R(F 2) FP adders Newest Reservation Stations FP multipliers from Memory Dest 1 R 1 6 ROB 4 20

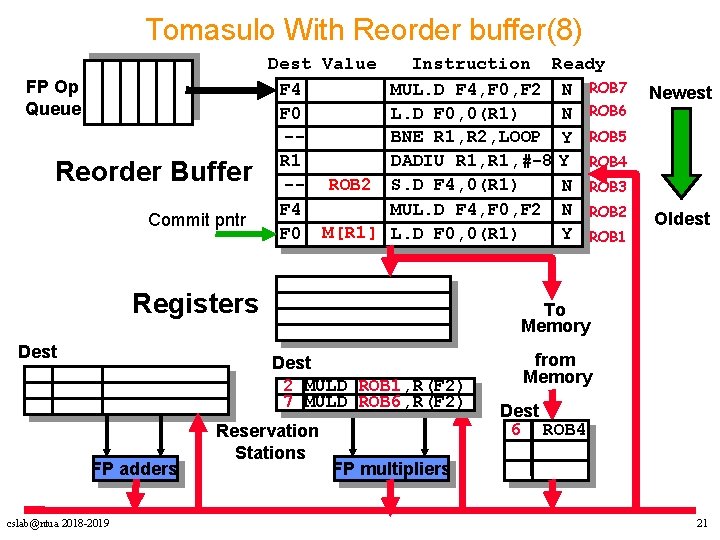

Tomasulo With Reorder buffer(8) FP Op Queue Reorder Buffer Commit pntr Dest Value Instruction Ready F 4 MUL. D F 4, F 0, F 2 N ROB 7 F 0 L. D F 0, 0(R 1) N ROB 6 -BNE R 1, R 2, LOOP Y ROB 5 R 1 DADIU R 1, #-8 Y ROB 4 -- ROB 2 S. D F 4, 0(R 1) N ROB 3 F 4 MUL. D F 4, F 0, F 2 N ROB 2 F 0 M[R 1] L. D F 0, 0(R 1) Y ROB 1 Registers Dest cslab@ntua 2018 -2019 Oldest To Memory Dest 22 MULDROB 1, R(F 2) 7 MULD ROB 6, R(F 2) FP adders Newest Reservation Stations from Memory Dest 6 ROB 4 FP multipliers 21

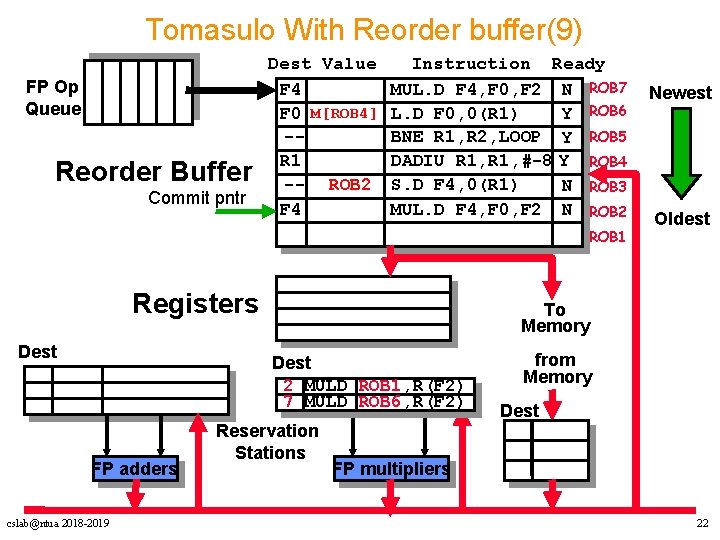

Tomasulo With Reorder buffer(9) FP Op Queue Reorder Buffer Commit pntr Dest Value F 4 F 0 M[ROB 4] -R 1 -- ROB 2 F 4 Instruction Ready MUL. D F 4, F 0, F 2 N ROB 7 L. D F 0, 0(R 1) Y ROB 6 BNE R 1, R 2, LOOP Y ROB 5 DADIU R 1, #-8 Y ROB 4 S. D F 4, 0(R 1) N ROB 3 MUL. D F 4, F 0, F 2 N ROB 2 ROB 1 Registers Dest cslab@ntua 2018 -2019 Oldest To Memory Dest 2 MULDROB 1, R(F 2) 7 MULD ROB 6, R(F 2) FP adders Newest Reservation Stations from Memory Dest FP multipliers 22

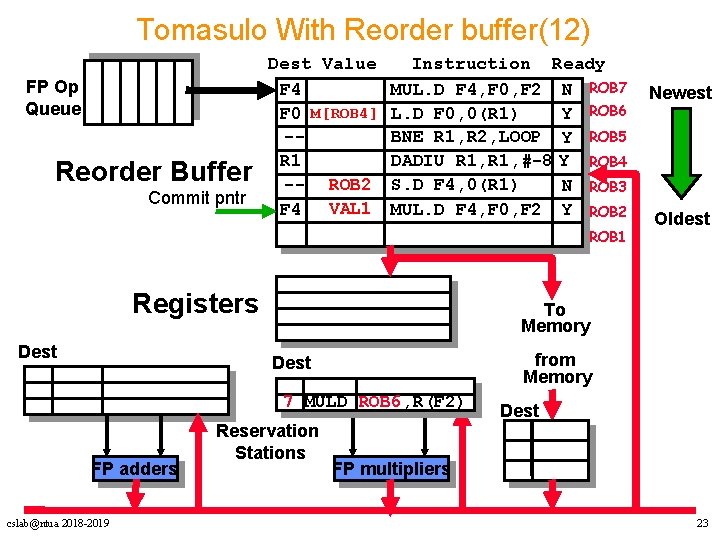

Tomasulo With Reorder buffer(12) FP Op Queue Reorder Buffer Commit pntr Dest Value F 4 F 0 M[ROB 4] -R 1 -- ROB 2 F 4 VAL 1 Instruction Ready MUL. D F 4, F 0, F 2 N ROB 7 L. D F 0, 0(R 1) Y ROB 6 BNE R 1, R 2, LOOP Y ROB 5 DADIU R 1, #-8 Y ROB 4 S. D F 4, 0(R 1) N ROB 3 MUL. D F 4, F 0, F 2 Y ROB 2 ROB 1 Registers Dest cslab@ntua 2018 -2019 Oldest To Memory Dest 2 MULD ROB 1, R(F 2) 7 MULD ROB 6, R(F 2) FP adders Newest Reservation Stations from Memory Dest FP multipliers 23

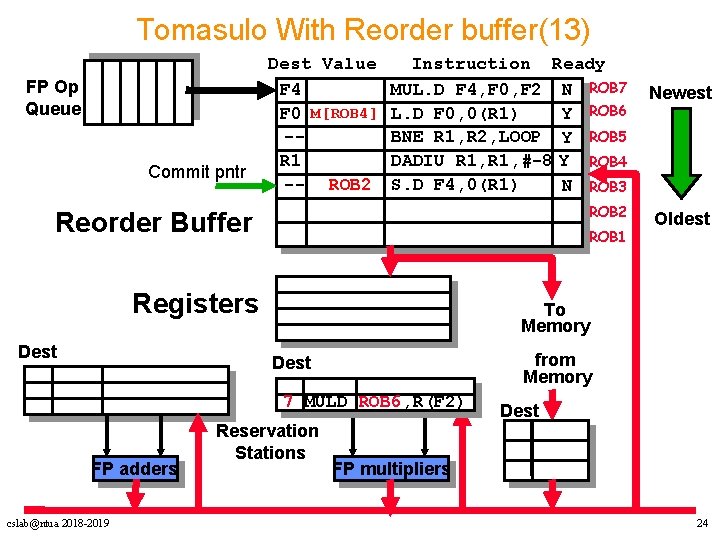

Tomasulo With Reorder buffer(13) FP Op Queue Commit pntr Dest Value F 4 F 0 M[ROB 4] -R 1 -- ROB 2 Instruction Ready MUL. D F 4, F 0, F 2 N ROB 7 L. D F 0, 0(R 1) Y ROB 6 BNE R 1, R 2, LOOP Y ROB 5 DADIU R 1, #-8 Y ROB 4 S. D F 4, 0(R 1) N ROB 3 ROB 2 Reorder Buffer ROB 1 Registers Dest cslab@ntua 2018 -2019 Oldest To Memory Dest 2 MULD ROB 1, R(F 2) 7 MULD ROB 6, R(F 2) FP adders Newest Reservation Stations from Memory Dest FP multipliers 24

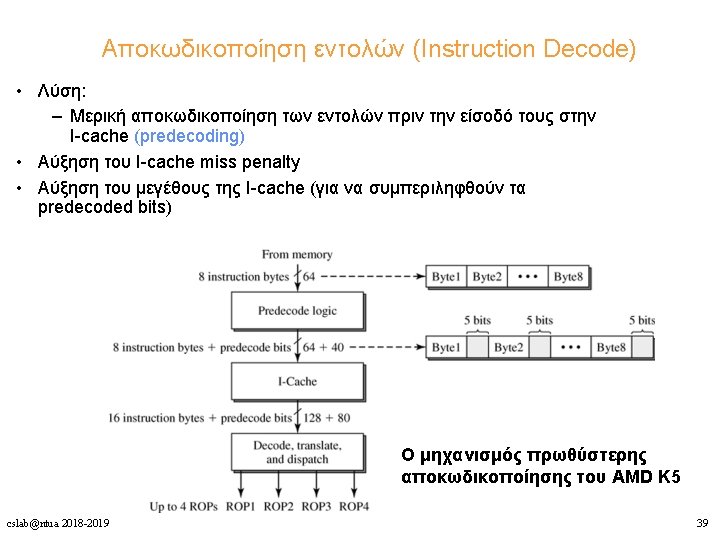

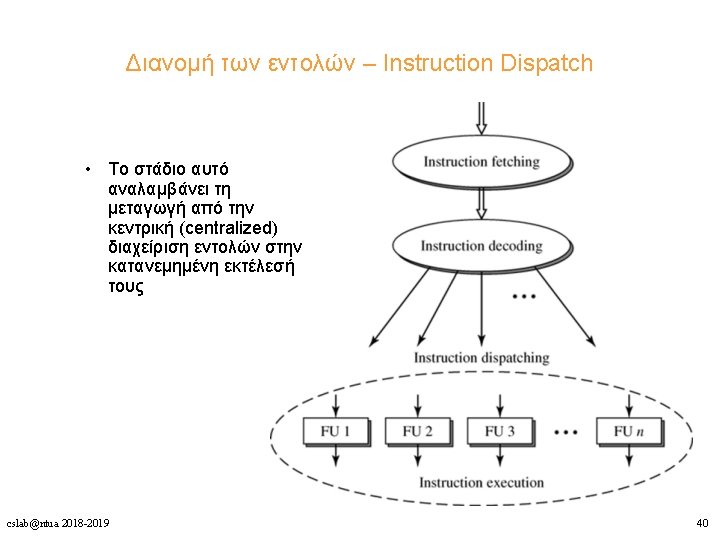

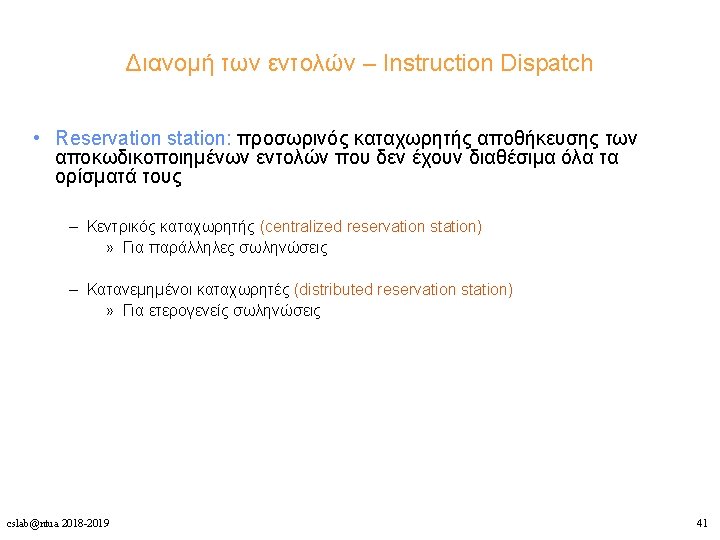

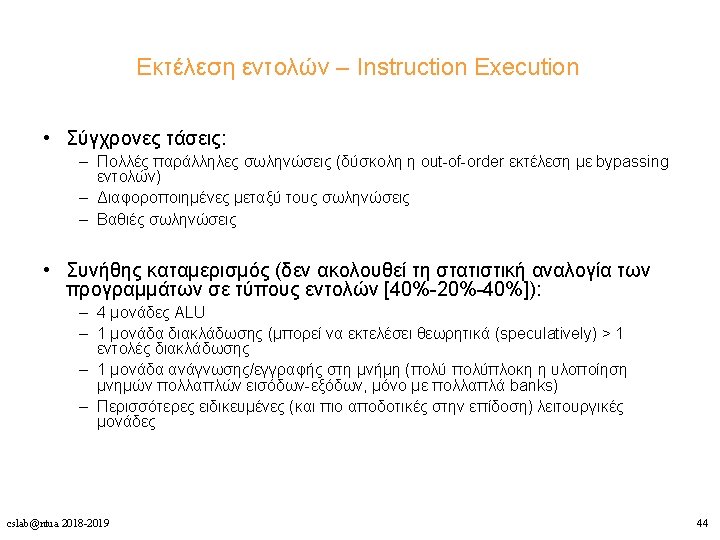

Superscalar Pipeline Design • • • Instruction Fetching Issues Instruction Decoding Issues Instruction Dispatching Issues Instruction Execution Issues Instruction Completion & Retiring Issues cslab@ntua 2018 -2019 33

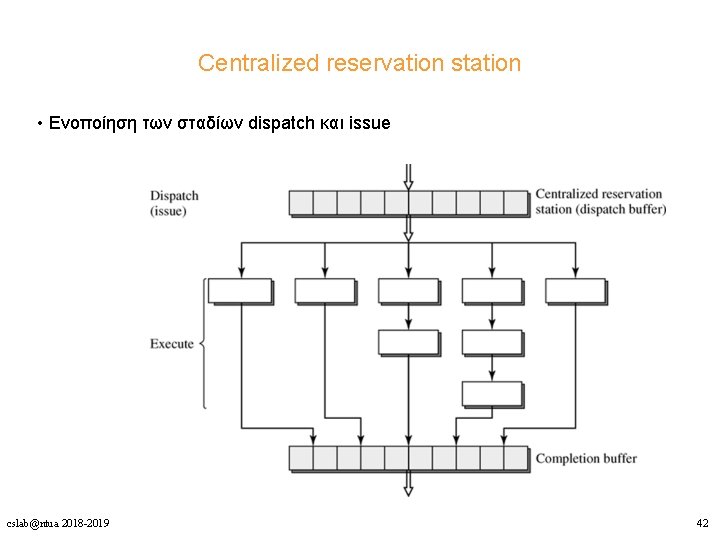

Centralized reservation station • Ενοποίηση των σταδίων dispatch και issue cslab@ntua 2018 -2019 42

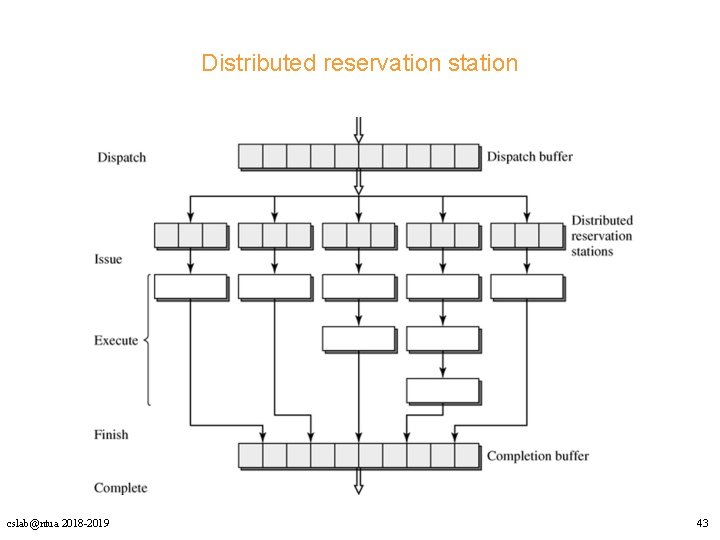

Distributed reservation station cslab@ntua 2018 -2019 43

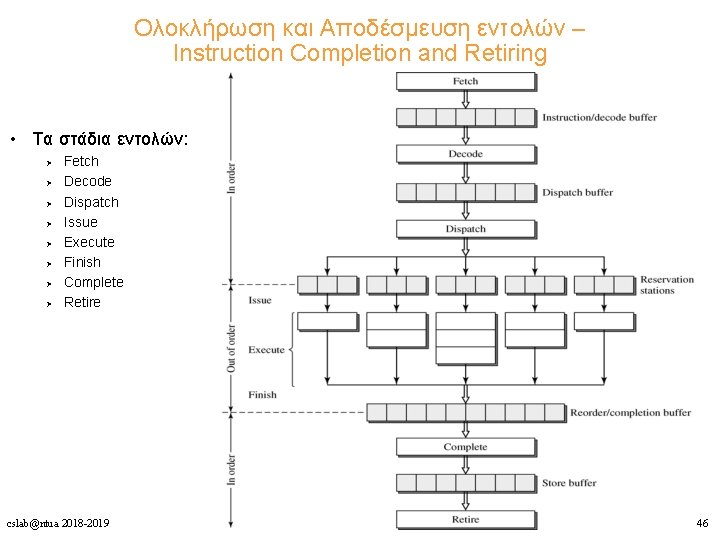

Ολοκλήρωση και Αποδέσμευση εντολών – Instruction Completion and Retiring • Τα στάδια εντολών: Ø Ø Ø Ø Fetch Decode Dispatch Issue Execute Finish Complete Retire cslab@ntua 2018 -2019 46

- Slides: 46