Hardware unrolling inorder commit and explicit register renaming

- Slides: 19

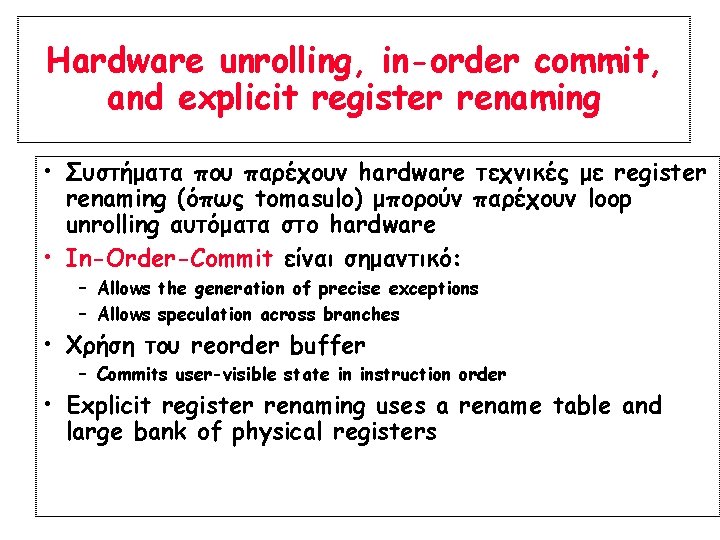

Hardware unrolling, in-order commit, and explicit register renaming • Συστήματα που παρέχουν hardware τεχνικές με register renaming (όπως tomasulo) μπορούν παρέχουν loop unrolling αυτόματα στο hardware • In-Order-Commit είναι σημαντικό: – Allows the generation of precise exceptions – Allows speculation across branches • Χρήση του reorder buffer – Commits user-visible state in instruction order • Explicit register renaming uses a rename table and large bank of physical registers

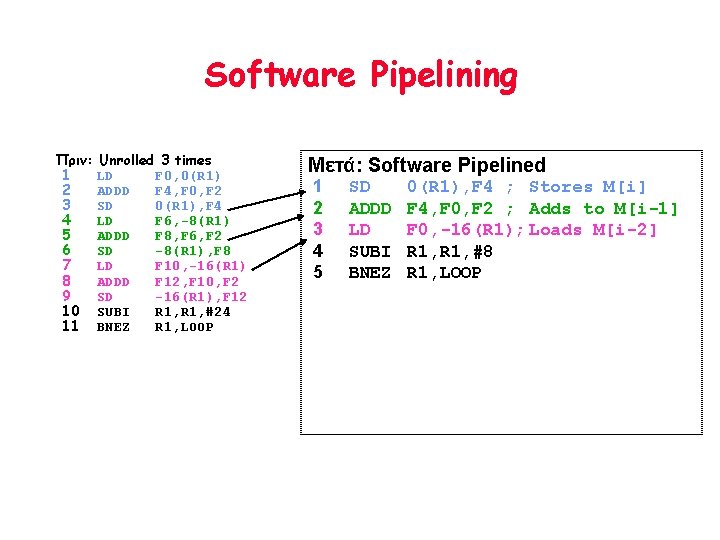

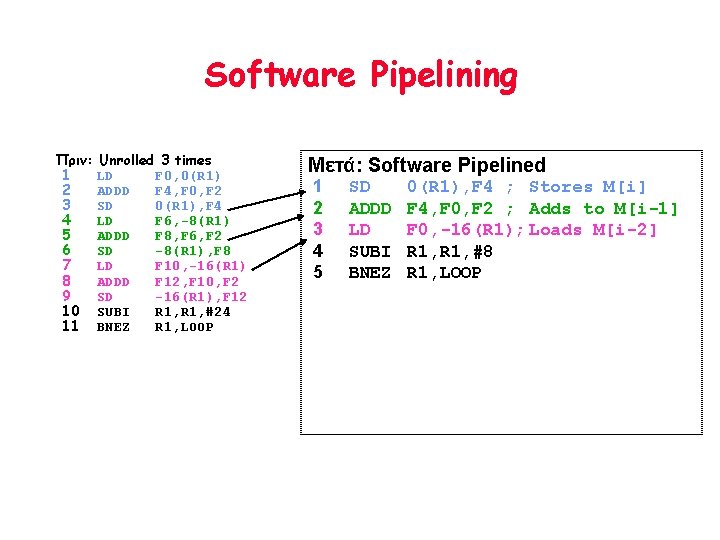

Software Pipelining Πριν: Unrolled 3 times 1 LD F 0, 0(R 1) 2 ADDD F 4, F 0, F 2 3 SD 0(R 1), F 4 4 LD F 6, -8(R 1) 5 ADDD F 8, F 6, F 2 6 SD -8(R 1), F 8 7 LD F 10, -16(R 1) 8 ADDD F 12, F 10, F 2 9 SD -16(R 1), F 12 10 SUBI R 1, #24 11 BNEZ R 1, LOOP Μετά: Software Pipelined 1 2 3 4 5 SD ADDD LD SUBI BNEZ 0(R 1), F 4 ; Stores M[i] F 4, F 0, F 2 ; Adds to M[i-1] F 0, -16(R 1); Loads M[i-2] R 1, #8 R 1, LOOP

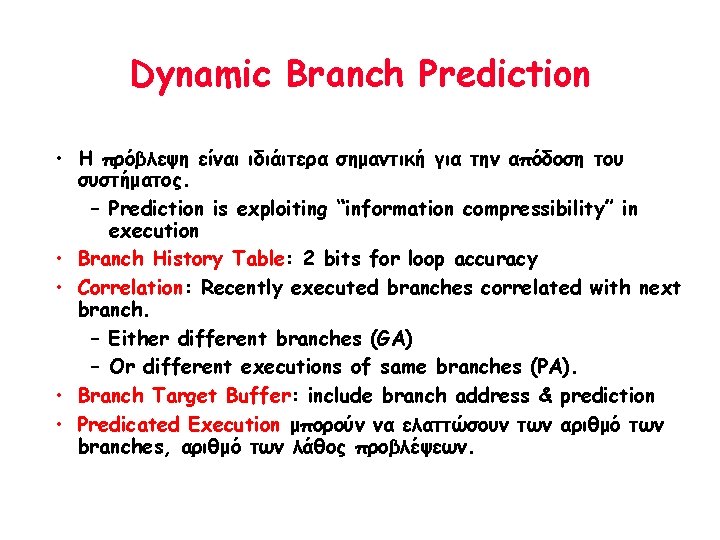

Dynamic Branch Prediction • Η πρόβλεψη είναι ιδιάιτερα σημαντική για την απόδοση του συστήματος. – Prediction is exploiting “information compressibility” in execution • Branch History Table: 2 bits for loop accuracy • Correlation: Recently executed branches correlated with next branch. – Either different branches (GA) – Or different executions of same branches (PA). • Branch Target Buffer: include branch address & prediction • Predicated Execution μπορούν να ελαττώσουν των αριθμό των branches, αριθμό των λάθος προβλέψεων.

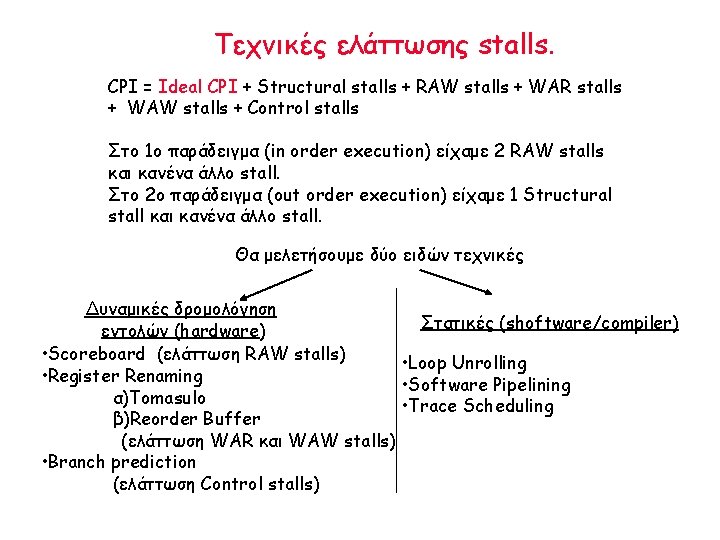

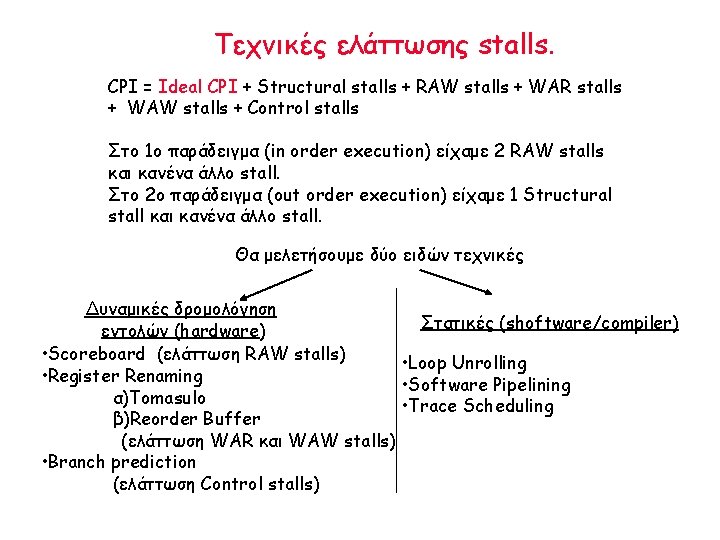

Τεχνικές ελάττωσης stalls. CPI = Ideal CPI + Structural stalls + RAW stalls + WAR stalls + WAW stalls + Control stalls Στο 1ο παράδειγμα (in order execution) είχαμε 2 RAW stalls και κανένα άλλο stall. Στο 2ο παράδειγμα (out order execution) είχαμε 1 Structural stall και κανένα άλλο stall. Θα μελετήσουμε δύο ειδών τεχνικές Δυναμικές δρομολόγηση Στατικές (shoftware/compiler) εντολών (hardware) • Scoreboard (ελάττωση RAW stalls) • Loop Unrolling • Register Renaming • Software Pipelining α)Tomasulo • Trace Scheduling β)Reorder Buffer (ελάττωση WAR και WAW stalls) • Branch prediction (ελάττωση Control stalls)

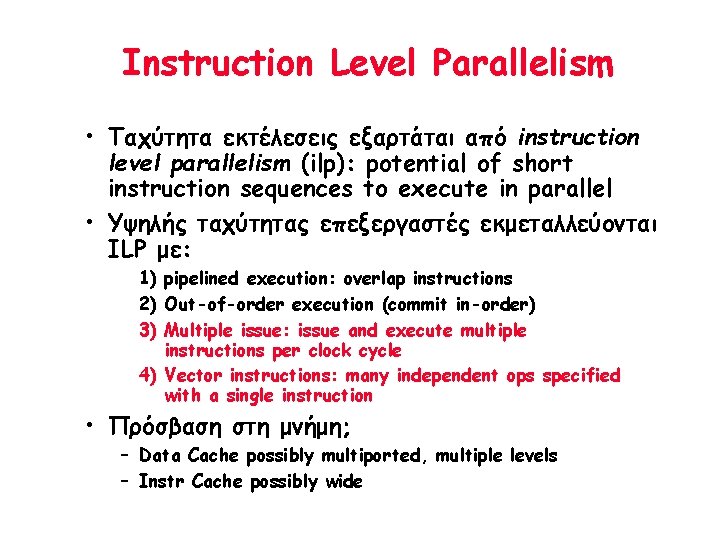

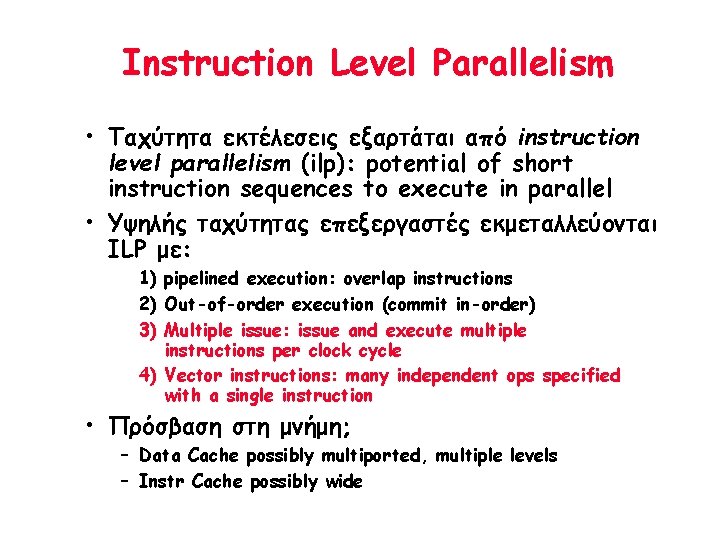

Instruction Level Parallelism • Ταχύτητα εκτέλεσεις εξαρτάται από instruction level parallelism (ilp): potential of short instruction sequences to execute in parallel • Υψηλής ταχύτητας επεξεργαστές εκμεταλλεύονται ILP με: 1) pipelined execution: overlap instructions 2) Out-of-order execution (commit in-order) 3) Multiple issue: issue and execute multiple instructions per clock cycle 4) Vector instructions: many independent ops specified with a single instruction • Πρόσβαση στη μνήμη; – Data Cache possibly multiported, multiple levels – Instr Cache possibly wide

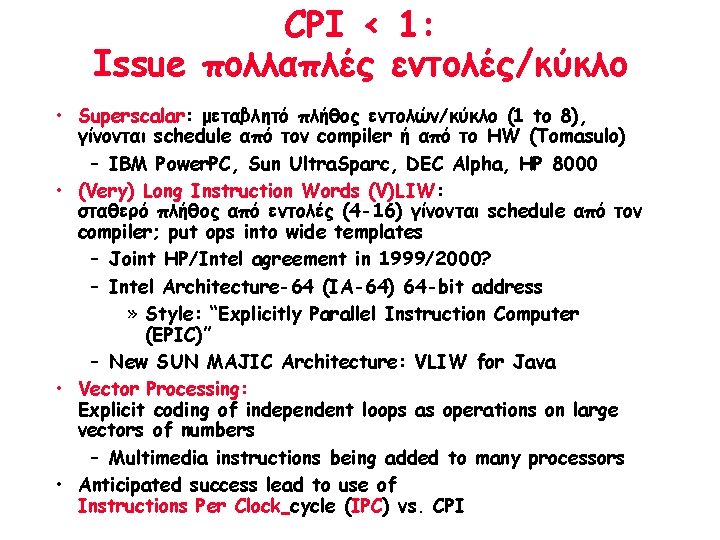

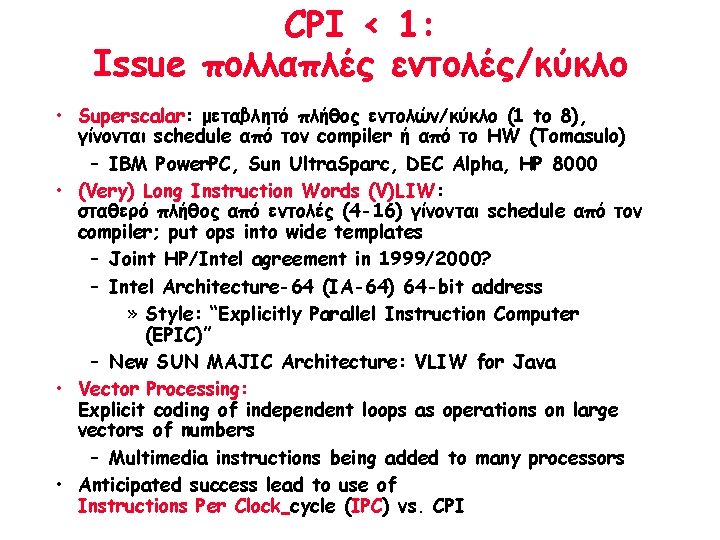

CPI < 1: Issue πολλαπλές εντολές/κύκλο • Superscalar: μεταβλητό πλήθος εντολών/κύκλο (1 to 8), γίνονται schedule από τον compiler ή από το HW (Tomasulo) – IBM Power. PC, Sun Ultra. Sparc, DEC Alpha, HP 8000 • (Very) Long Instruction Words (V)LIW: σταθερό πλήθος από εντολές (4 -16) γίνονται schedule από τον compiler; put ops into wide templates – Joint HP/Intel agreement in 1999/2000? – Intel Architecture-64 (IA-64) 64 -bit address » Style: “Explicitly Parallel Instruction Computer (EPIC)” – New SUN MAJIC Architecture: VLIW for Java • Vector Processing: Explicit coding of independent loops as operations on large vectors of numbers – Multimedia instructions being added to many processors • Anticipated success lead to use of Instructions Per Clock cycle (IPC) vs. CPI

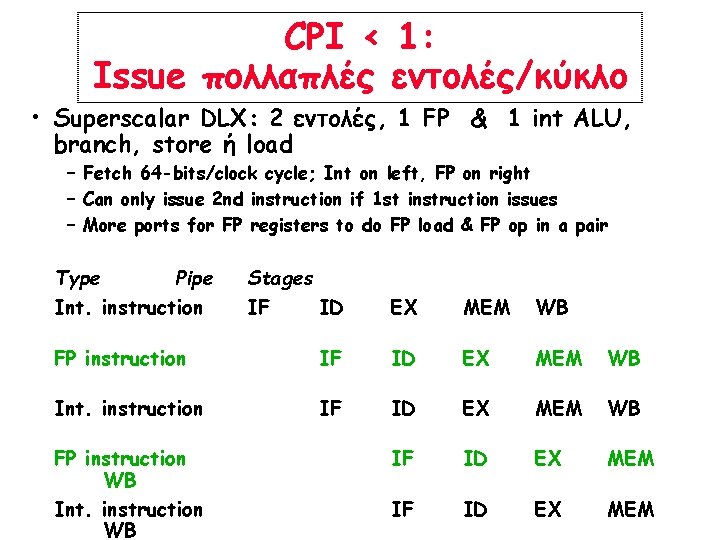

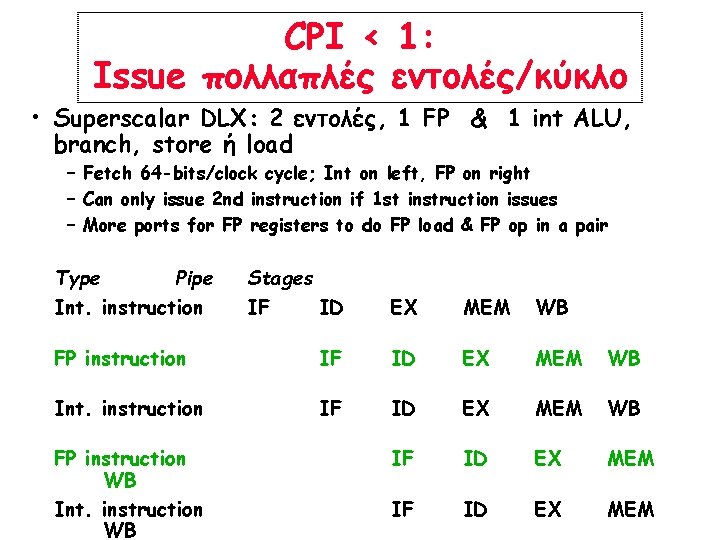

CPI < 1: Issue πολλαπλές εντολές/κύκλο • Superscalar DLX: 2 εντολές, 1 FP & 1 int ALU, branch, store ή load – Fetch 64 -bits/clock cycle; Int on left, FP on right – Can only issue 2 nd instruction if 1 st instruction issues – More ports for FP registers to do FP load & FP op in a pair Type Pipe Int. instruction Stages IF ID EX MEM WB FP instruction IF ID EX MEM WB Int. instruction IF ID EX MEM WB IF ID EX MEM FP instruction WB Int. instruction WB

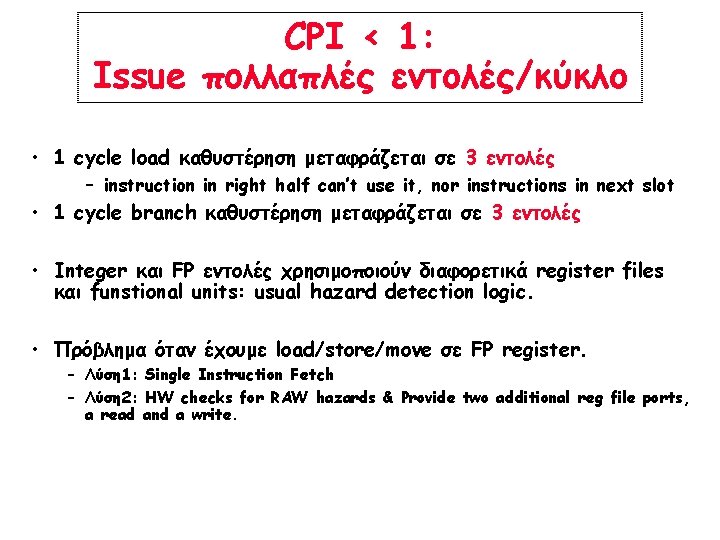

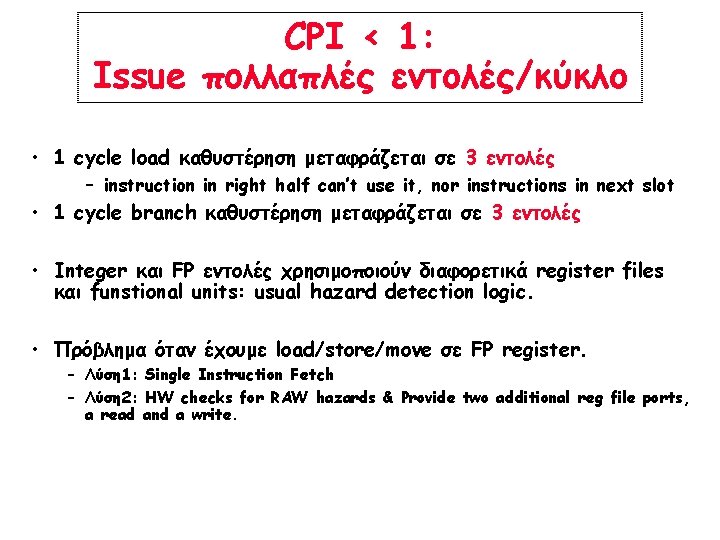

CPI < 1: Issue πολλαπλές εντολές/κύκλο • 1 cycle load καθυστέρηση μεταφράζεται σε 3 εντολές – instruction in right half can’t use it, nor instructions in next slot • 1 cycle branch καθυστέρηση μεταφράζεται σε 3 εντολές • Integer και FP εντολές χρησιμοποιούν διαφορετικά register files και funstional units: usual hazard detection logic. • Πρόβλημα όταν έχουμε load/store/move σε FP register. – Λύση 1: Single Instruction Fetch – Λύση 2: HW checks for RAW hazards & Provide two additional reg file ports, a read and a write.

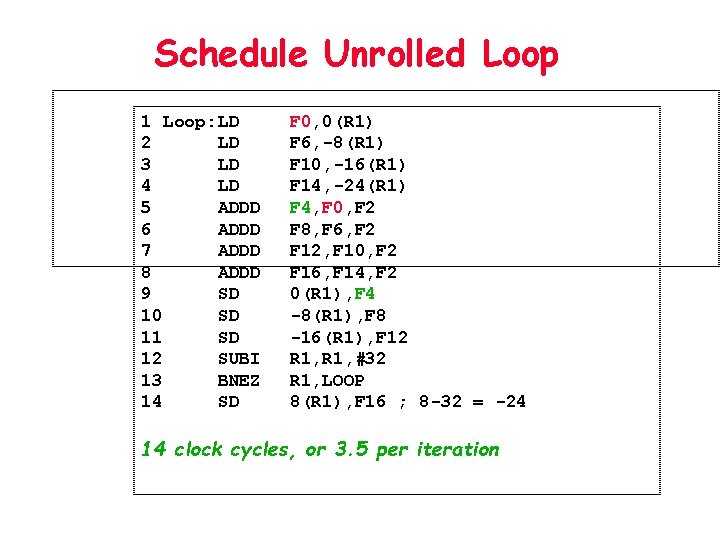

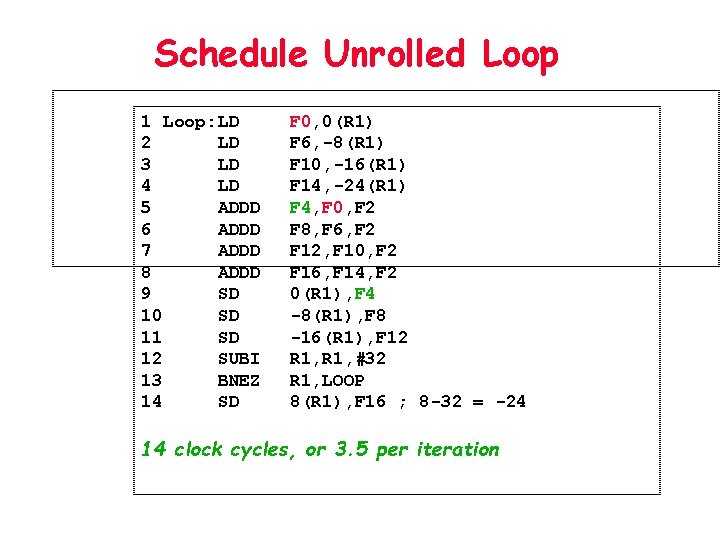

Schedule Unrolled Loop 1 Loop: LD 2 LD 3 LD 4 LD 5 ADDD 6 ADDD 7 ADDD 8 ADDD 9 SD 10 SD 11 SD 12 SUBI 13 BNEZ 14 SD F 0, 0(R 1) F 6, -8(R 1) F 10, -16(R 1) F 14, -24(R 1) F 4, F 0, F 2 F 8, F 6, F 2 F 12, F 10, F 2 F 16, F 14, F 2 0(R 1), F 4 -8(R 1), F 8 -16(R 1), F 12 R 1, #32 R 1, LOOP 8(R 1), F 16 ; 8 -32 = -24 14 clock cycles, or 3. 5 per iteration

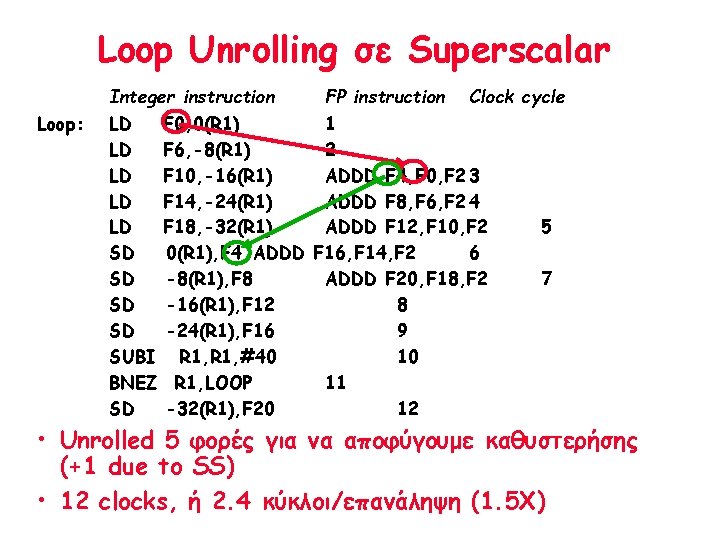

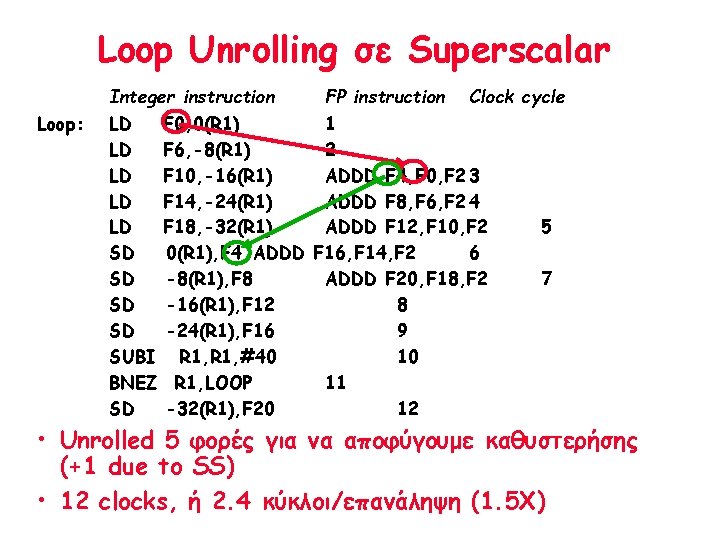

Loop Unrolling σε Superscalar Integer instruction Loop: FP instruction Clock cycle LD F 0, 0(R 1) 1 LD F 6, -8(R 1) 2 LD F 10, -16(R 1) ADDD F 4, F 0, F 2 3 LD F 14, -24(R 1) ADDD F 8, F 6, F 2 4 LD F 18, -32(R 1) ADDD F 12, F 10, F 2 SD 0(R 1), F 4 ADDD F 16, F 14, F 2 6 SD -8(R 1), F 8 ADDD F 20, F 18, F 2 SD -16(R 1), F 12 8 SD -24(R 1), F 16 9 SUBI R 1, #40 10 BNEZ R 1, LOOP 11 SD -32(R 1), F 20 12 5 7 • Unrolled 5 φορές για να αποφύγουμε καθυστερήσης (+1 due to SS) • 12 clocks, ή 2. 4 κύκλοι/επανάληψη (1. 5 X)

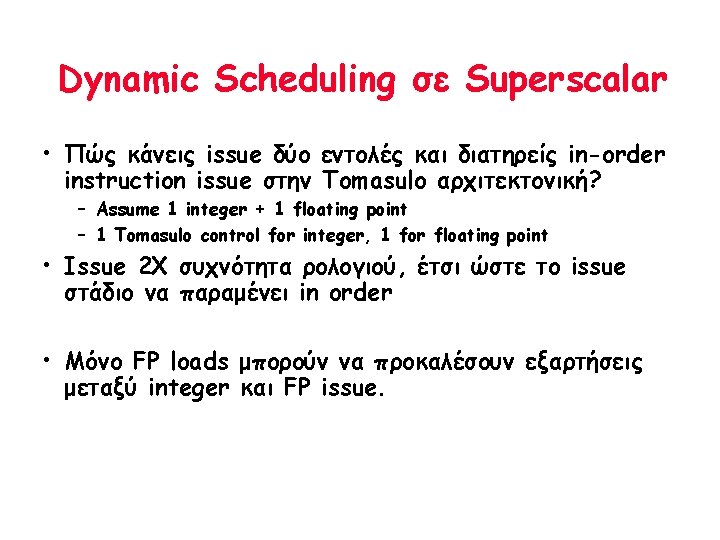

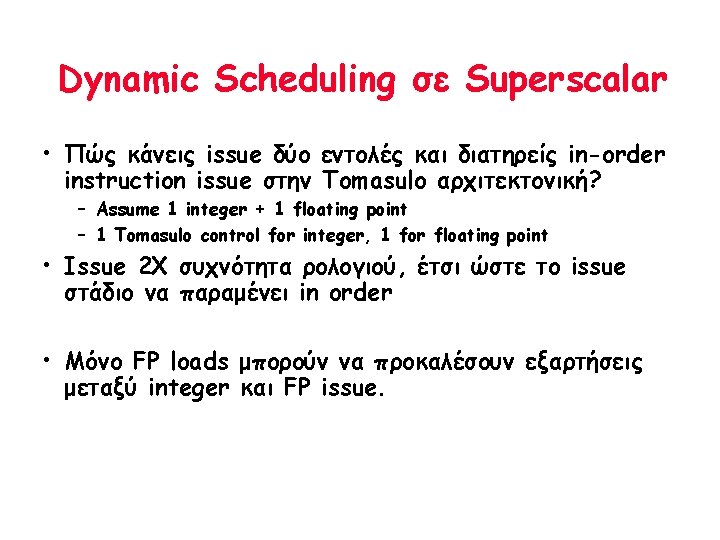

Dynamic Scheduling σε Superscalar • Πώς κάνεις issue δύο εντολές και διατηρείς in-order instruction issue στην Tomasulo αρχιτεκτονική? – Assume 1 integer + 1 floating point – 1 Tomasulo control for integer, 1 for floating point • Issue 2 X συχνότητα ρολογιού, έτσι ώστε το issue στάδιο να παραμένει in order • Μόνο FP loads μπορούν να προκαλέσουν εξαρτήσεις μεταξύ integer και FP issue.

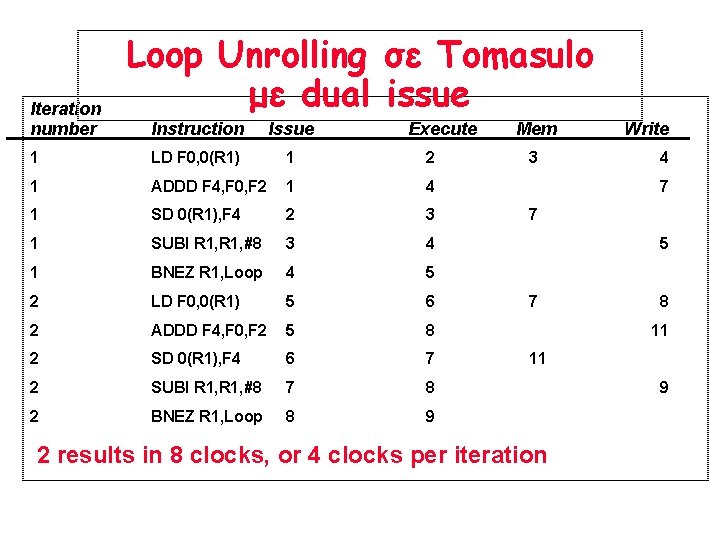

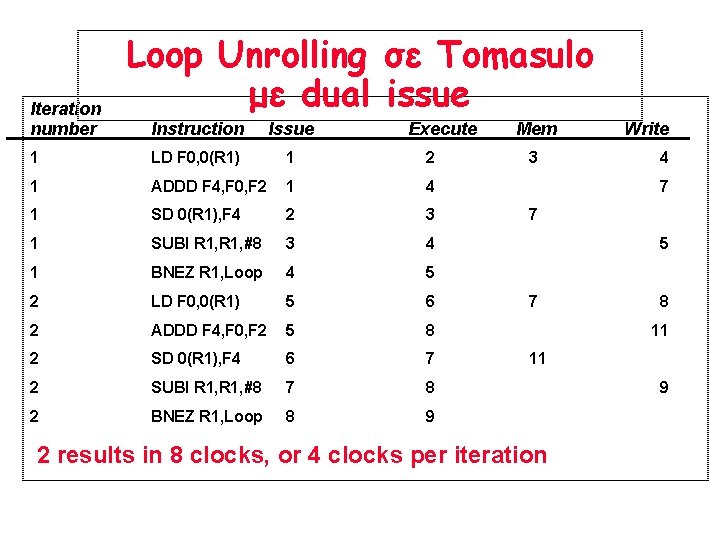

Iteration number Loop Unrolling σε Tomasulo με dual issue Instruction Issue Execute 1 LD F 0, 0(R 1) 1 2 1 ADDD F 4, F 0, F 2 1 4 1 SD 0(R 1), F 4 2 3 1 SUBI R 1, #8 3 4 1 BNEZ R 1, Loop 4 5 2 LD F 0, 0(R 1) 5 6 2 ADDD F 4, F 0, F 2 5 8 2 SD 0(R 1), F 4 6 7 2 SUBI R 1, #8 7 8 2 BNEZ R 1, Loop 8 9 Mem 3 Write 4 7 7 5 7 8 11 11 2 results in 8 clocks, or 4 clocks per iteration 9

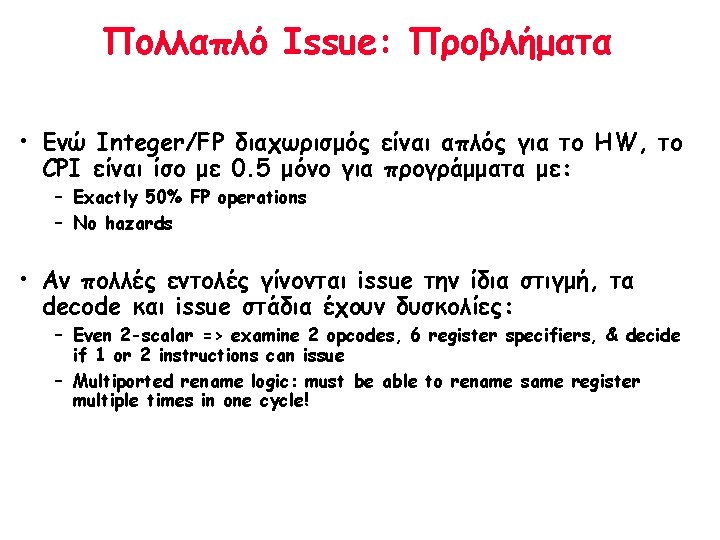

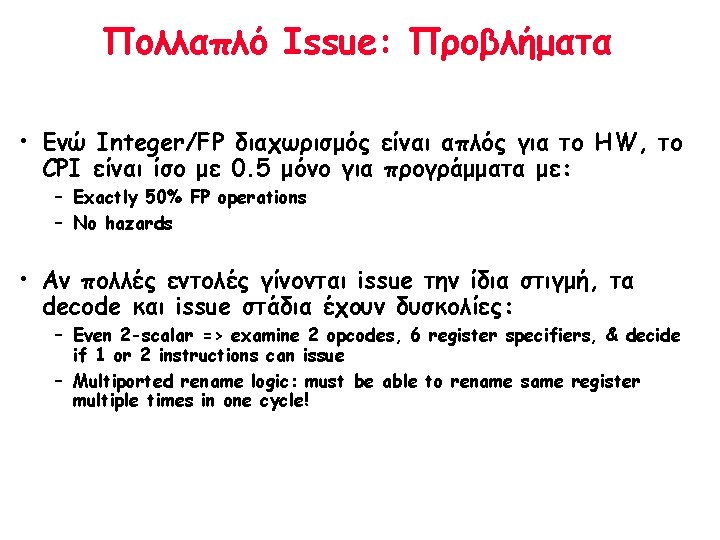

Πολλαπλό Issue: Προβλήματα • Ενώ Integer/FP διαχωρισμός είναι απλός για το HW, το CPI είναι ίσο με 0. 5 μόνο για προγράμματα με: – Exactly 50% FP operations – No hazards • Αν πολλές εντολές γίνονται issue την ίδια στιγμή, τα decode και issue στάδια έχουν δυσκολίες: – Even 2 -scalar => examine 2 opcodes, 6 register specifiers, & decide if 1 or 2 instructions can issue – Multiported rename logic: must be able to rename same register multiple times in one cycle!

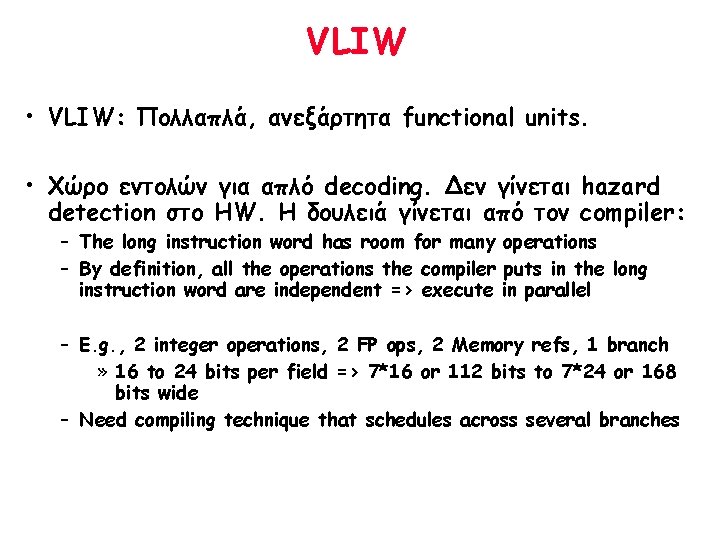

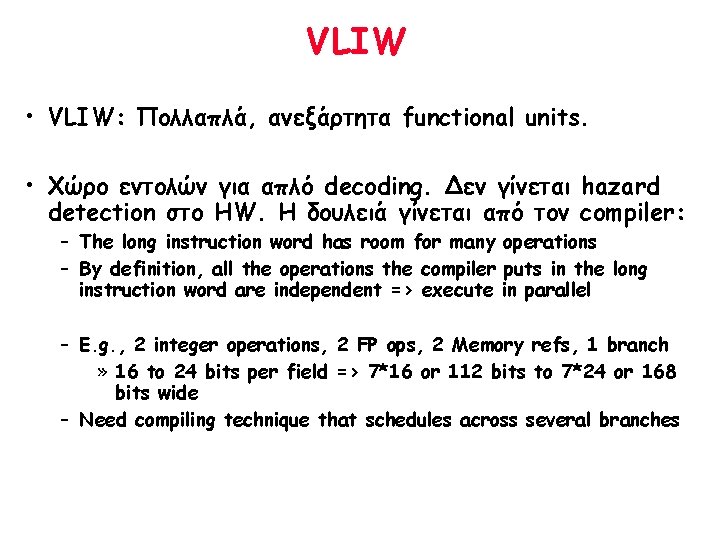

VLIW • VLIW: Πολλαπλά, ανεξάρτητα functional units. • Xώρο εντολών για απλό decoding. Δεν γίνεται hazard detection στο HW. H δουλειά γίνεται από τον compiler: – The long instruction word has room for many operations – By definition, all the operations the compiler puts in the long instruction word are independent => execute in parallel – E. g. , 2 integer operations, 2 FP ops, 2 Memory refs, 1 branch » 16 to 24 bits per field => 7*16 or 112 bits to 7*24 or 168 bits wide – Need compiling technique that schedules across several branches

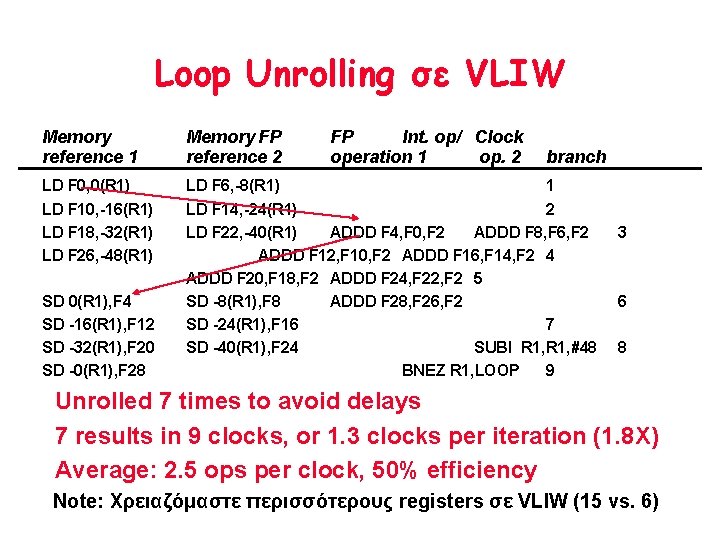

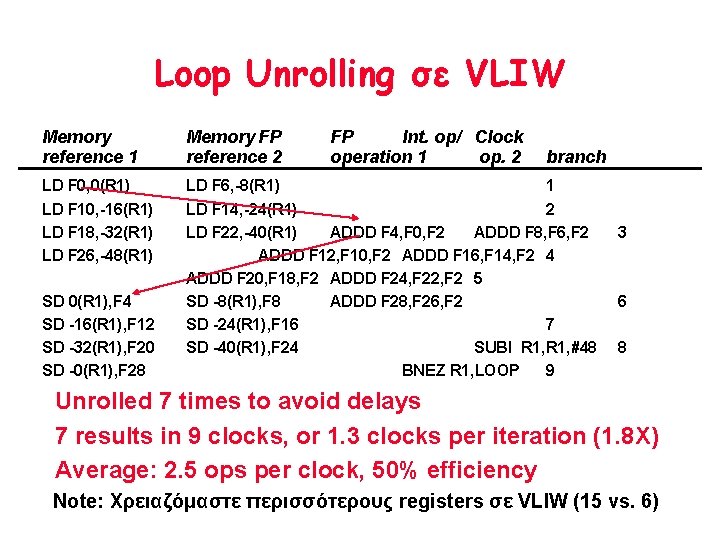

Loop Unrolling σε VLIW Memory reference 1 Memory FP reference 2 LD F 0, 0(R 1) LD F 6, -8(R 1) LD F 10, -16(R 1) LD F 18, -32(R 1) LD F 26, -48(R 1) LD F 14, -24(R 1) 2 LD F 22, -40(R 1) ADDD F 4, F 0, F 2 ADDD F 8, F 6, F 2 ADDD F 12, F 10, F 2 ADDD F 16, F 14, F 2 4 ADDD F 20, F 18, F 2 ADDD F 24, F 22, F 2 5 SD -8(R 1), F 8 ADDD F 28, F 26, F 2 SD -24(R 1), F 16 7 SD -40(R 1), F 24 SUBI R 1, #48 BNEZ R 1, LOOP 9 SD 0(R 1), F 4 SD -16(R 1), F 12 SD -32(R 1), F 20 SD -0(R 1), F 28 FP Int. op/ Clock operation 1 op. 2 branch 1 3 6 8 Unrolled 7 times to avoid delays 7 results in 9 clocks, or 1. 3 clocks per iteration (1. 8 X) Average: 2. 5 ops per clock, 50% efficiency Note: Χρειαζόμαστε περισσότερους registers σε VLIW (15 vs. 6)

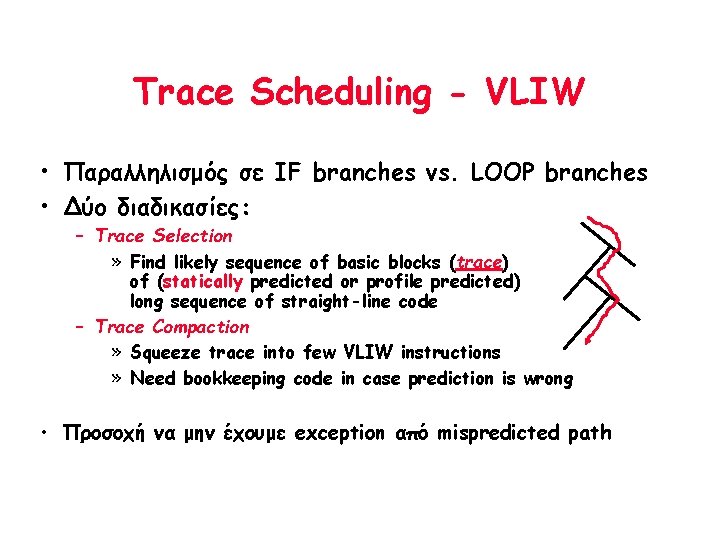

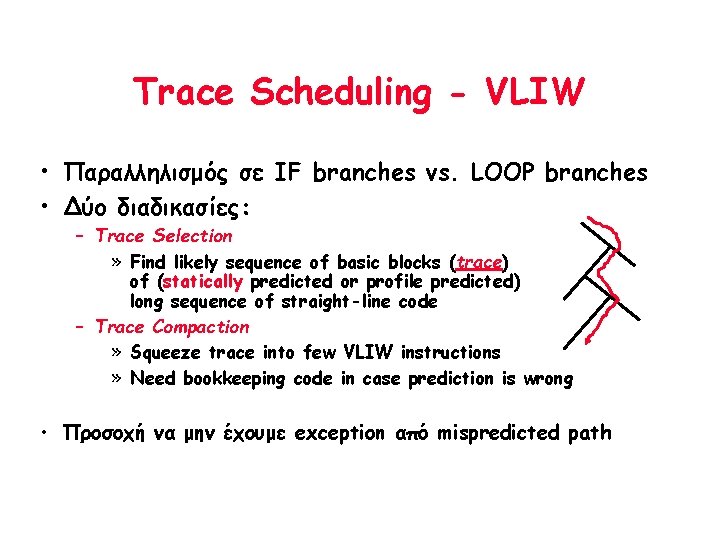

Trace Scheduling - VLIW • Παραλληλισμός σε IF branches vs. LOOP branches • Δύο διαδικασίες: – Trace Selection » Find likely sequence of basic blocks (trace) of (statically predicted or profile predicted) long sequence of straight-line code – Trace Compaction » Squeeze trace into few VLIW instructions » Need bookkeeping code in case prediction is wrong • Προσοχή να μην έχουμε exception από mispredicted path

Πλεονεκτήματα του HW (Tomasulo) vs. SW (VLIW), prediction • • • HW determines address conflicts HW better branch prediction HW maintains precise exception model HW does not execute bookkeeping instructions Works across multiple implementations SW speculation is much easier for HW design

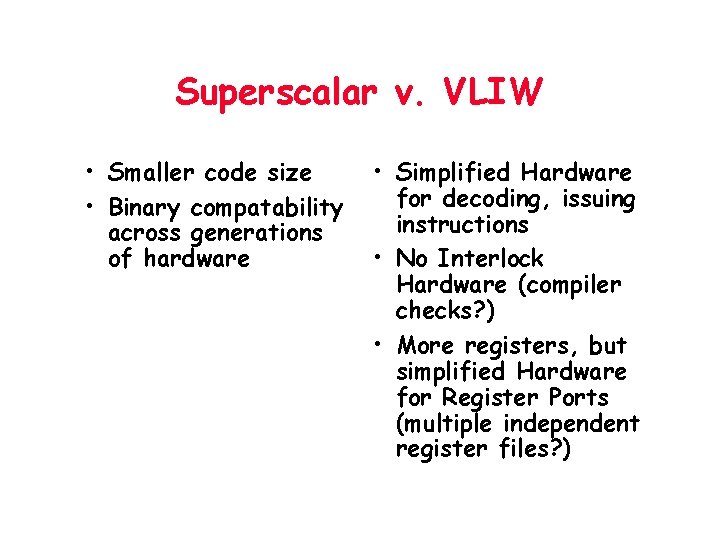

Superscalar v. VLIW • Smaller code size • Binary compatability across generations of hardware • Simplified Hardware for decoding, issuing instructions • No Interlock Hardware (compiler checks? ) • More registers, but simplified Hardware for Register Ports (multiple independent register files? )