Hardware Simulator Tutorial The Hardware Simulator is part

- Slides: 39

Hardware Simulator Tutorial The Hardware Simulator is part of the software suite that accompanies the book “The Digital Core”, by Nisan and Schocken, forthcoming in 2003, www. idc. ac. il/csd Hardware Simulator Tutorial Index Slide 1

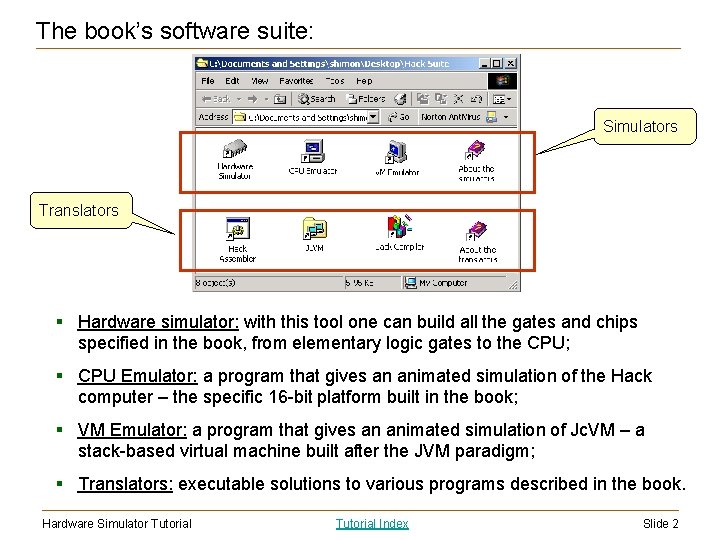

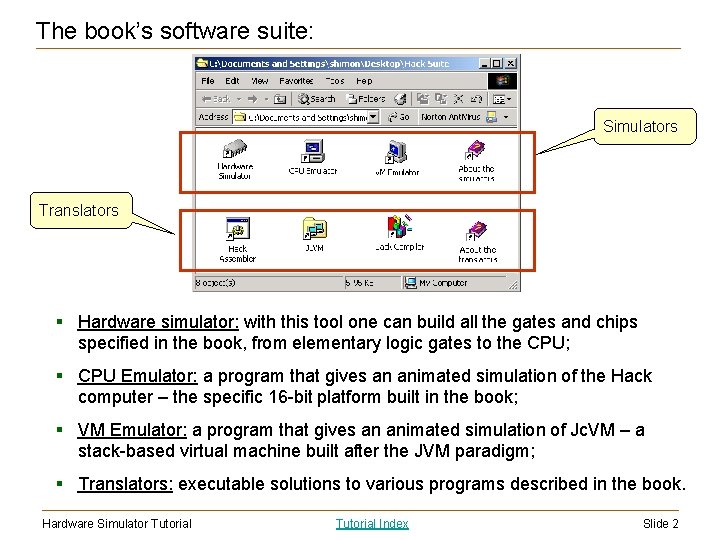

The book’s software suite: Simulators Translators § Hardware simulator: with this tool one can build all the gates and chips specified in the book, from elementary logic gates to the CPU; § CPU Emulator: a program that gives an animated simulation of the Hack computer – the specific 16 -bit platform built in the book; § VM Emulator: a program that gives an animated simulation of Jc. VM – a stack-based virtual machine built after the JVM paradigm; § Translators: executable solutions to various programs described in the book. Hardware Simulator Tutorial Index Slide 2

The book’s software suite: This tutorial describes the Hardware simulator only. Hardware Simulator Tutorial Index Slide 3

Hardware Simulation Tutorial § Purpose: learn how to use the simulator with which all the chips specified in the book can be built § Required knowledge: Chapter 1 of the book § Recommended: Appendix A of the book. § Contents: I. Getting started II. Test scripts III. Built-in chips IV. Clocked chips V. Debugging tools Hardware Simulator Tutorial Index Slide 4

Hardware Simulation Tutorial Part I: Getting Started Hardware Simulator Tutorial Index Slide 5

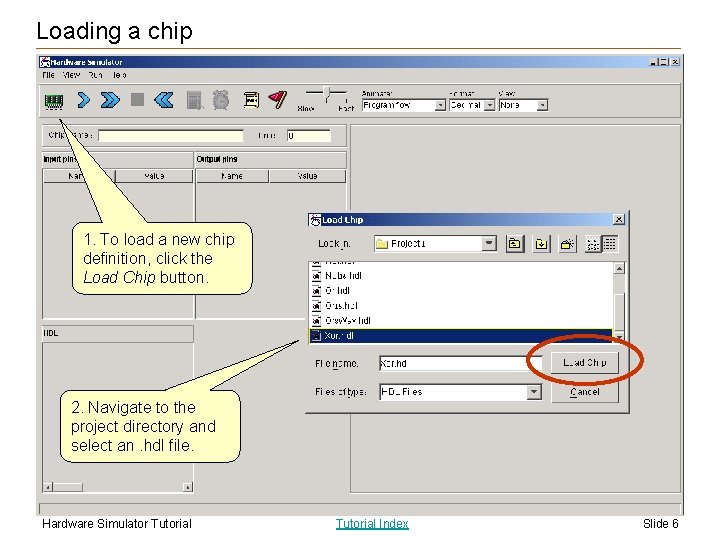

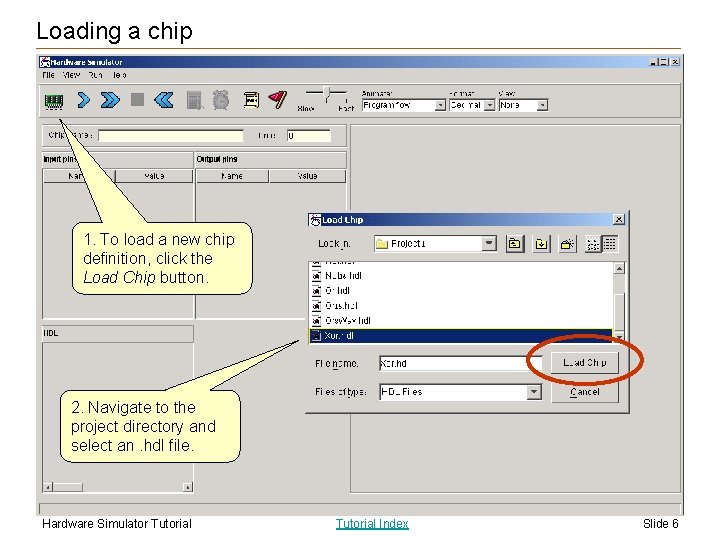

Loading a chip 1. To load a new chip definition, click the Load Chip button. 2. Navigate to the project directory and select an. hdl file. Hardware Simulator Tutorial Index Slide 6

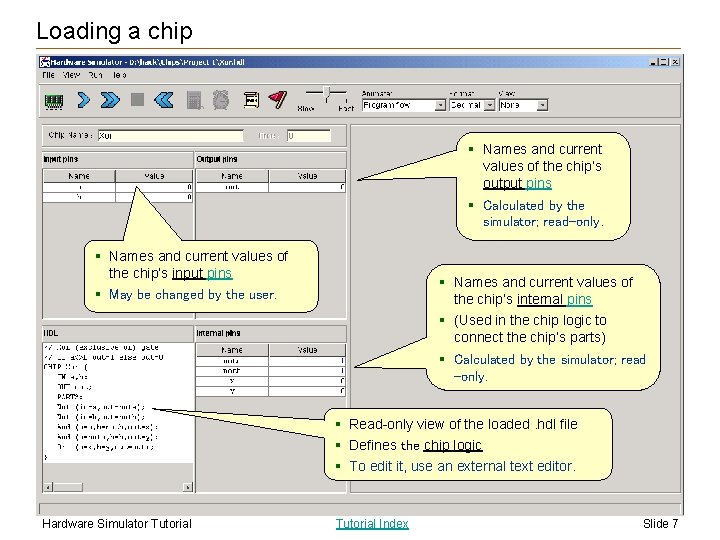

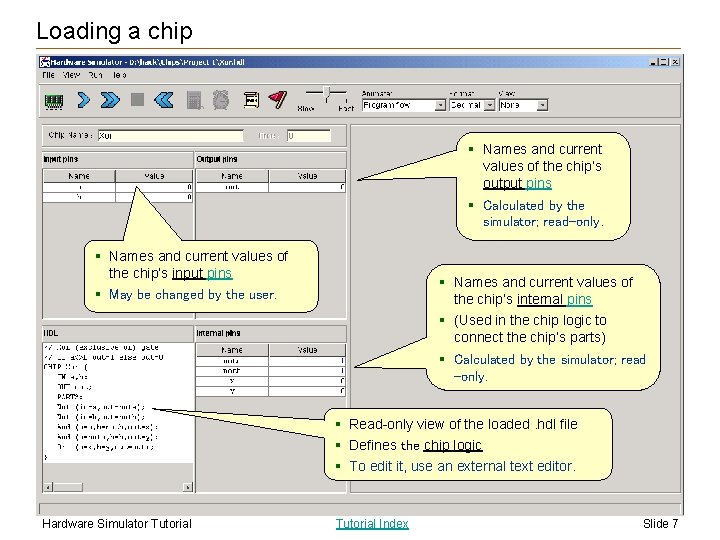

Loading a chip § Names and current values of the chip’s output pins § Calculated by the simulator; read-only. § Names and current values of the chip’s input pins § Names and current values of the chip’s internal pins § (Used in the chip logic to connect the chip’s parts) § May be changed by the user. § Calculated by the simulator; read -only. § Read-only view of the loaded. hdl file § Defines the chip logic § To edit it, use an external text editor. Hardware Simulator Tutorial Index Slide 7

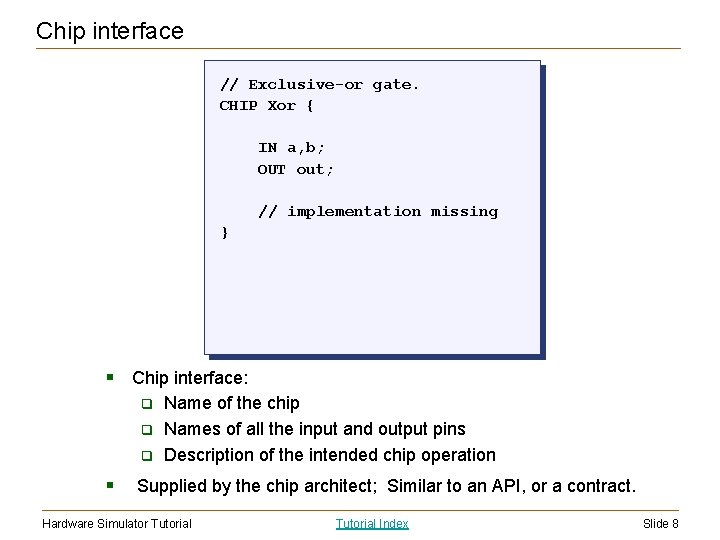

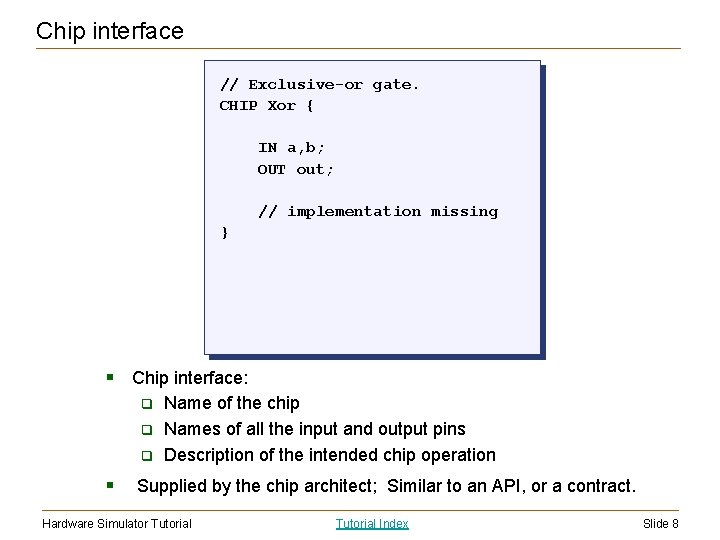

Chip interface // Exclusive-or gate. CHIP Xor { IN a, b; OUT out; // implementation missing } § Chip interface: q q q § Name of the chip Names of all the input and output pins Description of the intended chip operation Supplied by the chip architect; Similar to an API, or a contract. Hardware Simulator Tutorial Index Slide 8

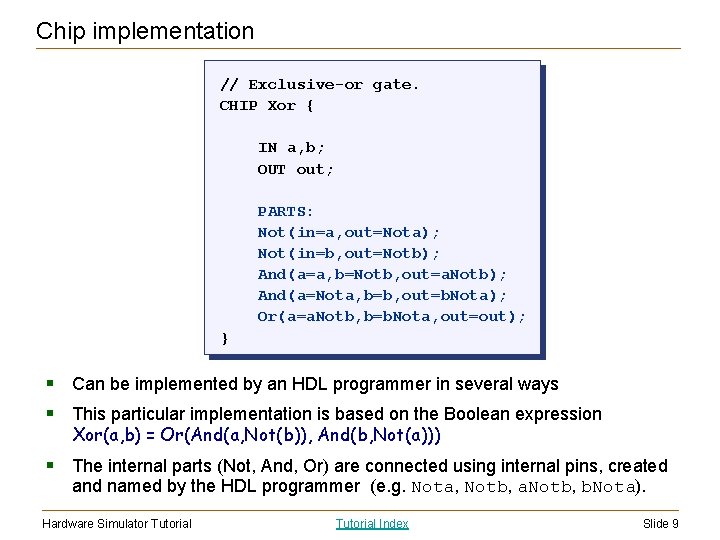

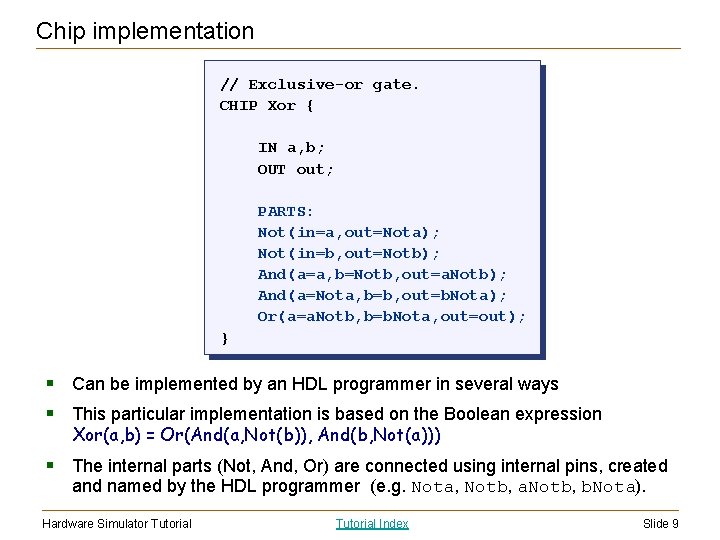

Chip implementation // Exclusive-or gate. CHIP Xor { IN a, b; OUT out; PARTS: Not(in=a, out=Nota); Not(in=b, out=Notb); And(a=a, b=Notb, out=a. Notb); And(a=Nota, b=b, out=b. Nota); Or(a=a. Notb, b=b. Nota, out=out); } § Can be implemented by an HDL programmer in several ways § This particular implementation is based on the Boolean expression Xor(a, b) = Or(And(a, Not(b)), And(b, Not(a))) § The internal parts (Not, And, Or) are connected using internal pins, created and named by the HDL programmer (e. g. Nota, Notb, a. Notb, b. Nota). Hardware Simulator Tutorial Index Slide 9

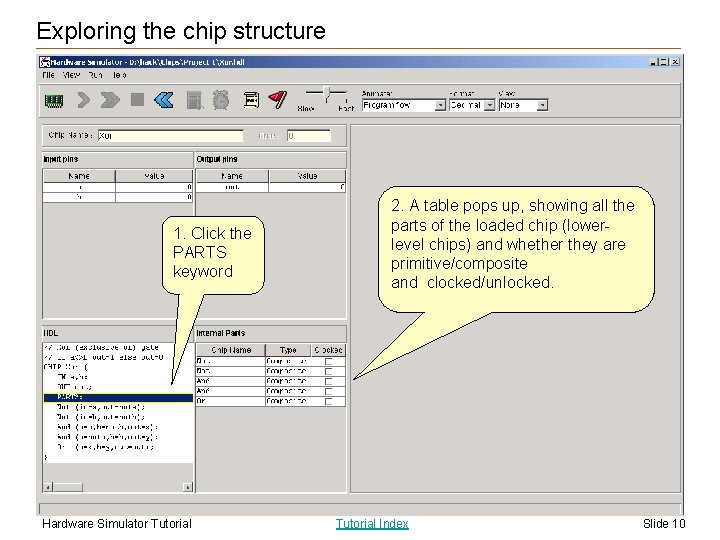

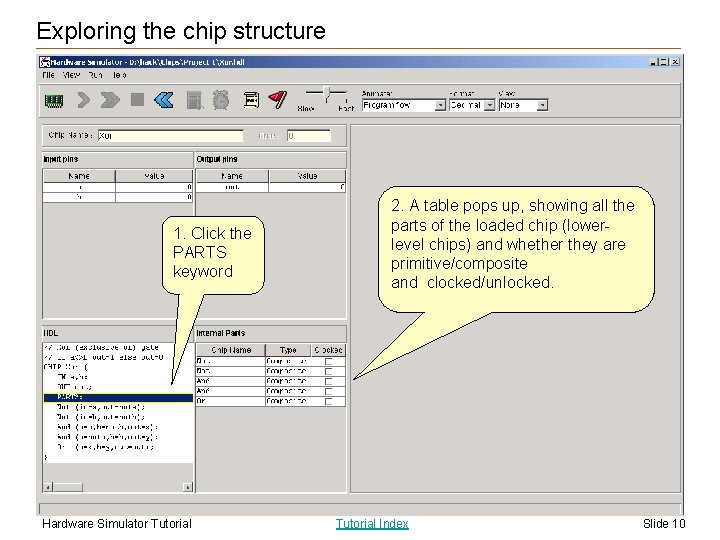

Exploring the chip structure 1. Click the PARTS keyword Hardware Simulator Tutorial 2. A table pops up, showing all the parts of the loaded chip (lowerlevel chips) and whether they are primitive/composite and clocked/unlocked. Tutorial Index Slide 10

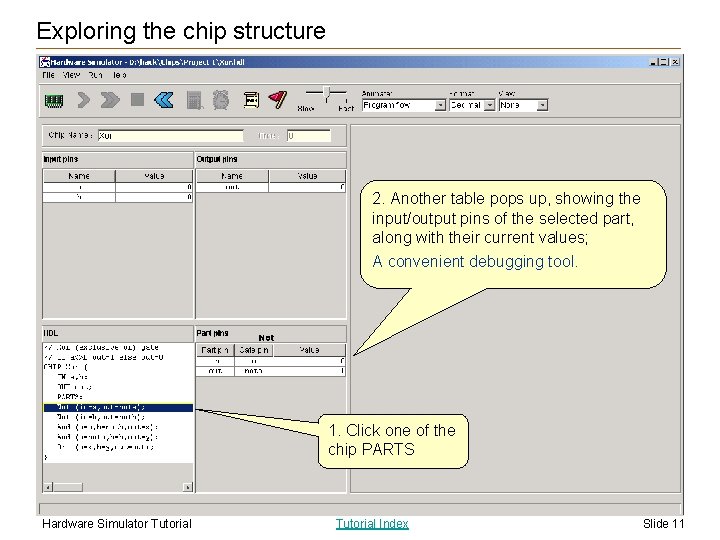

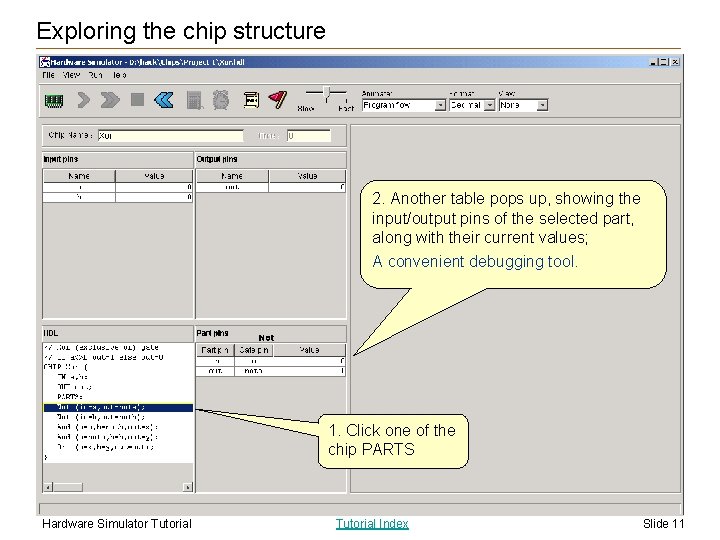

Exploring the chip structure 2. Another table pops up, showing the input/output pins of the selected part, along with their current values; A convenient debugging tool. 1. Click one of the chip PARTS Hardware Simulator Tutorial Index Slide 11

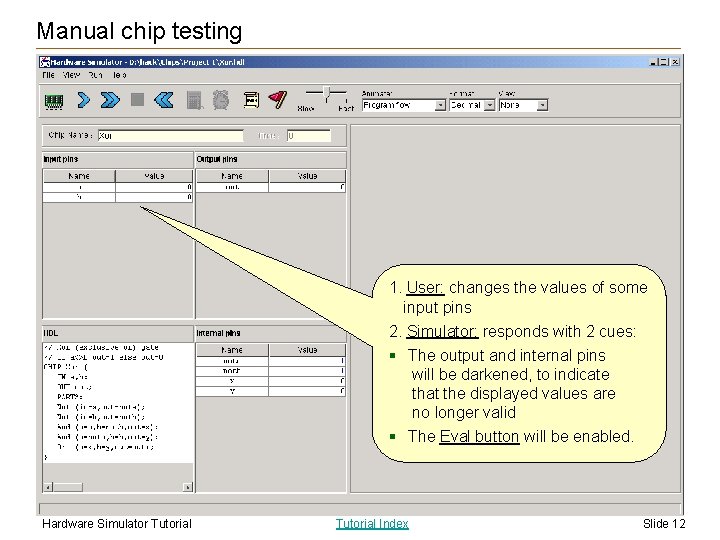

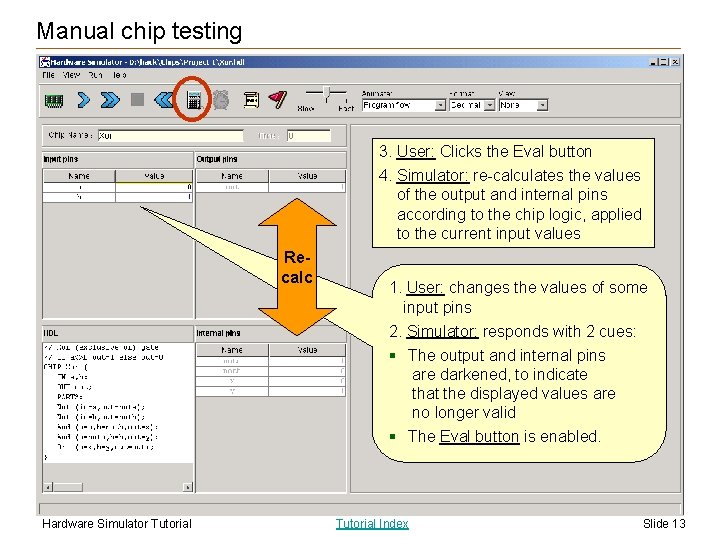

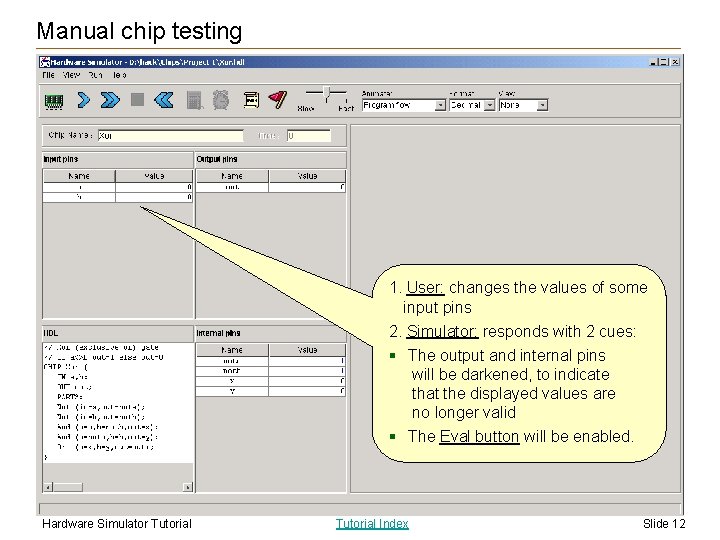

Manual chip testing 1. User: changes the values of some input pins 2. Simulator: responds with 2 cues: § The output and internal pins will be darkened, to indicate that the displayed values are no longer valid § The Eval button will be enabled. Hardware Simulator Tutorial Index Slide 12

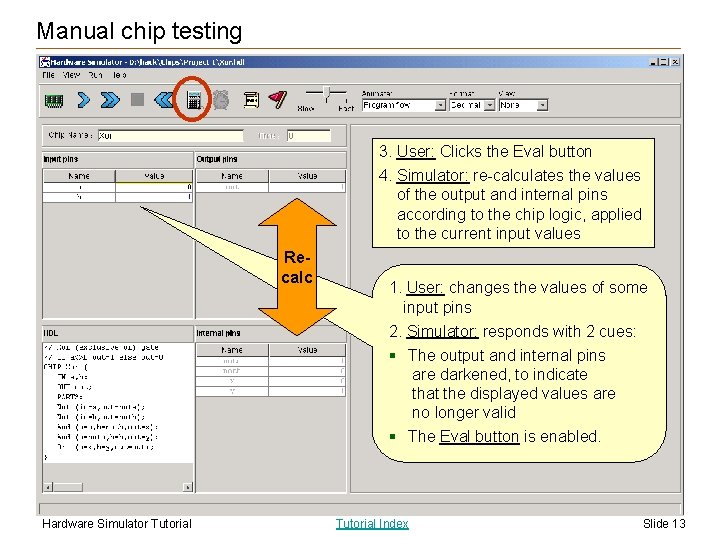

Manual chip testing 3. User: Clicks the Eval button 4. Simulator: re-calculates the values of the output and internal pins according to the chip logic, applied to the current input values Recalc 1. User: changes the values of some input pins 2. Simulator: responds with 2 cues: § The output and internal pins are darkened, to indicate that the displayed values are no longer valid § The Eval button is enabled. Hardware Simulator Tutorial Index Slide 13

Hardware Simulation Tutorial Part II: Test Scripts Hardware Simulator Tutorial Index Slide 14

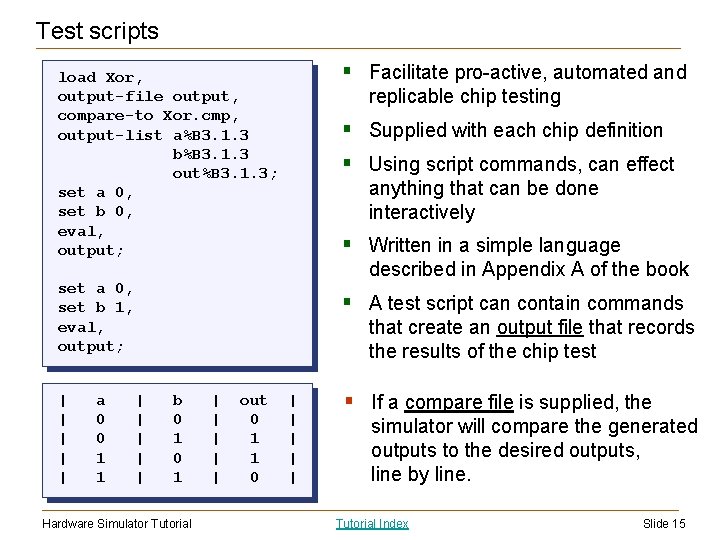

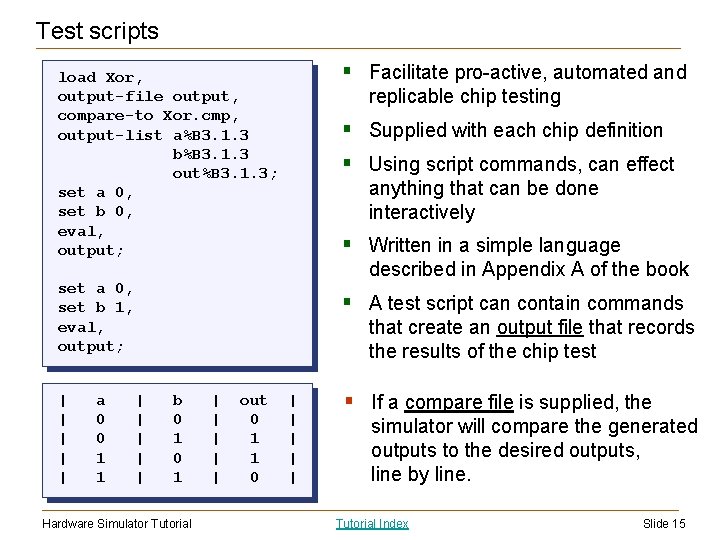

Test scripts § Facilitate pro-active, automated and load Xor, output-file output, compare-to Xor. cmp, output-list a%B 3. 1. 3 b%B 3. 1. 3 out%B 3. 1. 3; set a 0, set b 0, eval, output; replicable chip testing § Supplied with each chip definition § Using script commands, can effect anything that can be done interactively § Written in a simple language described in Appendix A of the book set a 0, set b 1, eval, output; | | | a 0 0 1 1 § A test script can contain commands that create an output file that records the results of the chip test | | | b 0 1 Hardware Simulator Tutorial | | | out 0 1 1 0 | | | § If a compare file is supplied, the simulator will compare the generated outputs to the desired outputs, line by line. Tutorial Index Slide 15

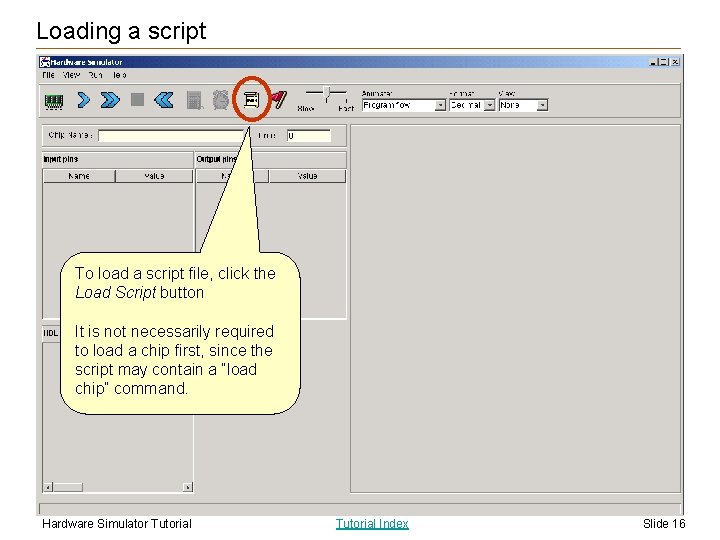

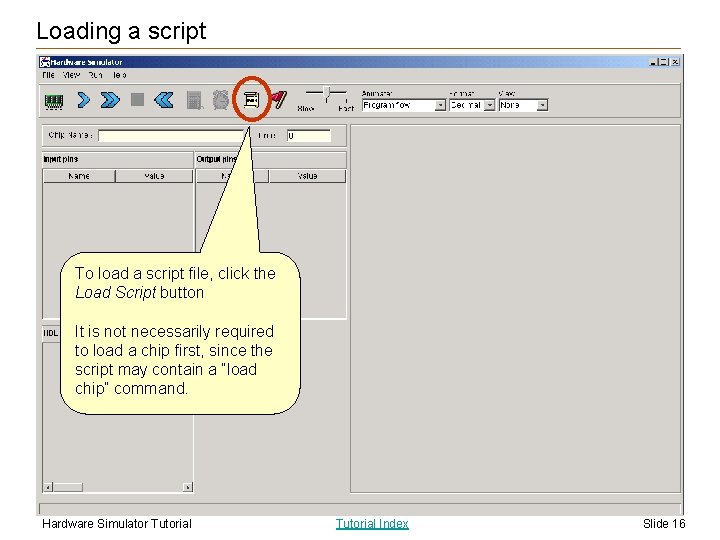

Loading a script To load a script file, click the Load Script button It is not necessarily required to load a chip first, since the script may contain a “load chip” command. Hardware Simulator Tutorial Index Slide 16

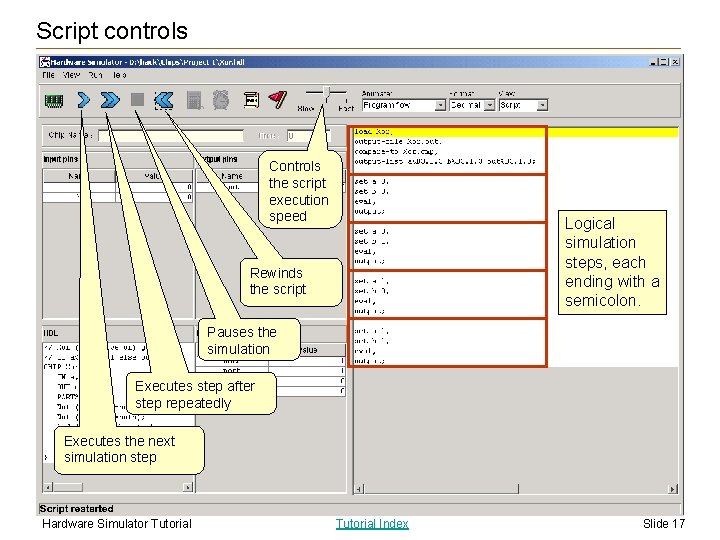

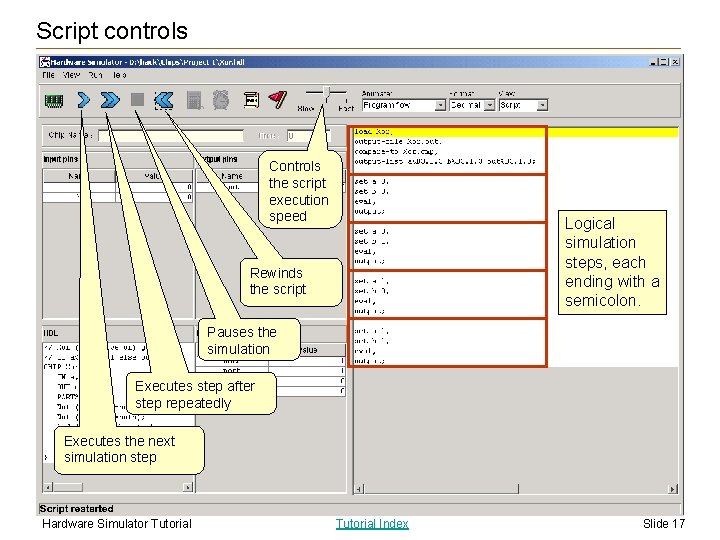

Script controls Controls the script execution speed Logical simulation steps, each ending with a semicolon. Rewinds the script Pauses the simulation Executes step after step repeatedly Executes the next simulation step Hardware Simulator Tutorial Index Slide 17

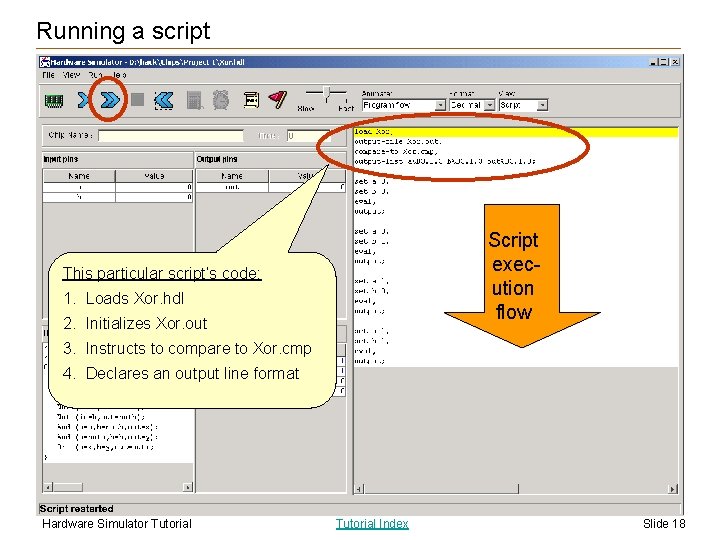

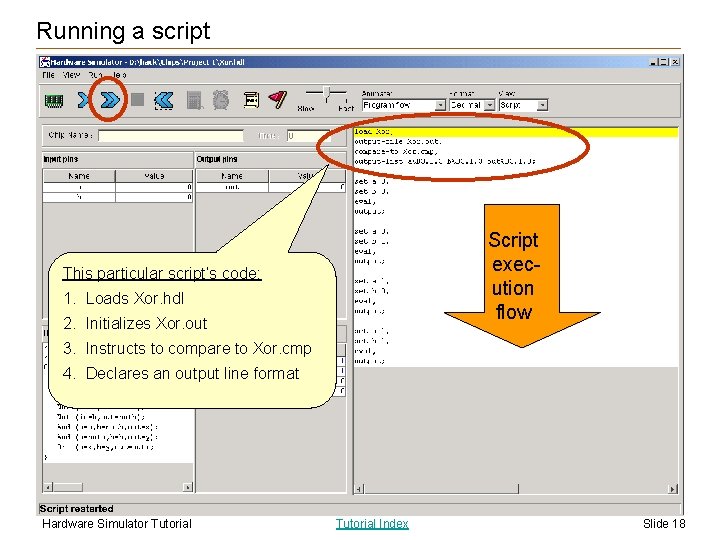

Running a script Script execution flow This particular script’s code: 1. Loads Xor. hdl 2. Initializes Xor. out 3. Instructs to compare to Xor. cmp 4. Declares an output line format Hardware Simulator Tutorial Index Slide 18

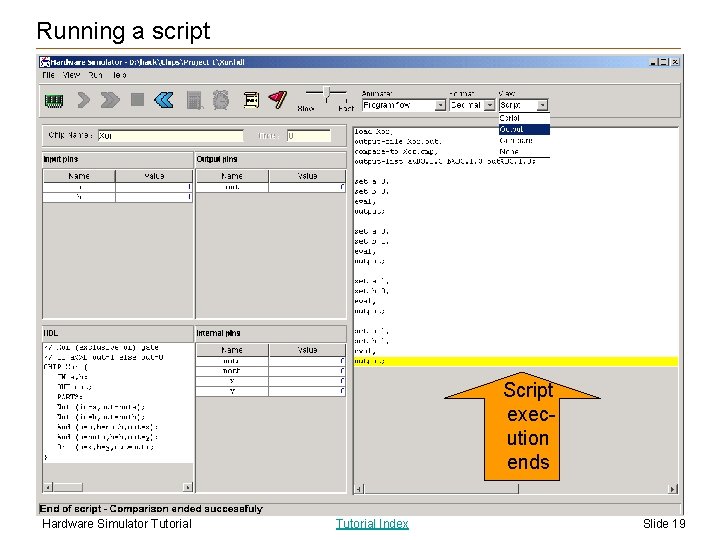

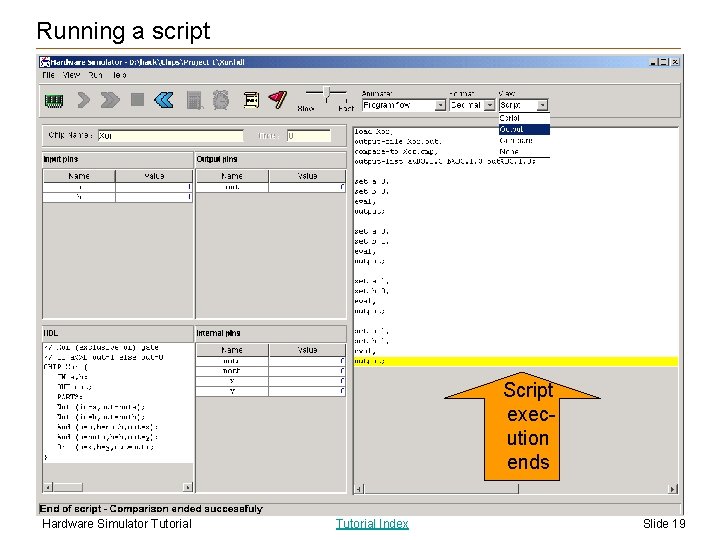

Running a script Script execution ends Hardware Simulator Tutorial Index Slide 19

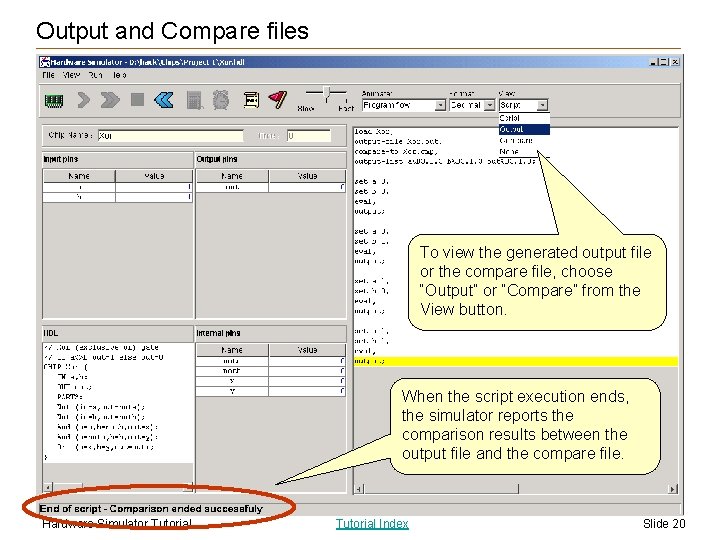

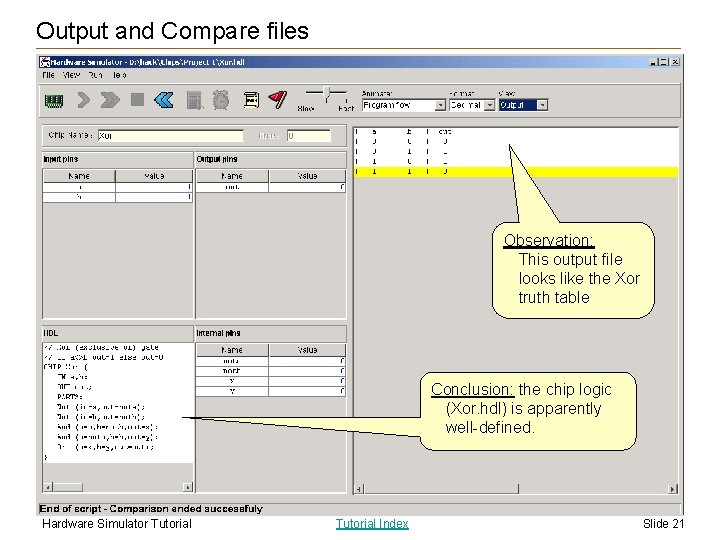

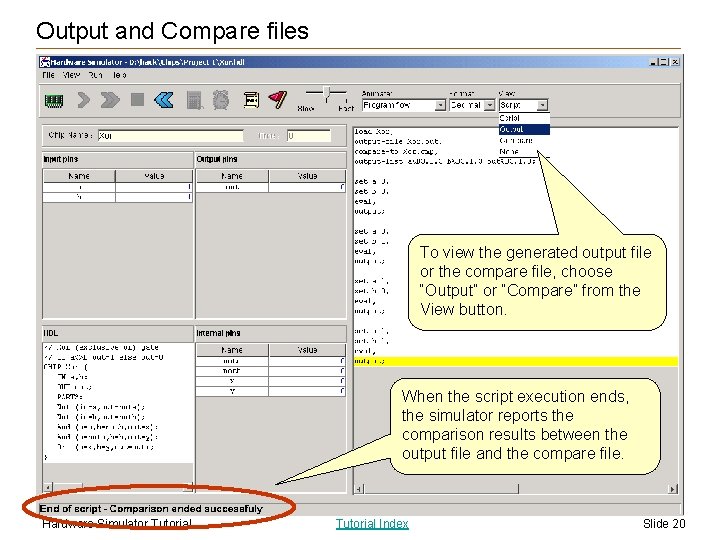

Output and Compare files To view the generated output file or the compare file, choose “Output” or “Compare” from the View button. When the script execution ends, the simulator reports the comparison results between the output file and the compare file. Hardware Simulator Tutorial Index Slide 20

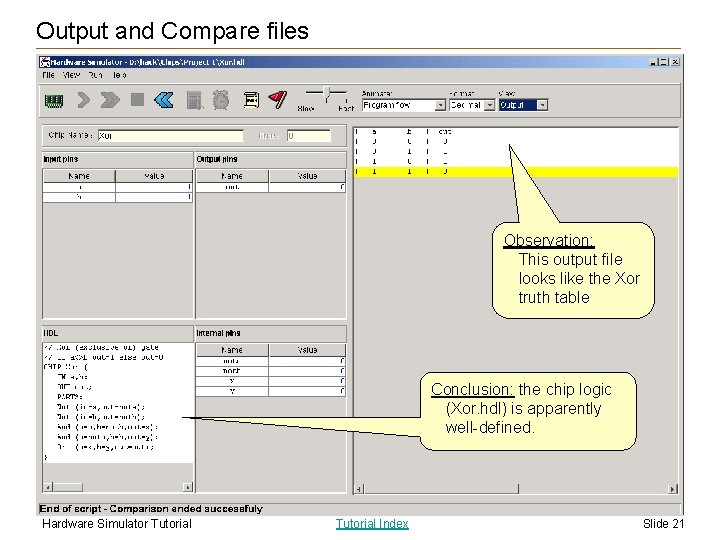

Output and Compare files Observation: This output file looks like the Xor truth table Conclusion: the chip logic (Xor. hdl) is apparently well-defined. Hardware Simulator Tutorial Index Slide 21

Hardware Simulation Tutorial Part III: Built-in Chips Hardware Simulator Tutorial Index Slide 22

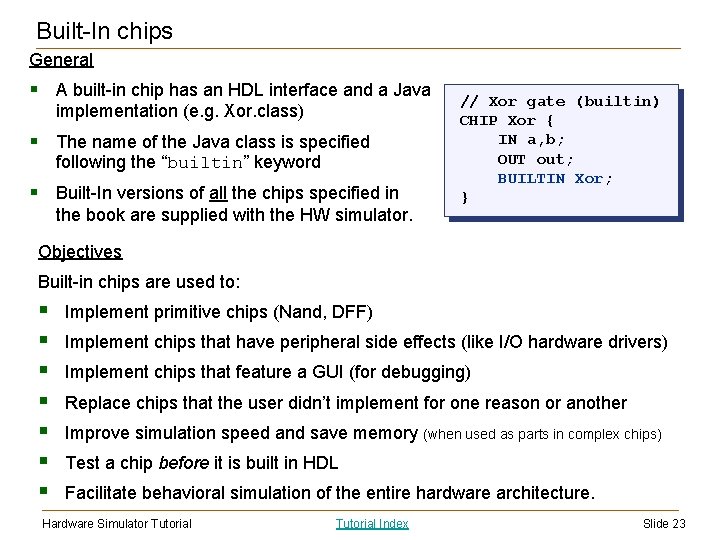

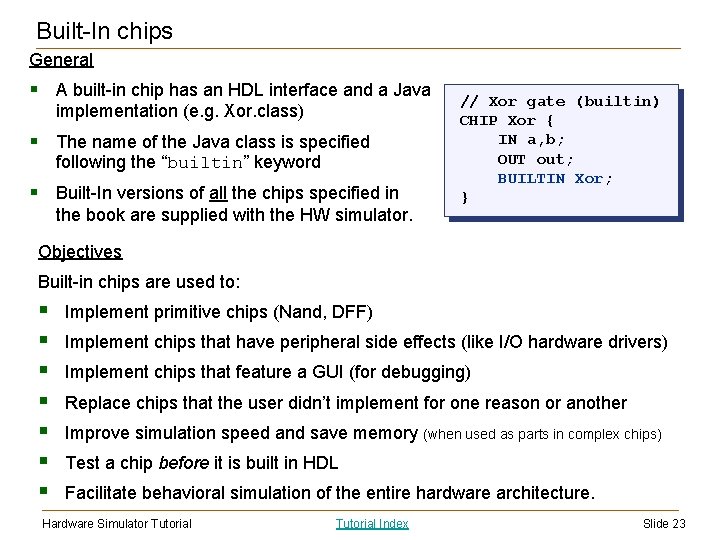

Built-In chips General § A built-in chip has an HDL interface and a Java implementation (e. g. Xor. class) § The name of the Java class is specified following the “builtin” keyword § Built-In versions of all the chips specified in the book are supplied with the HW simulator. // Xor gate (builtin) CHIP Xor { IN a, b; OUT out; BUILTIN Xor; } Objectives Built-in chips are used to: § § § § Implement primitive chips (Nand, DFF) Implement chips that have peripheral side effects (like I/O hardware drivers) Implement chips that feature a GUI (for debugging) Replace chips that the user didn’t implement for one reason or another Improve simulation speed and save memory (when used as parts in complex chips) Test a chip before it is built in HDL Facilitate behavioral simulation of the entire hardware architecture. Hardware Simulator Tutorial Index Slide 23

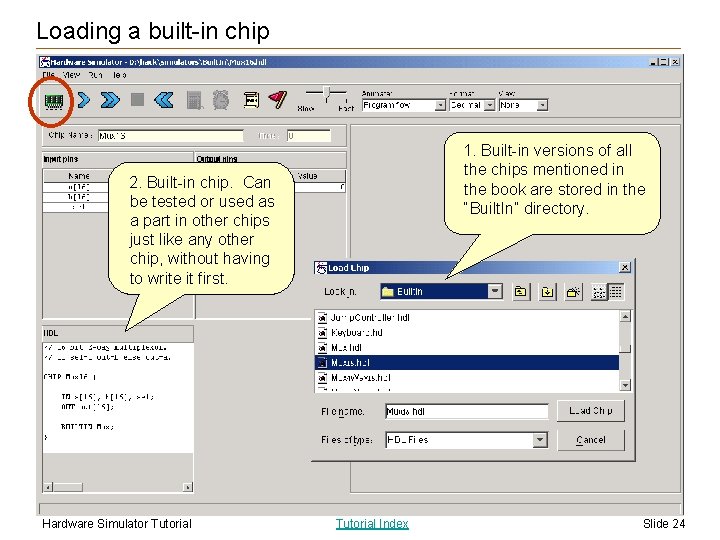

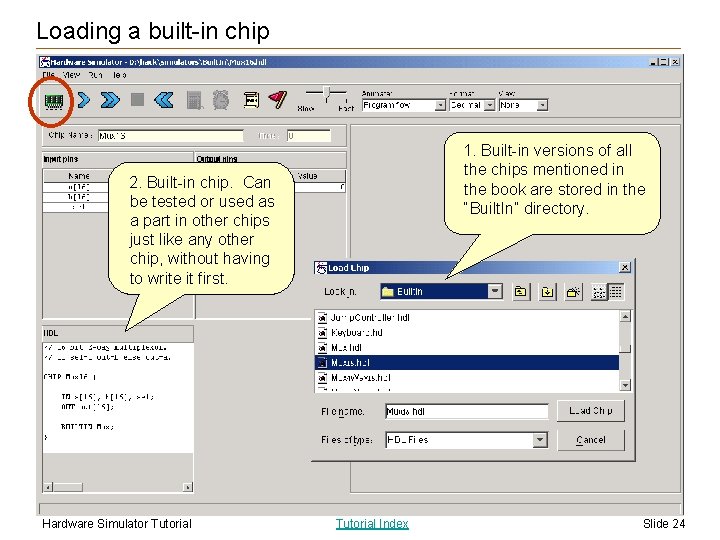

Loading a built-in chip 1. Built-in versions of all the chips mentioned in the book are stored in the “Built. In” directory. 2. Built-in chip. Can be tested or used as a part in other chips just like any other chip, without having to write it first. Hardware Simulator Tutorial Index Slide 24

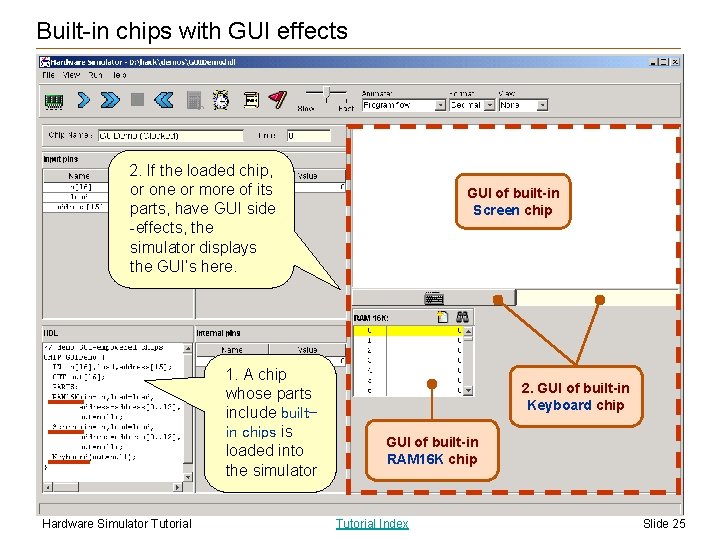

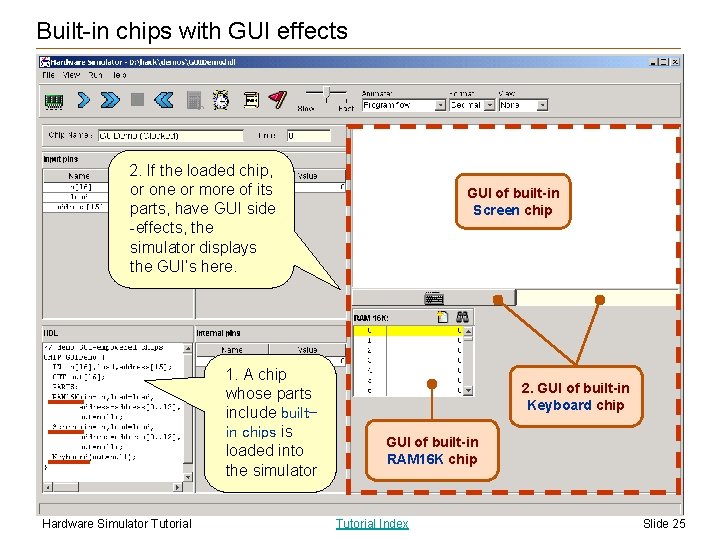

Built-in chips with GUI effects 2. If the loaded chip, or one or more of its parts, have GUI side -effects, the simulator displays the GUI’s here. 1. A chip whose parts include builtin chips is loaded into the simulator Hardware Simulator Tutorial GUI of built-in Screen chip 2. GUI of built-in Keyboard chip GUI of built-in RAM 16 K chip Tutorial Index Slide 25

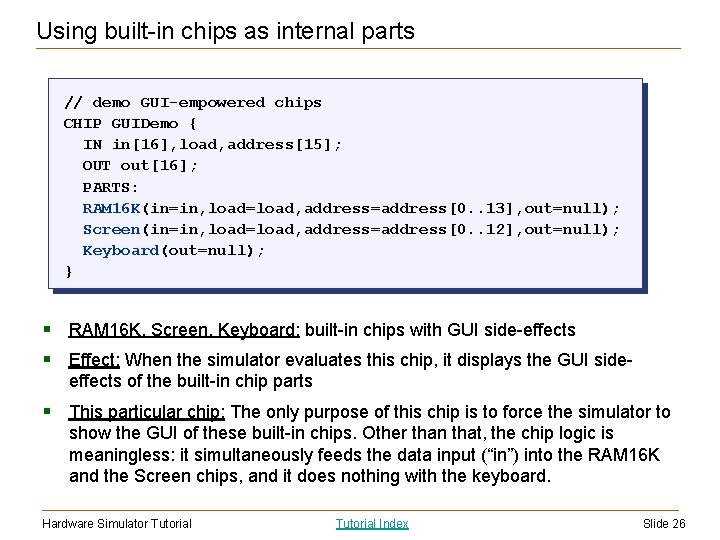

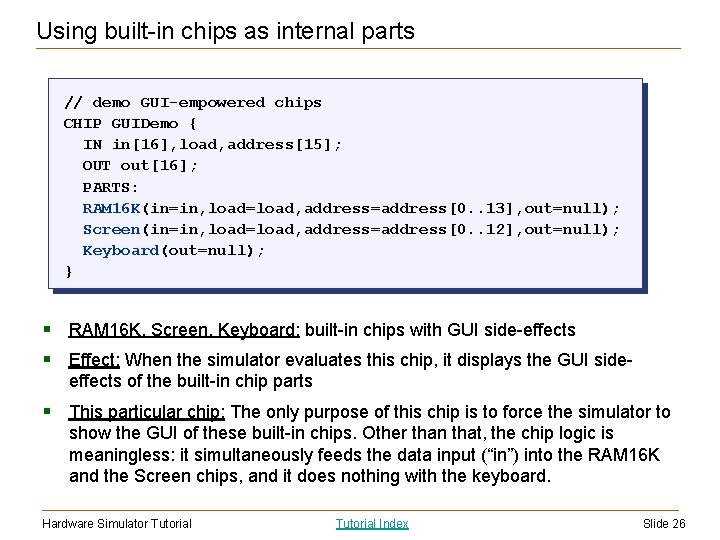

Using built-in chips as internal parts // demo GUI-empowered chips CHIP GUIDemo { IN in[16], load, address[15]; OUT out[16]; PARTS: RAM 16 K(in=in, load=load, address=address[0. . 13], out=null); Screen(in=in, load=load, address=address[0. . 12], out=null); Keyboard(out=null); } § RAM 16 K, Screen, Keyboard: built-in chips with GUI side-effects § Effect: When the simulator evaluates this chip, it displays the GUI sideeffects of the built-in chip parts § This particular chip: The only purpose of this chip is to force the simulator to show the GUI of these built-in chips. Other than that, the chip logic is meaningless: it simultaneously feeds the data input (“in”) into the RAM 16 K and the Screen chips, and it does nothing with the keyboard. Hardware Simulator Tutorial Index Slide 26

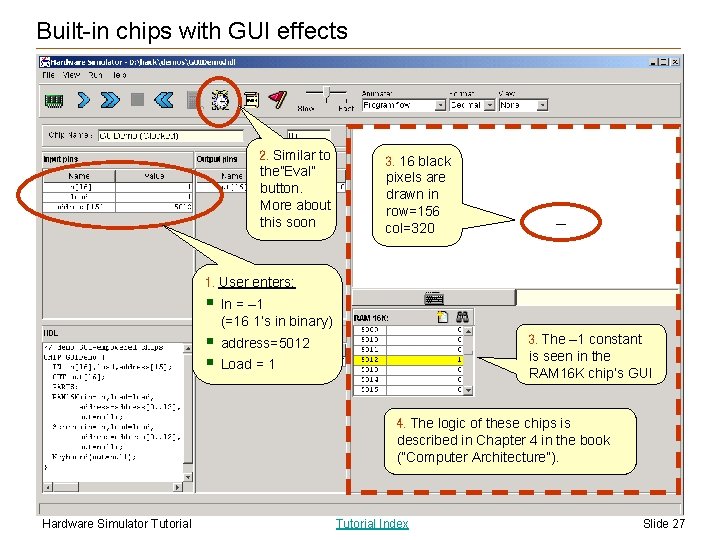

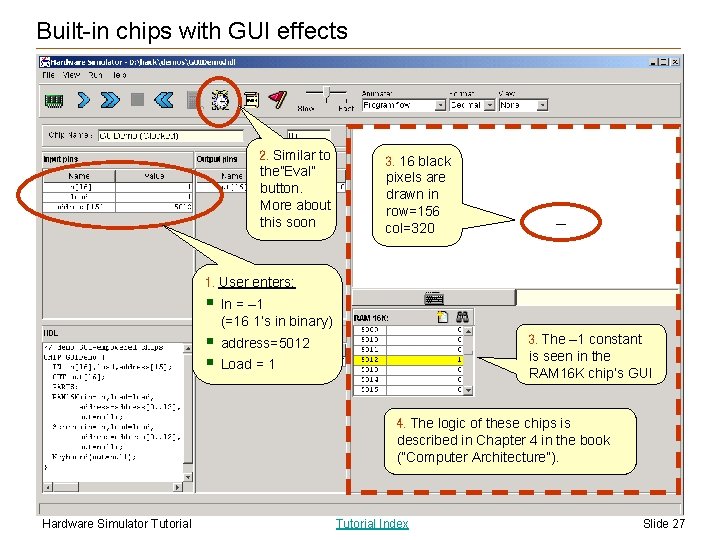

Built-in chips with GUI effects 2. Similar to the”Eval” button. More about this soon 3. 16 black pixels are drawn in row=156 col=320 1. User enters: § In = – 1 (=16 1’s in binary) § § address=5012 3. The – 1 constant is seen in the RAM 16 K chip’s GUI Load = 1 4. The logic of these chips is described in Chapter 4 in the book (“Computer Architecture”). Hardware Simulator Tutorial Index Slide 27

Hardware Simulation Tutorial Part IV: Clocked Chips (Sequential Logic) Hardware Simulator Tutorial Index Slide 28

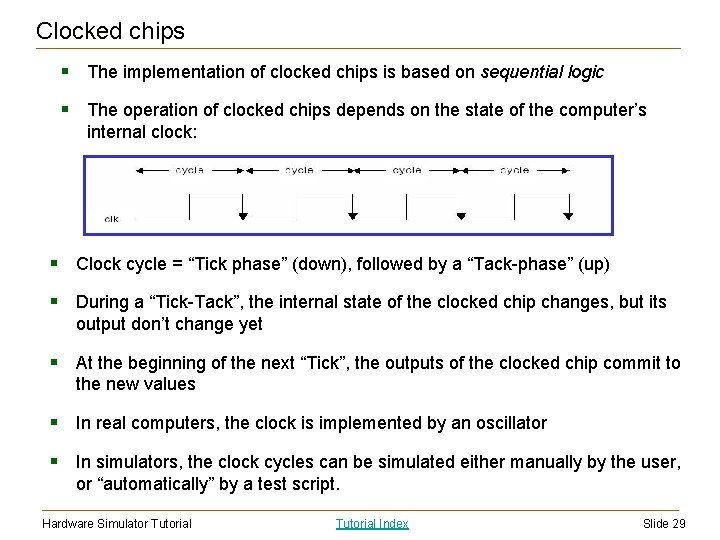

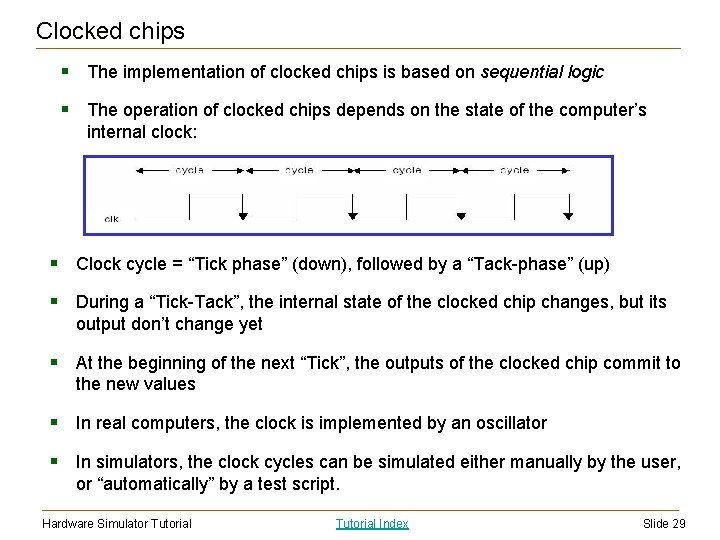

Clocked chips § The implementation of clocked chips is based on sequential logic § The operation of clocked chips depends on the state of the computer’s internal clock: § Clock cycle = “Tick phase” (down), followed by a “Tack-phase” (up) § During a “Tick-Tack”, the internal state of the clocked chip changes, but its output don’t change yet § At the beginning of the next “Tick”, the outputs of the clocked chip commit to the new values § In real computers, the clock is implemented by an oscillator § In simulators, the clock cycles can be simulated either manually by the user, or “automatically” by a test script. Hardware Simulator Tutorial Index Slide 29

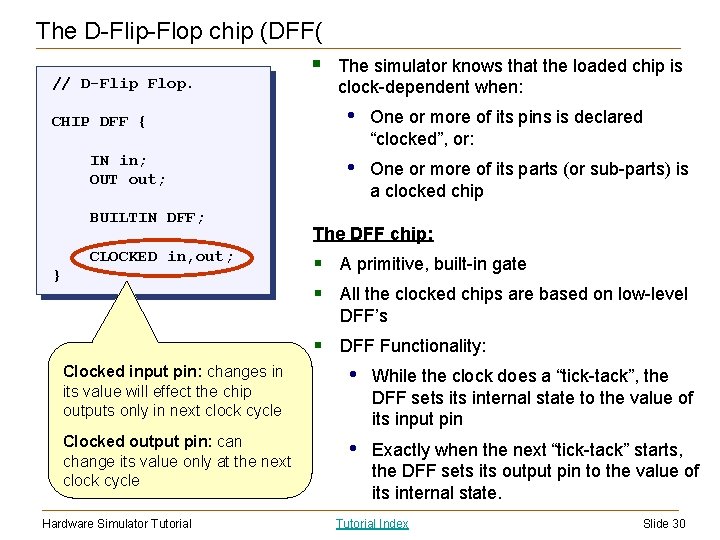

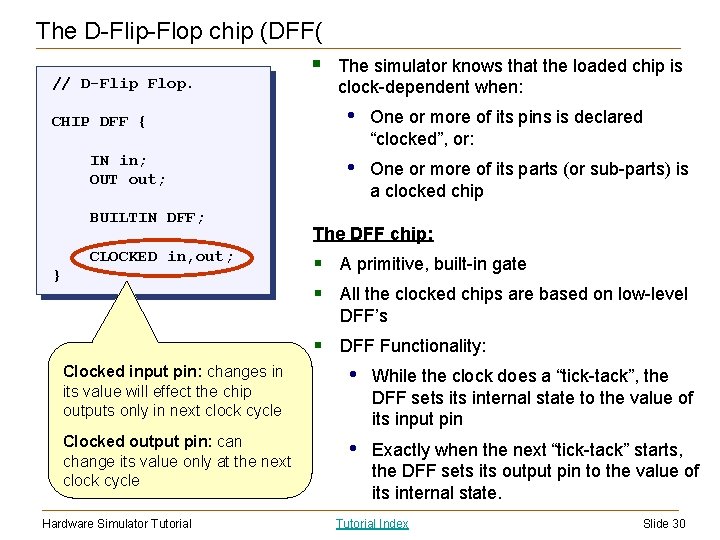

The D-Flip-Flop chip (DFF( § // D-Flip Flop. CHIP DFF { IN in; OUT out; BUILTIN DFF; CLOCKED in, out; } The simulator knows that the loaded chip is clock-dependent when: • One or more of its pins is declared “clocked”, or: • One or more of its parts (or sub-parts) is a clocked chip The DFF chip: § A primitive, built-in gate § All the clocked chips are based on low-level DFF’s § DFF Functionality: Clocked input pin: changes in its value will effect the chip outputs only in next clock cycle • While the clock does a “tick-tack”, the DFF sets internal state to the value of its input pin Clocked output pin: can change its value only at the next clock cycle • Exactly when the next “tick-tack” starts, the DFF sets its output pin to the value of its internal state. Hardware Simulator Tutorial Index Slide 30

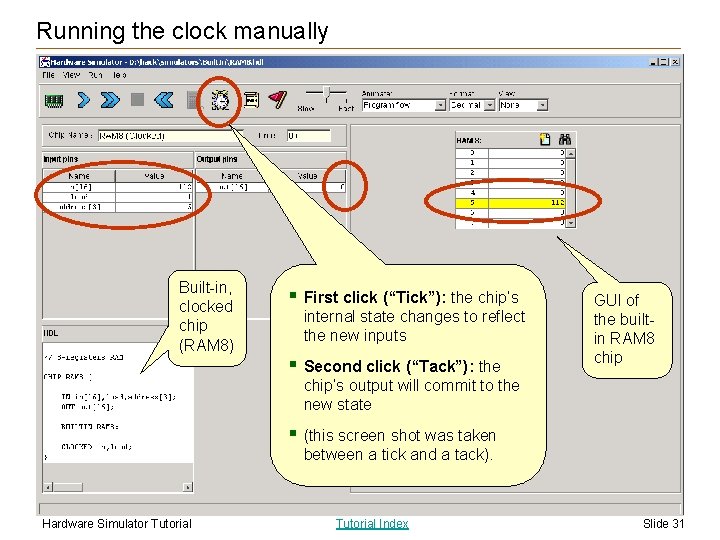

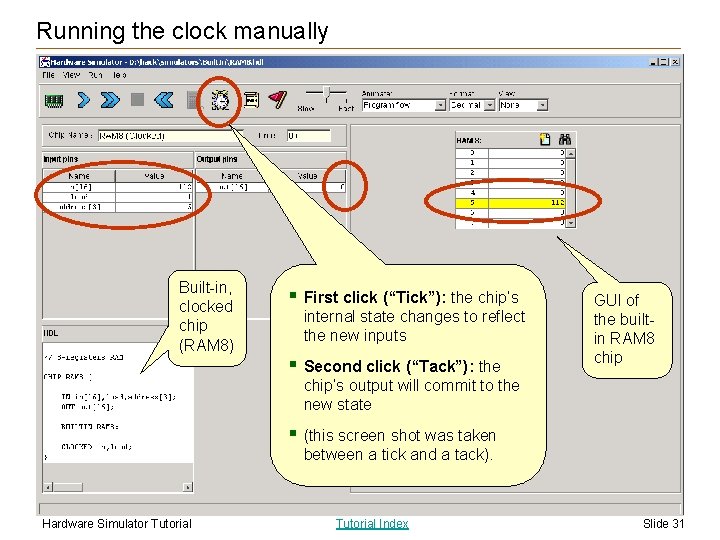

Running the clock manually Built-in, clocked chip (RAM 8) § First click (“Tick”): the chip’s internal state changes to reflect the new inputs § Second click (“Tack”): the GUI of the builtin RAM 8 chip’s output will commit to the new state § (this screen shot was taken between a tick and a tack). Hardware Simulator Tutorial Index Slide 31

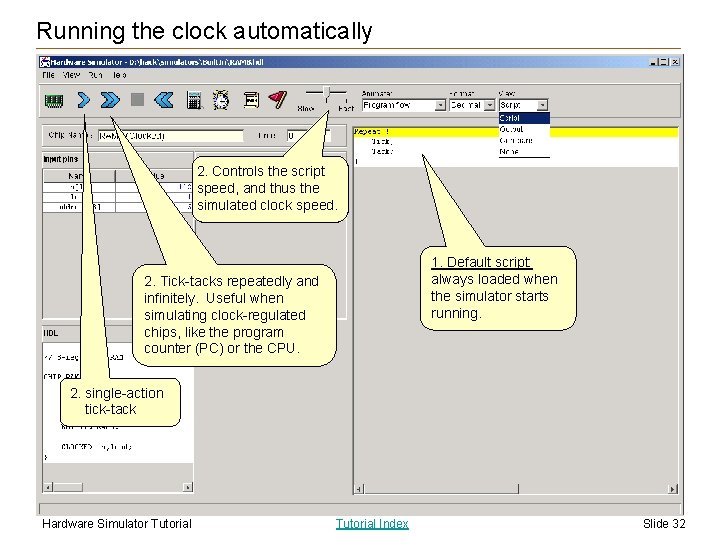

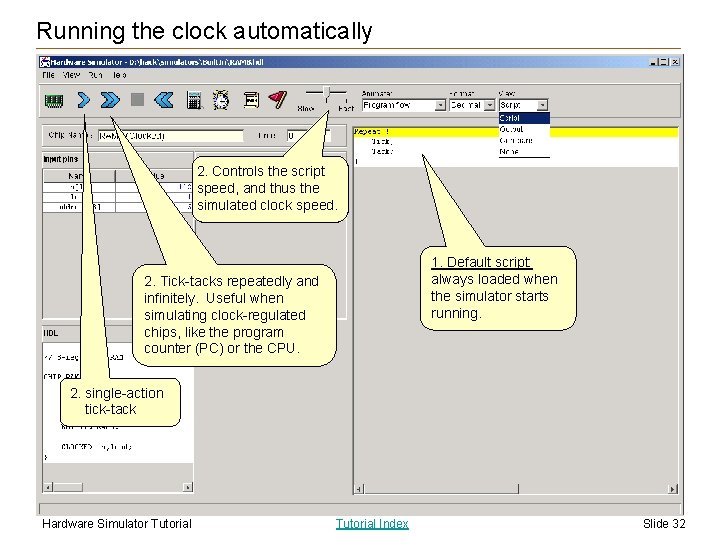

Running the clock automatically 2. Controls the script speed, and thus the simulated clock speed. 1. Default script: always loaded when the simulator starts running. 2. Tick-tacks repeatedly and infinitely. Useful when simulating clock-regulated chips, like the program counter (PC) or the CPU. 2. single-action tick-tack Hardware Simulator Tutorial Index Slide 32

Hardware Simulation Tutorial Part V: Debugging tools Hardware Simulator Tutorial Index Slide 33

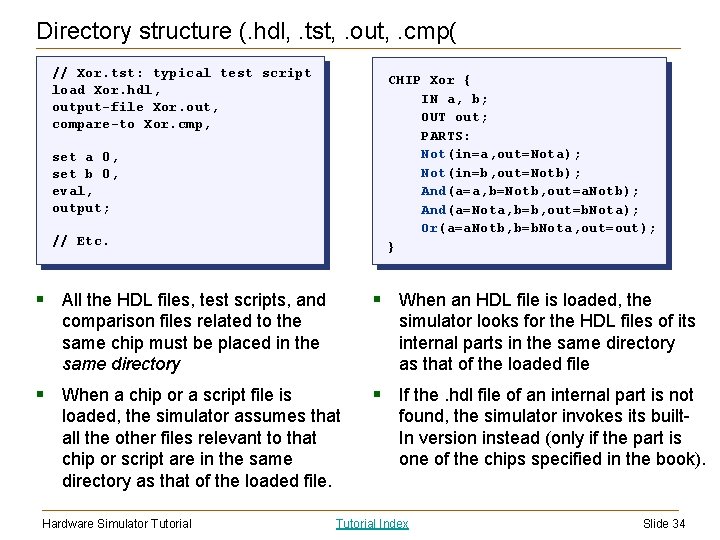

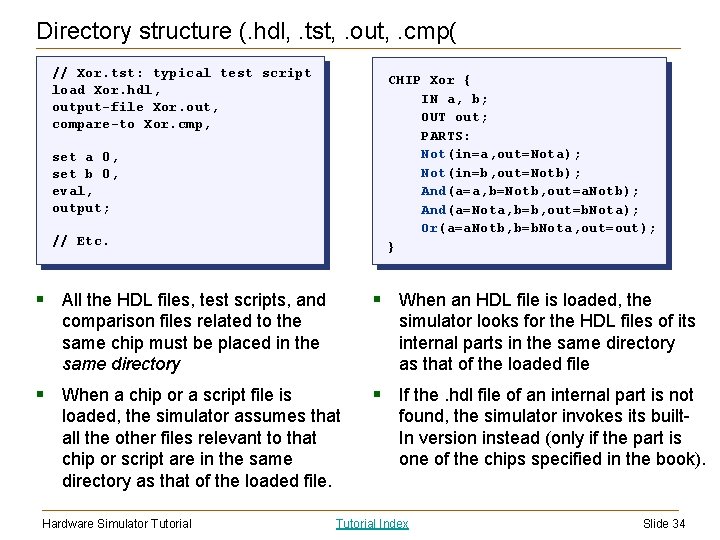

Directory structure (. hdl, . tst, . out, . cmp( // Xor. tst: typical test script load Xor. hdl, output-file Xor. out, compare-to Xor. cmp, CHIP Xor { IN a, b; OUT out; PARTS: Not(in=a, out=Nota); Not(in=b, out=Notb); And(a=a, b=Notb, out=a. Notb); And(a=Nota, b=b, out=b. Nota); Or(a=a. Notb, b=b. Nota, out=out); } set a 0, set b 0, eval, output; // Etc. § All the HDL files, test scripts, and § When an HDL file is loaded, the comparison files related to the same chip must be placed in the same directory simulator looks for the HDL files of its internal parts in the same directory as that of the loaded file § When a chip or a script file is § If the. hdl file of an internal part is not loaded, the simulator assumes that all the other files relevant to that chip or script are in the same directory as that of the loaded file. Hardware Simulator Tutorial found, the simulator invokes its built. In version instead (only if the part is one of the chips specified in the book). Tutorial Index Slide 34

System variables The simulator recognizes and maintains the values of the following variables: § Time: the number of time-units (clock-cycles) that elapsed since the script started running is stored in the variable time § Pins: the values of all the input, output, and internal pins of the simulated chip are accessible as variables, using their HDL names, e. g. a, b, out, Nota, Notb, etc. in the case of the Xor implementation presented earlier in this tutorial § GUI elements: the values stored in the contents of built-in chips with GUI can be accessed via variables with proper names. For example, the value of register 3 of the RAM 8 chip can be accessed via RAM 8[3]. These variables can be used in scripts and breakpoints, for debugging. Hardware Simulator Tutorial Index Slide 35

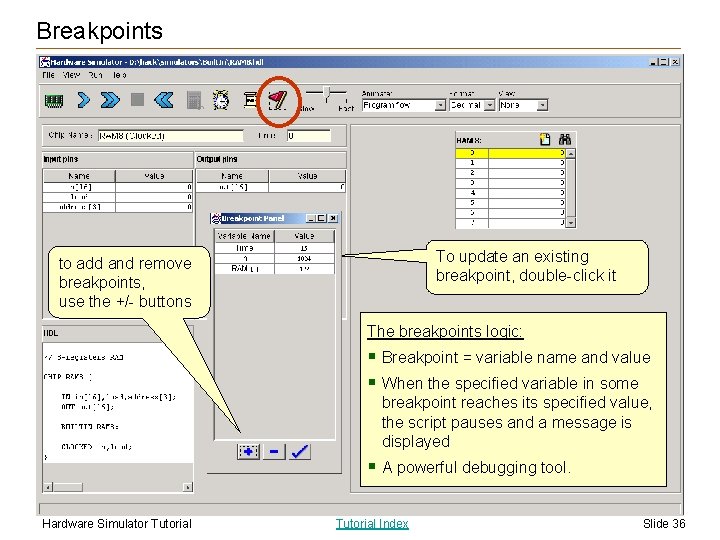

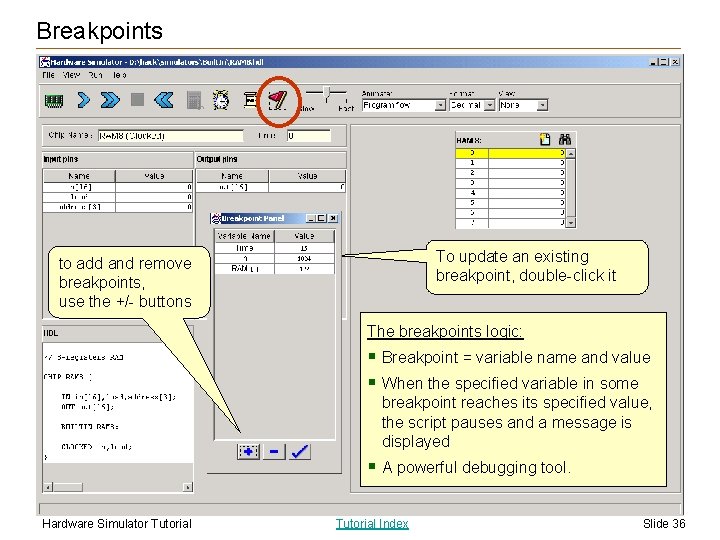

Breakpoints To update an existing breakpoint, double-click it to add and remove breakpoints, use the +/- buttons The breakpoints logic: § Breakpoint = variable name and value § When the specified variable in some breakpoint reaches its specified value, the script pauses and a message is displayed § A powerful debugging tool. Hardware Simulator Tutorial Index Slide 36

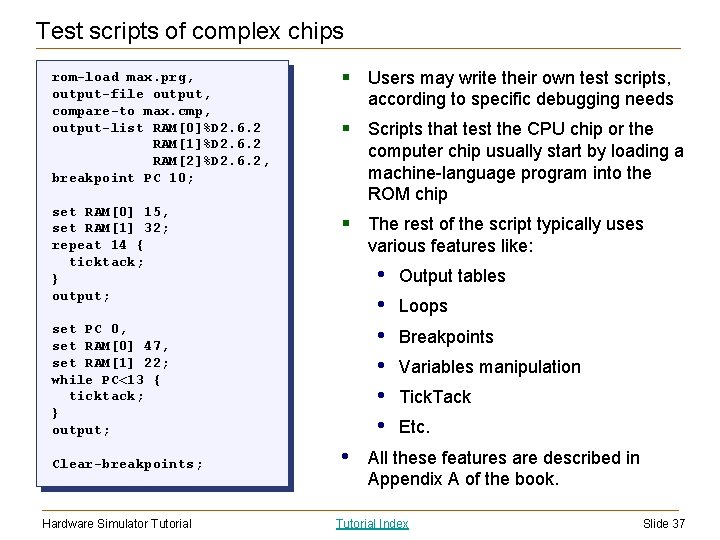

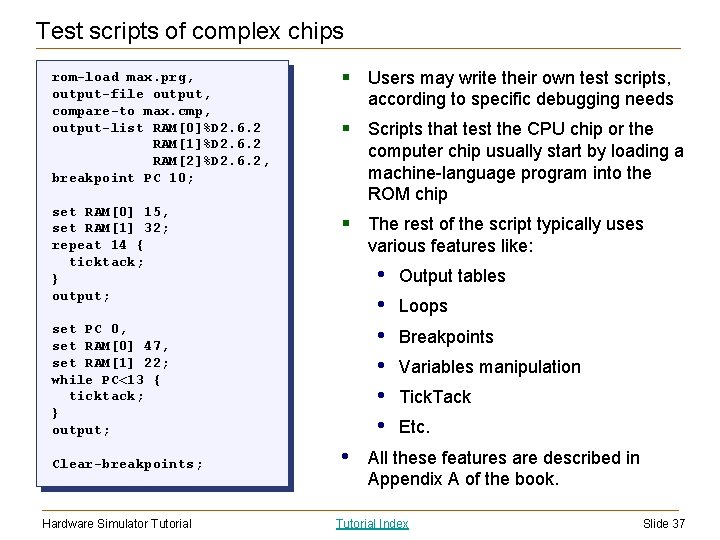

Test scripts of complex chips rom-load max. prg, output-file output, compare-to max. cmp, output-list RAM[0]%D 2. 6. 2 RAM[1]%D 2. 6. 2 RAM[2]%D 2. 6. 2, breakpoint PC 10; set RAM[0] 15, set RAM[1] 32; repeat 14 { ticktack; } output; § Users may write their own test scripts, according to specific debugging needs § Scripts that test the CPU chip or the computer chip usually start by loading a machine-language program into the ROM chip § The rest of the script typically uses various features like: • • • set PC 0, set RAM[0] 47, set RAM[1] 22; while PC<13 { ticktack; } output; Clear-breakpoints; Hardware Simulator Tutorial • Output tables Loops Breakpoints Variables manipulation Tick. Tack Etc. All these features are described in Appendix A of the book. Tutorial Index Slide 37

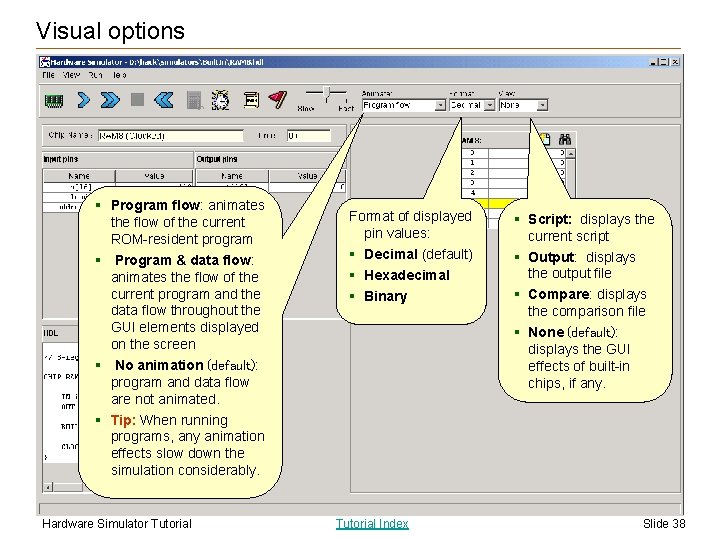

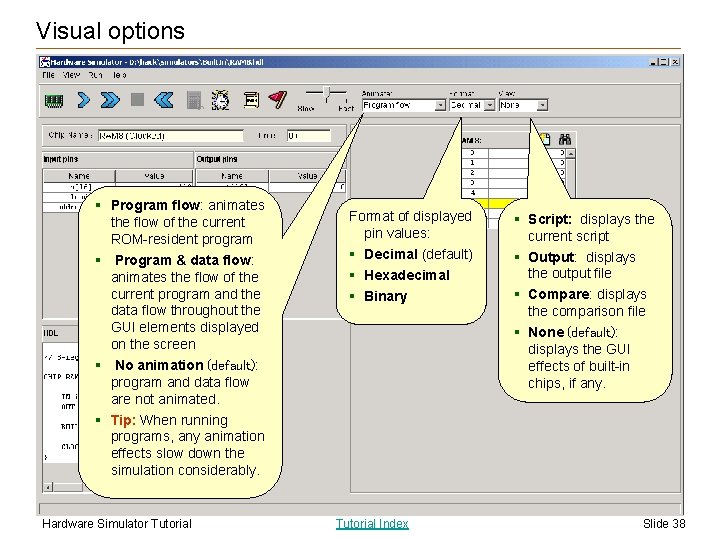

Visual options § Program flow: animates the flow of the current ROM-resident program § Program & data flow: animates the flow of the current program and the data flow throughout the GUI elements displayed on the screen § No animation (default): program and data flow are not animated. § Tip: When running programs, any animation effects slow down the simulation considerably. Hardware Simulator Tutorial Format of displayed pin values: § Script: displays the § Decimal (default) § Hexadecimal § Binary § Output: displays the output file § Compare: displays the comparison file § None (default): displays the GUI effects of built-in chips, if any. Tutorial Index current script Slide 38

Postscript: H. D. Thoreau about chips, bugs, and close observation: I was surprised to find that the chips were covered with such combatants, that it was not a duellum, but a bellum, a war between two races of ants, the red always pitted against the black, and frequently two red ones to one black. The legions of these Myrmidons covered all the hills and vales in my wood-yard, and the ground was already strewn with the dead and dying, both red and black. It was the only battle which I have ever witnessed, the only battlefield I ever trod while the battle was raging; internecine war; the red republicans on the one hand, and the black imperialists on the other. On every side they were engaged in deadly combat, yet without any noise that I could hear, and human soldiers never fought so resolutely. . The more you think of it, the less the difference. And certainly there is not the fight recorded in Concord history, at least, if in the history of America, that will bear a moment’s comparison with this, whether for the numbers engaged in it, or for the patriotism and heroism displayed. From “Brute Neighbors, ” Walden (1854). Hardware Simulator Tutorial Index Slide 39