Hardware languages Programminglanguage for modelling of digital hardware

- Slides: 6

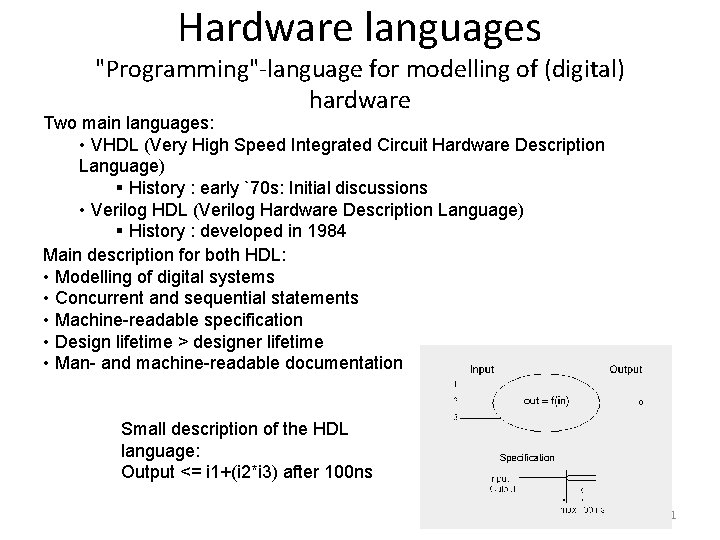

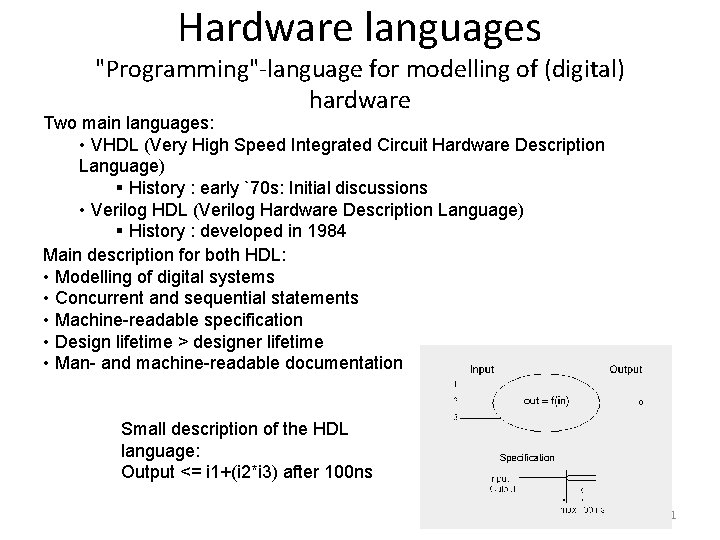

Hardware languages "Programming"-language for modelling of (digital) hardware Two main languages: • VHDL (Very High Speed Integrated Circuit Hardware Description Language) § History : early `70 s: Initial discussions • Verilog HDL (Verilog Hardware Description Language) § History : developed in 1984 Main description for both HDL: • Modelling of digital systems • Concurrent and sequential statements • Machine-readable specification • Design lifetime > designer lifetime • Man- and machine-readable documentation Small description of the HDL language: Output <= i 1+(i 2*i 3) after 100 ns 1

VHDL structural elements • Entity : Interface (1) • Architecture : Implementation, behaviour, function (2) • Configuration : Model chaining, structure, hierarchy • Process : Concurrency, event controlled (2) • Package : Modular design, standard solution, data types, constants • Library : Compilation, object code 2

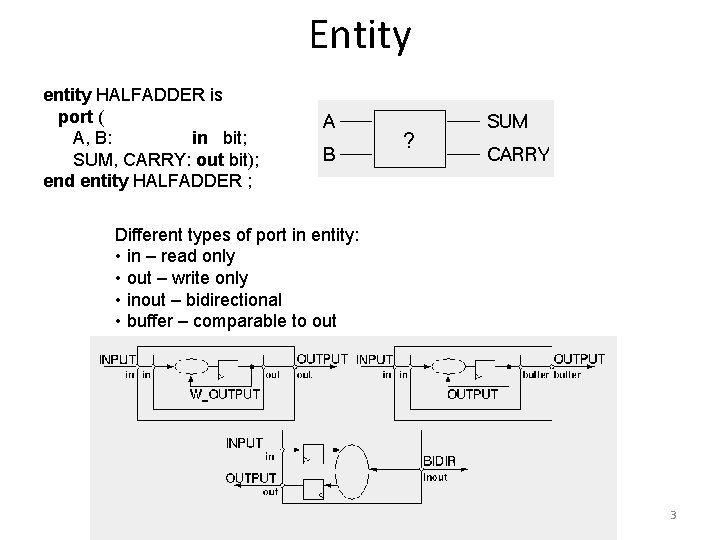

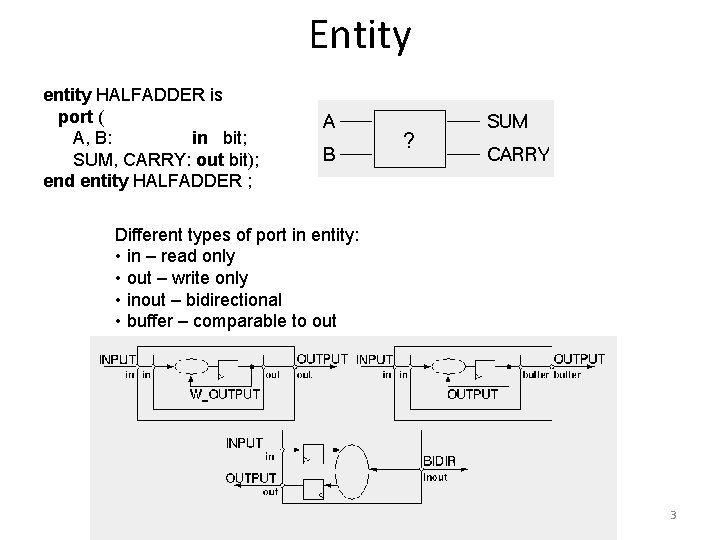

Entity entity HALFADDER is port ( A, B: in bit; SUM, CARRY: out bit); end entity HALFADDER ; Different types of port in entity: • in – read only • out – write only • inout – bidirectional • buffer – comparable to out 3

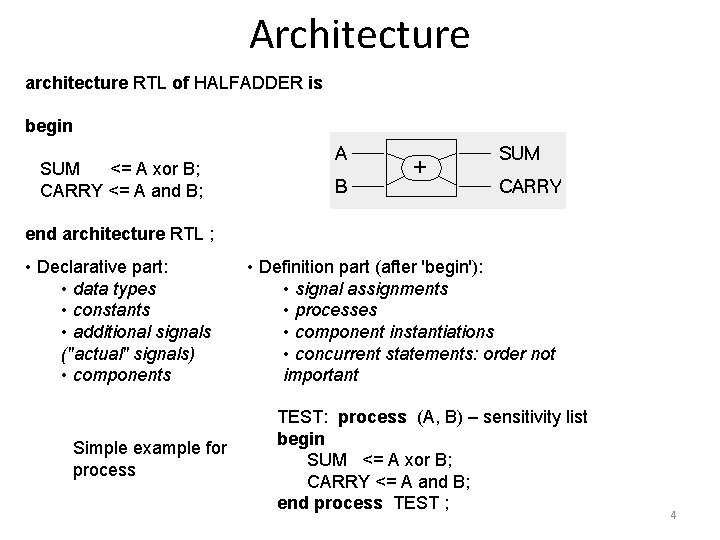

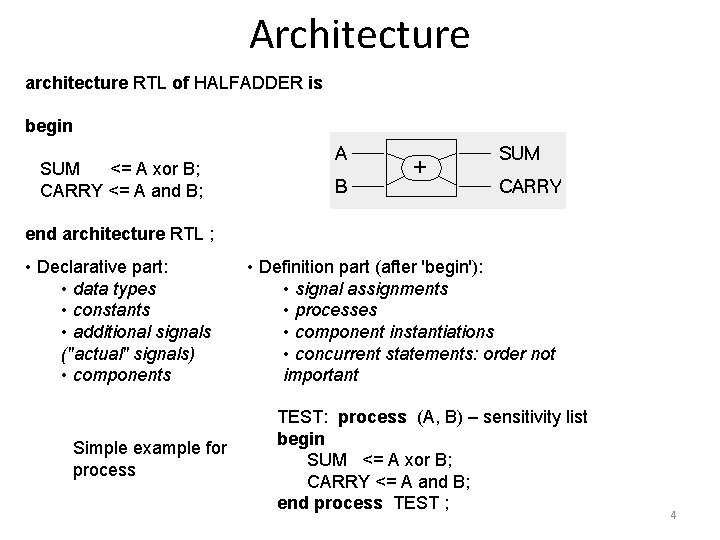

Architecture architecture RTL of HALFADDER is begin SUM <= A xor B; CARRY <= A and B; end architecture RTL ; • Declarative part: • data types • constants • additional signals ("actual" signals) • components Simple example for process • Definition part (after 'begin'): • signal assignments • processes • component instantiations • concurrent statements: order not important TEST: process (A, B) – sensitivity list begin SUM <= A xor B; CARRY <= A and B; end process TEST ; 4

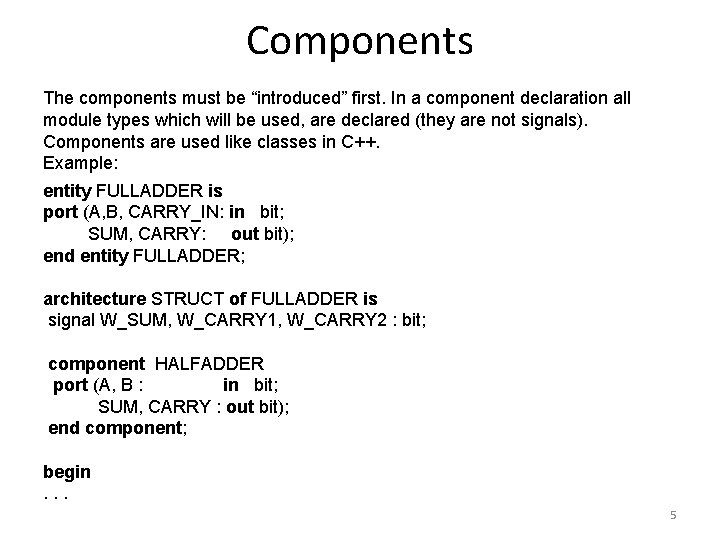

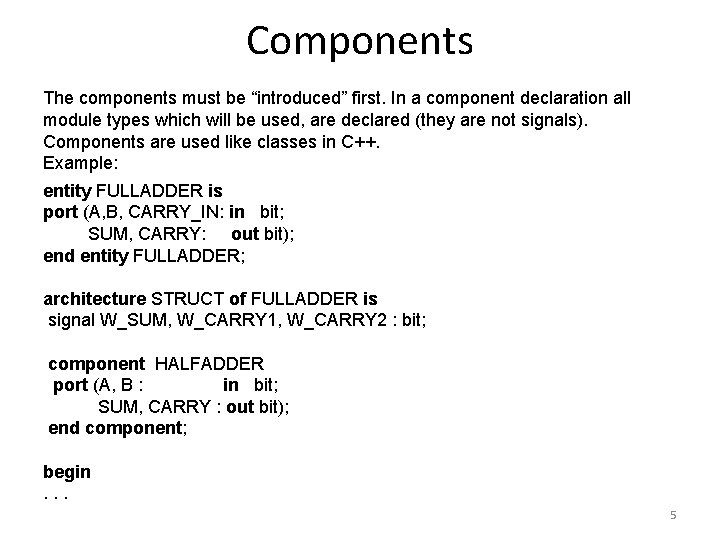

Components The components must be “introduced” first. In a component declaration all module types which will be used, are declared (they are not signals). Components are used like classes in C++. Example: entity FULLADDER is port (A, B, CARRY_IN: in bit; SUM, CARRY: out bit); end entity FULLADDER; architecture STRUCT of FULLADDER is signal W_SUM, W_CARRY 1, W_CARRY 2 : bit; component HALFADDER port (A, B : in bit; SUM, CARRY : out bit); end component; begin. . . 5

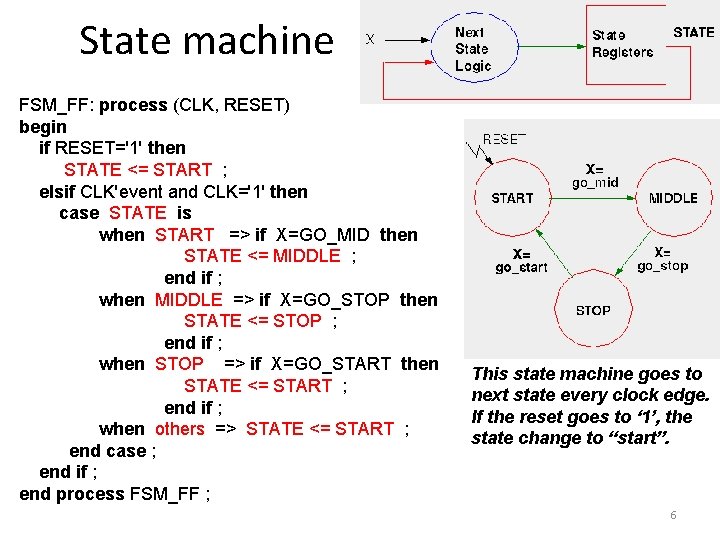

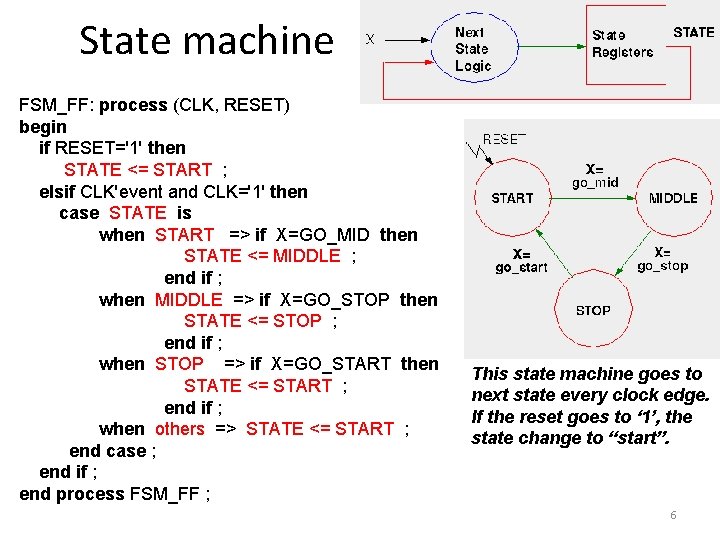

State machine FSM_FF: process (CLK, RESET) begin if RESET='1' then STATE <= START ; elsif CLK'event and CLK='1' then case STATE is when START => if X=GO_MID then STATE <= MIDDLE ; end if ; when MIDDLE => if X=GO_STOP then STATE <= STOP ; end if ; when STOP => if X=GO_START then STATE <= START ; end if ; when others => STATE <= START ; end case ; end if ; end process FSM_FF ; This state machine goes to next state every clock edge. If the reset goes to ‘ 1’, the state change to “start”. 6