Hardware Description Language HDL q What is the

![Dataflow Modeling q Uses continuous assignment statement Ø Format: assign [ delay ] net Dataflow Modeling q Uses continuous assignment statement Ø Format: assign [ delay ] net](https://slidetodoc.com/presentation_image/1e4e0ca318befa7e7bb84c53b39cce79/image-10.jpg)

![Data Types q Net Type: Wire wire [ msb : lsb ] wire 1, Data Types q Net Type: Wire wire [ msb : lsb ] wire 1,](https://slidetodoc.com/presentation_image/1e4e0ca318befa7e7bb84c53b39cce79/image-25.jpg)

![Memories q An array of registers reg [ msb : lsb ] memory 1 Memories q An array of registers reg [ msb : lsb ] memory 1](https://slidetodoc.com/presentation_image/1e4e0ca318befa7e7bb84c53b39cce79/image-27.jpg)

- Slides: 37

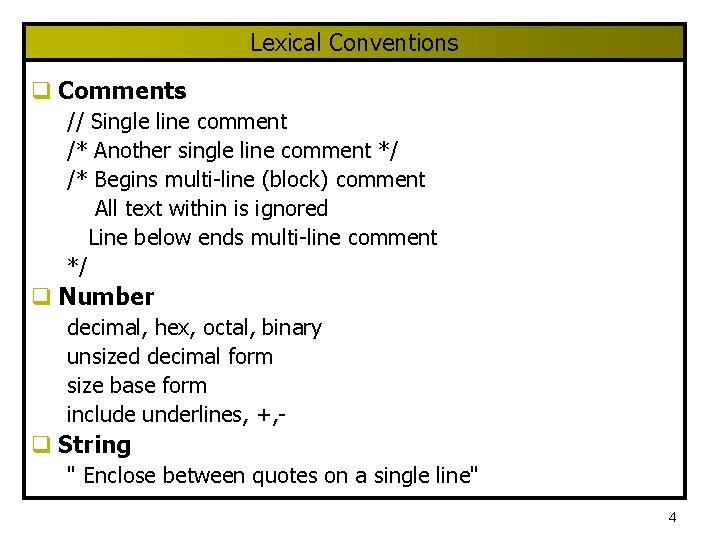

Hardware Description Language (HDL) q What is the need for Hardware Description Language? q Model, Represent, And Simulate Digital Hardware Ø Hardware Concurrency Ø Parallel Activity Flow Ø Semantics for Signal Value And Time q Special Constructs And Semantics Ø Edge Transitions Ø Propagation Delays Ø Timing Checks 1

VERILOG HDL q Basic Unit – A module q Module Ø Describes the functionality of the design Ø States the input and output ports q Example: A Computer Ø Functionality: Perform user defined computations Ø I/O Ports: Keyboard, Mouse, Monitor, Printer 2

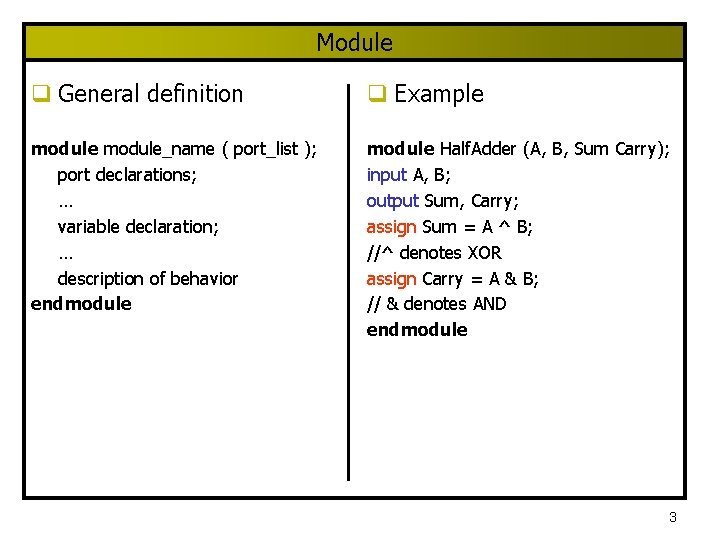

Module q General definition q Example module_name ( port_list ); port declarations; … variable declaration; … description of behavior endmodule Half. Adder (A, B, Sum Carry); input A, B; output Sum, Carry; assign Sum = A ^ B; //^ denotes XOR assign Carry = A & B; // & denotes AND endmodule 3

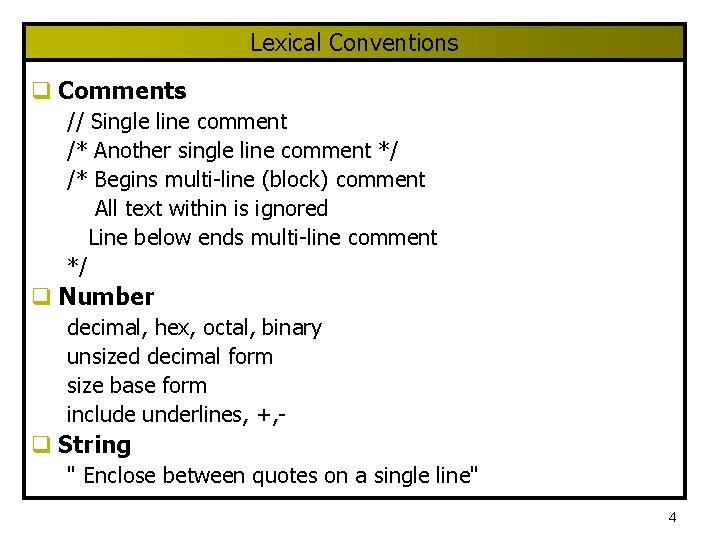

Lexical Conventions q Comments // Single line comment /* Another single line comment */ /* Begins multi-line (block) comment All text within is ignored Line below ends multi-line comment */ q Number decimal, hex, octal, binary unsized decimal form size base form include underlines, +, - q String " Enclose between quotes on a single line" 4

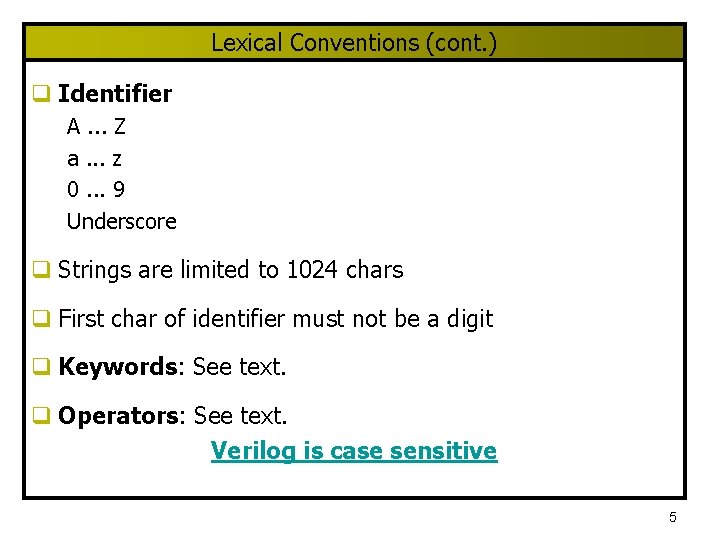

Lexical Conventions (cont. ) q Identifier A. . . Z a. . . z 0. . . 9 Underscore q Strings are limited to 1024 chars q First char of identifier must not be a digit q Keywords: See text. q Operators: See text. Verilog is case sensitive 5

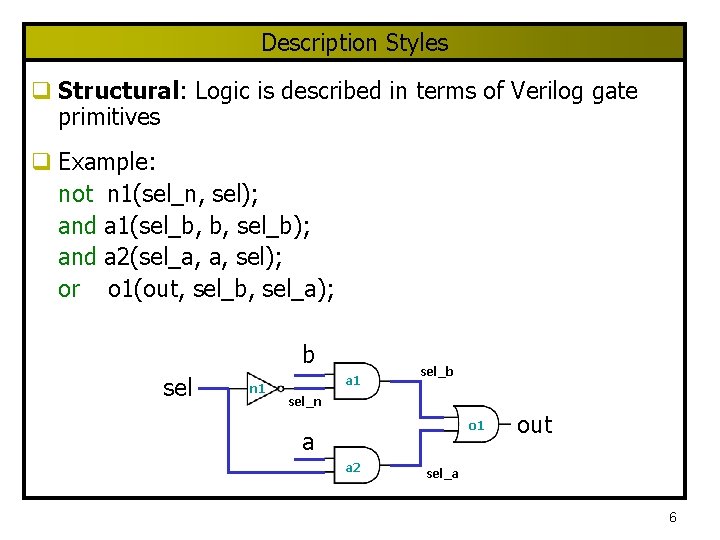

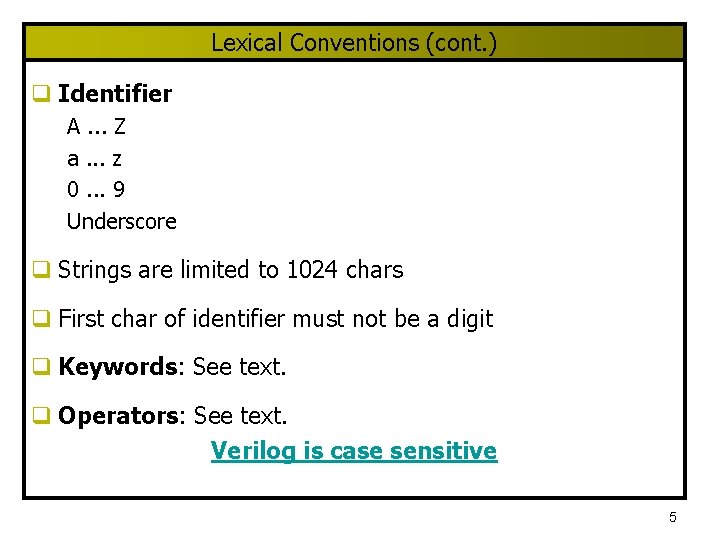

Description Styles q Structural: Logic is described in terms of Verilog gate primitives q Example: not n 1(sel_n, sel); and a 1(sel_b, b, sel_b); and a 2(sel_a, a, sel); or o 1(out, sel_b, sel_a); b sel n 1 a 1 sel_b sel_n o 1 a a 2 out sel_a 6

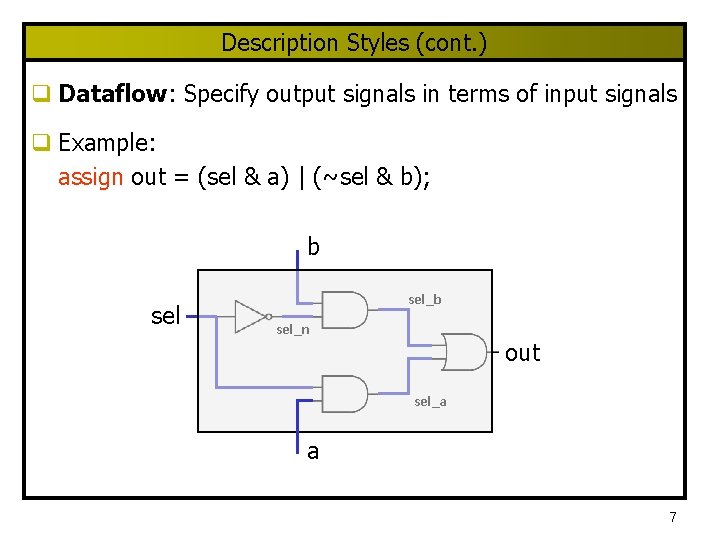

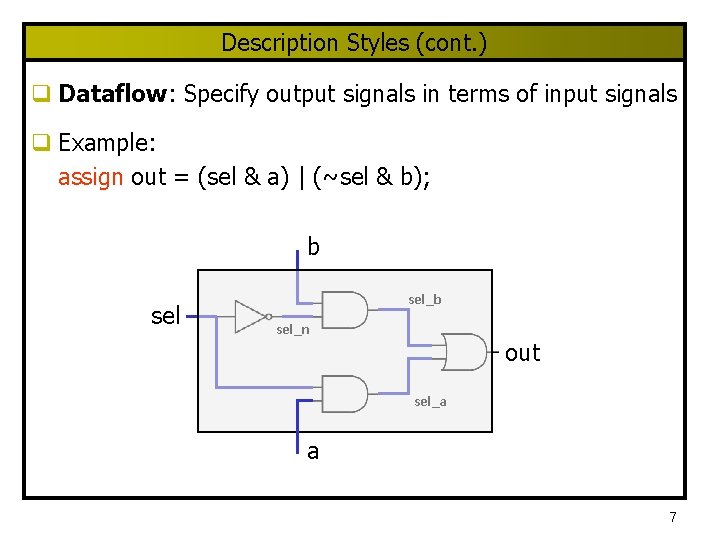

Description Styles (cont. ) q Dataflow: Specify output signals in terms of input signals q Example: assign out = (sel & a) | (~sel & b); b sel_b sel_n out sel_a a 7

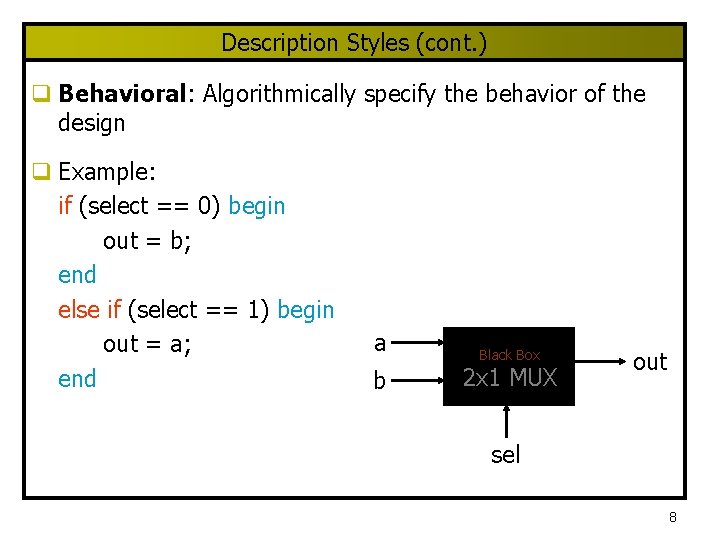

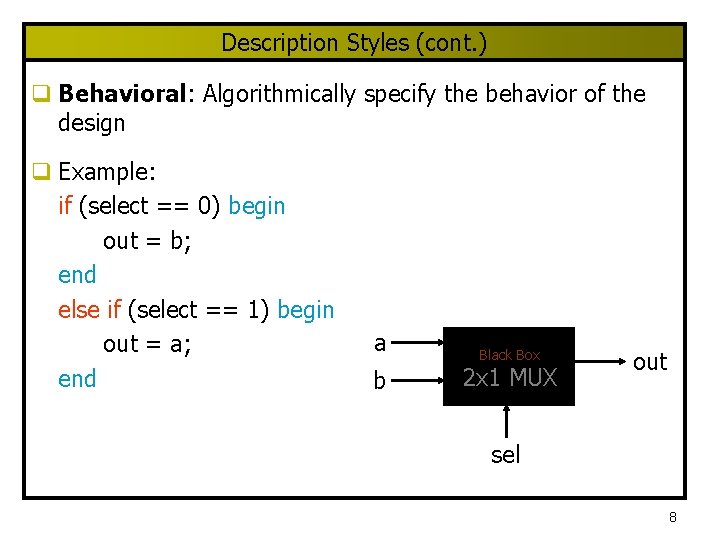

Description Styles (cont. ) q Behavioral: Algorithmically specify the behavior of the design q Example: if (select == 0) begin out = b; end else if (select == 1) begin out = a; end a b Black Box 2 x 1 MUX out sel 8

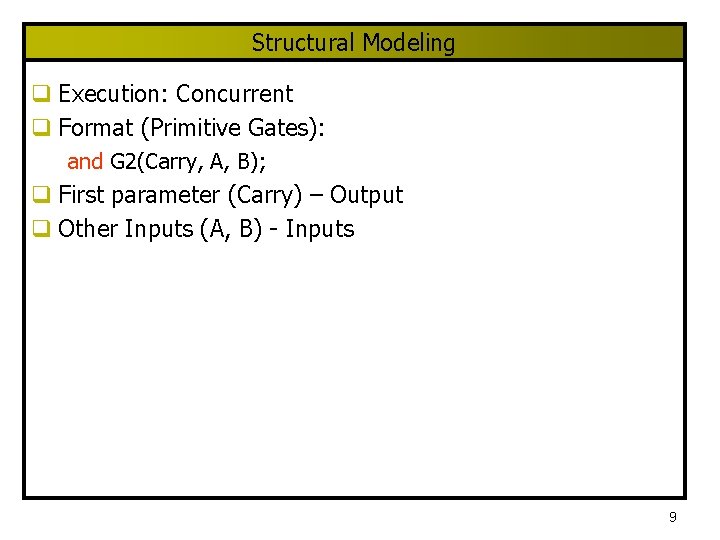

Structural Modeling q Execution: Concurrent q Format (Primitive Gates): and G 2(Carry, A, B); q First parameter (Carry) – Output q Other Inputs (A, B) - Inputs 9

![Dataflow Modeling q Uses continuous assignment statement Ø Format assign delay net Dataflow Modeling q Uses continuous assignment statement Ø Format: assign [ delay ] net](https://slidetodoc.com/presentation_image/1e4e0ca318befa7e7bb84c53b39cce79/image-10.jpg)

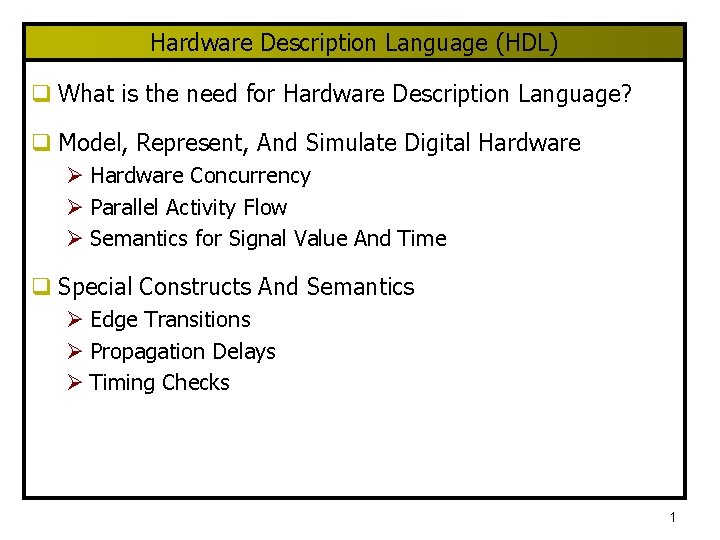

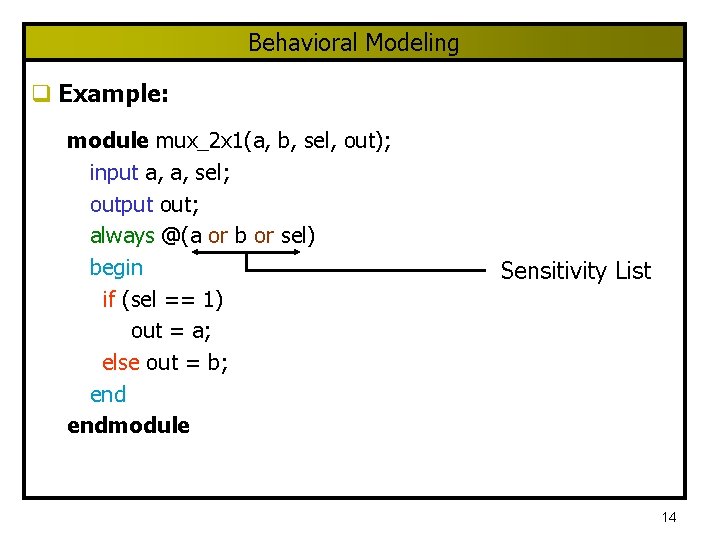

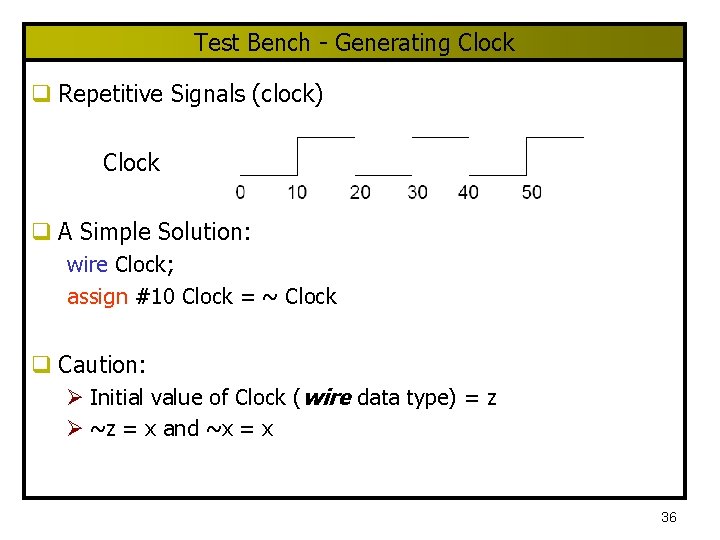

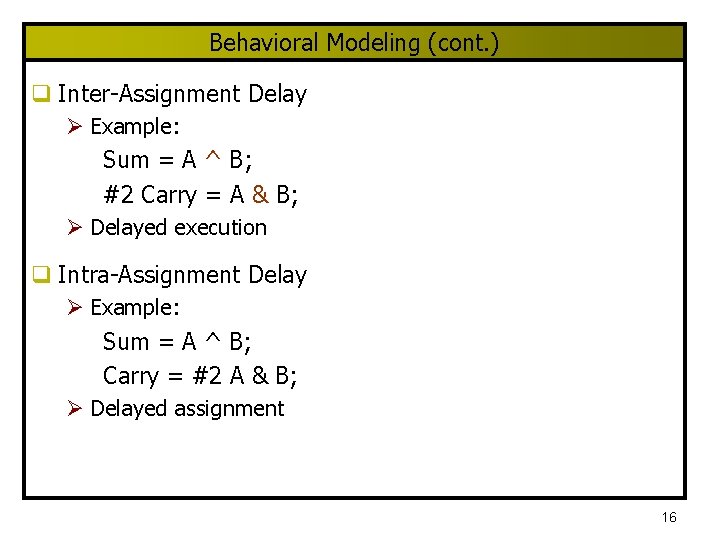

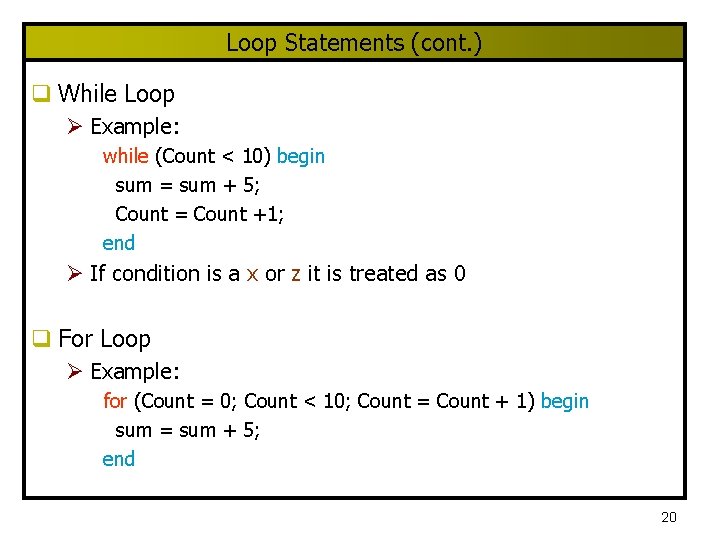

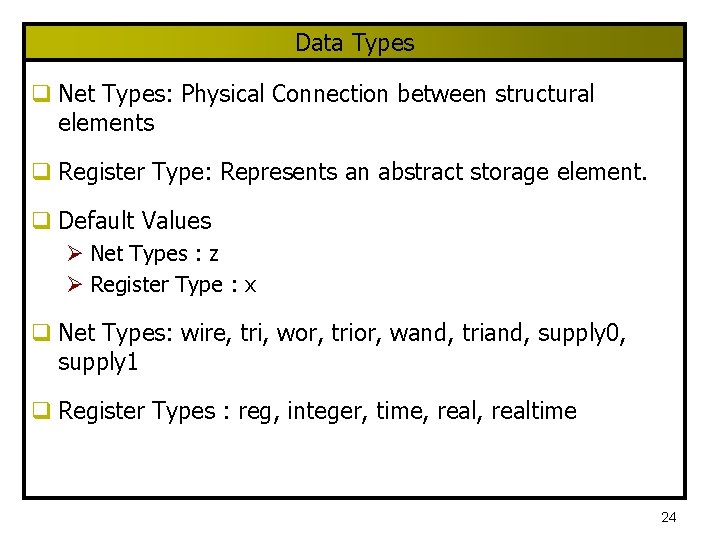

Dataflow Modeling q Uses continuous assignment statement Ø Format: assign [ delay ] net = expression; Ø Example: assign sum = a ^ b; q Delay: Time duration between assignment from RHS to LHS q All continuous assignment statements execute concurrently q Order of the statement does not impact the design 10

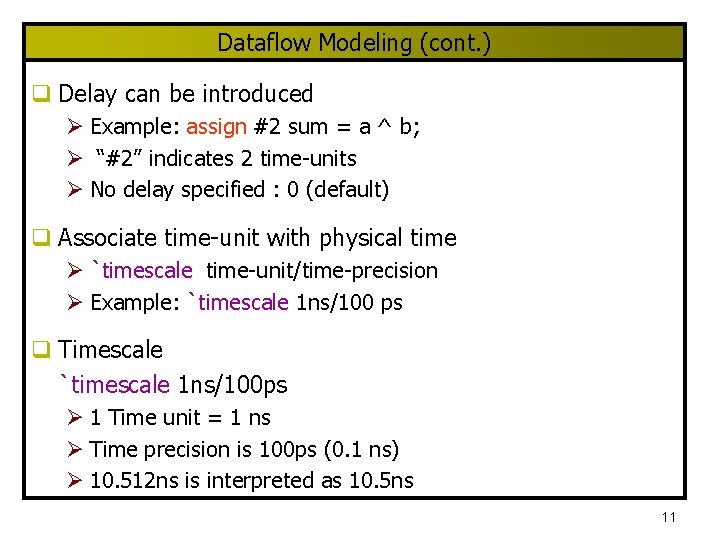

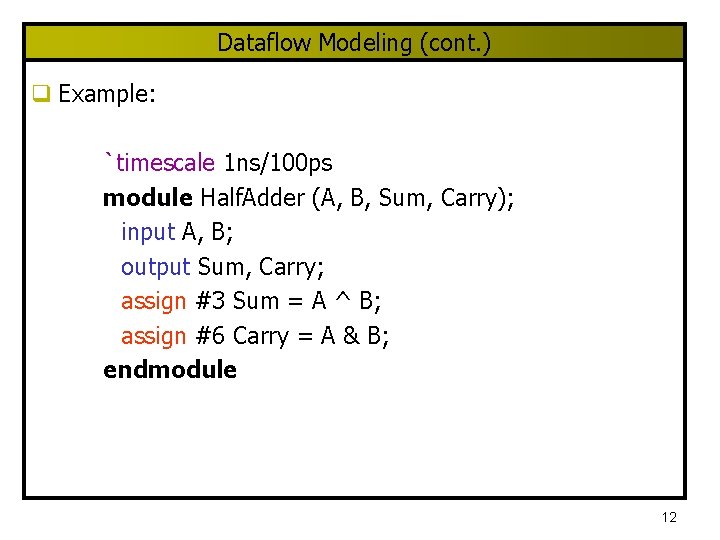

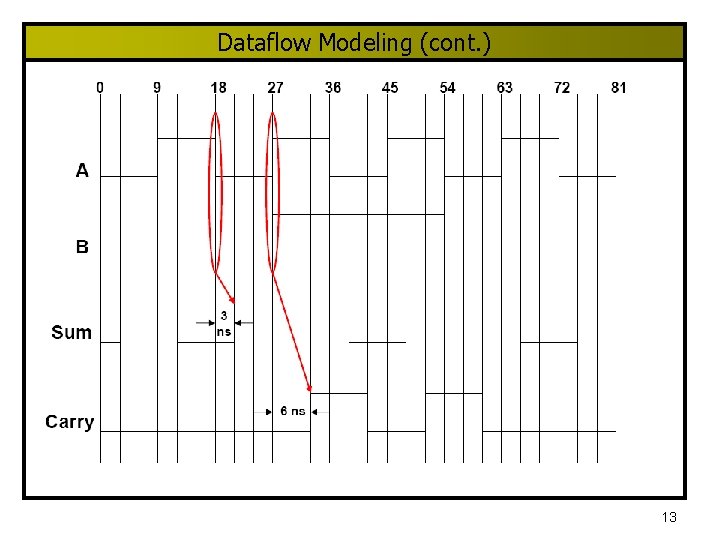

Dataflow Modeling (cont. ) q Delay can be introduced Ø Example: assign #2 sum = a ^ b; Ø “#2” indicates 2 time-units Ø No delay specified : 0 (default) q Associate time-unit with physical time Ø `timescale time-unit/time-precision Ø Example: `timescale 1 ns/100 ps q Timescale `timescale 1 ns/100 ps Ø 1 Time unit = 1 ns Ø Time precision is 100 ps (0. 1 ns) Ø 10. 512 ns is interpreted as 10. 5 ns 11

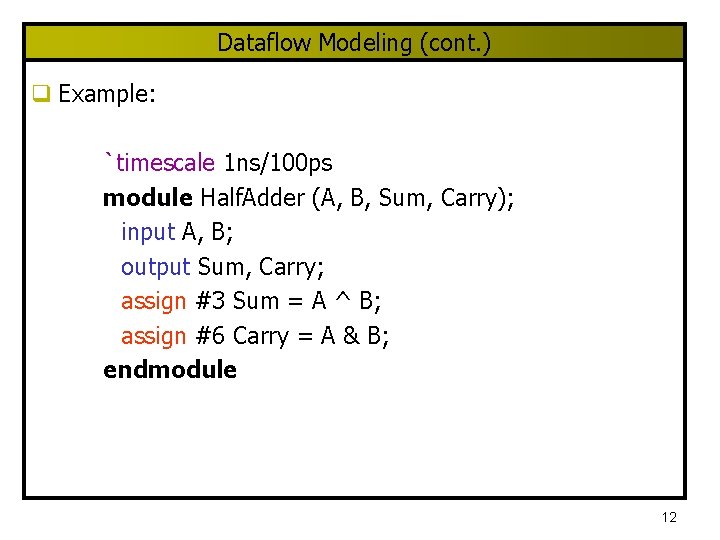

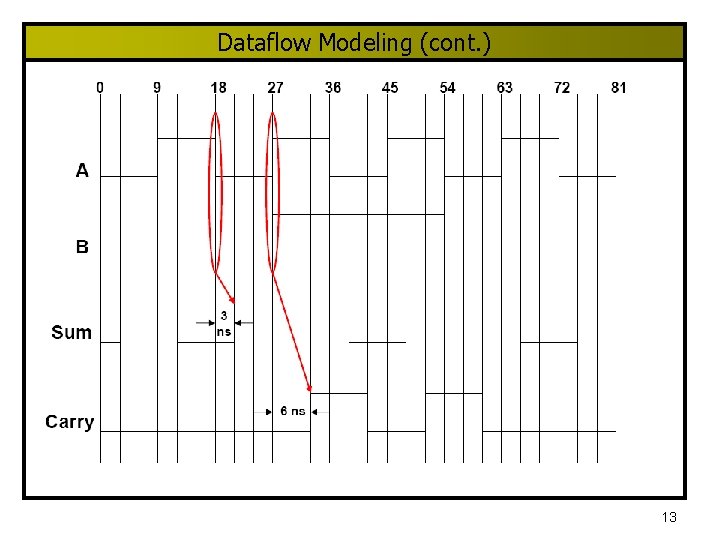

Dataflow Modeling (cont. ) q Example: `timescale 1 ns/100 ps module Half. Adder (A, B, Sum, Carry); input A, B; output Sum, Carry; assign #3 Sum = A ^ B; assign #6 Carry = A & B; endmodule 12

Dataflow Modeling (cont. ) 13

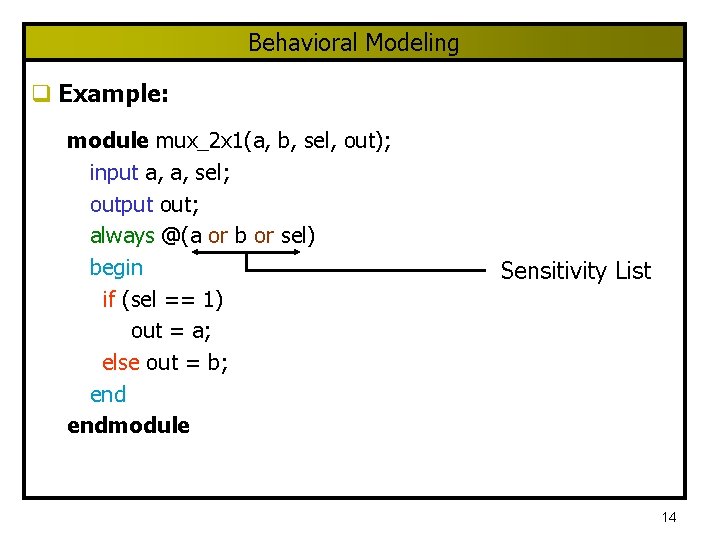

Behavioral Modeling q Example: module mux_2 x 1(a, b, sel, out); input a, a, sel; output out; always @(a or b or sel) begin if (sel == 1) out = a; else out = b; endmodule Sensitivity List 14

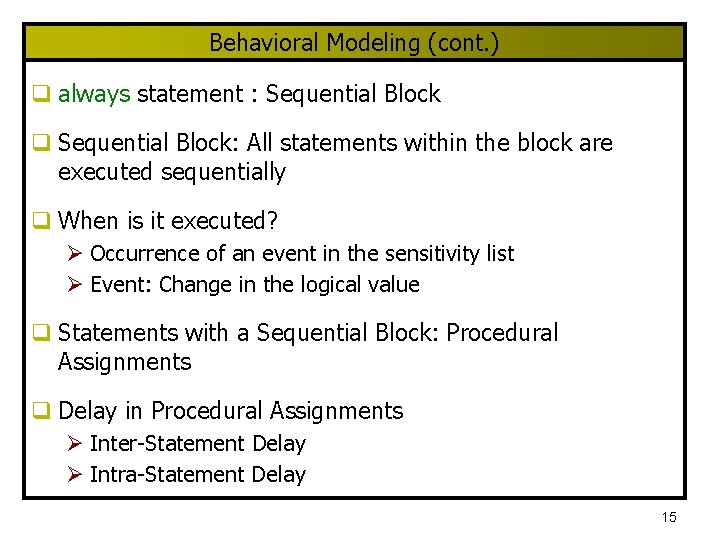

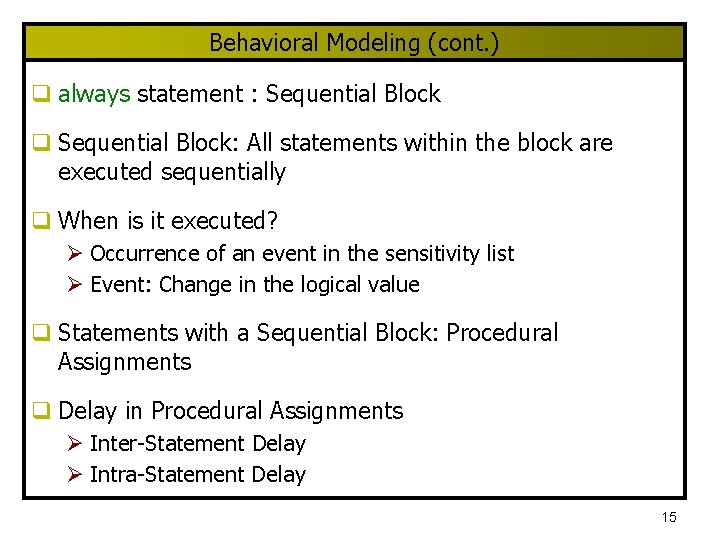

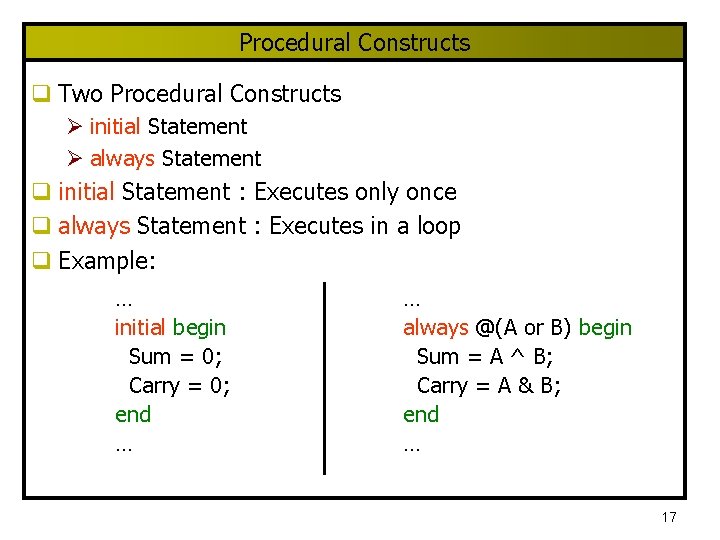

Behavioral Modeling (cont. ) q always statement : Sequential Block q Sequential Block: All statements within the block are executed sequentially q When is it executed? Ø Occurrence of an event in the sensitivity list Ø Event: Change in the logical value q Statements with a Sequential Block: Procedural Assignments q Delay in Procedural Assignments Ø Inter-Statement Delay Ø Intra-Statement Delay 15

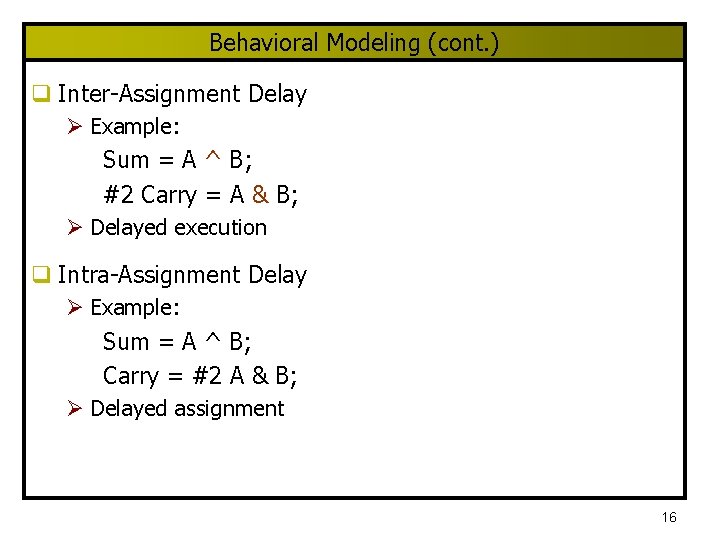

Behavioral Modeling (cont. ) q Inter-Assignment Delay Ø Example: Sum = A ^ B; #2 Carry = A & B; Ø Delayed execution q Intra-Assignment Delay Ø Example: Sum = A ^ B; Carry = #2 A & B; Ø Delayed assignment 16

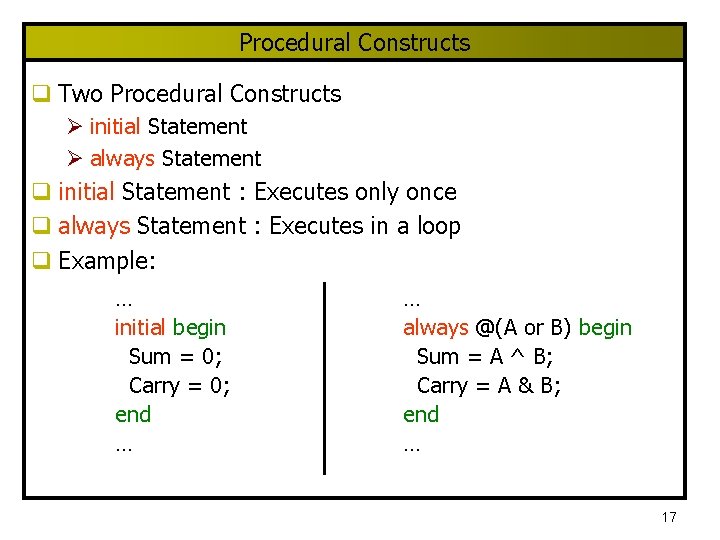

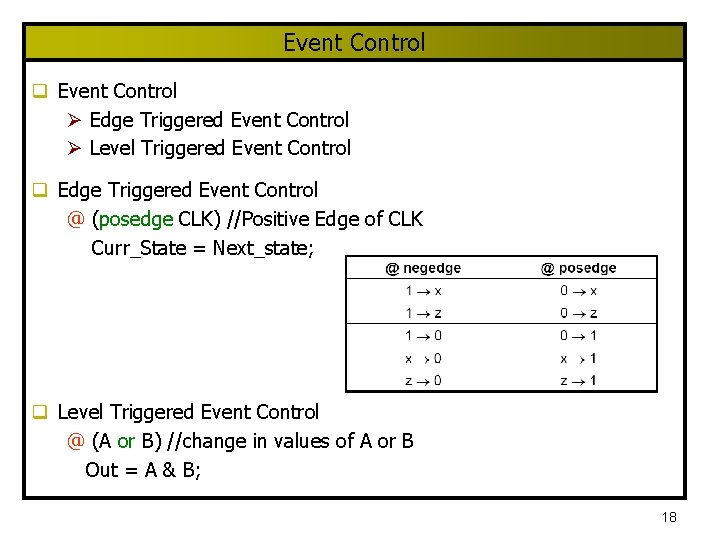

Procedural Constructs q Two Procedural Constructs Ø initial Statement Ø always Statement q initial Statement : Executes only once q always Statement : Executes in a loop q Example: … initial begin Sum = 0; Carry = 0; end … … always @(A or B) begin Sum = A ^ B; Carry = A & B; end … 17

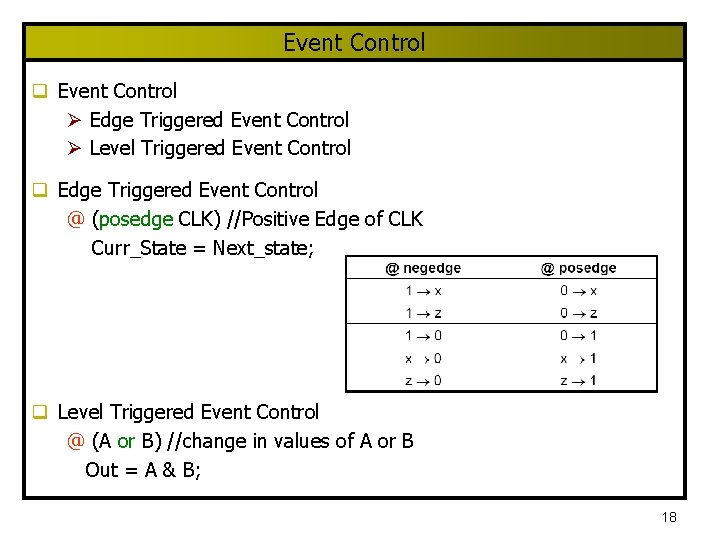

Event Control q Event Control Ø Edge Triggered Event Control Ø Level Triggered Event Control q Edge Triggered Event Control @ (posedge CLK) //Positive Edge of CLK Curr_State = Next_state; q Level Triggered Event Control @ (A or B) //change in values of A or B Out = A & B; 18

Loop Statements q Loop Statements Ø Repeat Ø While Ø For q Repeat Loop Ø Example: repeat (Count) sum = sum + 5; Ø If condition is a x or z it is treated as 0 19

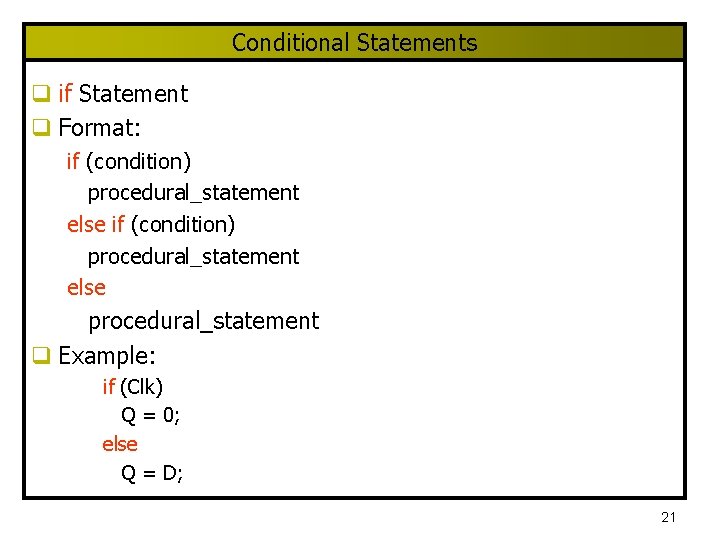

Loop Statements (cont. ) q While Loop Ø Example: while (Count < 10) begin sum = sum + 5; Count = Count +1; end Ø If condition is a x or z it is treated as 0 q For Loop Ø Example: for (Count = 0; Count < 10; Count = Count + 1) begin sum = sum + 5; end 20

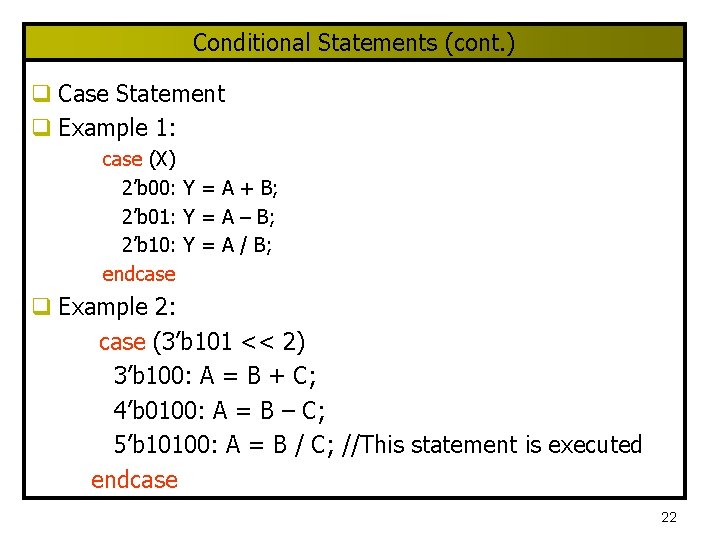

Conditional Statements q if Statement q Format: if (condition) procedural_statement else procedural_statement q Example: if (Clk) Q = 0; else Q = D; 21

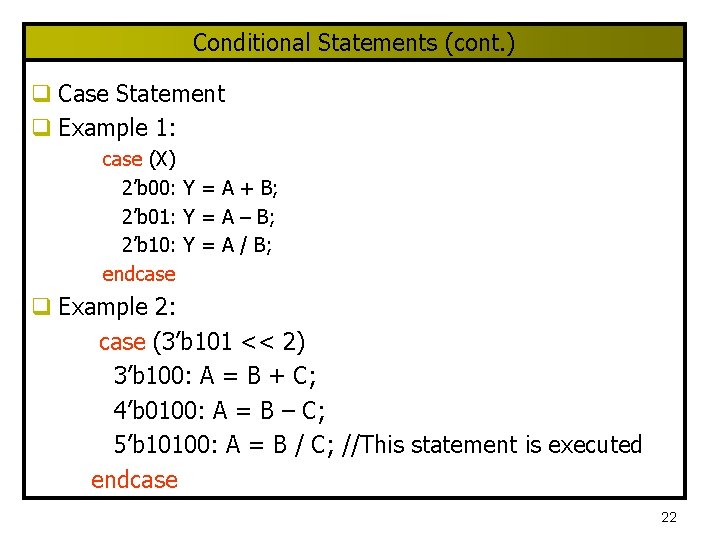

Conditional Statements (cont. ) q Case Statement q Example 1: case (X) 2’b 00: Y = A + B; 2’b 01: Y = A – B; 2’b 10: Y = A / B; endcase q Example 2: case (3’b 101 << 2) 3’b 100: A = B + C; 4’b 0100: A = B – C; 5’b 10100: A = B / C; //This statement is executed endcase 22

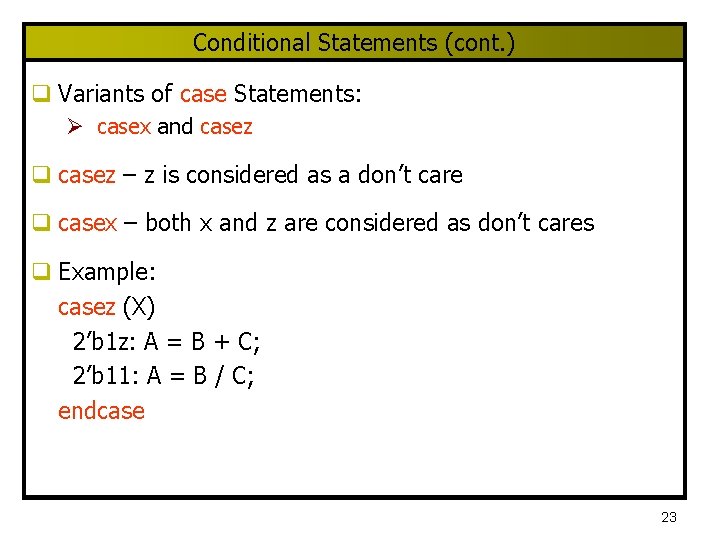

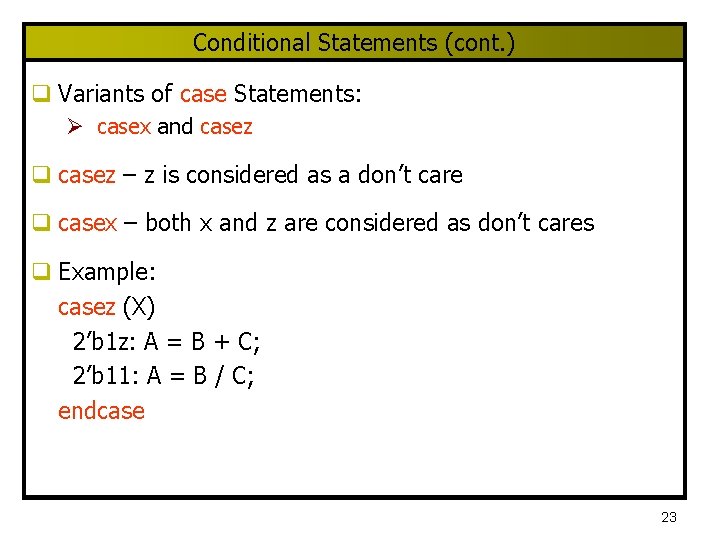

Conditional Statements (cont. ) q Variants of case Statements: Ø casex and casez q casez – z is considered as a don’t care q casex – both x and z are considered as don’t cares q Example: casez (X) 2’b 1 z: A = B + C; 2’b 11: A = B / C; endcase 23

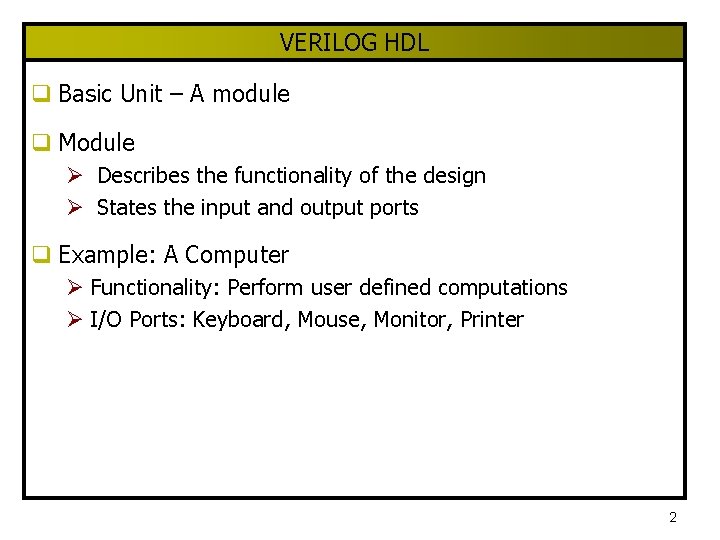

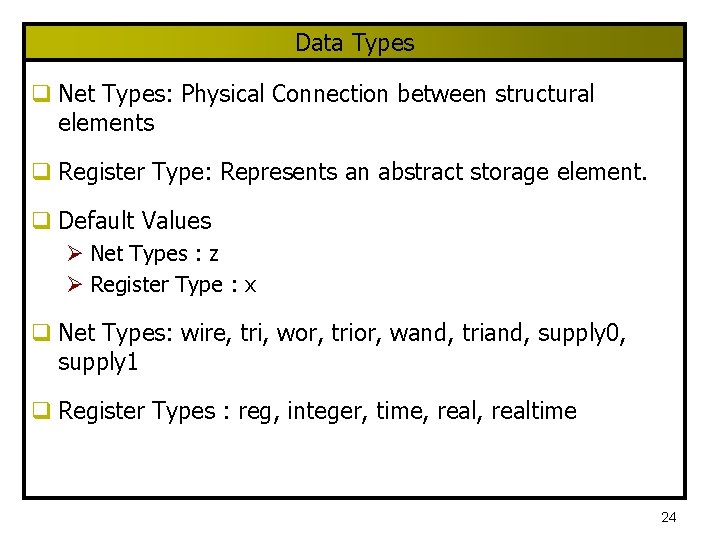

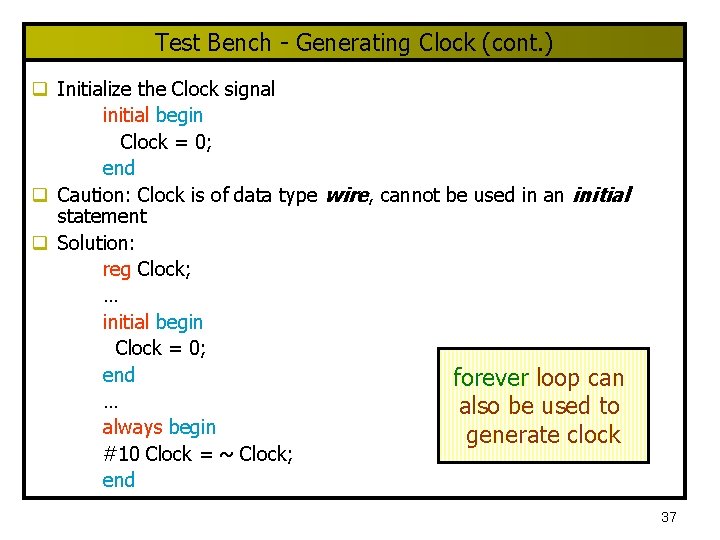

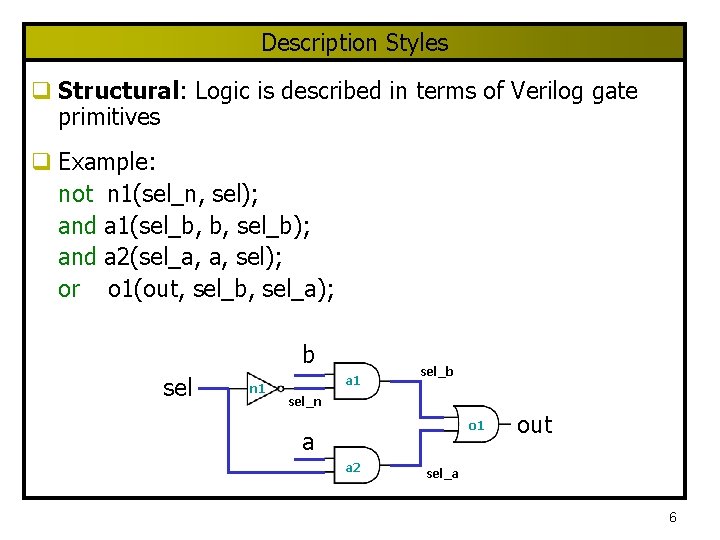

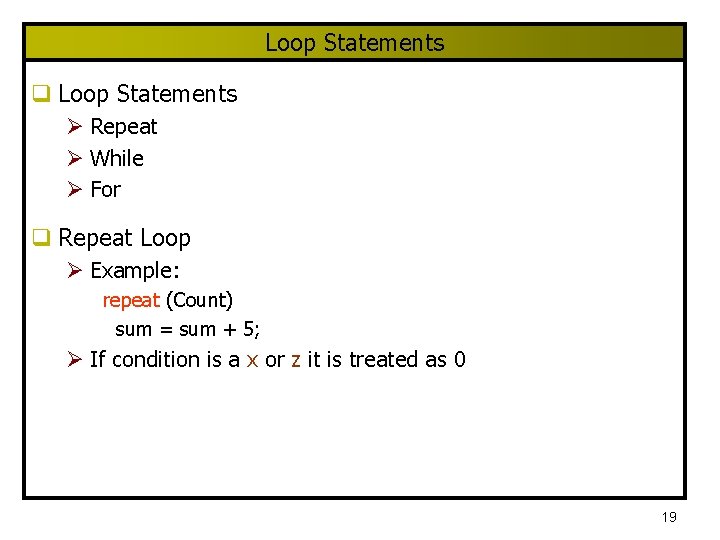

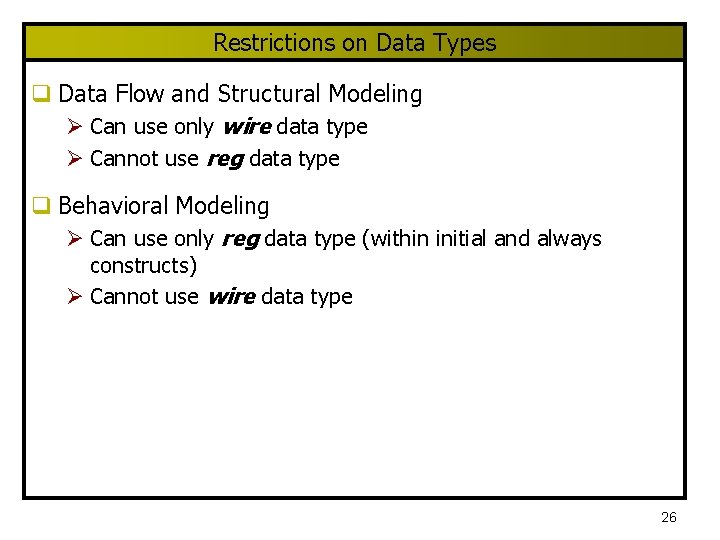

Data Types q Net Types: Physical Connection between structural elements q Register Type: Represents an abstract storage element. q Default Values Ø Net Types : z Ø Register Type : x q Net Types: wire, tri, wor, trior, wand, triand, supply 0, supply 1 q Register Types : reg, integer, time, realtime 24

![Data Types q Net Type Wire wire msb lsb wire 1 Data Types q Net Type: Wire wire [ msb : lsb ] wire 1,](https://slidetodoc.com/presentation_image/1e4e0ca318befa7e7bb84c53b39cce79/image-25.jpg)

Data Types q Net Type: Wire wire [ msb : lsb ] wire 1, wire 2, … Ø Example wire Reset; // A 1 -bit wire [6: 0] Clear; // A 7 -bit wire q Register Type: Reg reg [ msb : lsb ] reg 1, reg 2, … Ø Example reg [ 3: 0 ] cla; // A 4 -bit register reg cla; // A 1 -bit register 25

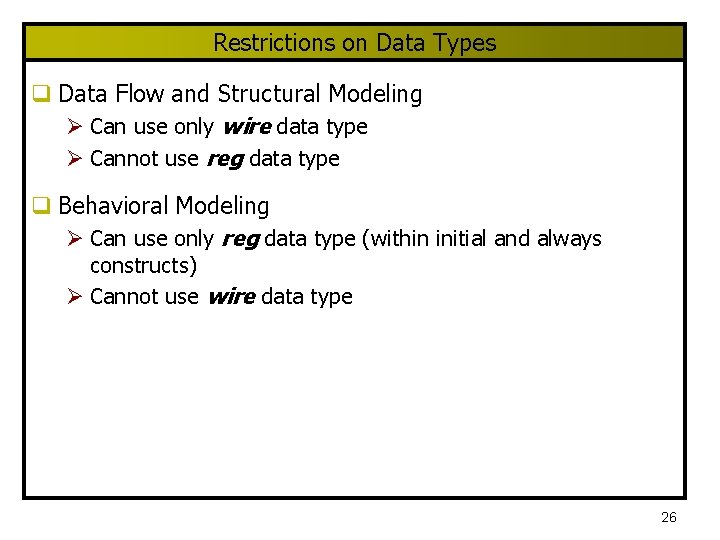

Restrictions on Data Types q Data Flow and Structural Modeling Ø Can use only wire data type Ø Cannot use reg data type q Behavioral Modeling Ø Can use only reg data type (within initial and always constructs) Ø Cannot use wire data type 26

![Memories q An array of registers reg msb lsb memory 1 Memories q An array of registers reg [ msb : lsb ] memory 1](https://slidetodoc.com/presentation_image/1e4e0ca318befa7e7bb84c53b39cce79/image-27.jpg)

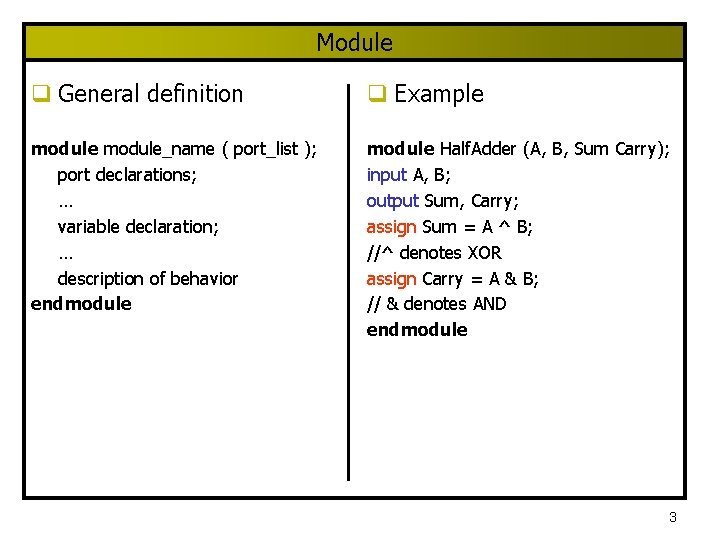

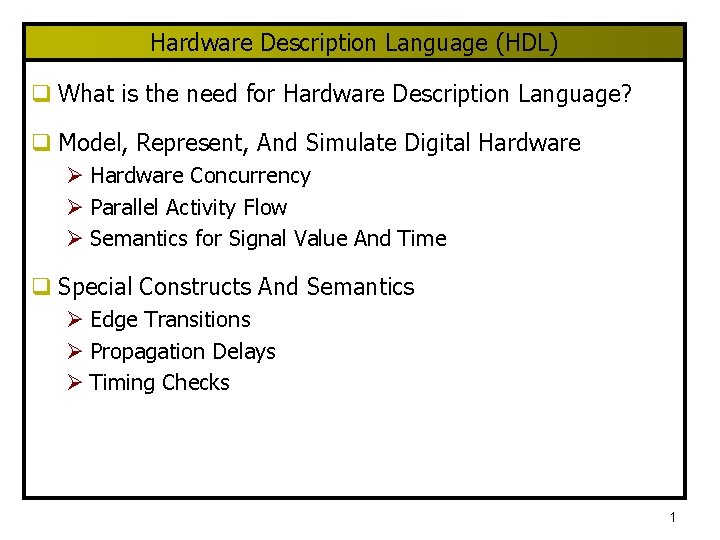

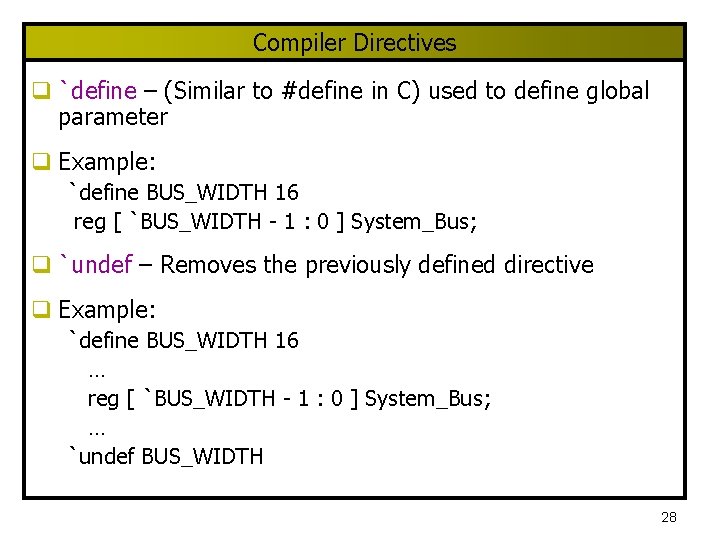

Memories q An array of registers reg [ msb : lsb ] memory 1 [ upper : lower ]; q Example reg [ 0 : 3 ] mem [ 0 : 63 ]; // An array of 64 4 -bit registers reg mem [ 0 : 4 ]; // An array of 5 1 -bit registers 27

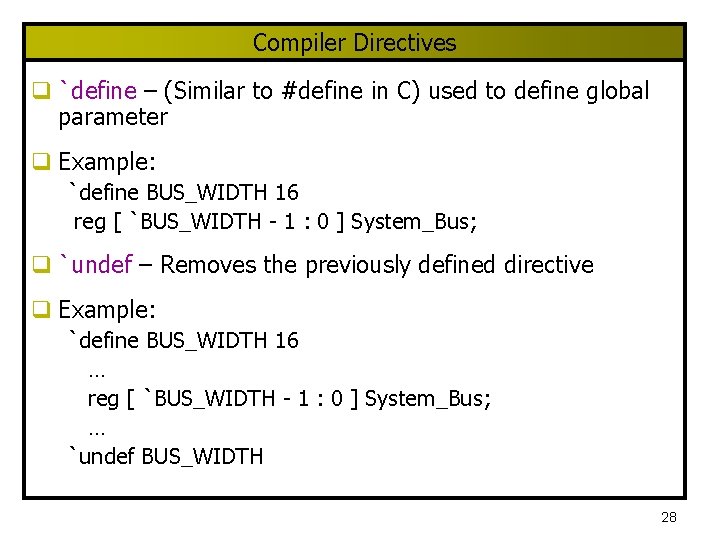

Compiler Directives q `define – (Similar to #define in C) used to define global parameter q Example: `define BUS_WIDTH 16 reg [ `BUS_WIDTH - 1 : 0 ] System_Bus; q `undef – Removes the previously defined directive q Example: `define BUS_WIDTH 16 … reg [ `BUS_WIDTH - 1 : 0 ] System_Bus; … `undef BUS_WIDTH 28

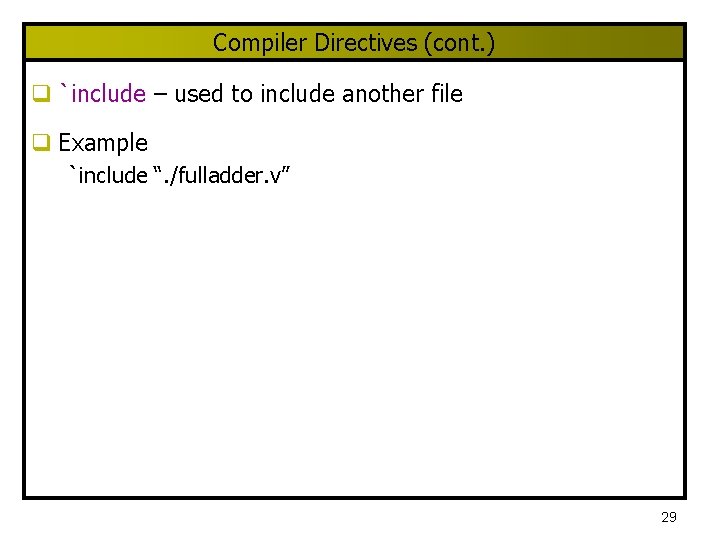

Compiler Directives (cont. ) q `include – used to include another file q Example `include “. /fulladder. v” 29

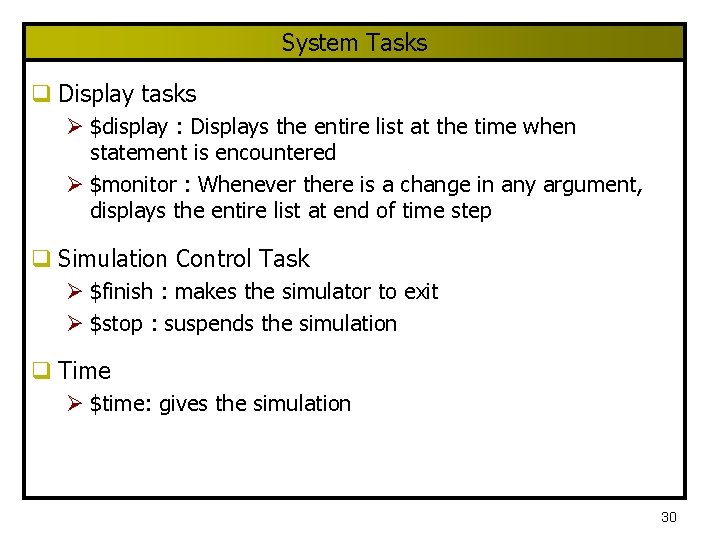

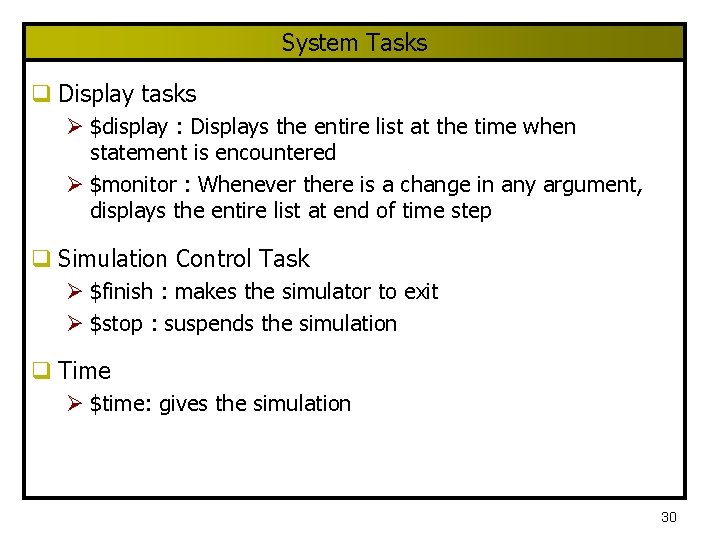

System Tasks q Display tasks Ø $display : Displays the entire list at the time when statement is encountered Ø $monitor : Whenever there is a change in any argument, displays the entire list at end of time step q Simulation Control Task Ø $finish : makes the simulator to exit Ø $stop : suspends the simulation q Time Ø $time: gives the simulation 30

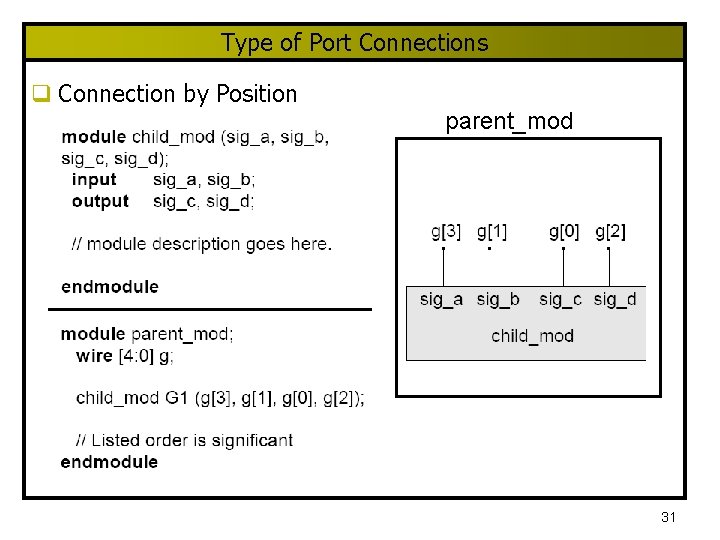

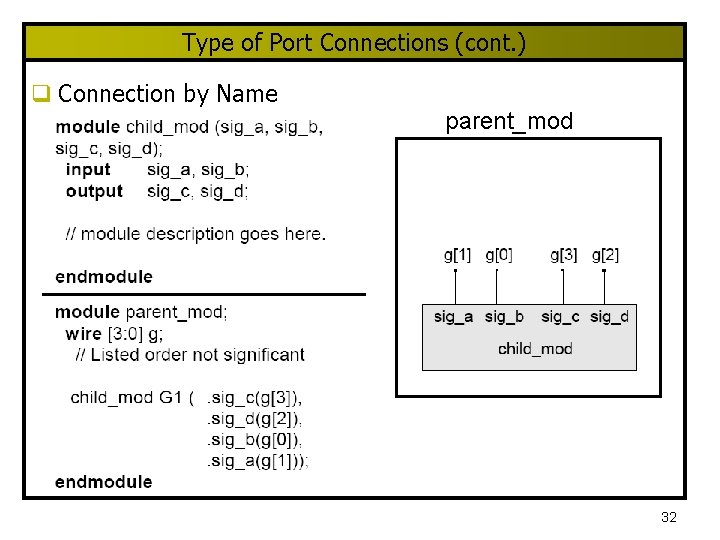

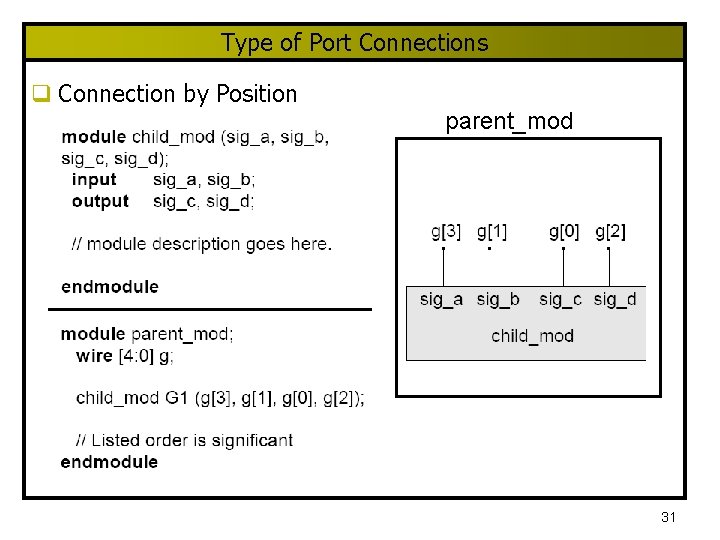

Type of Port Connections q Connection by Position parent_mod 31

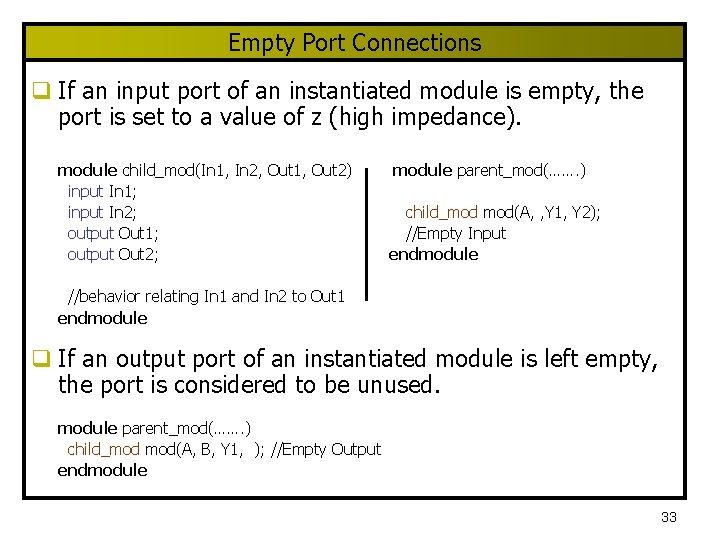

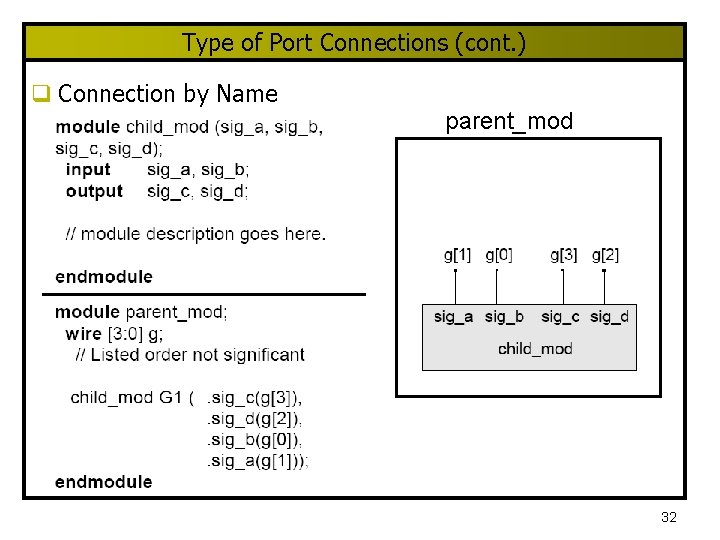

Type of Port Connections (cont. ) q Connection by Name parent_mod 32

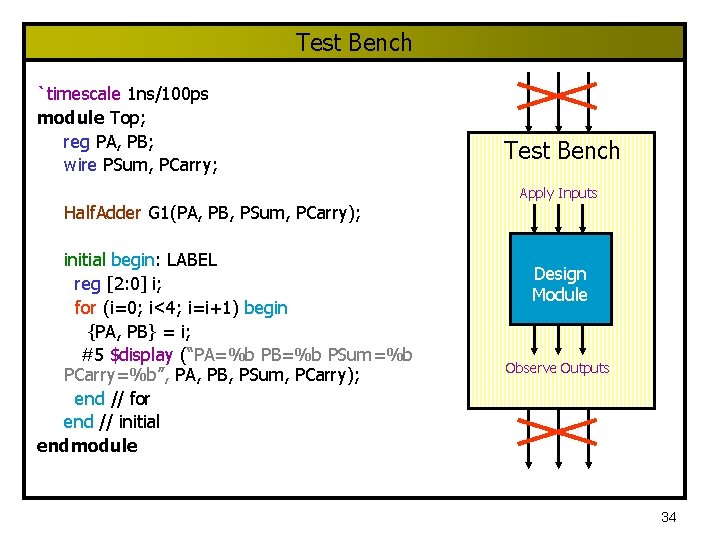

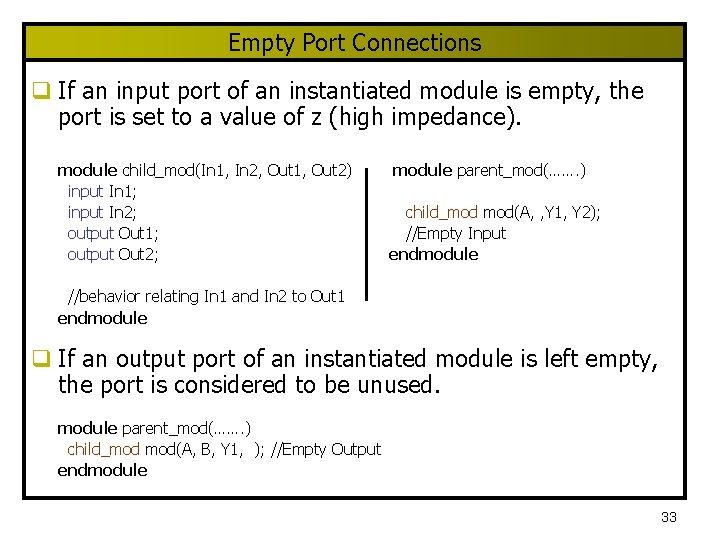

Empty Port Connections q If an input port of an instantiated module is empty, the port is set to a value of z (high impedance). module child_mod(In 1, In 2, Out 1, Out 2) input In 1; input In 2; output Out 1; output Out 2; module parent_mod(……. ) child_mod mod(A, , Y 1, Y 2); //Empty Input endmodule //behavior relating In 1 and In 2 to Out 1 endmodule q If an output port of an instantiated module is left empty, the port is considered to be unused. module parent_mod(……. ) child_mod mod(A, B, Y 1, ); //Empty Output endmodule 33

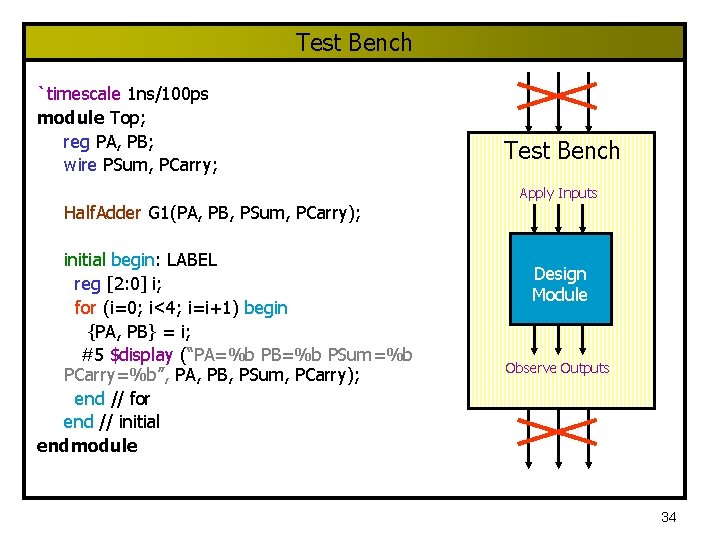

Test Bench `timescale 1 ns/100 ps module Top; reg PA, PB; wire PSum, PCarry; Test Bench Apply Inputs Half. Adder G 1(PA, PB, PSum, PCarry); initial begin: LABEL reg [2: 0] i; for (i=0; i<4; i=i+1) begin {PA, PB} = i; #5 $display (“PA=%b PB=%b PSum=%b PCarry=%b”, PA, PB, PSum, PCarry); end // for end // initial endmodule Design Module Observe Outputs 34

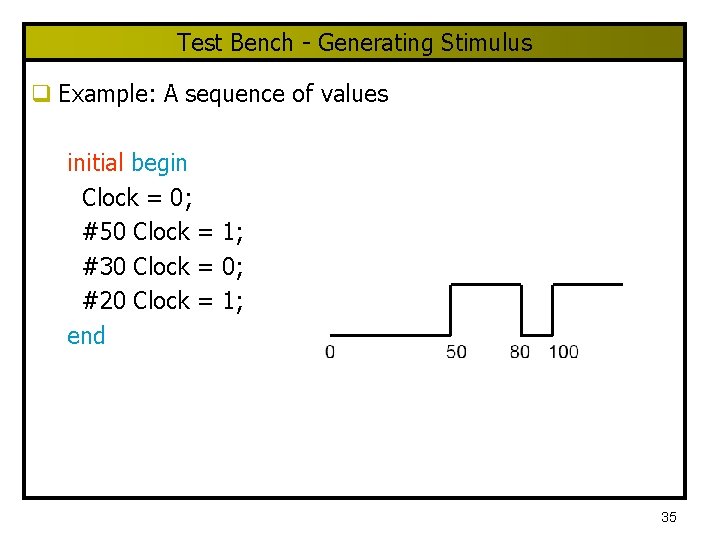

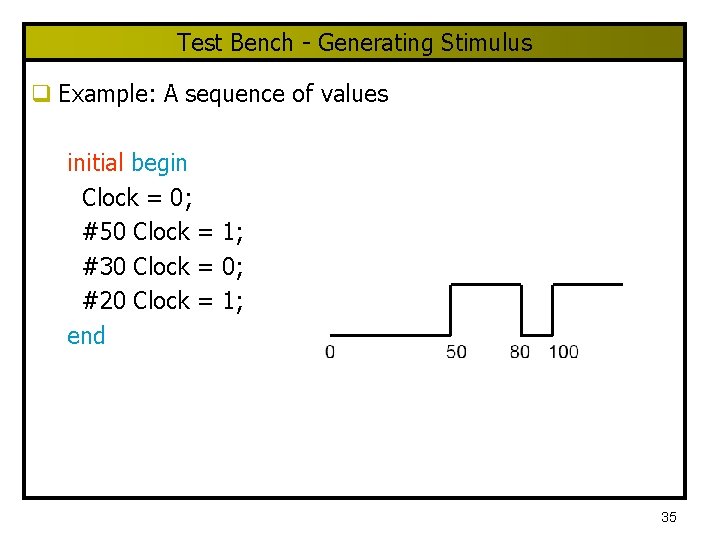

Test Bench - Generating Stimulus q Example: A sequence of values initial begin Clock = 0; #50 Clock = 1; #30 Clock = 0; #20 Clock = 1; end 35

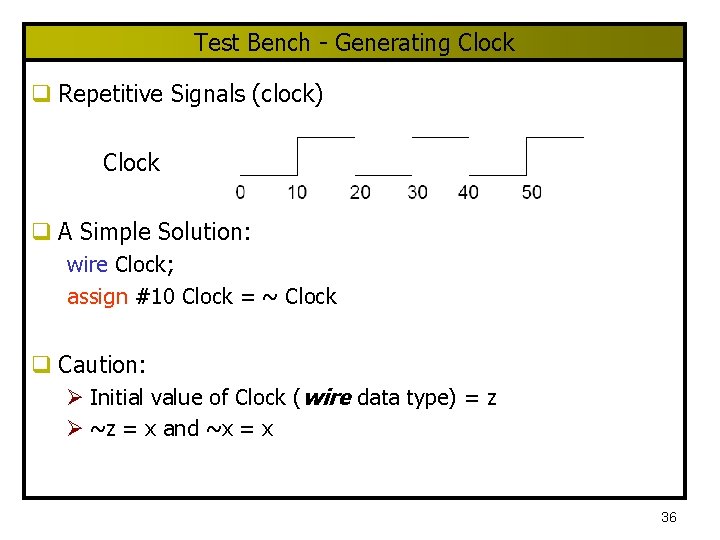

Test Bench - Generating Clock q Repetitive Signals (clock) Clock q A Simple Solution: wire Clock; assign #10 Clock = ~ Clock q Caution: Ø Initial value of Clock (wire data type) = z Ø ~z = x and ~x = x 36

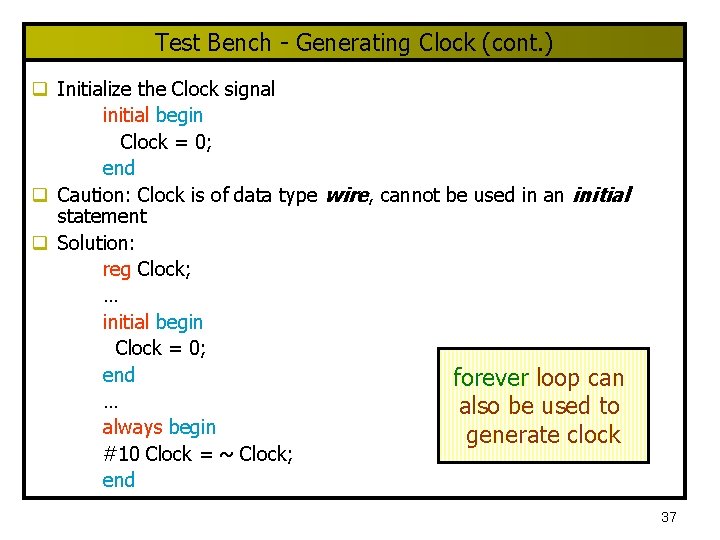

Test Bench - Generating Clock (cont. ) q Initialize the Clock signal initial begin Clock = 0; end q Caution: Clock is of data type wire, cannot be used in an initial statement q Solution: reg Clock; … initial begin Clock = 0; end forever loop can … also be used to always begin generate clock #10 Clock = ~ Clock; end 37