Hardware Description Language HDL Para qu precisamos de

![Data Types Net Type: Wire wire [ msb : lsb ] wire 1, wire Data Types Net Type: Wire wire [ msb : lsb ] wire 1, wire](https://slidetodoc.com/presentation_image/5d37636584006c7178fb12d707caaa46/image-24.jpg)

![Memories An array of registers reg [ msb : lsb ] memory 1 [ Memories An array of registers reg [ msb : lsb ] memory 1 [](https://slidetodoc.com/presentation_image/5d37636584006c7178fb12d707caaa46/image-26.jpg)

- Slides: 36

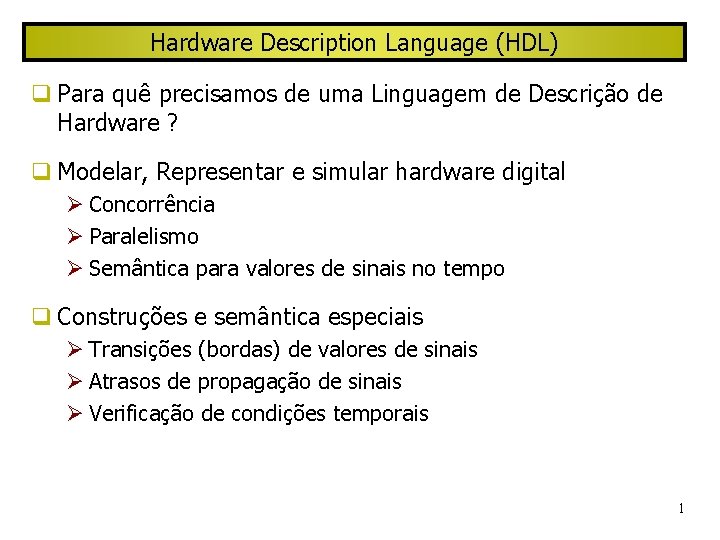

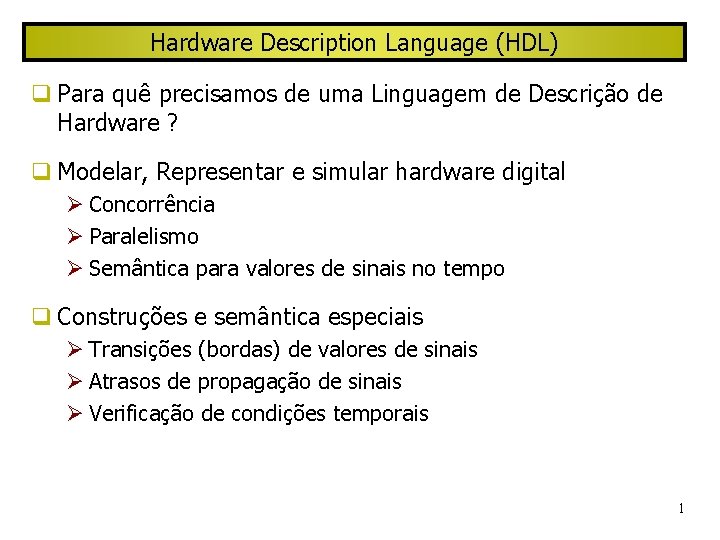

Hardware Description Language (HDL) Para quê precisamos de uma Linguagem de Descrição de Hardware ? Modelar, Representar e simular hardware digital Concorrência Paralelismo Semântica para valores de sinais no tempo Construções e semântica especiais Transições (bordas) de valores de sinais Atrasos de propagação de sinais Verificação de condições temporais 1

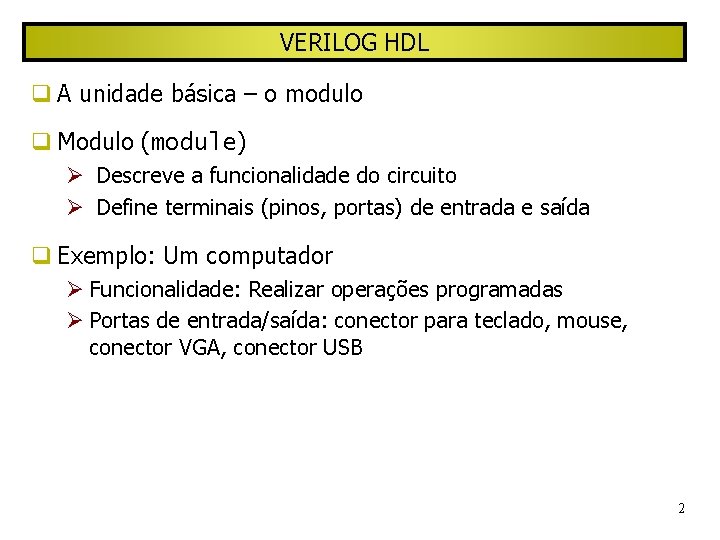

VERILOG HDL A unidade básica – o modulo Modulo (module) Descreve a funcionalidade do circuito Define terminais (pinos, portas) de entrada e saída Exemplo: Um computador Funcionalidade: Realizar operações programadas Portas de entrada/saída: conector para teclado, mouse, conector VGA, conector USB 2

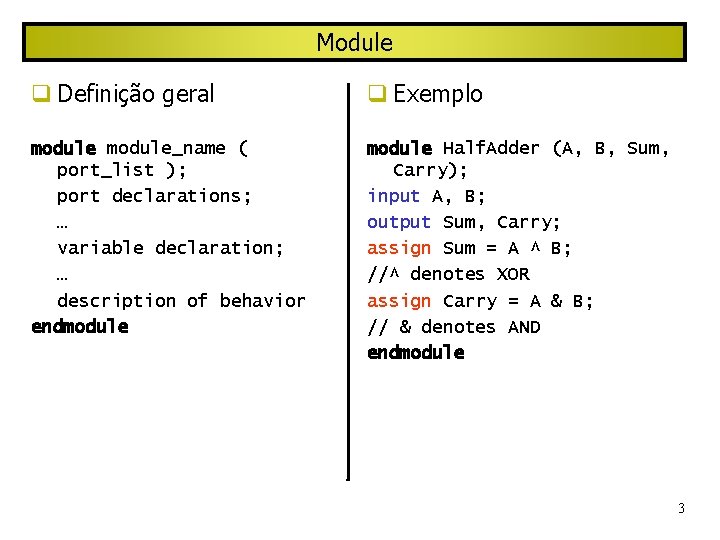

Module Definição geral Exemplo module_name ( port_list ); port declarations; … variable declaration; … description of behavior endmodule Half. Adder (A, B, Sum, Carry); input A, B; output Sum, Carry; assign Sum = A ^ B; //^ denotes XOR assign Carry = A & B; // & denotes AND endmodule 3

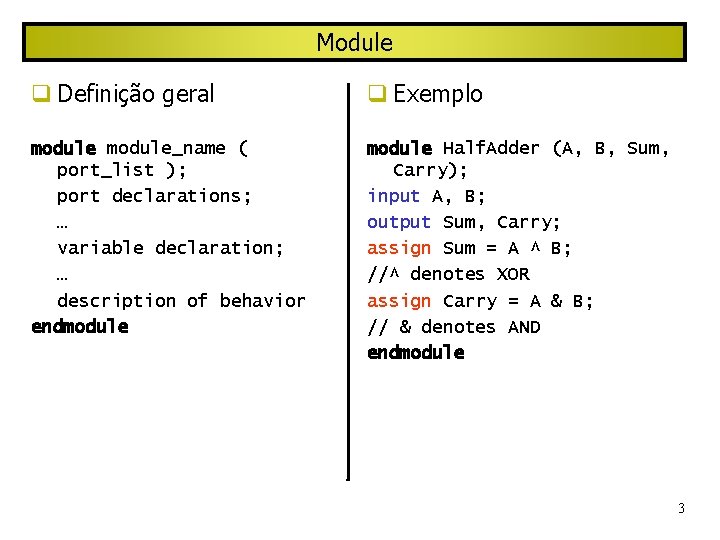

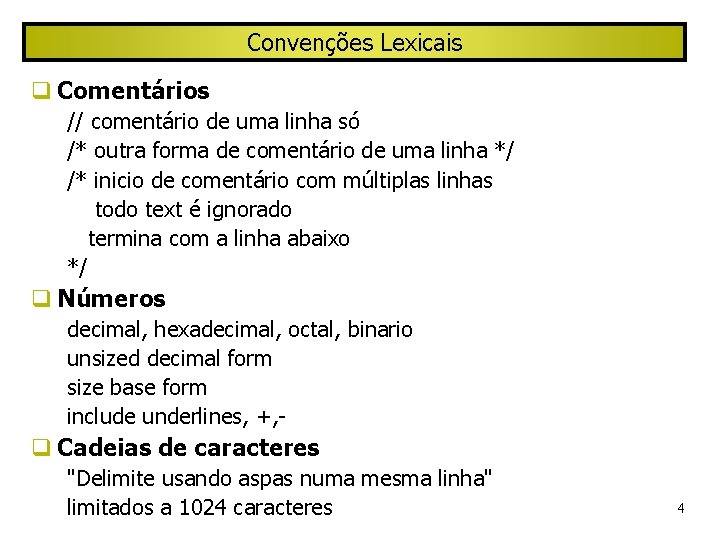

Convenções Lexicais Comentários // comentário de uma linha só /* outra forma de comentário de uma linha */ /* inicio de comentário com múltiplas linhas todo text é ignorado termina com a linha abaixo */ Números decimal, hexadecimal, octal, binario unsized decimal form size base form include underlines, +, - Cadeias de caracteres "Delimite usando aspas numa mesma linha" limitados a 1024 caracteres 4

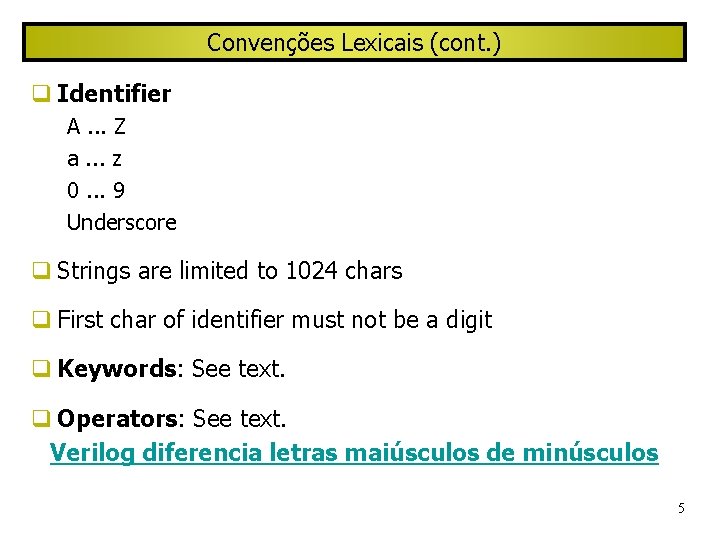

Convenções Lexicais (cont. ) Identifier A. . . Z a. . . z 0. . . 9 Underscore Strings are limited to 1024 chars First char of identifier must not be a digit Keywords: See text. Operators: See text. Verilog diferencia letras maiúsculos de minúsculos 5

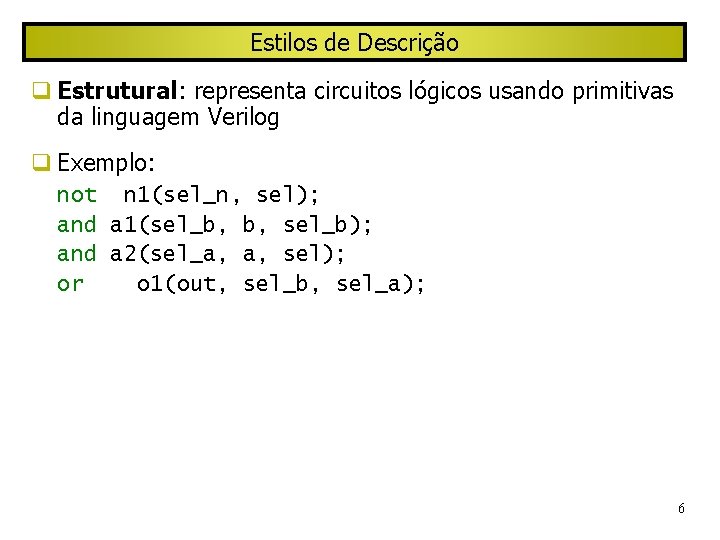

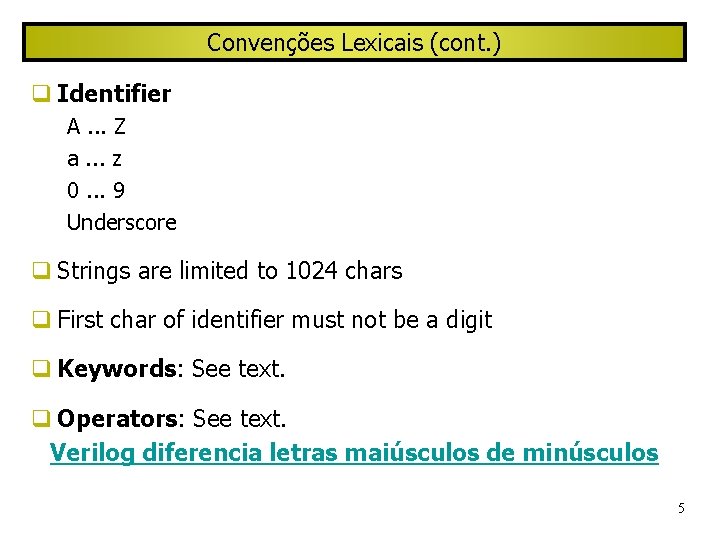

Estilos de Descrição Estrutural: representa circuitos lógicos usando primitivas da linguagem Verilog Exemplo: not n 1(sel_n, sel); and a 1(sel_b, b, sel_b); and a 2(sel_a, a, sel); or o 1(out, sel_b, sel_a); 6

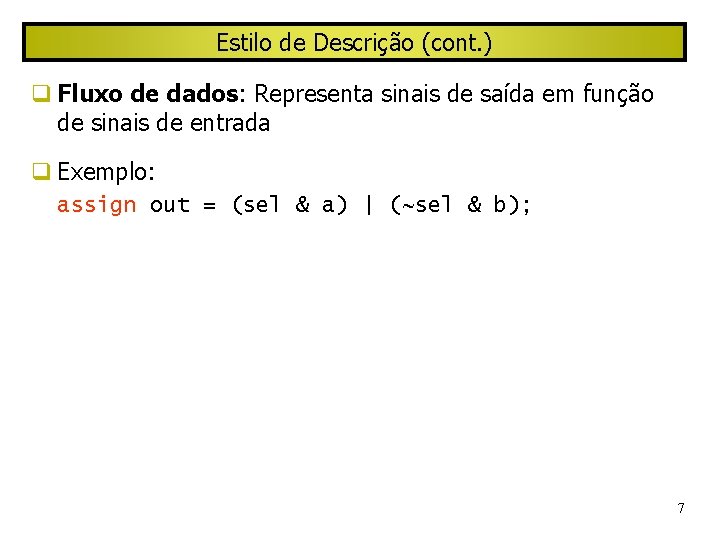

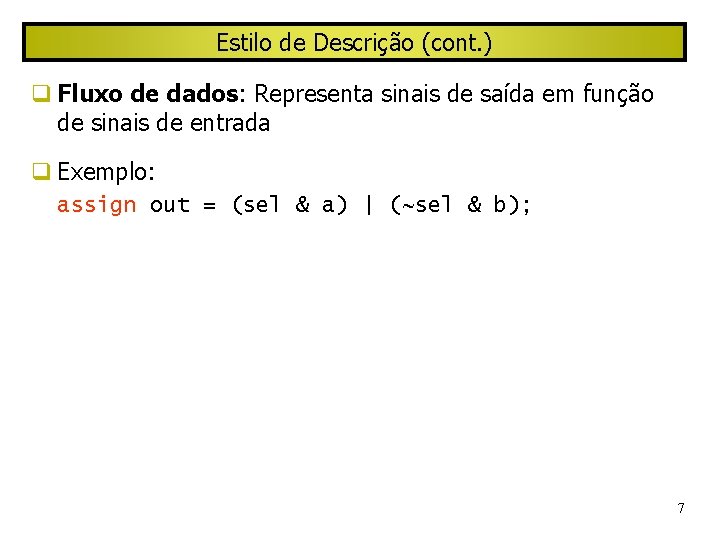

Estilo de Descrição (cont. ) Fluxo de dados: Representa sinais de saída em função de sinais de entrada Exemplo: assign out = (sel & a) | (~sel & b); 7

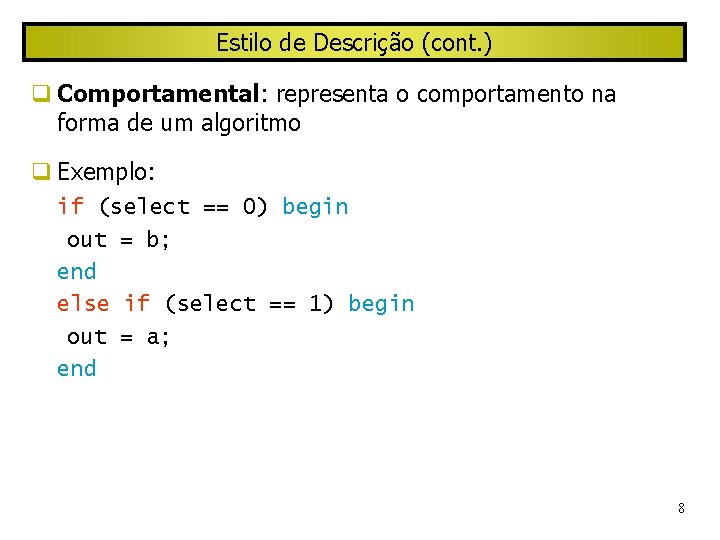

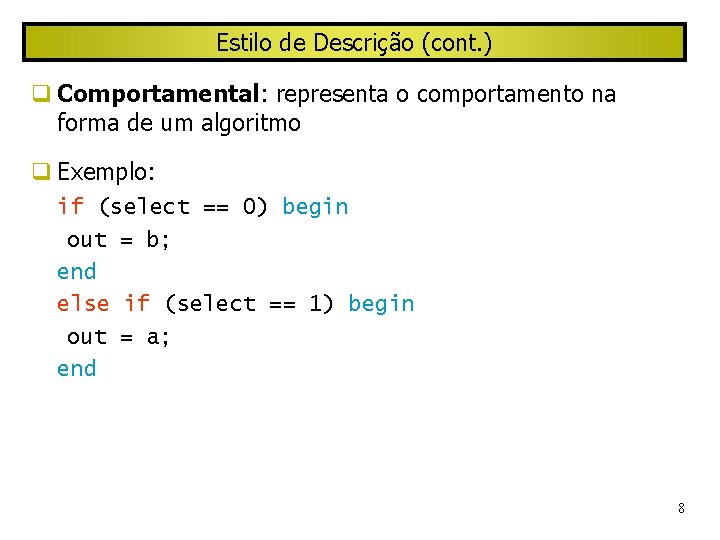

Estilo de Descrição (cont. ) Comportamental: representa o comportamento na forma de um algoritmo Exemplo: if (select == 0) begin out = b; end else if (select == 1) begin out = a; end 8

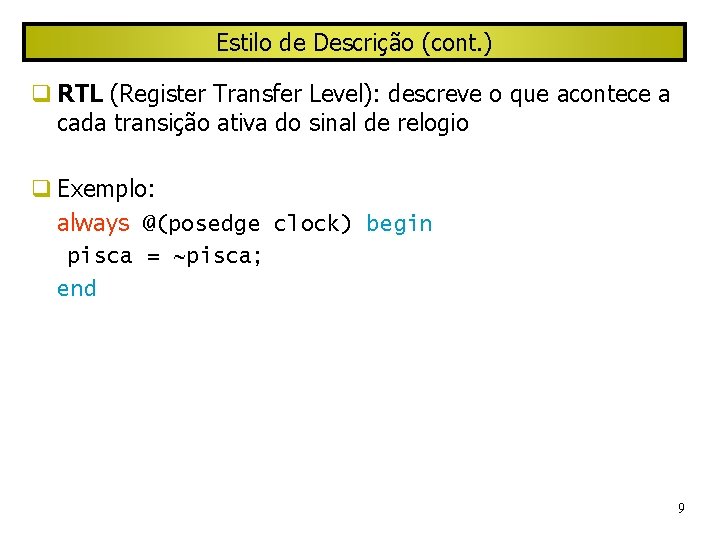

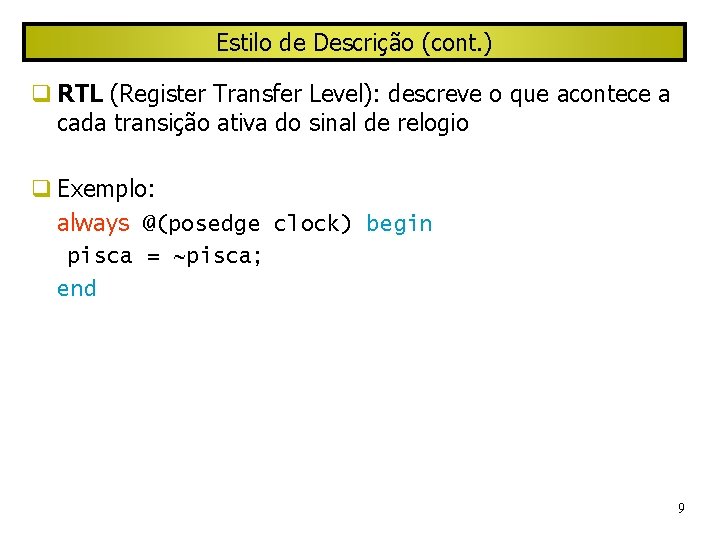

Estilo de Descrição (cont. ) RTL (Register Transfer Level): descreve o que acontece a cada transição ativa do sinal de relogio Exemplo: always @(posedge clock) begin pisca = ~pisca; end 9

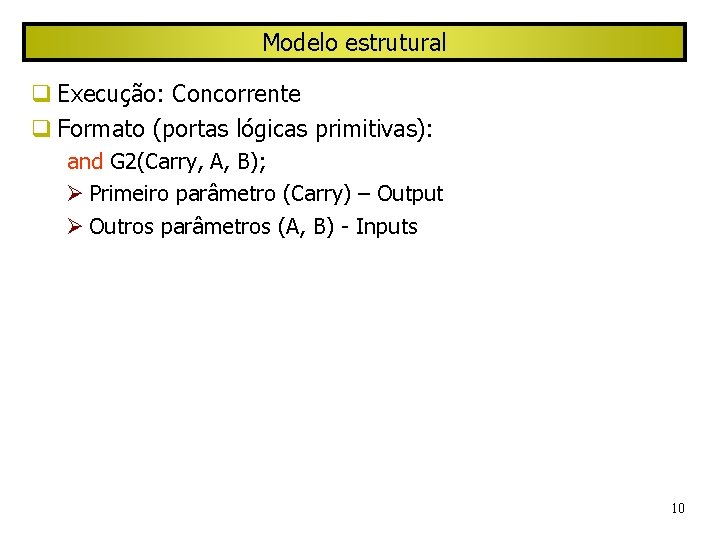

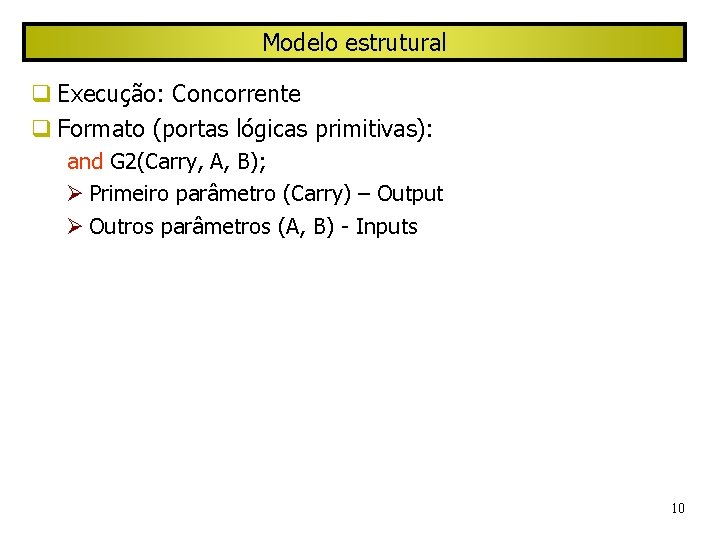

Modelo estrutural Execução: Concorrente Formato (portas lógicas primitivas): and G 2(Carry, A, B); Primeiro parâmetro (Carry) – Output Outros parâmetros (A, B) - Inputs 10

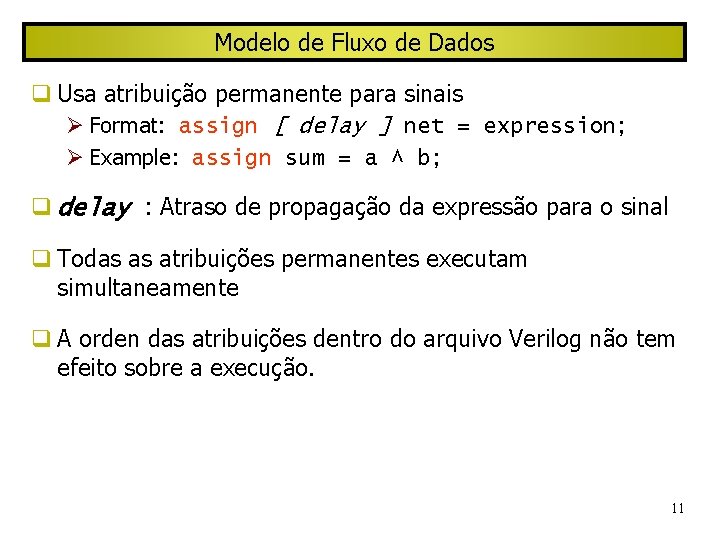

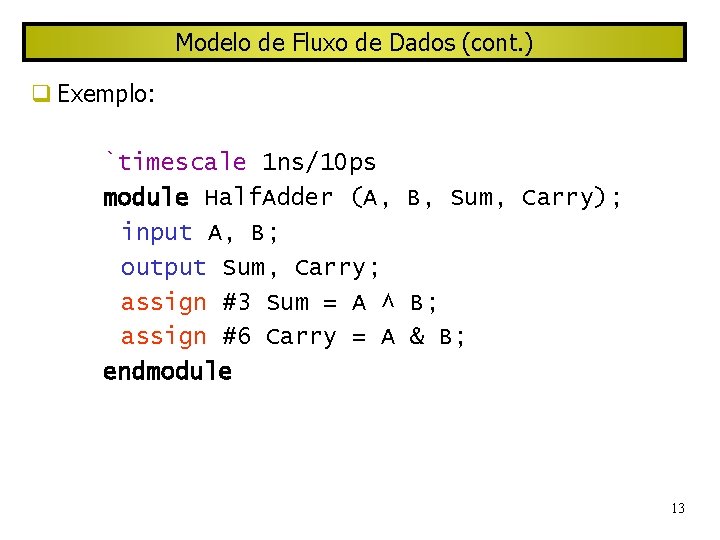

Modelo de Fluxo de Dados Usa atribuição permanente para sinais Format: assign [ delay ] net = expression; Example: assign sum = a ^ b; delay : Atraso de propagação da expressão para o sinal Todas as atribuições permanentes executam simultaneamente A orden das atribuições dentro do arquivo Verilog não tem efeito sobre a execução. 11

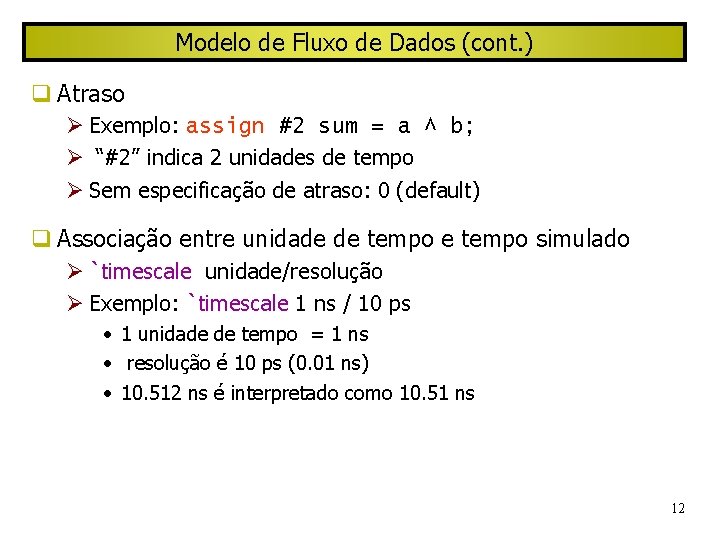

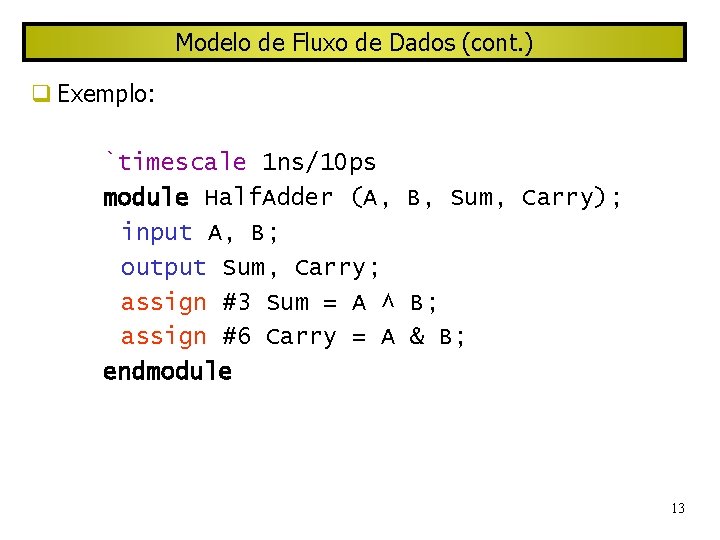

Modelo de Fluxo de Dados (cont. ) Atraso Exemplo: assign #2 sum = a ^ b; “#2” indica 2 unidades de tempo Sem especificação de atraso: 0 (default) Associação entre unidade de tempo simulado `timescale unidade/resolução Exemplo: `timescale 1 ns / 10 ps • 1 unidade de tempo = 1 ns • resolução é 10 ps (0. 01 ns) • 10. 512 ns é interpretado como 10. 51 ns 12

Modelo de Fluxo de Dados (cont. ) Exemplo: `timescale 1 ns/10 ps module Half. Adder (A, B, Sum, Carry); input A, B; output Sum, Carry; assign #3 Sum = A ^ B; assign #6 Carry = A & B; endmodule 13

Modelo de Fluxo de Dados (cont. ) 14

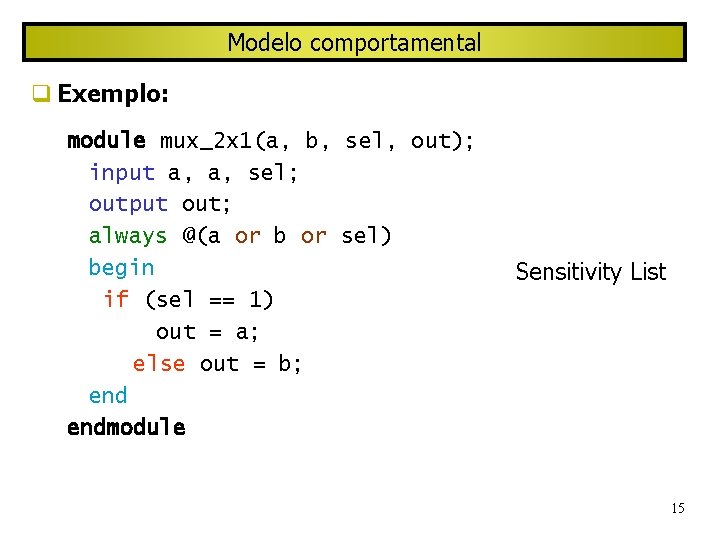

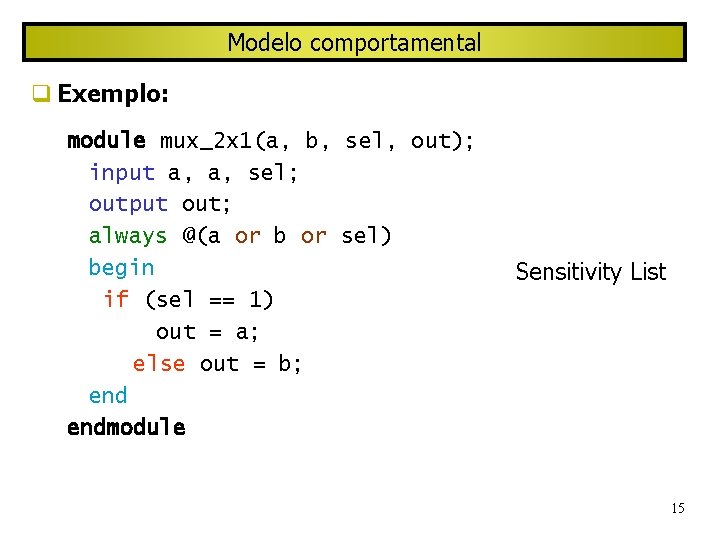

Modelo comportamental Exemplo: module mux_2 x 1(a, b, sel, out); input a, a, sel; output out; always @(a or b or sel) begin if (sel == 1) out = a; else out = b; endmodule Sensitivity List 15

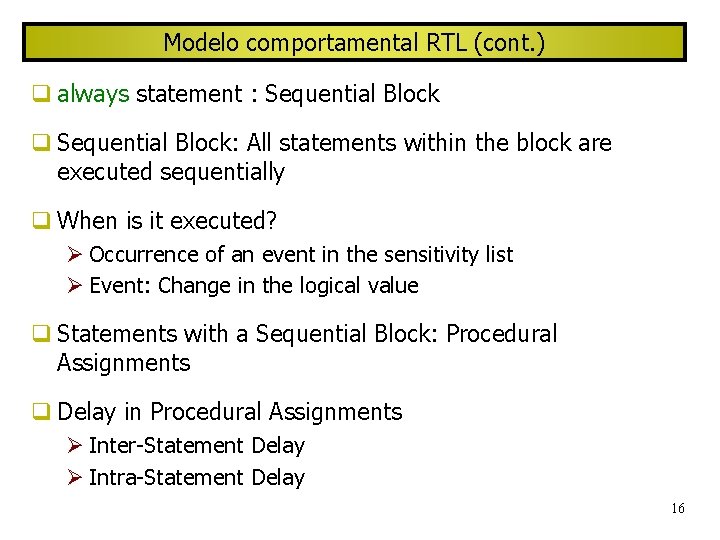

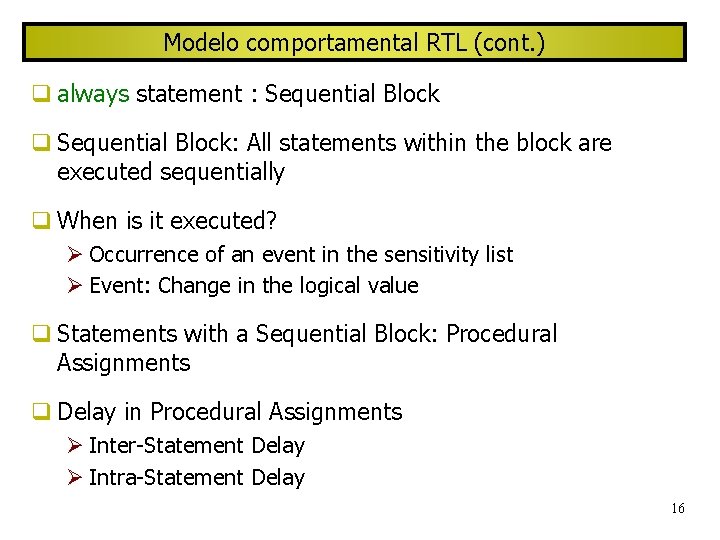

Modelo comportamental RTL (cont. ) always statement : Sequential Block: All statements within the block are executed sequentially When is it executed? Occurrence of an event in the sensitivity list Event: Change in the logical value Statements with a Sequential Block: Procedural Assignments Delay in Procedural Assignments Inter-Statement Delay Intra-Statement Delay 16

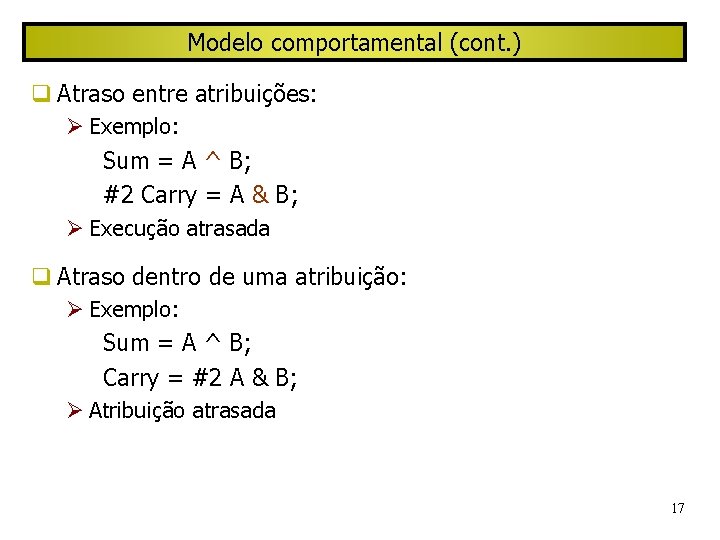

Modelo comportamental (cont. ) Atraso entre atribuições: Exemplo: Sum = A ^ B; #2 Carry = A & B; Execução atrasada Atraso dentro de uma atribuição: Exemplo: Sum = A ^ B; Carry = #2 A & B; Atribuição atrasada 17

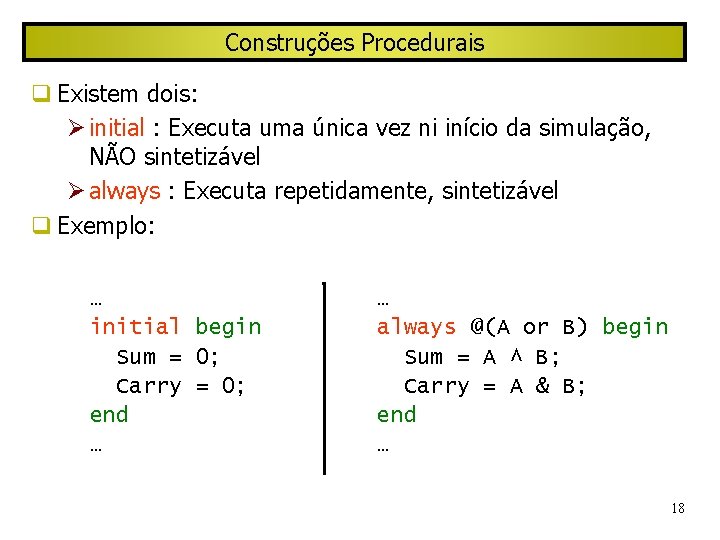

Construções Procedurais Existem dois: initial : Executa uma única vez ni início da simulação, NÃO sintetizável always : Executa repetidamente, sintetizável Exemplo: … initial begin Sum = 0; Carry = 0; end … … always @(A or B) begin Sum = A ^ B; Carry = A & B; end … 18

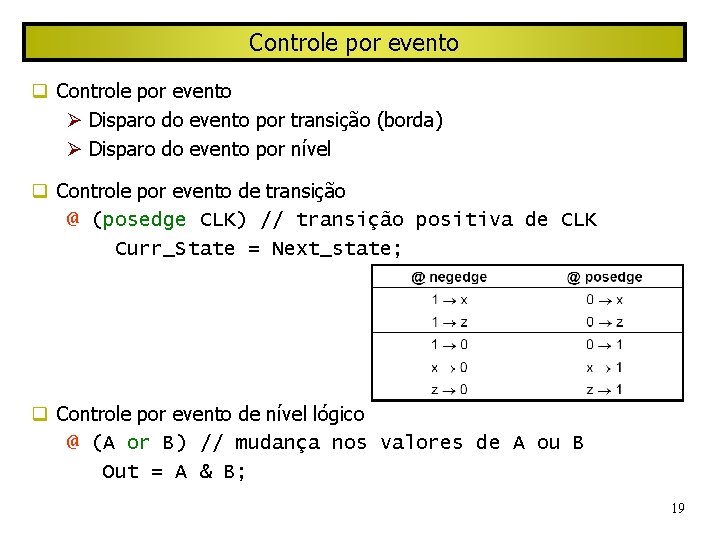

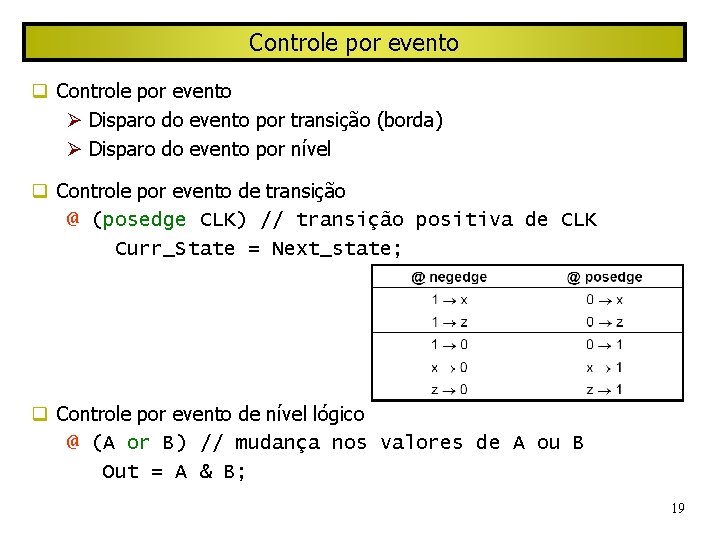

Controle por evento Disparo do evento por transição (borda) Disparo do evento por nível Controle por evento de transição @ (posedge CLK) // transição positiva de CLK Curr_State = Next_state; Controle por evento de nível lógico @ (A or B) // mudança nos valores de A ou B Out = A & B; 19

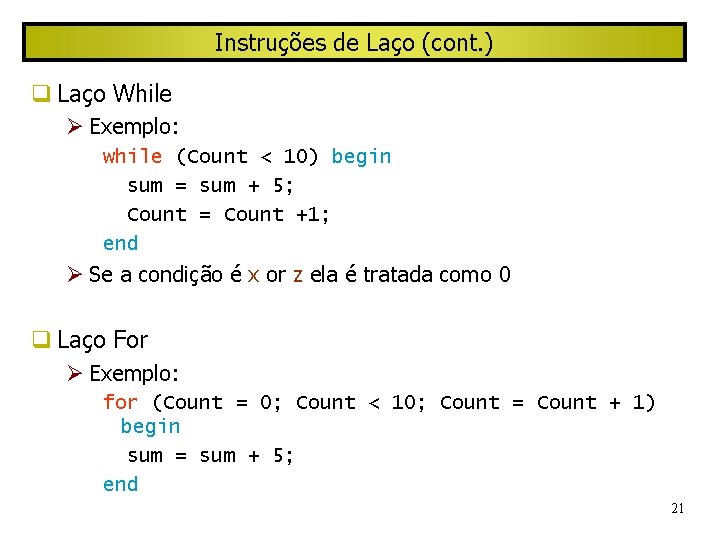

Instruções de Laços Repeat While For Laço repeat Exemplo: repeat (Count) sum = sum + 5; Se a condição é x or z ela é tratada como 0 20

Instruções de Laço (cont. ) Laço While Exemplo: while (Count < 10) begin sum = sum + 5; Count = Count +1; end Se a condição é x or z ela é tratada como 0 Laço For Exemplo: for (Count = 0; Count < 10; Count = Count + 1) begin sum = sum + 5; end 21

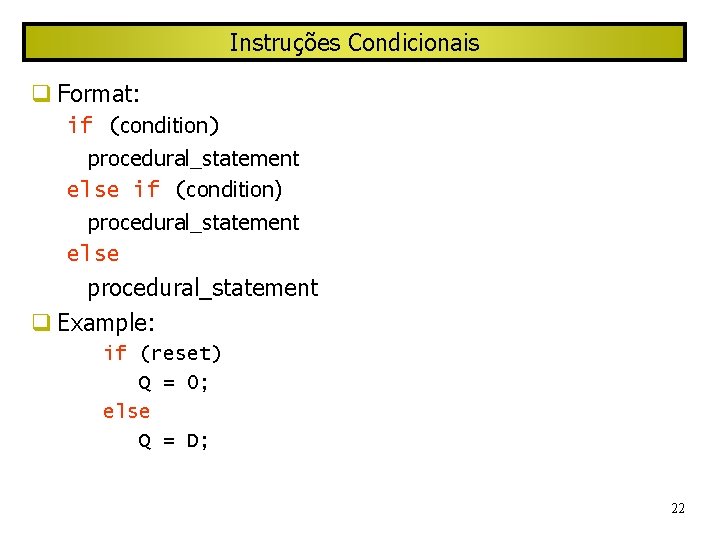

Instruções Condicionais Format: if (condition) procedural_statement else procedural_statement Example: if (reset) Q = 0; else Q = D; 22

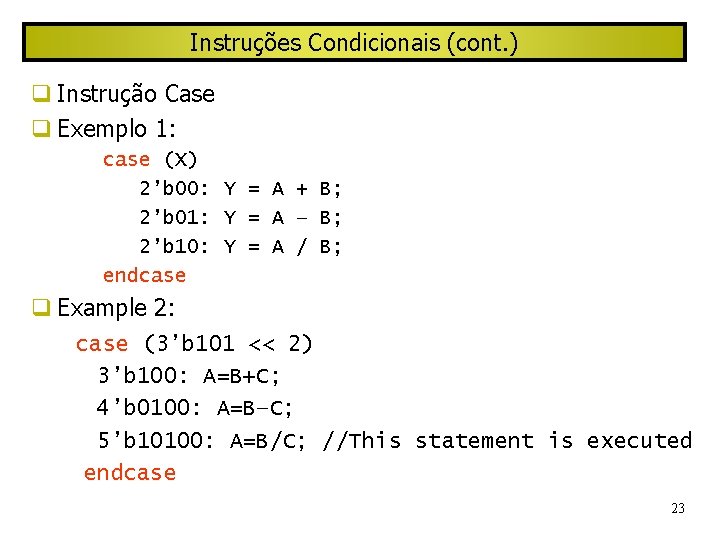

Instruções Condicionais (cont. ) Instrução Case Exemplo 1: case (X) 2’b 00: Y = A + B; 2’b 01: Y = A – B; 2’b 10: Y = A / B; endcase Example 2: case (3’b 101 << 2) 3’b 100: A=B+C; 4’b 0100: A=B–C; 5’b 10100: A=B/C; //This statement is executed endcase 23

![Data Types Net Type Wire wire msb lsb wire 1 wire Data Types Net Type: Wire wire [ msb : lsb ] wire 1, wire](https://slidetodoc.com/presentation_image/5d37636584006c7178fb12d707caaa46/image-24.jpg)

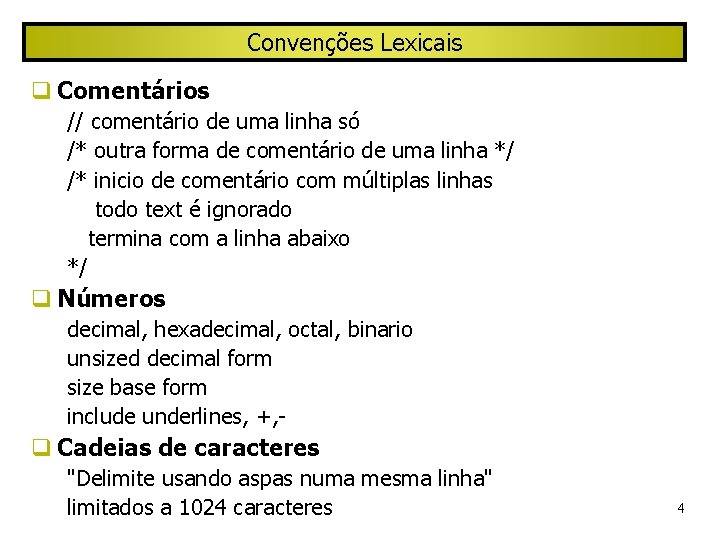

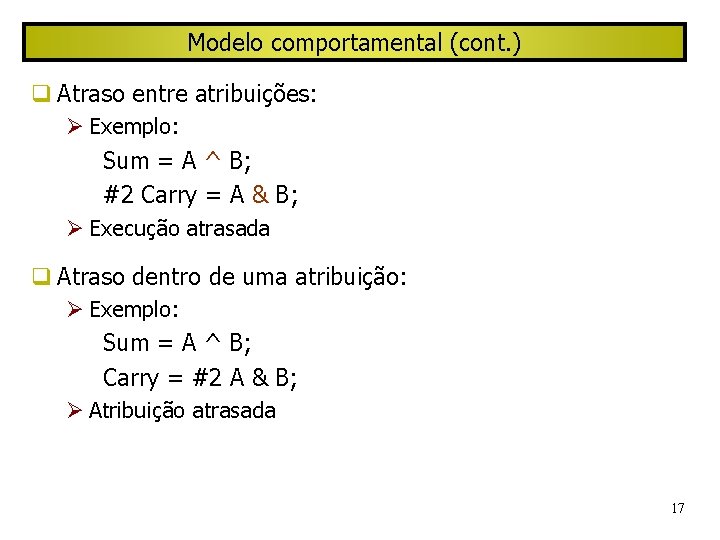

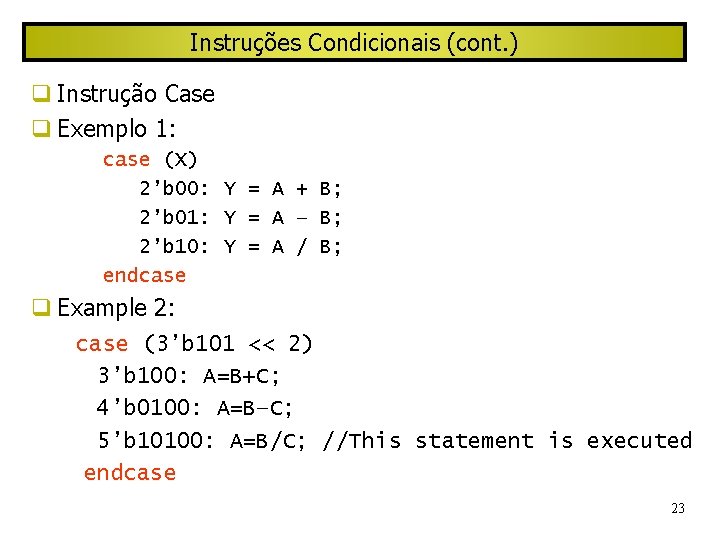

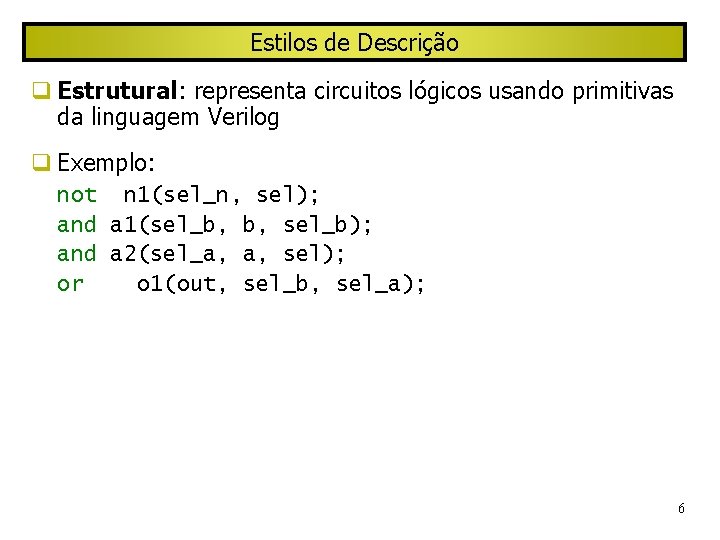

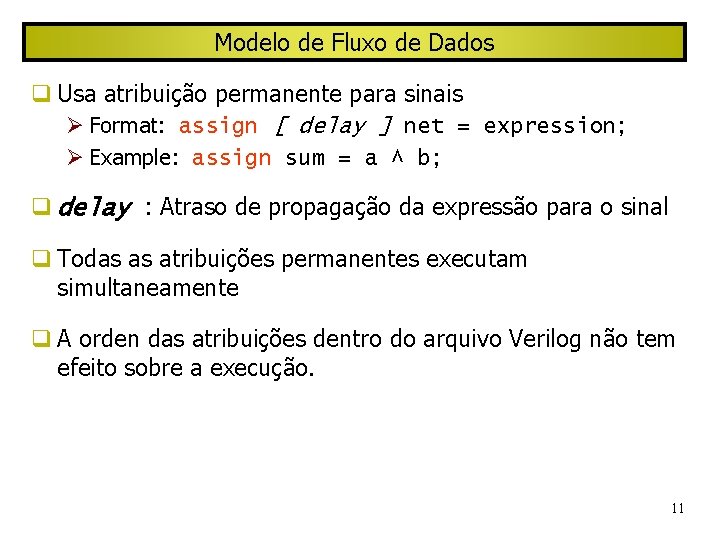

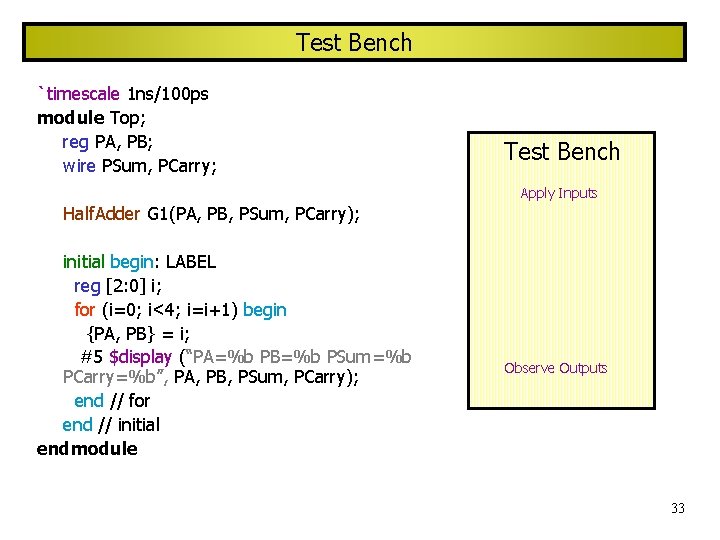

Data Types Net Type: Wire wire [ msb : lsb ] wire 1, wire 2, … Example wire Reset; // A 1 -bit wire [6: 0] Clear; // A 7 -bit wire Register Type: Reg reg [ msb : lsb ] reg 1, reg 2, … Example reg [ 3: 0 ] cla; // A 4 -bit register reg cla; // A 1 -bit register 24

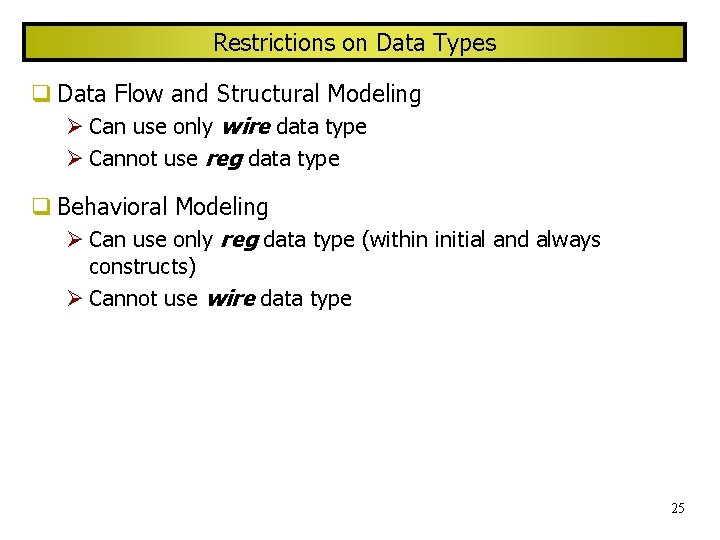

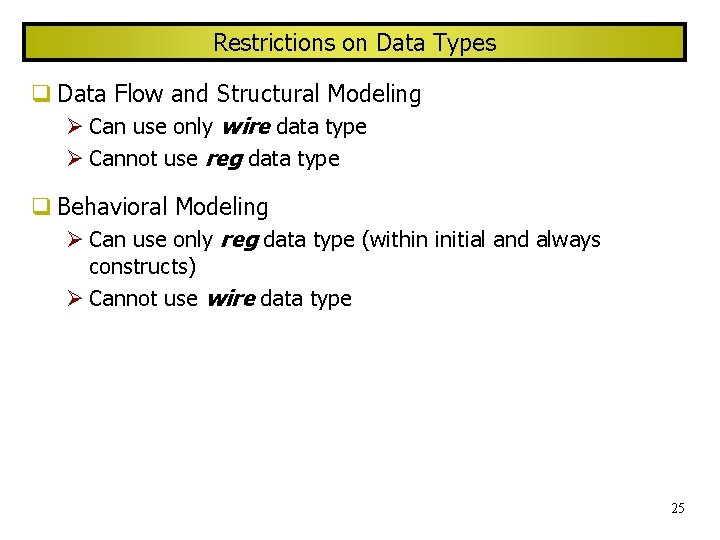

Restrictions on Data Types Data Flow and Structural Modeling Can use only wire data type Cannot use reg data type Behavioral Modeling Can use only reg data type (within initial and always constructs) Cannot use wire data type 25

![Memories An array of registers reg msb lsb memory 1 Memories An array of registers reg [ msb : lsb ] memory 1 [](https://slidetodoc.com/presentation_image/5d37636584006c7178fb12d707caaa46/image-26.jpg)

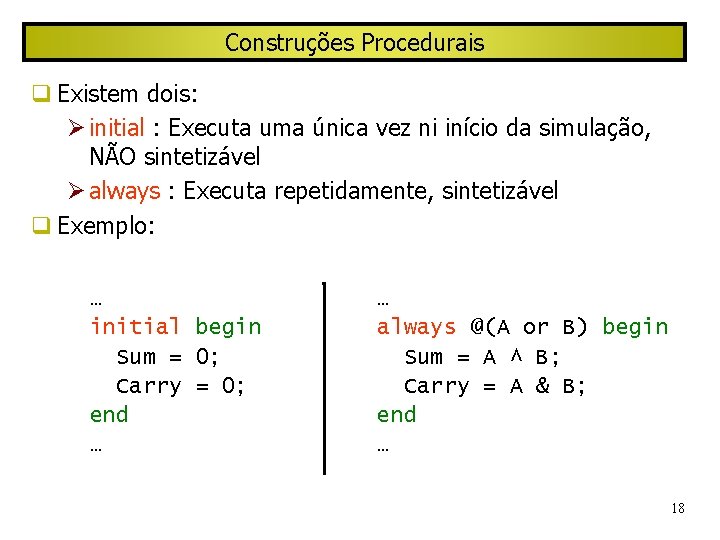

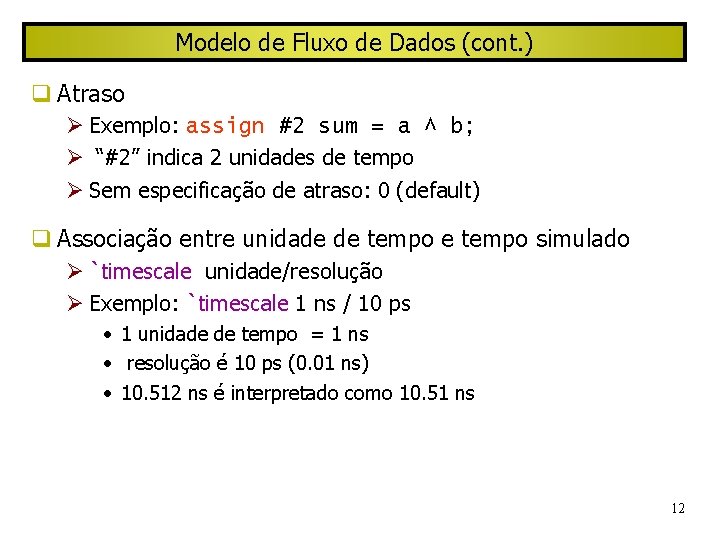

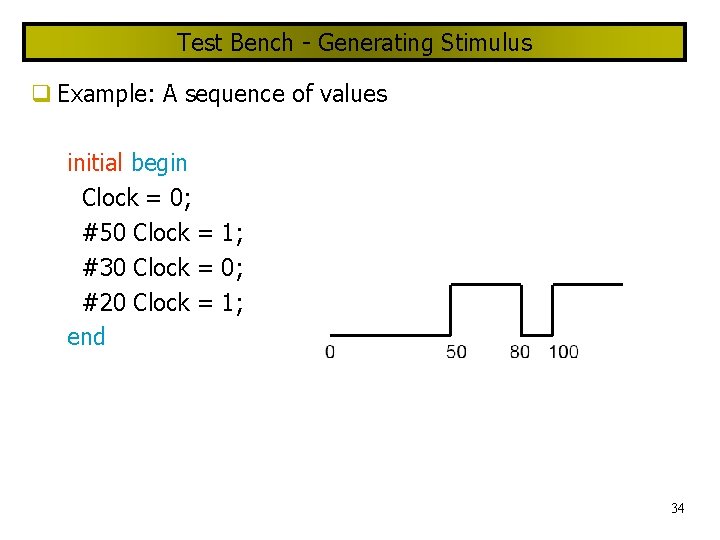

Memories An array of registers reg [ msb : lsb ] memory 1 [ upper : lower ]; Example reg [ 0 : 3 ] mem [ 0 : 63 ]; // An array of 64 4 -bit registers reg mem [ 0 : 4 ]; // An array of 5 1 -bit registers 26

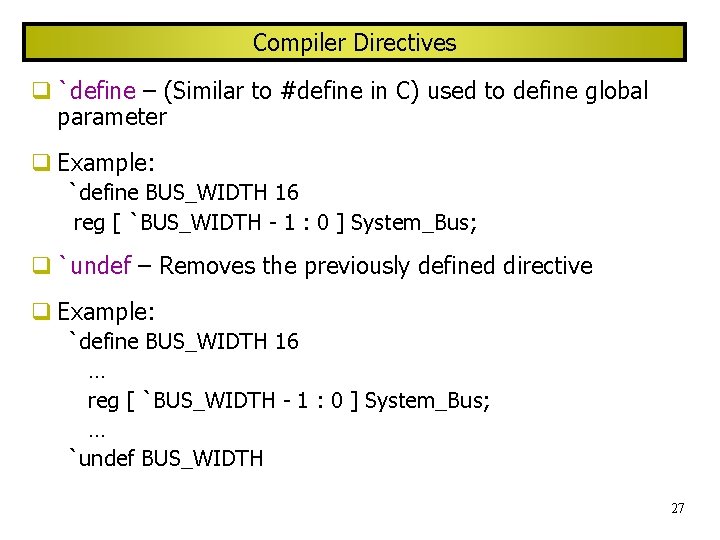

Compiler Directives `define – (Similar to #define in C) used to define global parameter Example: `define BUS_WIDTH 16 reg [ `BUS_WIDTH - 1 : 0 ] System_Bus; `undef – Removes the previously defined directive Example: `define BUS_WIDTH 16 … reg [ `BUS_WIDTH - 1 : 0 ] System_Bus; … `undef BUS_WIDTH 27

Compiler Directives (cont. ) `include – used to include another file Example `include “. /fulladder. v” 28

System Tasks Display tasks $display : Displays the entire list at the time when statement is encountered $monitor : Whenever there is a change in any argument, displays the entire list at end of time step Simulation Control Task $finish : makes the simulator to exit $stop : suspends the simulation Time $time: gives the simulation 29

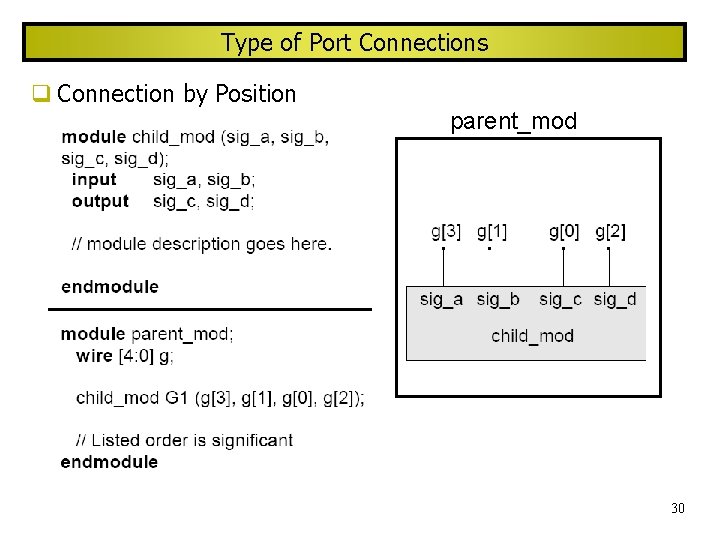

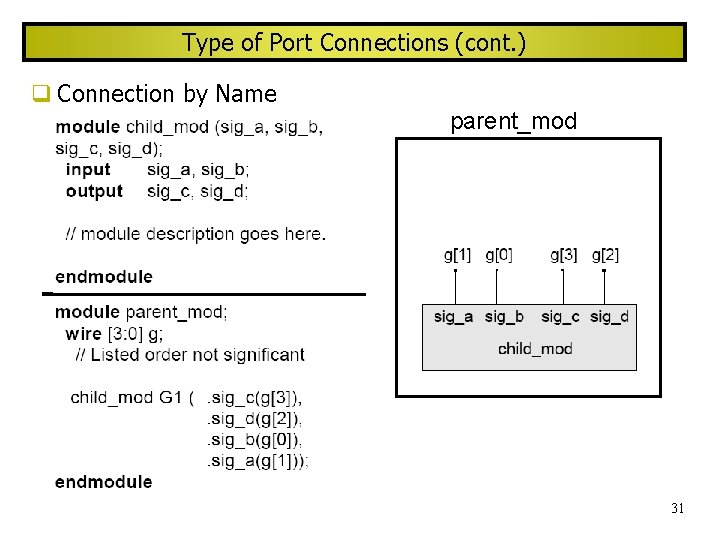

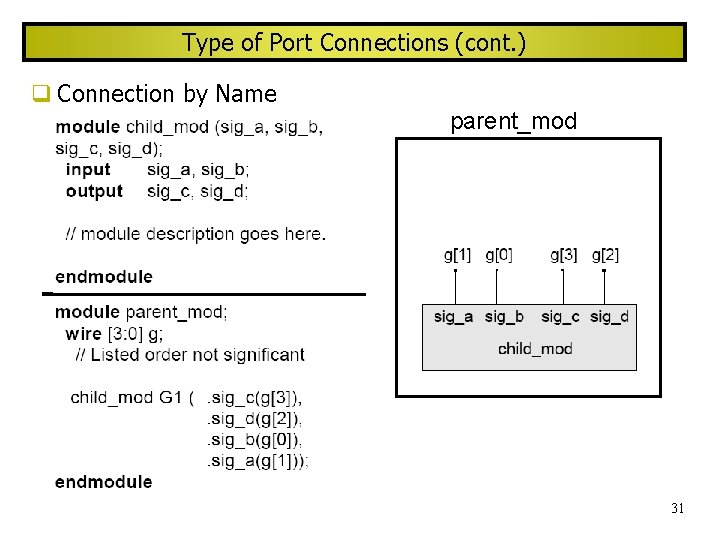

Type of Port Connections Connection by Position parent_mod 30

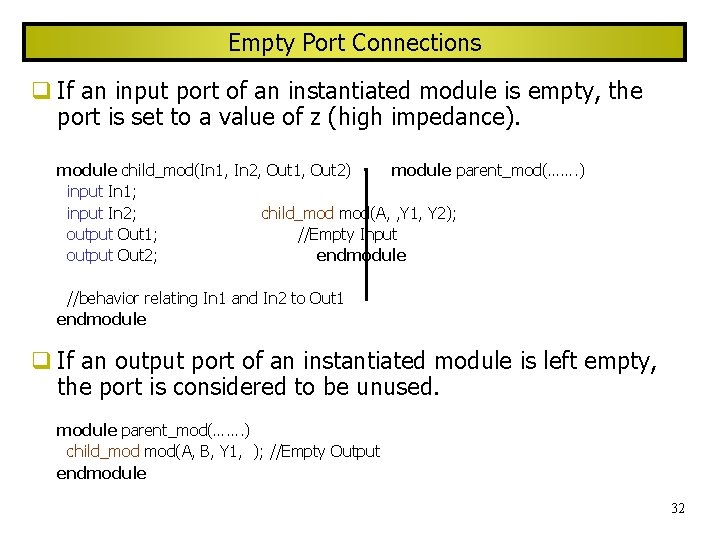

Type of Port Connections (cont. ) Connection by Name parent_mod 31

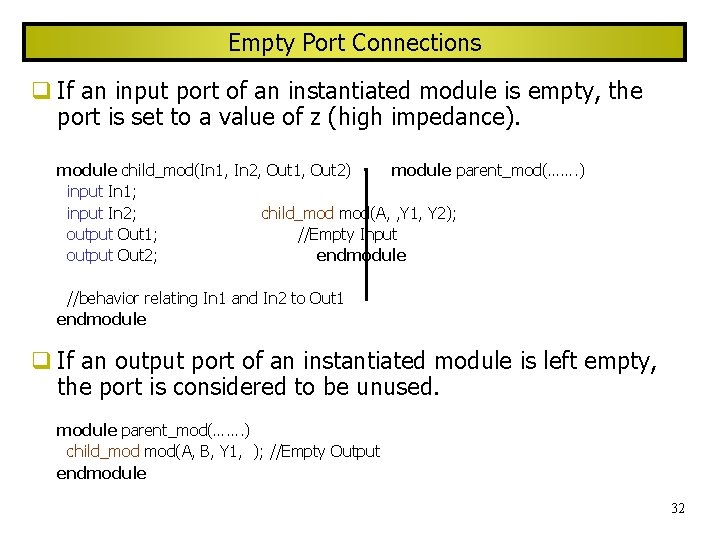

Empty Port Connections If an input port of an instantiated module is empty, the port is set to a value of z (high impedance). module child_mod(In 1, In 2, Out 1, Out 2) module parent_mod(……. ) input In 1; input In 2; child_mod mod(A, , Y 1, Y 2); output Out 1; //Empty Input output Out 2; endmodule //behavior relating In 1 and In 2 to Out 1 endmodule If an output port of an instantiated module is left empty, the port is considered to be unused. module parent_mod(……. ) child_mod mod(A, B, Y 1, ); //Empty Output endmodule 32

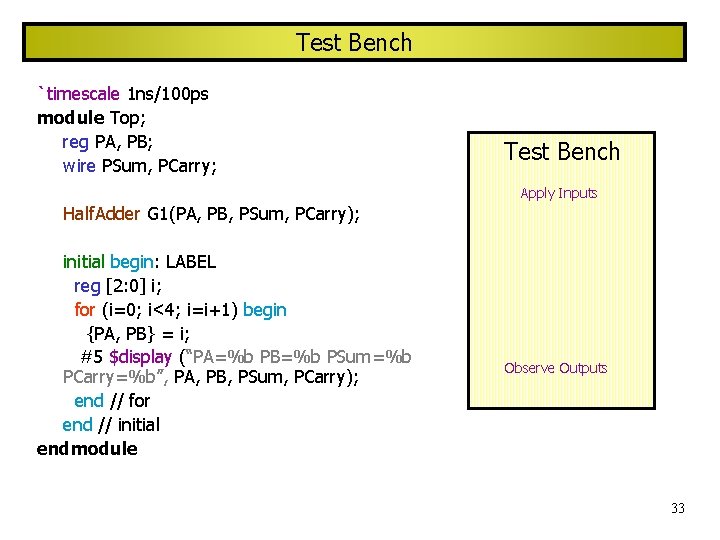

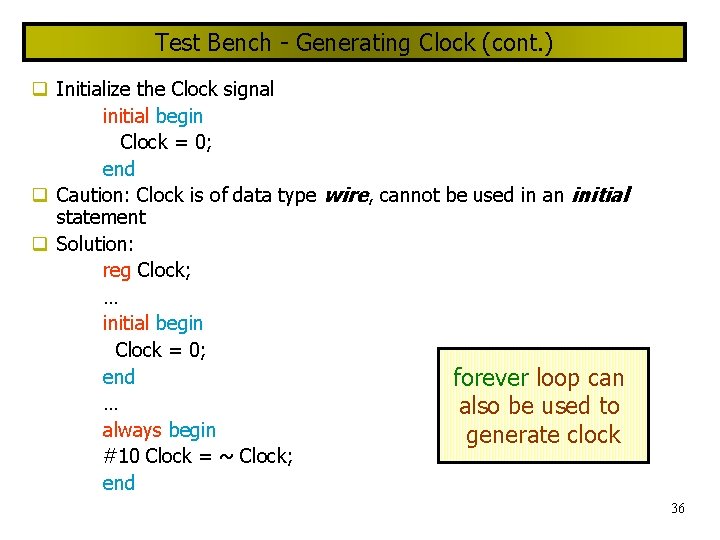

Test Bench `timescale 1 ns/100 ps module Top; reg PA, PB; wire PSum, PCarry; Test Bench Apply Inputs Half. Adder G 1(PA, PB, PSum, PCarry); initial begin: LABEL reg [2: 0] i; for (i=0; i<4; i=i+1) begin {PA, PB} = i; #5 $display (“PA=%b PB=%b PSum=%b PCarry=%b”, PA, PB, PSum, PCarry); end // for end // initial endmodule Observe Outputs 33

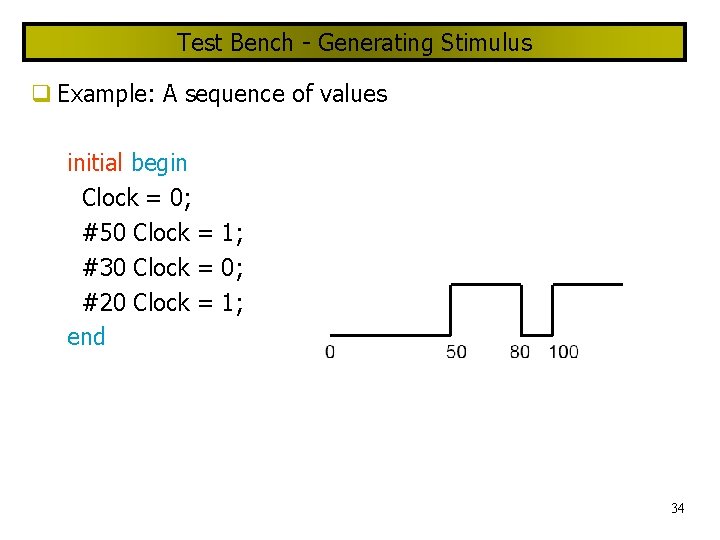

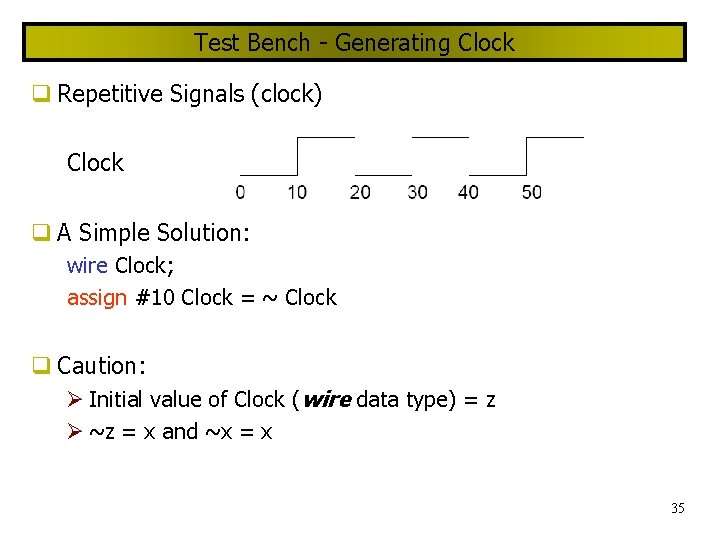

Test Bench - Generating Stimulus Example: A sequence of values initial begin Clock = 0; #50 Clock = 1; #30 Clock = 0; #20 Clock = 1; end 34

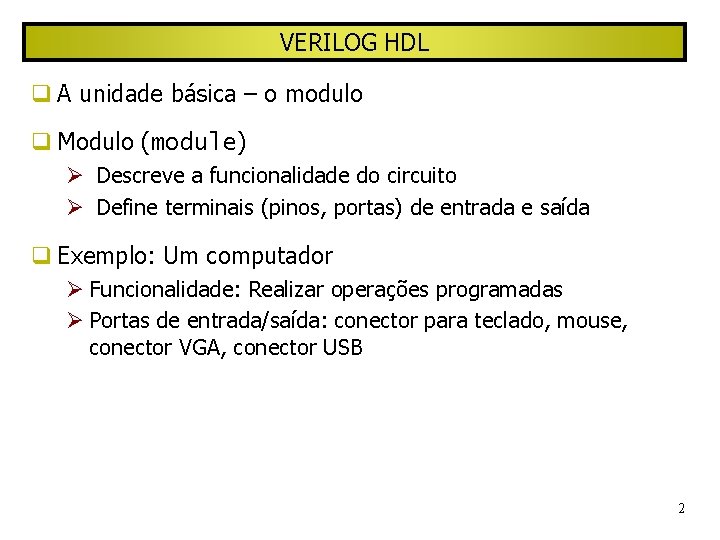

Test Bench - Generating Clock Repetitive Signals (clock) Clock A Simple Solution: wire Clock; assign #10 Clock = ~ Clock Caution: Initial value of Clock (wire data type) = z ~z = x and ~x = x 35

Test Bench - Generating Clock (cont. ) Initialize the Clock signal initial begin Clock = 0; end Caution: Clock is of data type wire, cannot be used in an initial statement Solution: reg Clock; … initial begin Clock = 0; end forever loop can … also be used to always begin generate clock #10 Clock = ~ Clock; end 36