Hardware Architecture Design Media IC and System Lab

Hardware Architecture Design Media IC and System Lab VLSI Crash Course 2018 Presentor: Yu Sheng Lin

Outline ● Hardware design concept. ● Importance of defining hardware protocol. ● Implementation of common protocols. ● Examples. 2

What is Hardware Design? ● Hardware design ≠ algorithm design. ● Hardware design cares about analyzing feasibility of algorithms! ○ Is this easy to implement? ● Is this algorithm efficient to implement? ○ Speedup compared to software? ○ Random data access? ○ Memory usage (DRAM, SRAM, Register. . . )? ○ Memory bandwidth? 3

What is Hardware Design? ● Given a top-level hardware view. ● Breakdown the system and keep asking: ● How large is the memory? (Very important) ● How fast is the memory? (Very important) ● How many computation units do you need? (Important) ● How complex is the control unit? (Hardest to write, but less related to chip area) ● Speed (Premature optimization is the root of all evil) 4

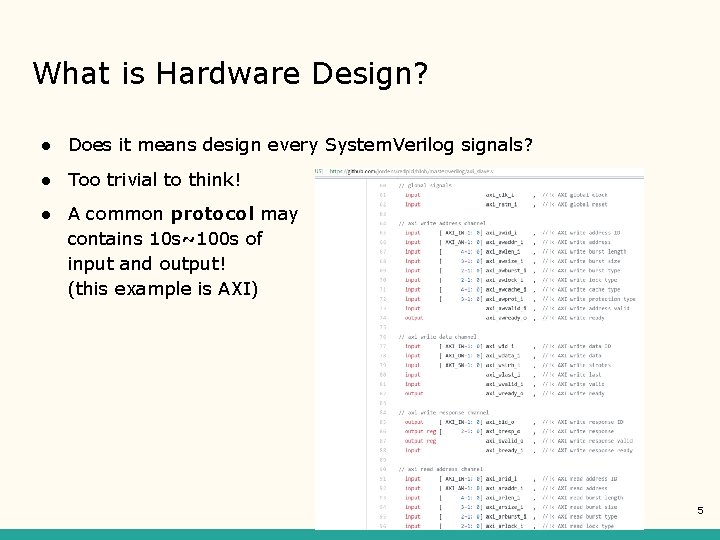

What is Hardware Design? ● Does it means design every System. Verilog signals? ● Too trivial to think! ● A common protocol may contains 10 s~100 s of input and output! (this example is AXI) 5

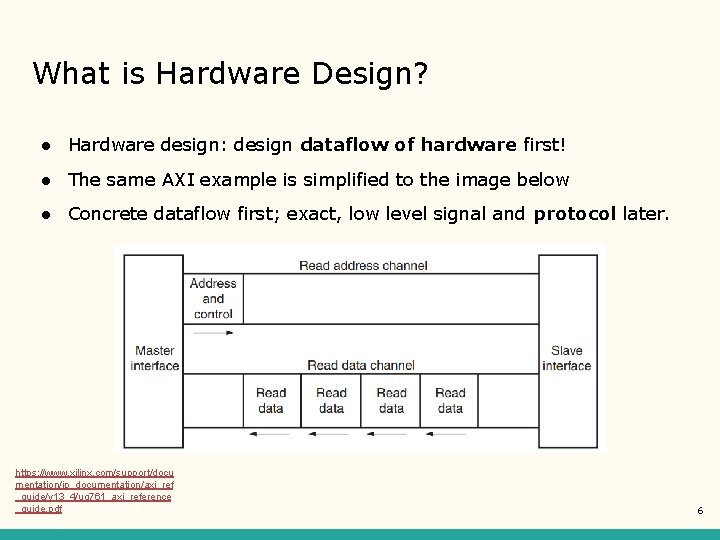

What is Hardware Design? ● Hardware design: design dataflow of hardware first! ● The same AXI example is simplified to the image below ● Concrete dataflow first; exact, low level signal and protocol later. https: //www. xilinx. com/support/docu mentation/ip_documentation/axi_ref _guide/v 13_4/ug 761_axi_reference _guide. pdf 6

Importance of Protocol in Hardware Design ● Design as dataflow, implement as protocol. ● Benefits: ○ Reuse verfication. ○ Play-and-Plug. ○ Uniform code. ○ Widely used and easy to understand. ● Protocol must be simple: ○ Handshake (2 -wire) ○ Streaming (1 -wire) 7

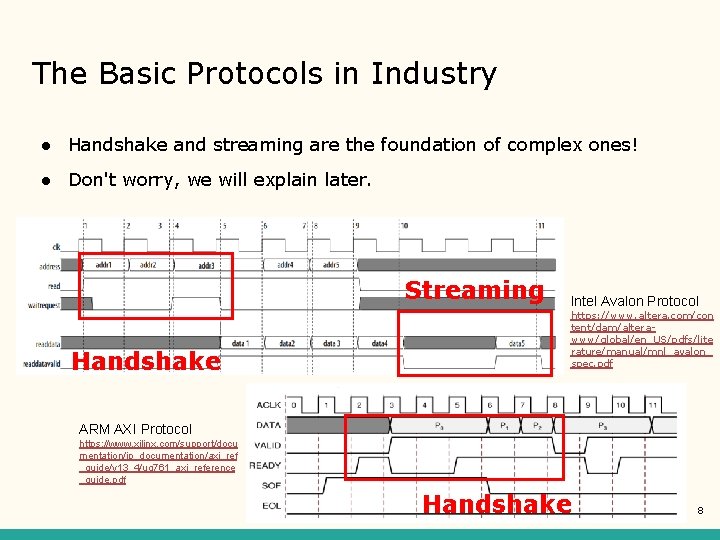

The Basic Protocols in Industry ● Handshake and streaming are the foundation of complex ones! ● Don't worry, we will explain later. Streaming Handshake Intel Avalon Protocol https: //www. altera. com/con tent/dam/alterawww/global/en_US/pdfs/lite rature/manual/mnl_avalon_ spec. pdf ARM AXI Protocol https: //www. xilinx. com/support/docu mentation/ip_documentation/axi_ref _guide/v 13_4/ug 761_axi_reference _guide. pdf Handshake 8

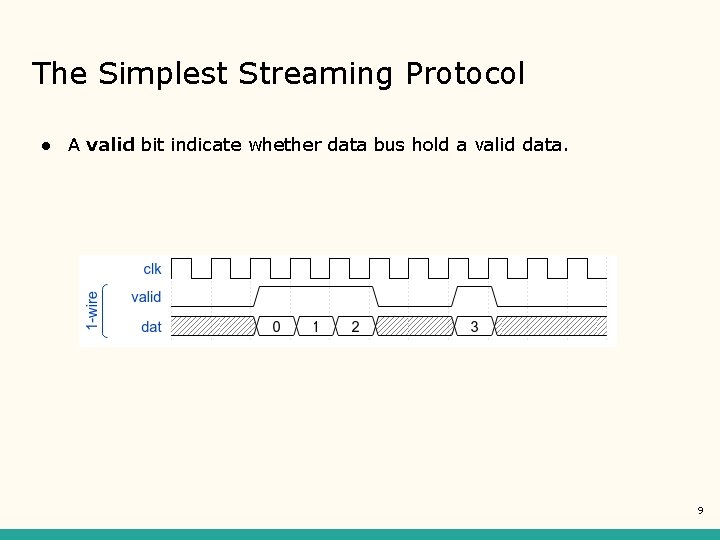

The Simplest Streaming Protocol ● A valid bit indicate whether data bus hold a valid data. 9

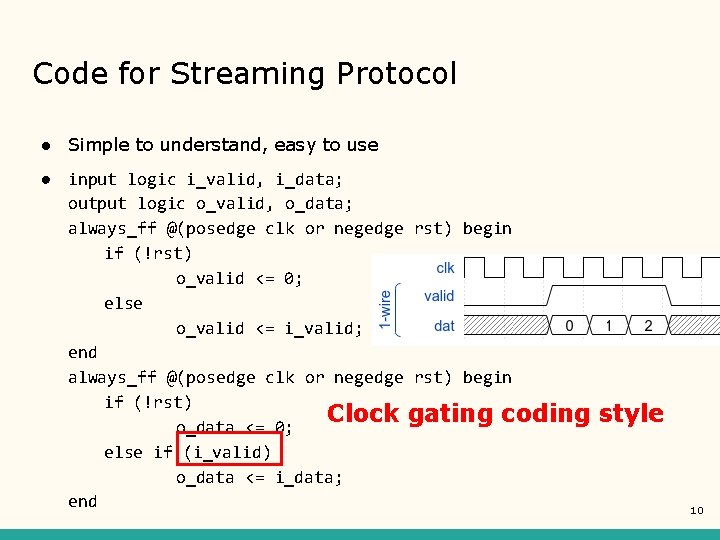

Code for Streaming Protocol ● Simple to understand, easy to use ● input logic i_valid, i_data; output logic o_valid, o_data; always_ff @(posedge clk or negedge rst) begin if (!rst) o_valid <= 0; else o_valid <= i_valid; end always_ff @(posedge clk or negedge rst) begin if (!rst) Clock gating coding o_data <= 0; else if (i_valid) o_data <= i_data; end style 10

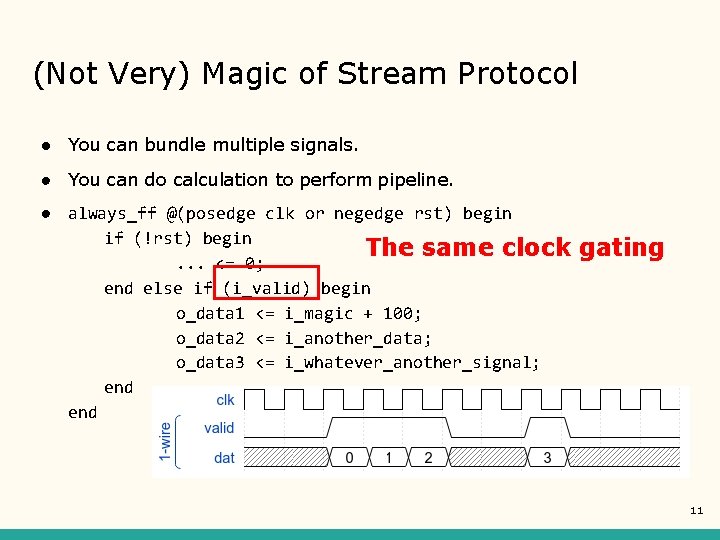

(Not Very) Magic of Stream Protocol ● You can bundle multiple signals. ● You can do calculation to perform pipeline. ● always_ff @(posedge clk or negedge rst) begin if (!rst) begin The same clock. . . <= 0; end else if (i_valid) begin o_data 1 <= i_magic + 100; o_data 2 <= i_another_data; o_data 3 <= i_whatever_another_signal; end gating 11

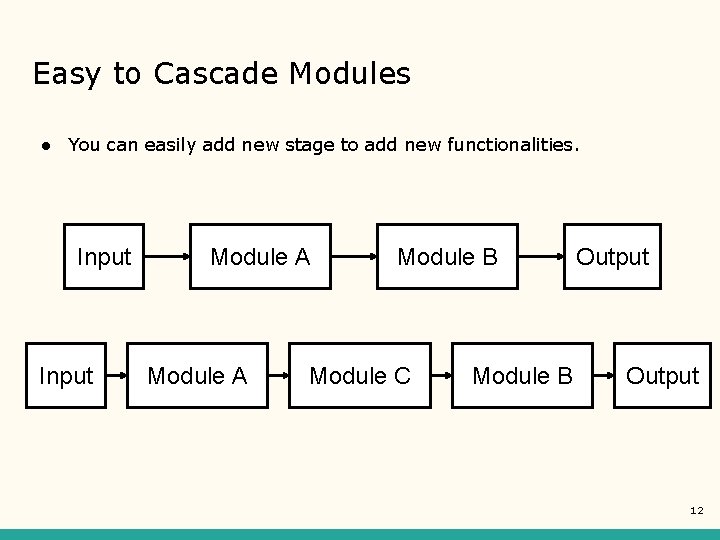

Easy to Cascade Modules ● You can easily add new stage to add new functionalities. Input Module A Module B Module C Module B Output 12

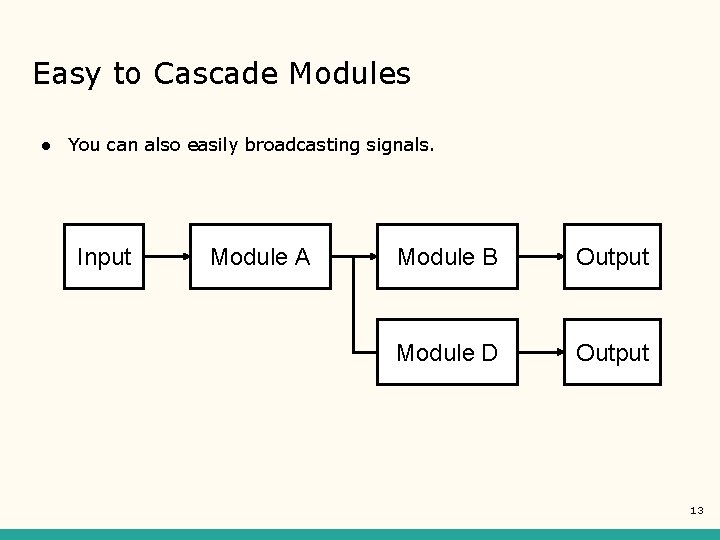

Easy to Cascade Modules ● You can also easily broadcasting signals. Input Module A Module B Output Module D Output 13

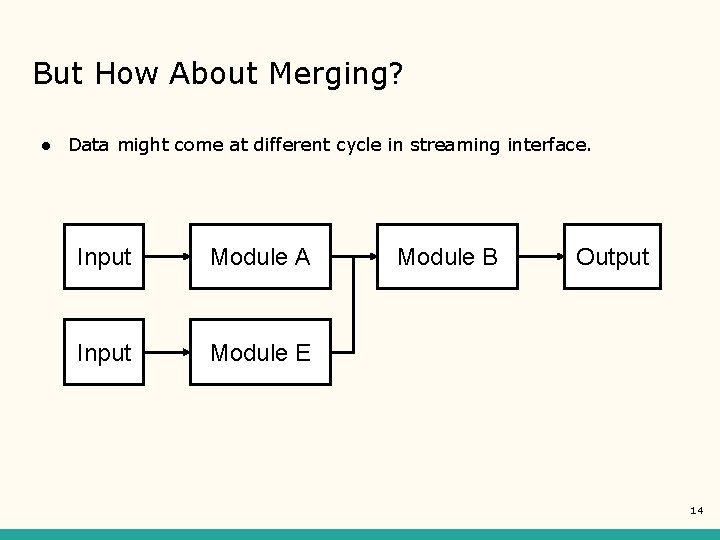

But How About Merging? ● Data might come at different cycle in streaming interface. Input Module A Input Module E Module B Output 14

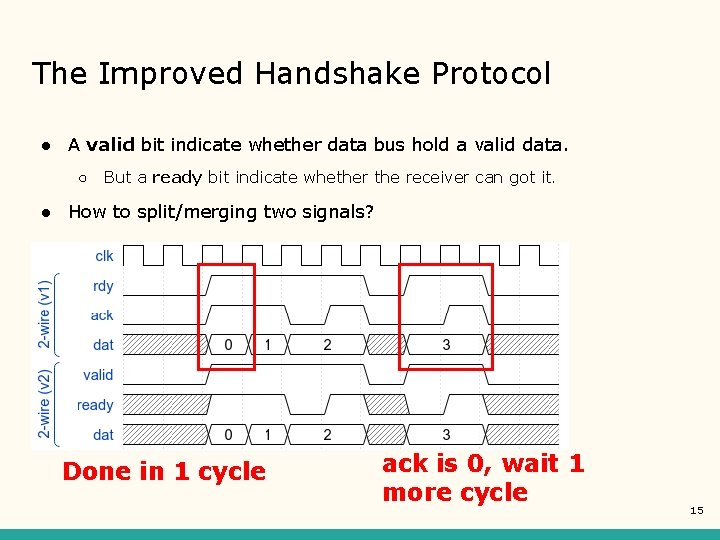

The Improved Handshake Protocol ● A valid bit indicate whether data bus hold a valid data. ○ But a ready bit indicate whether the receiver can got it. ● How to split/merging two signals? Done in 1 cycle ack is 0, wait 1 more cycle 15

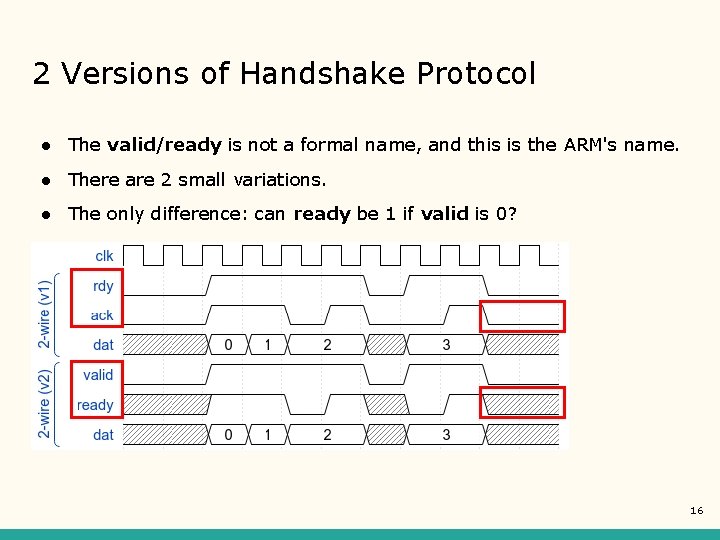

2 Versions of Handshake Protocol ● The valid/ready is not a formal name, and this is the ARM's name. ● There are 2 small variations. ● The only difference: can ready be 1 if valid is 0? 16

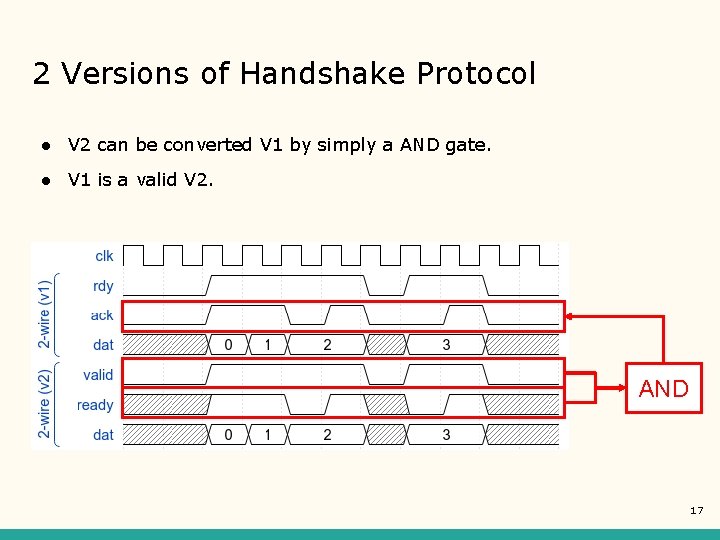

2 Versions of Handshake Protocol ● V 2 can be converted V 1 by simply a AND gate. ● V 1 is a valid V 2. AND 17

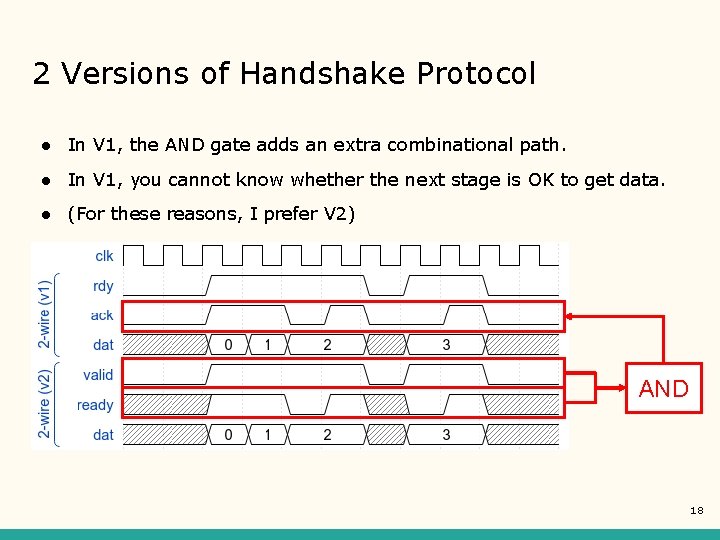

2 Versions of Handshake Protocol ● In V 1, the AND gate adds an extra combinational path. ● In V 1, you cannot know whether the next stage is OK to get data. ● (For these reasons, I prefer V 2) AND 18

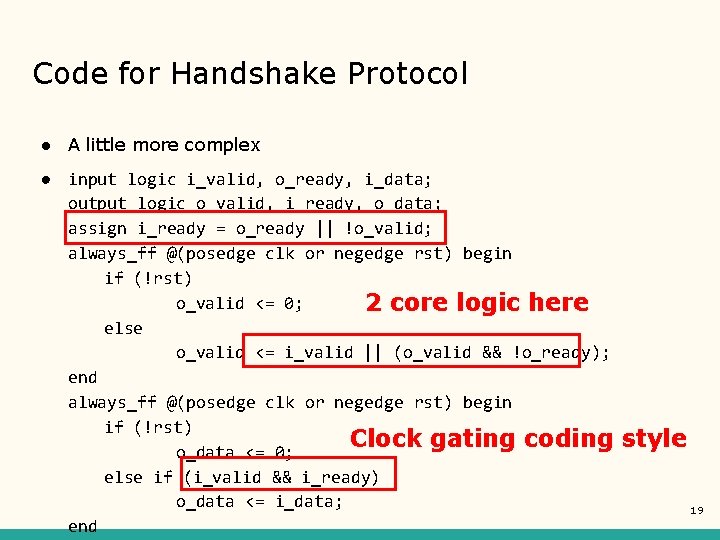

Code for Handshake Protocol ● A little more complex ● input logic i_valid, o_ready, i_data; output logic o_valid, i_ready, o_data; assign i_ready = o_ready || !o_valid; always_ff @(posedge clk or negedge rst) begin if (!rst) o_valid <= 0; 2 core logic here else o_valid <= i_valid || (o_valid && !o_ready); end always_ff @(posedge clk or negedge rst) begin if (!rst) Clock gating coding o_data <= 0; else if (i_valid && i_ready) o_data <= i_data; end style 19

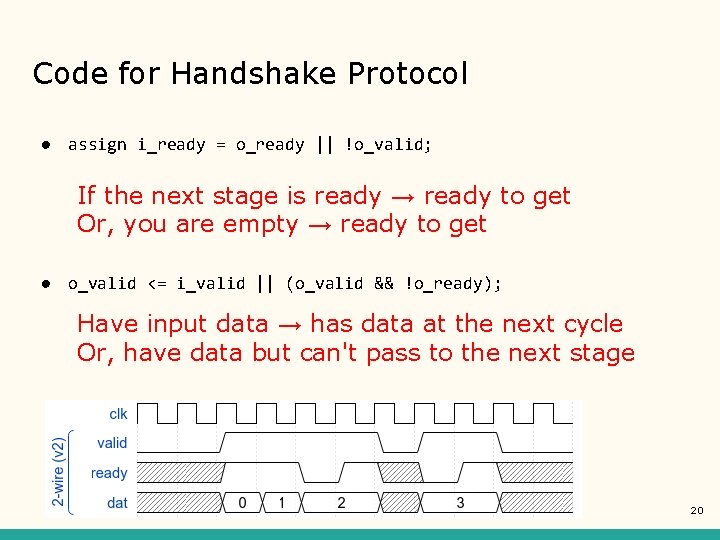

Code for Handshake Protocol ● assign i_ready = o_ready || !o_valid; If the next stage is ready → ready to get Or, you are empty → ready to get ● o_valid <= i_valid || (o_valid && !o_ready); Have input data → has data at the next cycle Or, have data but can't pass to the next stage 20

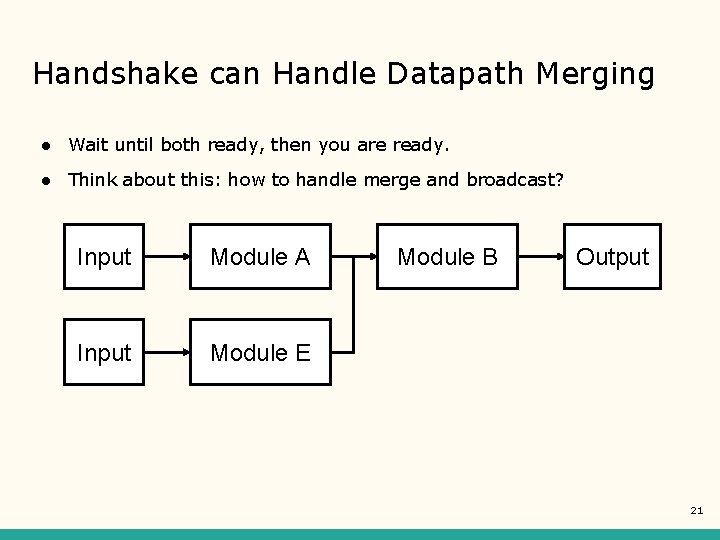

Handshake can Handle Datapath Merging ● Wait until both ready, then you are ready. ● Think about this: how to handle merge and broadcast? Input Module A Input Module E Module B Output 21

Brief Summarize ● Streaming (1 -wire) protocol. ○ Very simple to use. ○ But large, be sure you can always receive the data. ● Handshake (2 -wire) protocol. ○ Can stop the data input. ○ Very very commonly used!! ● Both make easy-to-understand hardware pipeline. ● Both are widely used in industries. 22

(My) Architecture Design Guideline ● Always think through before you write code. ● Always use the same protocol. ○ 1 -wire + 2 -wire can cover very large parts of your design! ○ They can largely replace finite state machines. ● Concrete dataflow first; exact, low level signal later. ○ If you cannot write System. Verilog smoothly, stop and rethink. ○ Or, stop and breakdown to smaller parts. 23

- Slides: 23