Habilitation Diriger des Recherches Calorimetry from LHC to

Habilitation à Diriger des Recherches : Calorimetry from LHC to ILC C. de La Taille 25 sept 2009

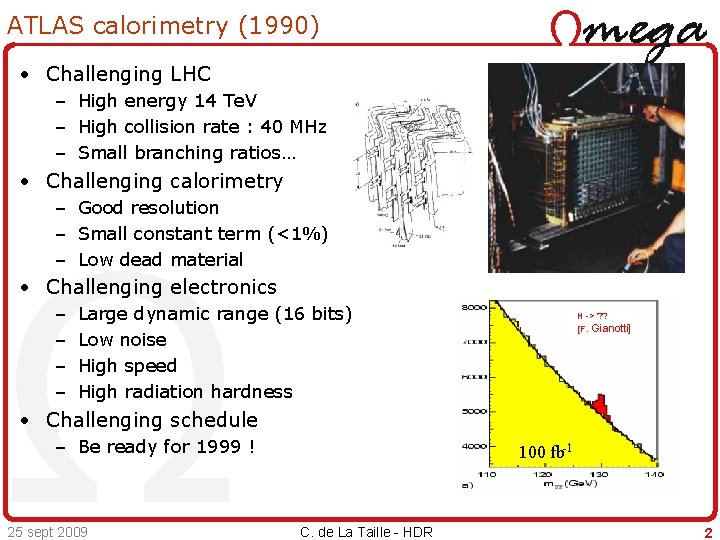

ATLAS calorimetry (1990) • Challenging LHC – High energy 14 Te. V – High collision rate : 40 MHz – Small branching ratios… • Challenging calorimetry – Good resolution – Small constant term (<1%) – Low dead material • Challenging electronics – – Large dynamic range (16 bits) Low noise High speed High radiation hardness H -> ? ? [F. Gianotti] • Challenging schedule – Be ready for 1999 ! 25 sept 2009 100 fb-1 C. de La Taille - HDR 2

![ØT preamps [NIM, Ph. D Y. Jacquier] • Line terminating preamplifiers – – Less ØT preamps [NIM, Ph. D Y. Jacquier] • Line terminating preamplifiers – – Less](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-3.jpg)

ØT preamps [NIM, Ph. D Y. Jacquier] • Line terminating preamplifiers – – Less radiation damage No power inside LAr No noise penalty at fast shaping ENC ~ en/Z*tp • Current sensitive configuration – Avoids saturation with large and long LAr pulses – Parallel noise negligible with fast shaping – Bipolar transistors, exhibit superior series noise (en = 0. 4 n. V/√Hz) 25 sept 2009 C. de La Taille - HDR 3

![Shaping [LArg 10] • Optimize signal to noise ratio between electronics noise and pileup Shaping [LArg 10] • Optimize signal to noise ratio between electronics noise and pileup](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-4.jpg)

Shaping [LArg 10] • Optimize signal to noise ratio between electronics noise and pileup noise – – High pass to clip long Lar tail Low pass to reduce series noise Optimum noise varies with luminosity • Several notes on theoretical analysis [Lar. G 10, LAr. G 35] – Current sensitive preamp : ENI instead of ENC – Pileup noise analysis – Effect of preamp risetime – Peaking time measurement tp 5% – Alleviates 2 nd stage noise issues • ENI = A/tp 3/2 + B/√tp • Pileup : ENE = C√tp 25 sept 2009 C. de La Taille - HDR 4

![The LAr CRRC 2 shaper [LArg 92] • 4 channels tri-gain shaper – – The LAr CRRC 2 shaper [LArg 92] • 4 channels tri-gain shaper – –](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-5.jpg)

The LAr CRRC 2 shaper [LArg 92] • 4 channels tri-gain shaper – – – – – Gain ratio 1 -10 -100 Low noise (2 n. V/√Hz) High linearity (0. 1%) Low crosstalk (0. 1%) 30 ns peaking time Trimming with fuses to 1 ns High power (150 m. W/channel) AMS 1. 2 µm Bi. CMOS technology 80 000 chips produced in 1998 Lots of irradiation tests ! 25 sept 2009 C. de La Taille - HDR 5

![Digital filtering [LAr. G 80, Ph. D Y. Jacquier] • Multiple Sampling technique [Cleland Digital filtering [LAr. G 80, Ph. D Y. Jacquier] • Multiple Sampling technique [Cleland](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-6.jpg)

Digital filtering [LAr. G 80, Ph. D Y. Jacquier] • Multiple Sampling technique [Cleland 1996] Sampled signal shape – Linear combination of 5 samples on waveform to optimize noise – Finite Impulse Filter • Signal : s(t)=Ag(t)+b – – A : amplitude G(t) : normalised signal shape B : noise Sampled signal : si=Agi+bi Autocorrelation function • Filter : weighted sum Σ ai si – ai = Σ R-1 ij gi – R = autocorrelation fonction – gi = signal shape (0, 0. 63, 1, 0. 8, 0. 47) – S = Σ aisi 25 sept 2009 C. de La Taille - HDR 6

Digital Filtering (2) • Slowing down the signal A = (0. 17, 0. 34, 0. 31, 0. 28) – Reduction of series noise – Similar to a simple integration [ATLAS-LAr. G-080] • Accelererating the signal – Reduction of pileup noise – Similar to a differentiation • Measuring the timing A = (-0. 75, 0. 47, 0. 75, 0. 07, -0. 19) • Several questions [Ph. D Jacquier] – How does-it compare to an analog filter ? – How many samples are needed ? – What accuracy is needed on the waveform and on the autocorrelation ? – What analog shaping time is needed ? – Is the analog filter really useful ? 25 sept 2009 C. de La Taille - HDR 7

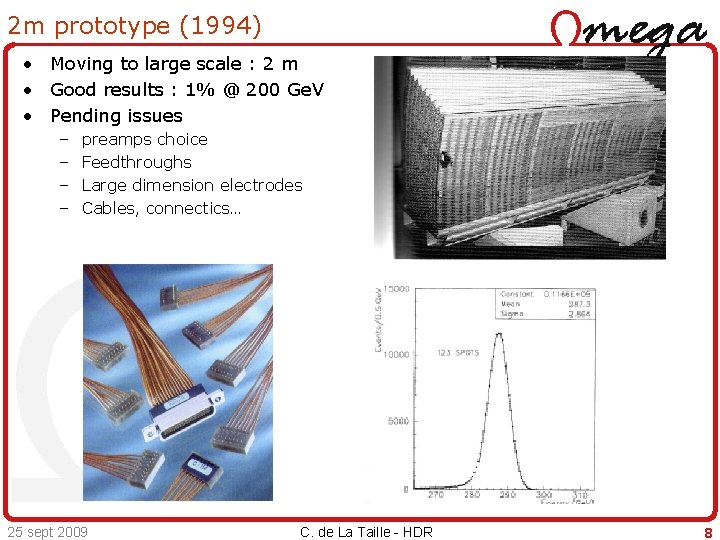

2 m prototype (1994) • Moving to large scale : 2 m • Good results : 1% @ 200 Ge. V • Pending issues – – preamps choice Feedthroughs Large dimension electrodes Cables, connectics… 25 sept 2009 C. de La Taille - HDR 8

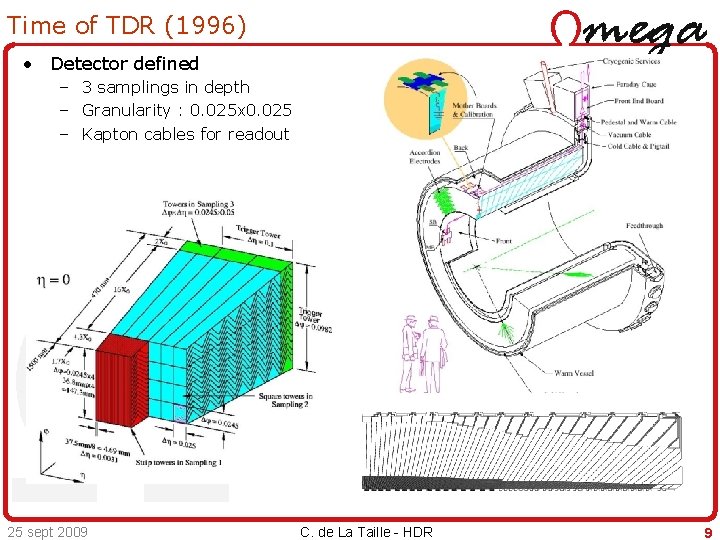

Time of TDR (1996) • Detector defined – 3 samplings in depth – Granularity : 0. 025 x 0. 025 – Kapton cables for readout 25 sept 2009 C. de La Taille - HDR 9

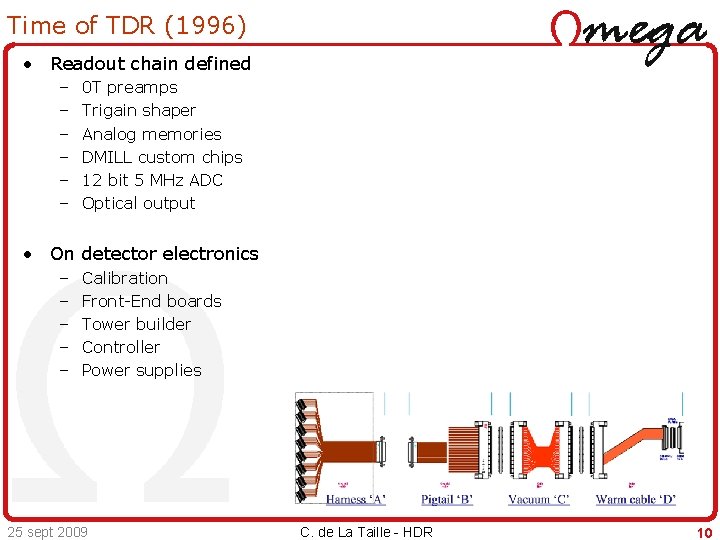

Time of TDR (1996) • Readout chain defined – – – 0 T preamps Trigain shaper Analog memories DMILL custom chips 12 bit 5 MHz ADC Optical output • On detector electronics – – – Calibration Front-End boards Tower builder Controller Power supplies 25 sept 2009 C. de La Taille - HDR 10

![Calibration [NIM] • Generate 0. 1% accuracy pulse over 16 bits dynamic range ROOM Calibration [NIM] • Generate 0. 1% accuracy pulse over 16 bits dynamic range ROOM](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-11.jpg)

Calibration [NIM] • Generate 0. 1% accuracy pulse over 16 bits dynamic range ROOM T LAr – Inject with 0. 1% accuracy resistor – Fabricate fast accurate pulse 50 µV to 5 V, tr ~1 ns, td ~400 ns – Operate in magnetic field ~100 Gauss – Tolerate radiations • Uniformity < 0. 25% 0. 1% Rinj 25 sept 2009 C. de La Taille - HDR 11

History • 12 boards produced in 1998 with COTS for module 0 – 5 years successful operation in beam tests. – Excellent uniformity : 0. 11% rms on 1300 channels – But radiation soft : COTS failed at 20 Gy • Active elements designed in DMILL in 1999 -2001 – DAC, Pulser, Control logic, delay chip – Radiation qualified at 5 k. Gy – Improved performance (DAC stability, parasitic signal at DAC=0, DAC stability and offset) – Simplified logic, 10 Alteras replaced by 6 identical ASICs (DMILL Calogic) – All ASICs produced in 2003 (30 000 opamps) • First final boards produced in 2002 -2003 – Final design review in 2002 – Production readiness review passed in march 2004 – Production of 140 boards in 2004 -2005 25 sept 2009 C. de La Taille - HDR Uniformity of Calib 0 12

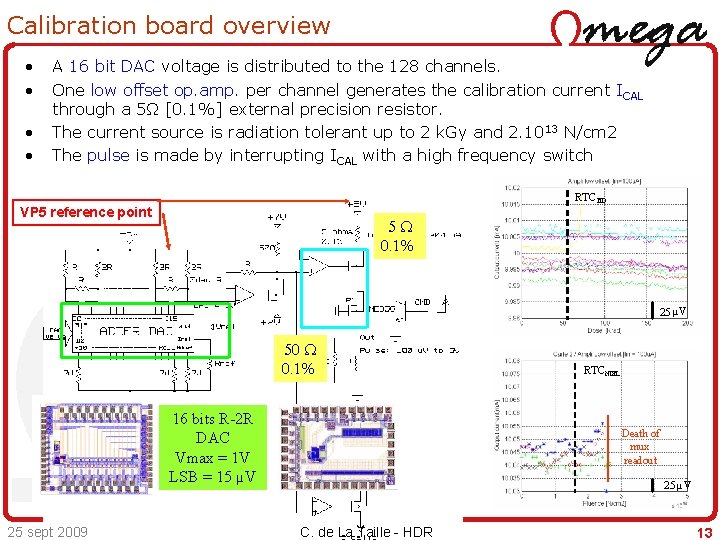

Calibration board overview • • A 16 bit DAC voltage is distributed to the 128 channels. One low offset op. amp. per channel generates the calibration current ICAL through a 5Ω [0. 1%] external precision resistor. The current source is radiation tolerant up to 2 k. Gy and 2. 1013 N/cm 2 The pulse is made by interrupting ICAL with a high frequency switch RTCTID VP 5 reference point 5 W 0. 1% 25 µV ? V 50 W 0. 1% 16 bits R-2 R DAC Vmax = 1 V LSB = 15 µV 25 sept 2009 RTCNIEL Death of mux readout 25 µV ? V C. de La Taille - HDR 13

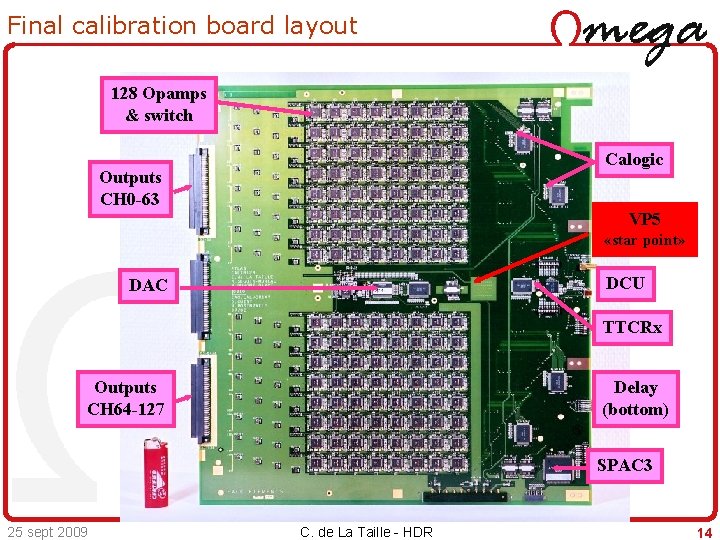

Final calibration board layout 128 Opamps & switch Calogic Outputs CH 0 -63 VP 5 «star point» DCU DAC TTCRx Outputs CH 64 -127 Delay (bottom) SPAC 3 25 sept 2009 C. de La Taille - HDR 14

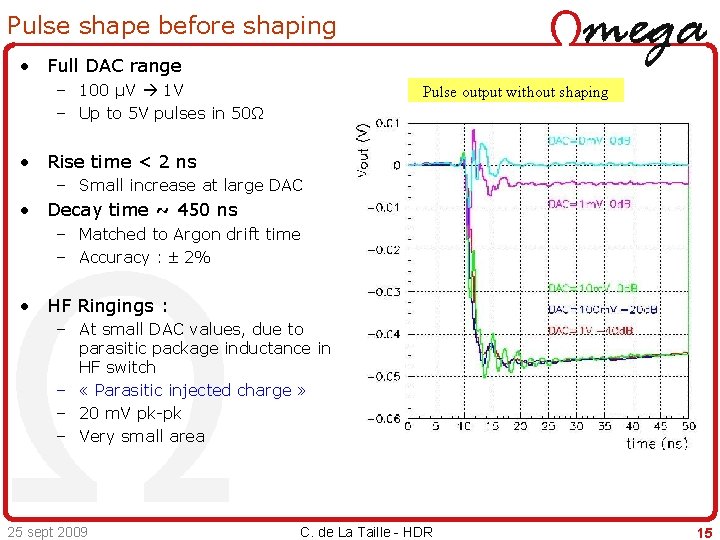

Pulse shape before shaping • Full DAC range – 100 µV 1 V – Up to 5 V pulses in 50Ω Pulse output without shaping • Rise time < 2 ns – Small increase at large DAC • Decay time ~ 450 ns – Matched to Argon drift time – Accuracy : 2% • HF Ringings : – At small DAC values, due to parasitic package inductance in HF switch – « Parasitic injected charge » – 20 m. V pk-pk – Very small area 25 sept 2009 C. de La Taille - HDR 15

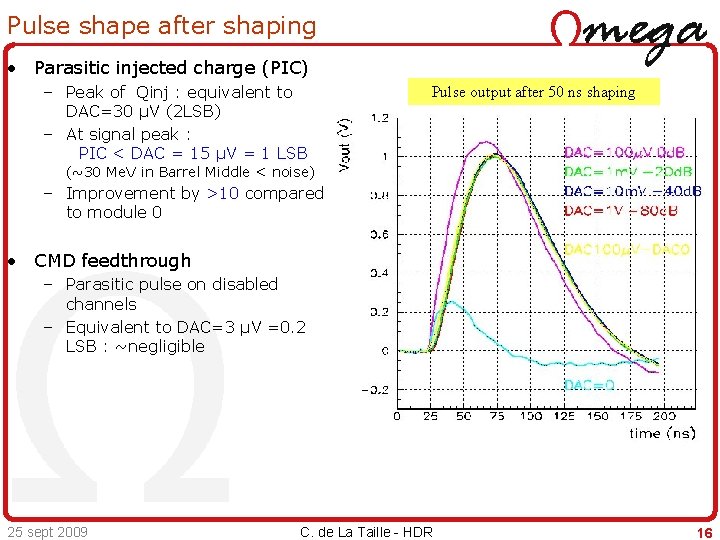

Pulse shape after shaping • Parasitic injected charge (PIC) – Peak of Qinj : equivalent to DAC=30 µV (2 LSB) – At signal peak : PIC < DAC = 15 µV = 1 LSB Pulse output after 50 ns shaping (~30 Me. V in Barrel Middle < noise) – Improvement by >10 compared to module 0 • CMD feedthrough – Parasitic pulse on disabled channels – Equivalent to DAC=3 µV =0. 2 LSB : ~negligible 25 sept 2009 C. de La Taille - HDR 3 = 2 1 16

pulse uniformity and linearity • Linearity : < 0. 1% – – Red : at signal peak Black : peak of signal Dominated by readout non-linearity DC linearity < 0. 01% pulse linearity vs DAC • Uniformity at DAC=5000 – Rms : 0. 13% (DC was 0. 07%) – Additionnal contribution from output resistors, output lines, inductors and scanner board pulse uniformity rms 0. 13% 25 sept 2009 C. de La Taille - HDR 17

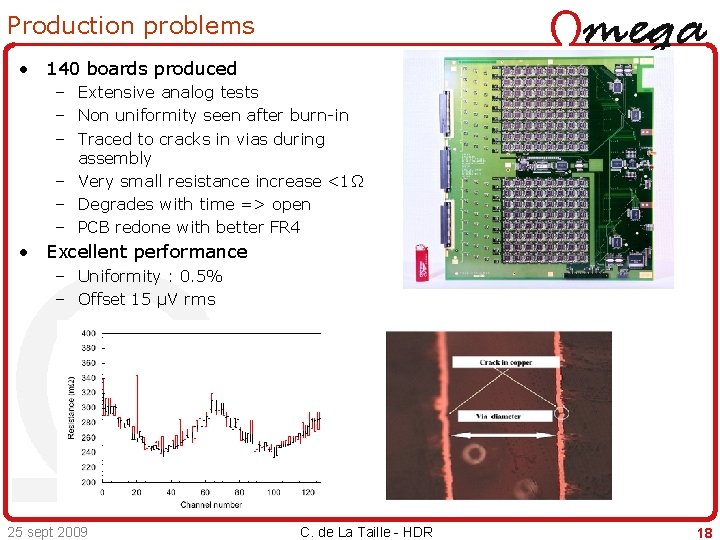

Production problems • 140 boards produced – Extensive analog tests – Non uniformity seen after burn-in – Traced to cracks in vias during assembly – Very small resistance increase <1Ω – Degrades with time => open – PCB redone with better FR 4 • Excellent performance – Uniformity : 0. 5% – Offset 15 µV rms 25 sept 2009 C. de La Taille - HDR 18

Calibration sensitivity to cables • Sensitivity to cable characteristic impedance Zc Amplitude vs cable impedance – Second order effect (if terminated both ends) : d. V/V = 1 – (d. Zc/2 Zc)2 – ± 2. 5Ω on cable gives ± 0. 1% - 0. 1% • Sensitivity to skin effect – First order effect : • - 1. 2 %/m @ 300 K, ± 5% • - 0. 5 %/m @ 77 K – Correction necessary for cable length – Calibration cable length : 3 -6 m : expect ~ 0. 2% contribution at cold (~0. 4% at warm) 25 sept 2009 C. de La Taille - HDR Amplitude vs cable length 19

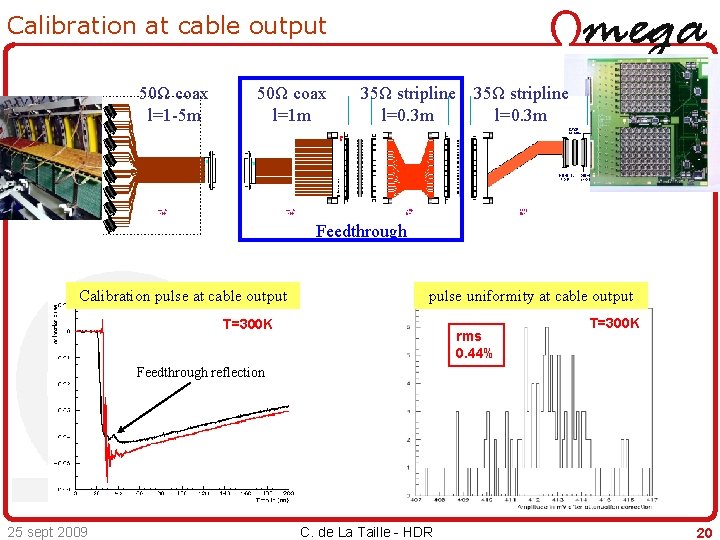

Calibration at cable output 50Ω coax l=1 -5 m 50Ω coax l=1 m 35Ω stripline l=0. 3 m Feedthrough Calibration pulse at cable output pulse uniformity at cable output T=300 K rms 0. 44% T=300 K Feedthrough reflection 25 sept 2009 C. de La Taille - HDR 20

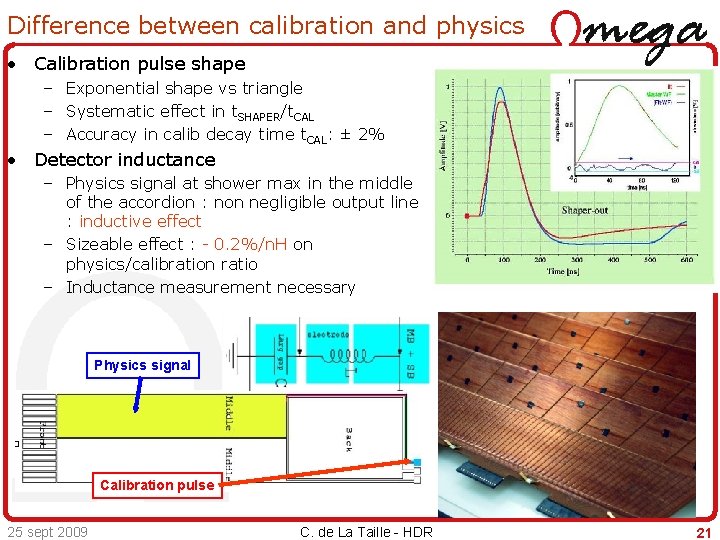

Difference between calibration and physics • Calibration pulse shape – Exponential shape vs triangle – Systematic effect in t. SHAPER/t. CAL – Accuracy in calib decay time t. CAL: ± 2% • Detector inductance – Physics signal at shower max in the middle of the accordion : non negligible output line : inductive effect – Sizeable effect : - 0. 2%/n. H on physics/calibration ratio – Inductance measurement necessary Physics signal Calibration pulse 25 sept 2009 C. de La Taille - HDR 21

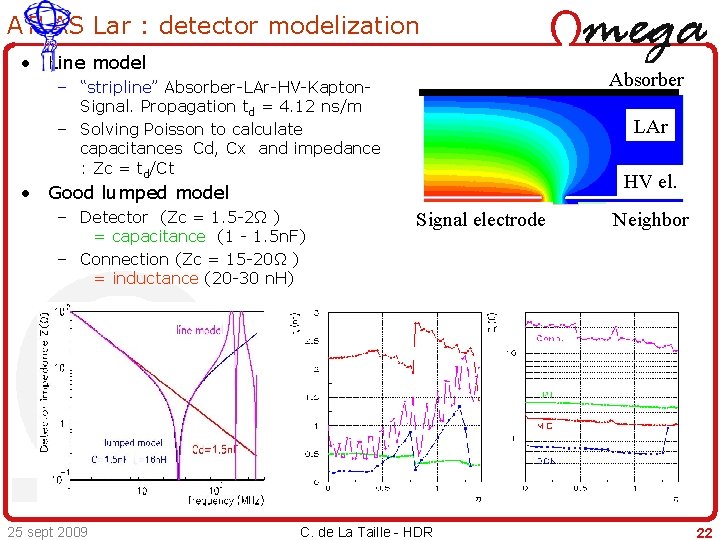

ATLAS Lar : detector modelization • Line model Absorber – “stripline” Absorber-LAr-HV-Kapton. Signal. Propagation td = 4. 12 ns/m – Solving Poisson to calculate capacitances Cd, Cx and impedance : Zc = td/Ct LAr HV el. • Good lumped model – Detector (Zc = 1. 5 -2Ω ) = capacitance (1 - 1. 5 n. F) – Connection (Zc = 15 -20Ω ) = inductance (20 -30 n. H) 25 sept 2009 Signal electrode C. de La Taille - HDR Neighbor 22

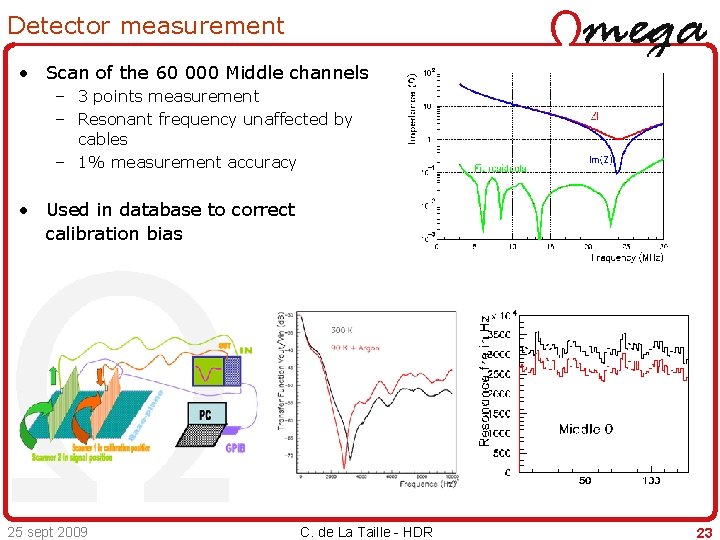

Detector measurement • Scan of the 60 000 Middle channels – 3 points measurement – Resonant frequency unaffected by cables – 1% measurement accuracy • Used in database to correct calibration bias 25 sept 2009 C. de La Taille - HDR 23

![Crosstalk and γ/π0 rejection [LAr. G 31] • Large crosstalk in front strips (8%) Crosstalk and γ/π0 rejection [LAr. G 31] • Large crosstalk in front strips (8%)](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-24.jpg)

Crosstalk and γ/π0 rejection [LAr. G 31] • Large crosstalk in front strips (8%) – – Cx ≈ Cd + fast shaping Can deteriorate γ/π0 rejection Signal broadening Noise correlations • Analtyical calculations – Crosstalk capacitance – Crosstalk signals & noise correlation – Feeds Geant 3 for γ/π0 simulation 25 sept 2009 C. de La Taille - HDR 24

![Crosstalk task force [LAr. G 00 -06] • Some large crosstalk (2 -5%) – Crosstalk task force [LAr. G 00 -06] • Some large crosstalk (2 -5%) –](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-25.jpg)

Crosstalk task force [LAr. G 00 -06] • Some large crosstalk (2 -5%) – Task force formed • Many unusual sources – Inductive loops – Ground resistance – Ground apertures • Actions taken – Redesign of motherboards, summing boards, connectors – Gold plating of feedthroughs 25 sept 2009 C. de La Taille - HDR 25

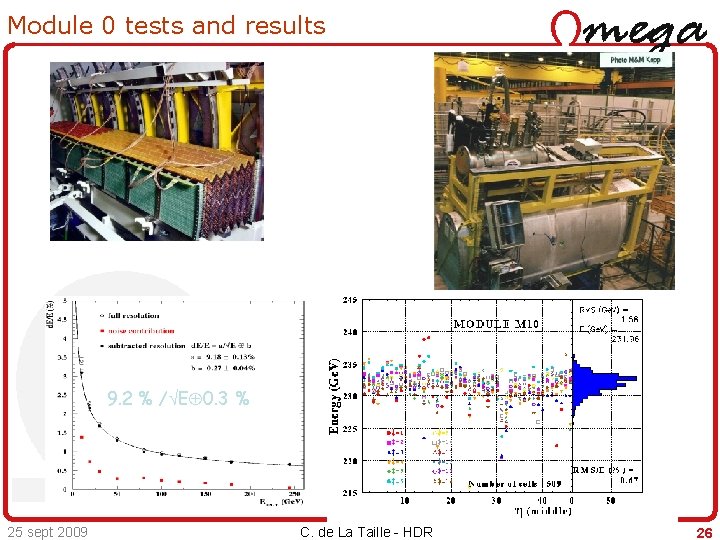

Module 0 tests and results 9. 2 % / E 0. 3 % 25 sept 2009 C. de La Taille - HDR 26

ATLAS ready for data taking (2007) 25 sept 2009 C. de La Taille - HDR 27

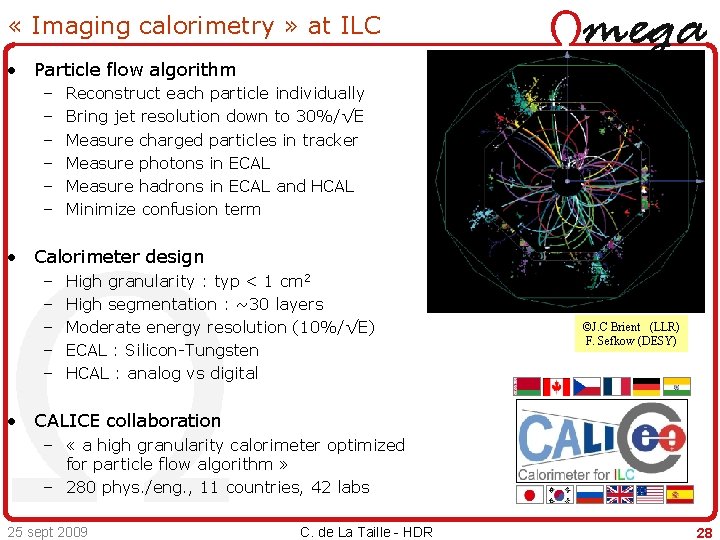

« Imaging calorimetry » at ILC • Particle flow algorithm – – – Reconstruct each particle individually Bring jet resolution down to 30%/√E Measure charged particles in tracker Measure photons in ECAL Measure hadrons in ECAL and HCAL Minimize confusion term • Calorimeter design – – – High granularity : typ < 1 cm 2 High segmentation : ~30 layers Moderate energy resolution (10%/√E) ECAL : Silicon-Tungsten HCAL : analog vs digital ©J. C Brient (LLR) F. Sefkow (DESY) • CALICE collaboration – « a high granularity calorimeter optimized for particle flow algorithm » – 280 phys. /eng. , 11 countries, 42 labs 25 sept 2009 C. de La Taille - HDR 28

ILC Challenges for electronics • Requirements for electronics – – Large dynamic range (15 bits) Auto-trigger on ½ MIP ASIC On chip zero suppress Front-end embedded in detector Si pads – Ultra-low power : ( « 25µW/ch) – 108 channels Ultra-low – Compactness • POWER W layer « Tracker electronics with calorimetric is the performance » KEY issue • No chip => no detector !! ILC : 25µW/ch 25 sept 2009 FLC_PHY 3 18 ch 10*10 mm 5 m. W/ch ATLAS LAr FEB 128 ch 400*500 mm 1 W/ch C. de La Taille - HDR 29

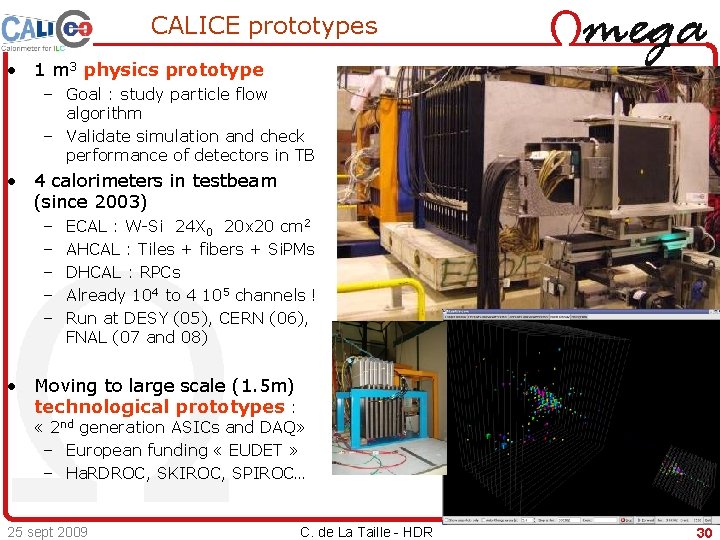

CALICE prototypes • 1 m 3 physics prototype – Goal : study particle flow algorithm – Validate simulation and check performance of detectors in TB • 4 calorimeters in testbeam (since 2003) – – – ECAL : W-Si 24 X 0 20 x 20 cm 2 AHCAL : Tiles + fibers + Si. PMs DHCAL : RPCs Already 104 to 4 105 channels ! Run at DESY (05), CERN (06), FNAL (07 and 08) • Moving to large scale (1. 5 m) technological prototypes : « 2 nd generation ASICs and DAQ» – European funding « EUDET » – Ha. RDROC, SKIROC, SPIROC… 25 sept 2009 C. de La Taille - HDR 30

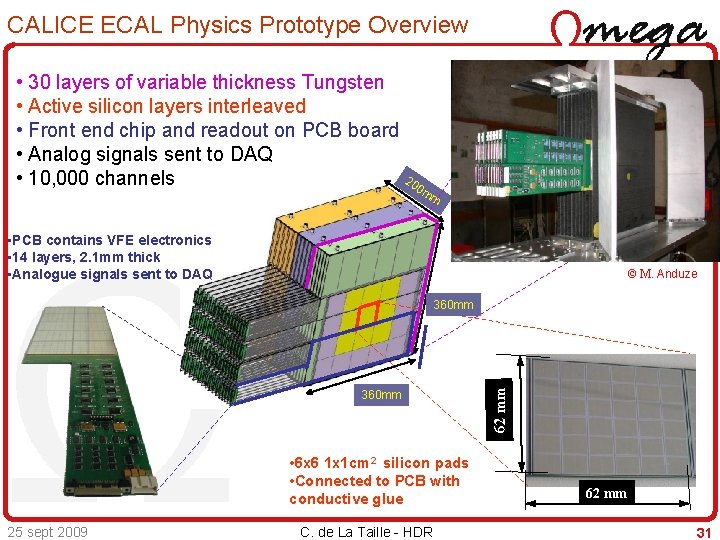

CALICE ECAL Physics Prototype Overview • 30 layers of variable thickness Tungsten • Active silicon layers interleaved • Front end chip and readout on PCB board • Analog signals sent to DAQ 20 • 10, 000 channels 0 m m • PCB contains VFE electronics • 14 layers, 2. 1 mm thick • Analogue signals sent to DAQ © M. Anduze 360 mm • 6 x 6 1 x 1 cm 2 silicon pads • Connected to PCB with conductive glue 25 sept 2009 C. de La Taille - HDR 62 mm 360 mm 62 mm 31

FLCPHY 3 front-end ASIC • Low noise charge preamp – – 1 channel optimized for Cd=70 p. F. Noise en=1. 6 n. V/ ENC = 1000 e- + 40 e-/p. F Variable gain (Cf = 0. 2 -> 3 p. F) OPA G 10 OPA G 1 • Dual gain shaper (G 1 -G 10) – Shaping time tp = 200 ns – dynamic range : 500 MIPs (G 1, Cf=1. 6 – Noise : 0. 1 MIP (G 1) • 2000 chips produced in 2003 Synoptic of 1 channel of FLCPHY 3 Output waveforms for various PA gain Measured gain vs set gain 25 sept 2009 Amp C. de La Taille - HDR 32

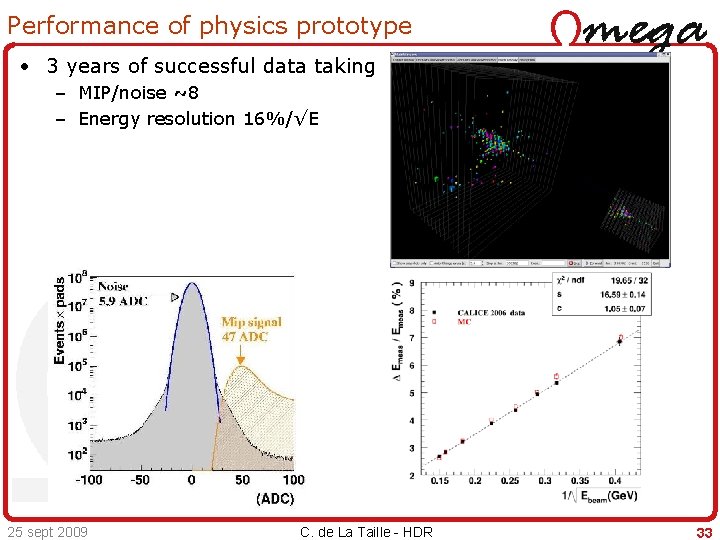

Performance of physics prototype • 3 years of successful data taking – MIP/noise ~8 – Energy resolution 16%/√E 25 sept 2009 C. de La Taille - HDR 33

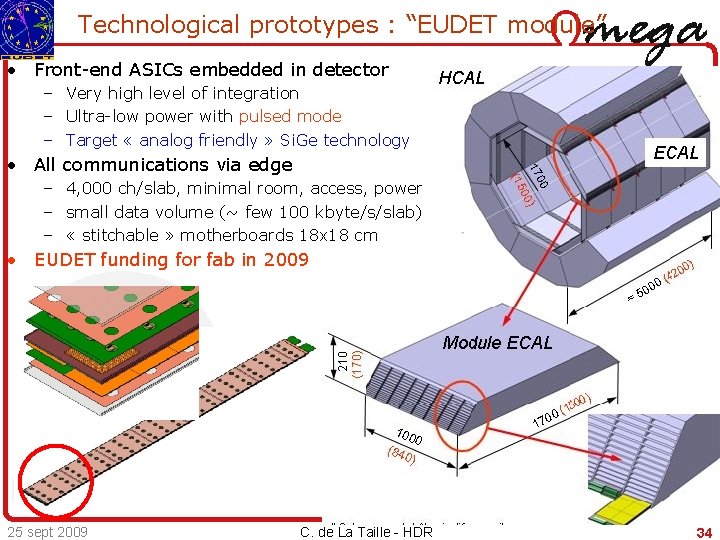

Technological prototypes : “EUDET module” • Front-end ASICs embedded in detector – Very high level of integration – Ultra-low power with pulsed mode – Target « analog friendly » Si. Ge technology • All communications via edge – 4, 000 ch/slab, minimal room, access, power – small data volume (~ few 100 kbyte/s/slab) – « stitchable » motherboards 18 x 18 cm • EUDET funding for fab in 2009 25 sept 2009 C. de La Taille - HDR 34

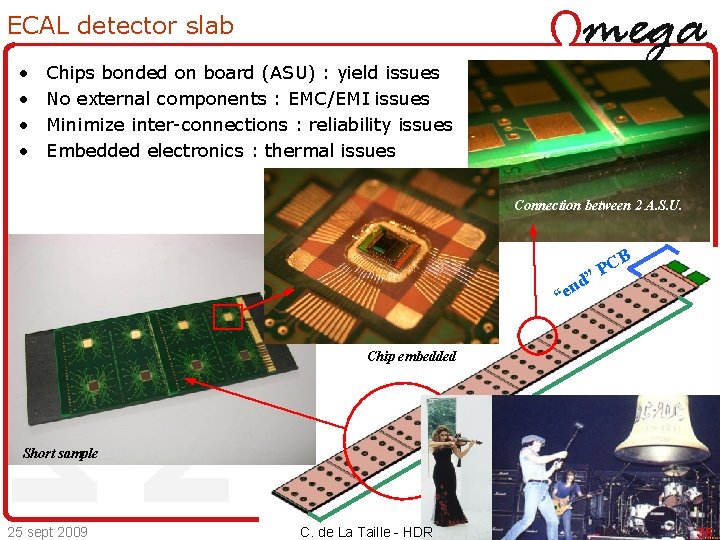

ECAL detector slab • • Chips bonded on board (ASU) : yield issues No external components : EMC/EMI issues Minimize inter-connections : reliability issues Embedded electronics : thermal issues Connection between 2 A. S. U. d” n “e B C P Chip embedded 7 . U S. A . Short sample 25 sept 2009 C. de La Taille - HDR 35

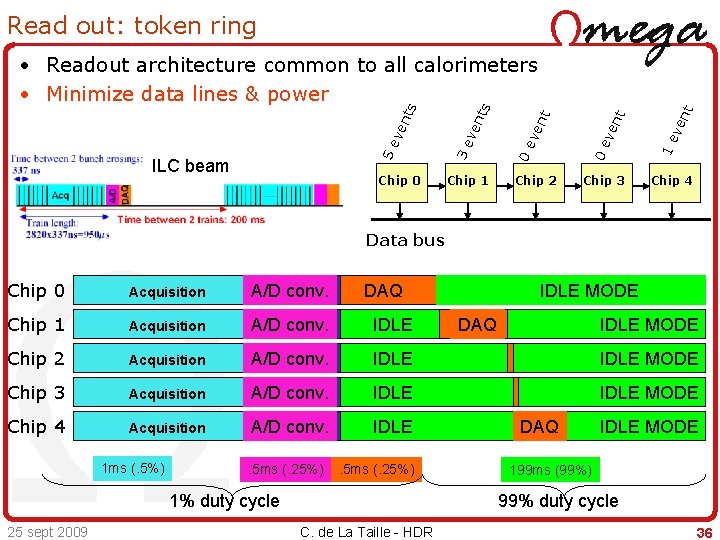

Read out: token ring Chip 0 Chip 2 Chip 3 ve nt 1 e nt 0 e ve nt ve ve nts Chip 1 0 e ILC beam 3 e 5 e ve nts • Readout architecture common to all calorimeters • Minimize data lines & power Chip 4 Data bus Chip 0 Acquisition A/D conv. Chip 1 Acquisition A/D conv. IDLE Chip 2 Acquisition A/D conv. IDLE MODE Chip 3 Acquisition A/D conv. IDLE MODE Chip 4 Acquisition A/D conv. IDLE 1 ms (. 5%) . 5 ms (. 25%) DAQ . 5 ms (. 25%) 1% duty cycle 25 sept 2009 IDLE MODE DAQ IDLE MODE 199 ms (99%) 99% duty cycle C. de La Taille - HDR 36

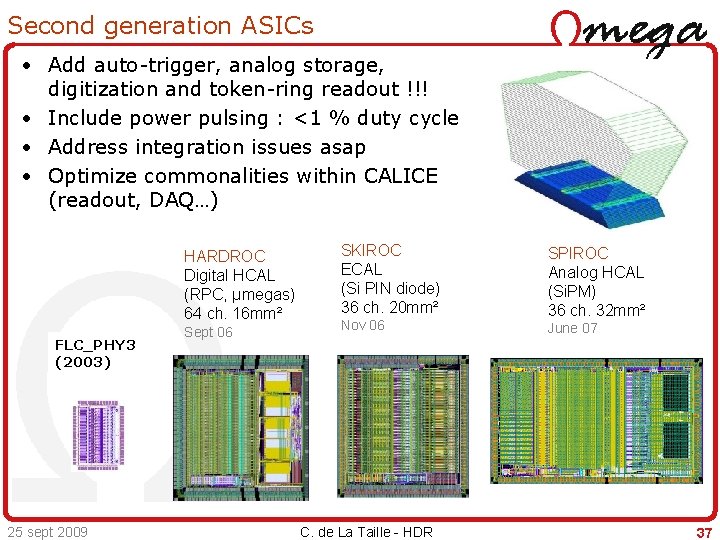

Second generation ASICs • Add auto-trigger, analog storage, digitization and token-ring readout !!! • Include power pulsing : <1 % duty cycle • Address integration issues asap • Optimize commonalities within CALICE (readout, DAQ…) HARDROC Digital HCAL (RPC, µmegas) 64 ch. 16 mm² FLC_PHY 3 (2003) 25 sept 2009 Sept 06 SKIROC ECAL (Si PIN diode) 36 ch. 20 mm² Nov 06 C. de La Taille - HDR SPIROC Analog HCAL (Si. PM) 36 ch. 32 mm² June 07 37

HARDROC: HAdronic Rpc Digital Read. Out Chip • Variable gain (6 bits) current preamps (50Ω input) • Auto-trigger on ½ MIP • Store all channels and BCID for every hit. Depth = 128 bits • Data format : 128(depth)*[2 bit*64 ch+24 bit(BCID)+ 8 bit(Header)] = 20 kbits • Power dissipation : 1. 5 m. W/ch (unpulsed)-> 7 µW with 0. 5% cycle • Large flexibility : >500 slow control • settings Si. Ge 0. 35µm sept 06 and june 08 25 sept 2009 C. de La Taille - HDR 38

Ha. RDROC preamplifier • Current conveyor – « Super common base » configuration – low input impedance, small « equivalent inductance » (<20 n. H) – Zin = 1/gm 1 gm 2 Rc = 50 -100Ω – good performance of Si. Ge • Variable output mirrors : 8 bits – Gain accuracy : 1% 25 sept 2009 C. de La Taille - HDR 39

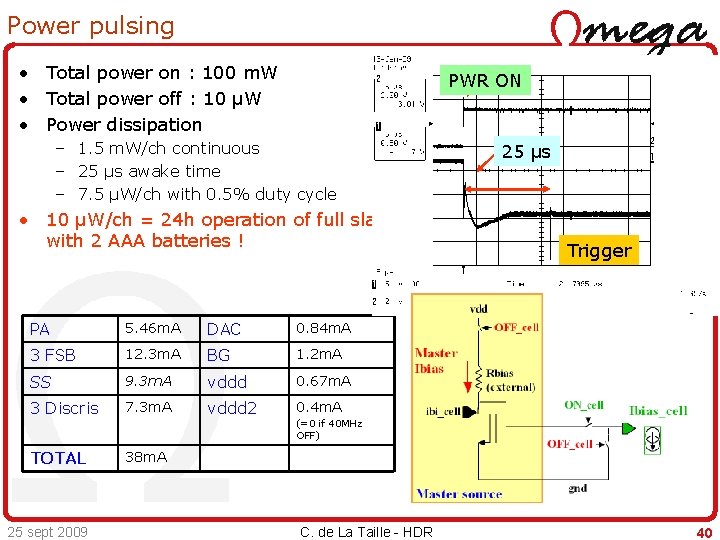

Power pulsing • Total power on : 100 m. W • Total power off : 10 µW • Power dissipation PWR ON – 1. 5 m. W/ch continuous – 25 µs awake time – 7. 5 µW/ch with 0. 5% duty cycle • 10 µW/ch = 24 h operation of full slab with 2 AAA batteries ! PA 5. 46 m. A DAC 0. 84 m. A 3 FSB 12. 3 m. A BG 1. 2 m. A SS 9. 3 m. A vddd 0. 67 m. A 3 Discris 7. 3 m. A vddd 2 0. 4 m. A TOTAL 38 m. A 25 sept 2009 25 µs Trigger (=0 if 40 MHz OFF) C. de La Taille - HDR 40

Analog and Digital crosstalk • Analog Crosstalk ~1% – Well differentiated, capacitive like – Dominated by the input – No long distance crosstalk • Digital crosstalk : 3 f. C – Coupling of discriminator to inputs through ground or substrate – Trigger on CH 1 and look at analog signal on CH 2 NO decoupling cap. 25 sept 2009 C. de La Taille - HDR 41

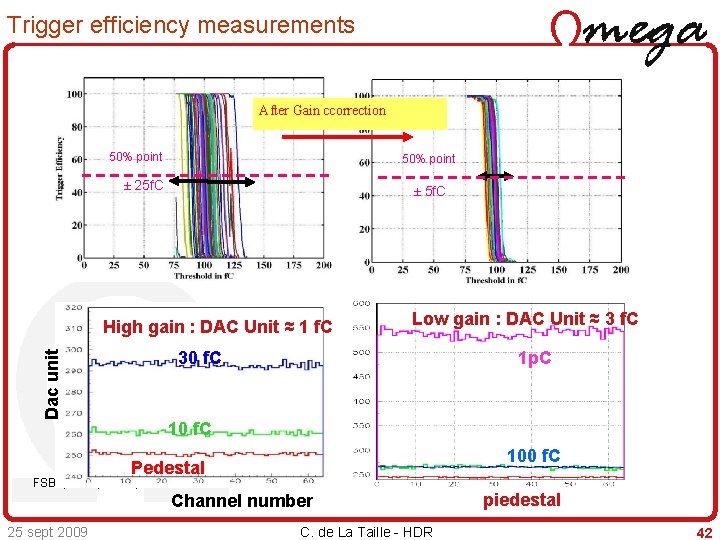

Trigger efficiency measurements After Gain ccorrection 50% point ± 25 f. C ± 5 f. C Dac unit High gain : DAC Unit ≈ 1 f. C Low gain : DAC Unit ≈ 3 f. C 1 p. C 30 f. C 100 f. C Pedestal FSB 0, 100 K, 100 f. F, G=144 Channel number 25 sept 2009 C. de La Taille - HDR piedestal 42

HARDROC 1: digital part 25 sept 2009 C. de La Taille - HDR 43

TESTBEAM (CERN, 2008): 1 st GRPC 2 d GRPC 3 d GRPC Hit pads 4 th GRPC 5 th. GRP C @I. Laktineh-IPNL 44 25 sept 2009 C. de La Taille - HDR 44

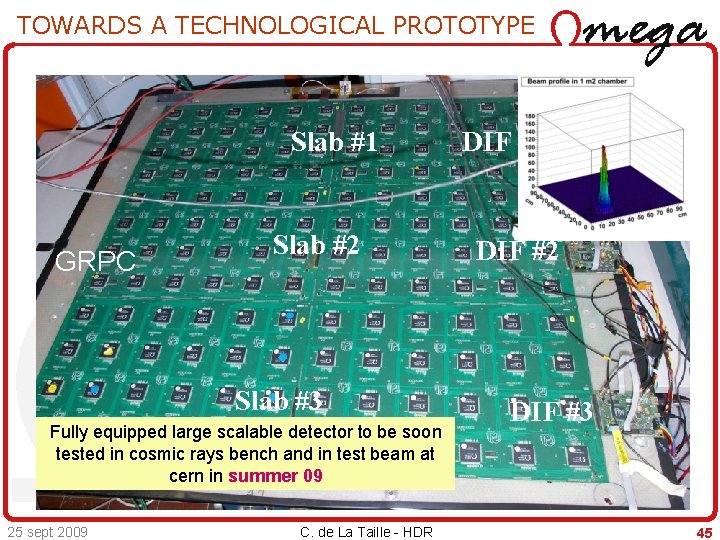

TOWARDS A TECHNOLOGICAL PROTOTYPE Slab #1 GRPC Slab #2 Slab #3 Fully equipped large scalable detector to be soon tested in cosmic rays bench and in test beam at cern in summer 09 25 sept 2009 C. de La Taille - HDR DIF #1 DIF #2 DIF #3 45

AHCAL: Technological prototype • Si. PM detector: 40 layers of 1. 5 m 2 2 cm thick steel plates interleaved with cassettes of 296 scintillating tiles (3 x 3 cm 2) readout by Si. PMs • FE Chip embedded inside the detector – Thickness: critical issue: Mother boards (HBU) are sandwiched between 2 absorber plates Mephy Si. PM 25 sept 2009 C. de La Taille - HDR 46

SPIROC: Silicon Photomultiplier Integrated Read Out Chip • A-HCAL read out – – – Silicon PM detector G=105 -106 36 channels Charge measurement (15 bits) Time measurement (< 1 ns) many SKIROC, HARDROC, and MAROC features re-used – Submitted in June 07 in Si. Ge 0. 35 µm AMS SPIROC • Collaboration with DESY – Physics prototype: 9000 channels used in test beam in 2004 -2008 – Production in 2009 for Eudet module (technological prototype) 25 sept 2009 FLC_Si. PM C. de La Taille - HDR 47

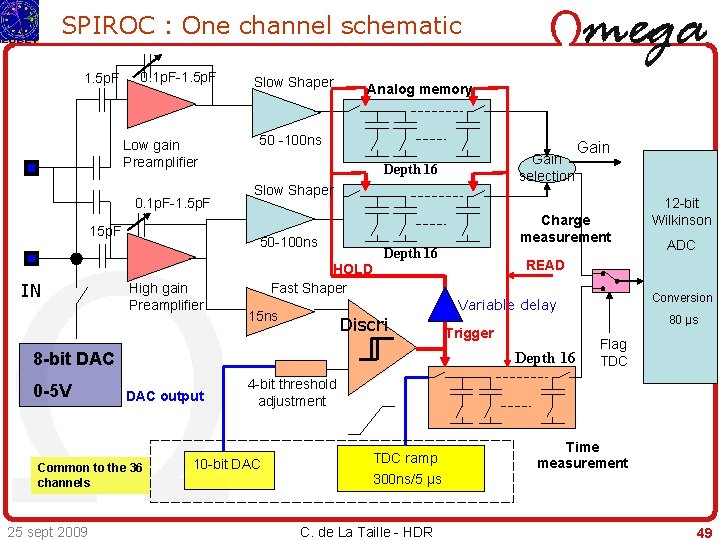

SPIROC main features • Internal input 8 -bit DAC (0 -5 V) for individual Si. PM gain adjustment • Energy measurement : 14 bits – 2 gains (1 -10) + 12 bit ADC: 1 pe 2000 pe – Variable shaping time from 50 ns to 100 ns – pe/noise ratio : 11 • Auto-trigger on 1/3 pe (50 f. C) – pe/noise ratio on trigger channel : 24 – Fast shaper : ~10 ns – Auto-Trigger on ½ pe • Time measurement : – 12 -bit Bunch Crossing ID – 12 bit TDC step~100 ps • • Analog memory for time and charge measurement : depth = 16 Low consumption : ~25 µW per channel (in power pulsing mode) Individually addressable calibration injection capacitance Embedded bandgap for voltage references Embedded 10 bit DAC for trigger threshold and gain selection Multiplexed analog output for physics prototype DAQ 4 k internal memory and Daisy chain readout 25 sept 2009 C. de La Taille - HDR 48

SPIROC : One channel schematic 1. 5 p. F 0. 1 p. F-1. 5 p. F Low gain Preamplifier 0. 1 p. F-1. 5 p. F 15 p. F IN Slow Shaper Analog memory 50 -100 ns Depth 16 Slow Shaper Depth 16 Discri Trigger Depth 16 DAC output Common to the 36 channels 25 sept 2009 ADC Conversion Variable delay 8 -bit DAC 0 -5 V 12 -bit Wilkinson READ HOLD Fast Shaper 15 ns Gain Charge measurement 50 -100 ns High gain Preamplifier Gain selection 80 µs Flag TDC 4 -bit threshold adjustment 10 -bit DAC TDC ramp 300 ns/5 µs C. de La Taille - HDR Time measurement 49

Valid. Hold. Analogb 16 Raz. Rang. N 16 Chipsat 16 Read. Mesureb Acquisition Ext. Sigma. TM (OR 36) gain Wilkinson ADC Discri output Channel 0 TM (Discri trigger) 36 36 Val. Gain (low gain or high Gain) BCID 16 x 8 bits Conversion ADC End. Ramp (Discri ADC Wilkinson) Trigger discri Output Flag. TDC Channel 1 TDC ramp readout Transmit. On Ram. Full Out. Serie End. Read. Out Ecriture RAM Start. Read. Out Rstb Clk 40 MHz . . … … Start. Conv. DAQb + 36 Wilkinson ADC Discri output Start. Acqt Slow. Clock Hit channel register 16 x 36 x 1 bits Trigger discri Output gain No. Trig ADC ramp Startrampb (wilkinson ramp) OR 36 Start. Ramp. TDC Chip ID register 8 bits RAM Chip. ID 8 Val. Dim. Gray ASIC 25 sept 2009 Val. Dim. Gray 12 bits 12 C. de La Taille - HDR DAQ 50

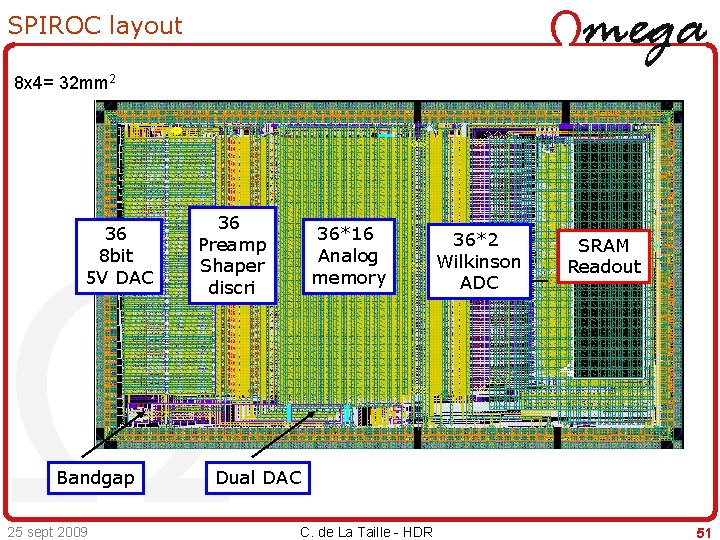

SPIROC layout 8 x 4= 32 mm 2 36 8 bit 5 V DAC Bandgap 25 sept 2009 36 Preamp Shaper discri 36*16 Analog memory 36*2 Wilkinson ADC SRAM Readout Dual DAC C. de La Taille - HDR 51

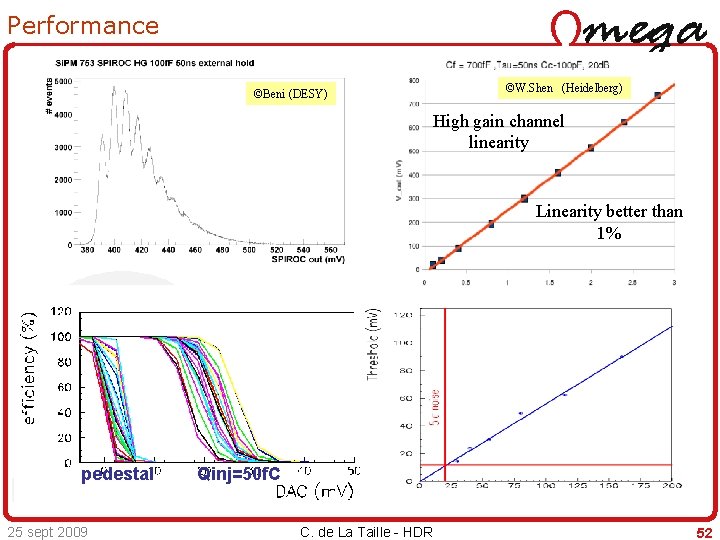

Performance ©W. Shen (Heidelberg) ©Beni (DESY) High gain channel linearity Linearity better than 1% pedestal 25 sept 2009 Qinj=50 f. C C. de La Taille - HDR 52

Internal 12 -bit ADC performance Chip 1 25 sept 2009 C. de La Taille - HDR 53

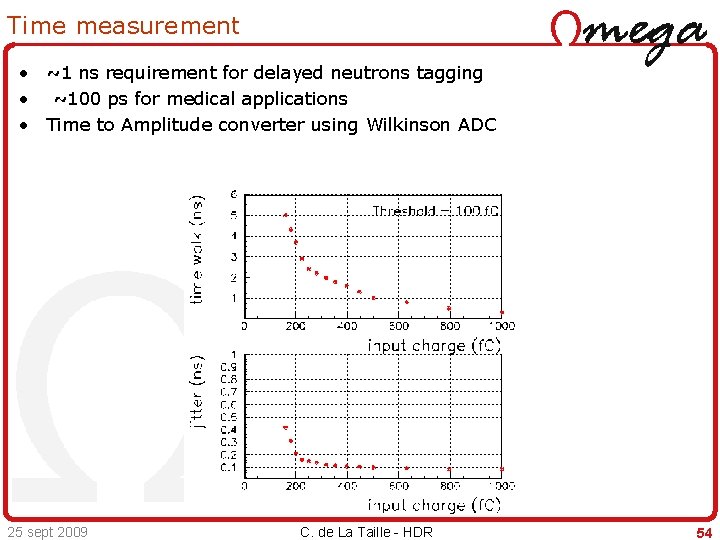

Time measurement • ~1 ns requirement for delayed neutrons tagging • ~100 ps for medical applications • Time to Amplitude converter using Wilkinson ADC 25 sept 2009 C. de La Taille - HDR 54

![Multi-Anode PM readout : OPERA_ROC [NIM] • OPERA_ROC : 32 ch ASIC – Variable Multi-Anode PM readout : OPERA_ROC [NIM] • OPERA_ROC : 32 ch ASIC – Variable](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-55.jpg)

Multi-Anode PM readout : OPERA_ROC [NIM] • OPERA_ROC : 32 ch ASIC – Variable gain preamp – Autotrigger on 1/3 photoelecton – Multiplexed charge readout – Bi. CMOS 0. 8µm 3000 chips produced (2002) 64 ch front-end board (BERN) 25 sept 2009 C. de La Taille - HDR 55

![MAROC : Multi. Anode Read-Out Chip [NIM] • Complete front-end chip for 64 channels MAROC : Multi. Anode Read-Out Chip [NIM] • Complete front-end chip for 64 channels](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-56.jpg)

MAROC : Multi. Anode Read-Out Chip [NIM] • Complete front-end chip for 64 channels multi-anode photomultipliers – – 6 bit-individual gain correction Auto-trigger on 1/3 p. e. at 10 MHz 12 bit charge output Si. Ge 0. 35 µm, 12 mm 2, Pd = 5 m. W/ch • Bonded on a compact PCB (PMF) for ATLAS luminometer (ALFA) • Also equips Double-Chooz, medical imaging… Hold signal 64 inputs Photons PM 64 channels Gain correction 64*6 bits 3 discris thresholds (3*12 bits) 25 sept 2009 Variable Gain Preamp. Variable S&H Slow Shaper S&H 64 20 -100 ns Bipolar Wilkinson Fast Shaper 12 bit ADC Unipolar 80 MHz encoder PMF Fast Shaper 3 DACs 12 bits Multiplexed Analog charge output Multiplexed Digital charge output 64 trigger outputs (to FPGA) LUCI D C. de La Taille - HDR 56

![PARi. SROC for PMm 2 [Ph. D S. Conforti] • “PMm 2” (2006 – PARi. SROC for PMm 2 [Ph. D S. Conforti] • “PMm 2” (2006 –](http://slidetodoc.com/presentation_image/055a624f9b20541fb5864f603b470254/image-57.jpg)

PARi. SROC for PMm 2 [Ph. D S. Conforti] • “PMm 2” (2006 – 2009), funded by the ANR : LAL, IPNO, LAPP, Photonis Joël Pouthas. IPN Orsay – Replace large PMTs (20”) by groups of smaller ones (12”) – central 16 ch ASIC (Pa. RISROC) – – 12 bit charge + 12 bit time water-tight, common High Voltage Only one wire out (DATA + VCC) Target low cost • Application : large water Cerenkov neutrino • External requests : – Neutrino (DUSEL, LENA) 25 sept 2009 C. de La Taille - HDR 57

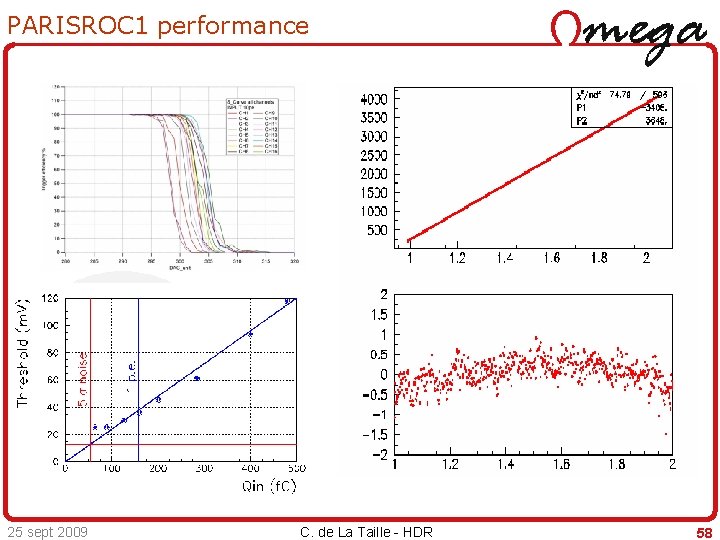

PARISROC 1 performance 25 sept 2009 C. de La Taille - HDR 58

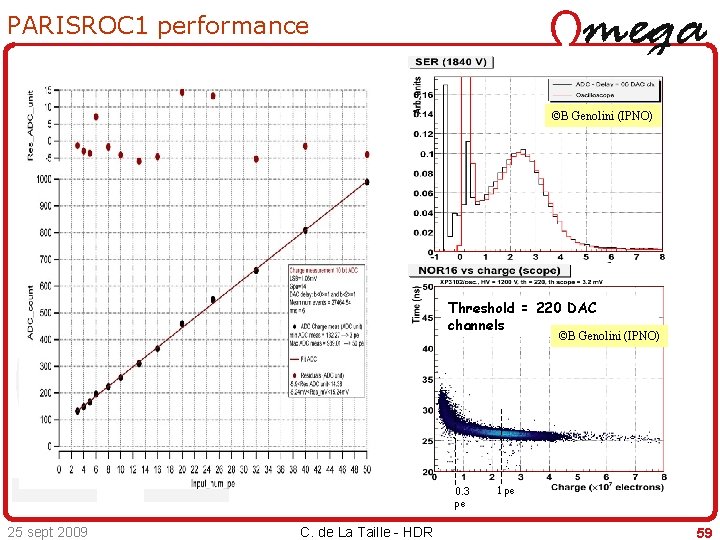

PARISROC 1 performance ©B Genolini (IPNO) Threshold = 220 DAC channels ©B Genolini (IPNO) 0. 3 pe 25 sept 2009 C. de La Taille - HDR 1 pe 59

Conclusion • Importance of close interaction between physics and front-end • High level integration thanks to micro-electronics technology • Large synergy between chips : efficiency of micro-electronics poles « acta est fabula » 25 sept 2009 C. de La Taille - HDR 60

Conclusion (2) • Thanks to all the OMEGA team ! 25 sept 2009 C. de La Taille - HDR 61

Semiconductor Industry Roadmap 25 sept 2009 C. de La Taille - HDR 62

Spare slides 25 sept 2009 C. de La Taille - HDR 63

backup slides 25 sept 2009 C. de La Taille - HDR 64

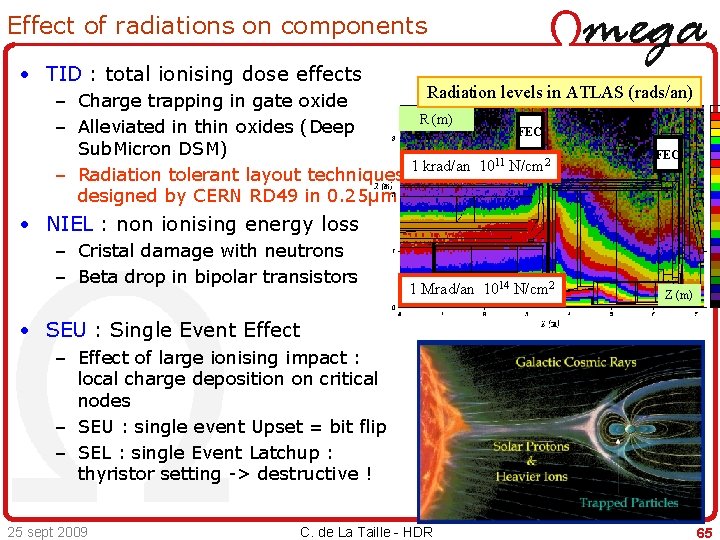

Effect of radiations on components • TID : total ionising dose effects Radiation levels in ATLAS (rads/an) – Charge trapping in gate oxide R (m) – Alleviated in thin oxides (Deep FEC Sub. Micron DSM) FEC 1 krad/an 1011 N/cm 2 – Radiation tolerant layout techniques designed by CERN RD 49 in 0. 25µm • NIEL : non ionising energy loss – Cristal damage with neutrons – Beta drop in bipolar transistors 1 Mrad/an 1014 N/cm 2 Z (m) • SEU : Single Event Effect – Effect of large ionising impact : local charge deposition on critical nodes – SEU : single event Upset = bit flip – SEL : single Event Latchup : thyristor setting -> destructive ! 25 sept 2009 C. de La Taille - HDR 65

25 sept 2009 C. de La Taille - HDR 66

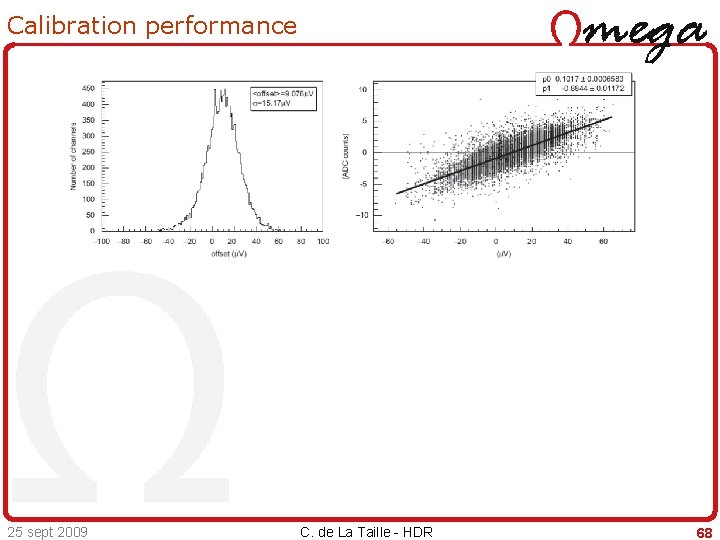

DC performance DC linearity < 0. 01% 25 sept 2009 DC uniformity 128 ch 0. 06% C. de La Taille - HDR 67

Calibration performance 25 sept 2009 C. de La Taille - HDR 68

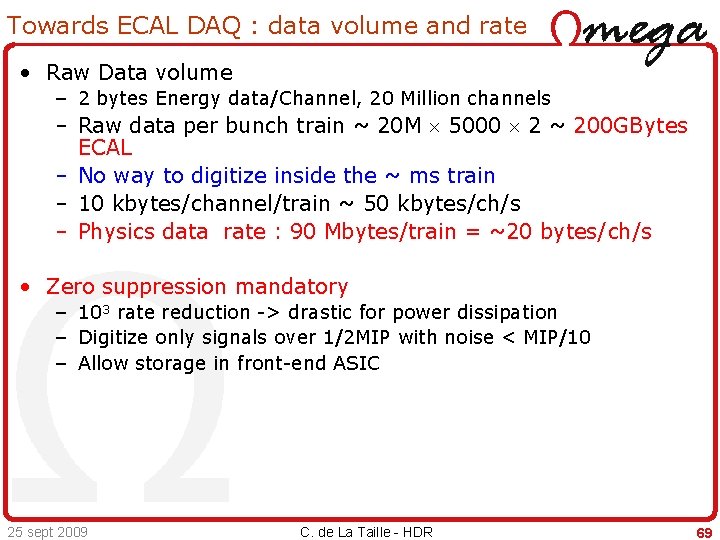

Towards ECAL DAQ : data volume and rate • Raw Data volume – 2 bytes Energy data/Channel, 20 Million channels – Raw data per bunch train ~ 20 M 5000 2 ~ 200 GBytes ECAL – No way to digitize inside the ~ ms train – 10 kbytes/channel/train ~ 50 kbytes/ch/s – Physics data rate : 90 Mbytes/train = ~20 bytes/ch/s • Zero suppression mandatory – 103 rate reduction -> drastic for power dissipation – Digitize only signals over 1/2 MIP with noise < MIP/10 – Allow storage in front-end ASIC 25 sept 2009 C. de La Taille - HDR 69

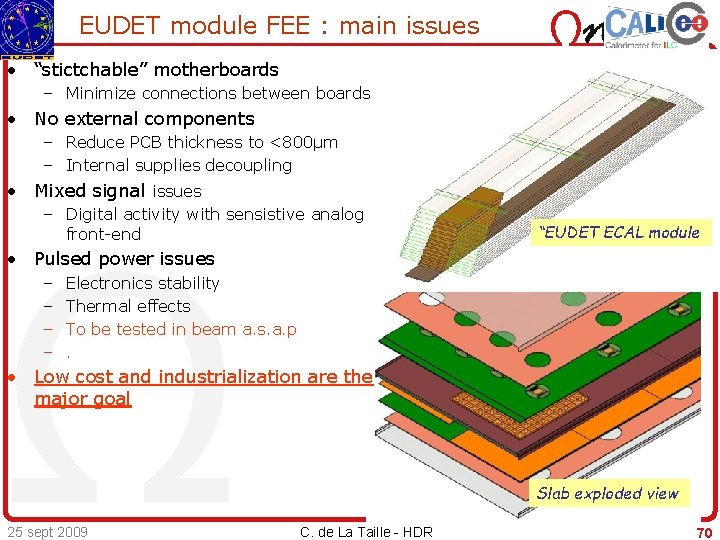

EUDET module FEE : main issues • “stictchable” motherboards – Minimize connections between boards • No external components – Reduce PCB thickness to <800µm – Internal supplies decoupling • Mixed signal issues – Digital activity with sensistive analog front-end “EUDET ECAL module • Pulsed power issues – – Electronics stability Thermal effects To be tested in beam a. s. a. p. • Low cost and industrialization are the major goal Slab exploded view 25 sept 2009 C. de La Taille - HDR 70

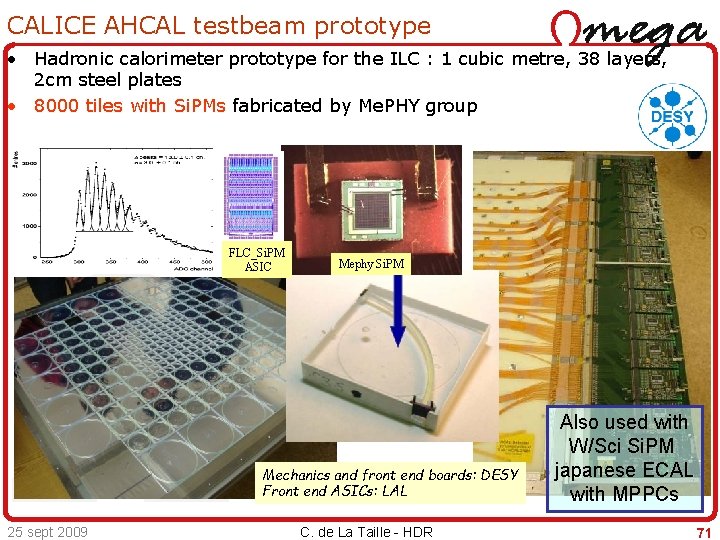

CALICE AHCAL testbeam prototype • Hadronic calorimeter prototype for the ILC : 1 cubic metre, 38 layers, 2 cm steel plates • 8000 tiles with Si. PMs fabricated by Me. PHY group FLC_Si. PM ASIC Mephy Si. PM Mechanics and front end boards: DESY Front end ASICs: LAL 25 sept 2009 C. de La Taille - HDR Also used with W/Sci Si. PM japanese ECAL with MPPCs 71

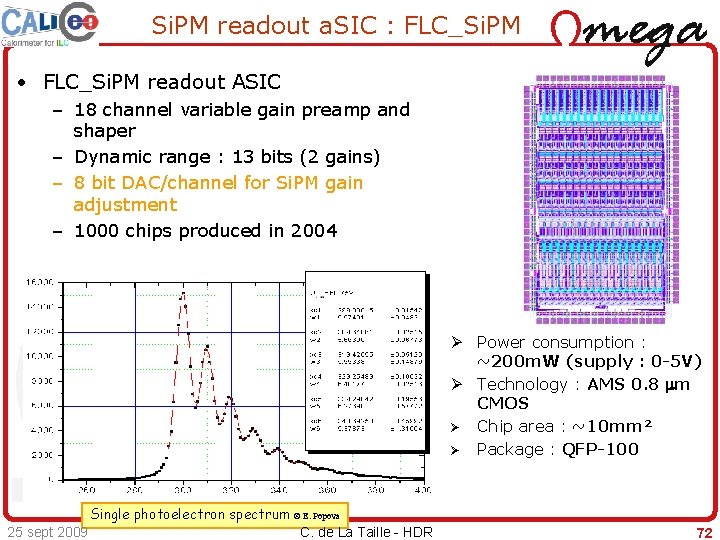

Si. PM readout a. SIC : FLC_Si. PM • FLC_Si. PM readout ASIC – 18 channel variable gain preamp and shaper – Dynamic range : 13 bits (2 gains) – 8 bit DAC/channel for Si. PM gain adjustment – 1000 chips produced in 2004 Ø Power consumption : ~200 m. W (supply : 0 -5 V) Ø Technology : AMS 0. 8 m CMOS Ø Chip area : ~10 mm² Ø Package : QFP-100 Single photoelectron spectrum 25 sept 2009 © E. Popova C. de La Taille - HDR 72

Input DAC • • 8 bit, 5 V range LSB=20 m. V 36 DACs : one per channel Ultra low power (1µW) : no power pulsing • Can sink 10 µA leakage current • Linearity : ± 2% +HV 8 -bit DAC Si PM High voltage on the cable shielding 25 sept 2009 ASIC C. de La Taille - HDR 73

- Slides: 73