GSEIS LME Processador MIPS Arquitetura e Assembly Wang

GSEIS - LME Processador MIPS Arquitetura e Assembly* Wang Jiang Chau Grupo de Projeto de Sistemas Eletrônicos e Software Aplicado Laboratório de Microeletrônica – LME Depto. Sistemas Eletrônicos- EPUSP Escola Politécnica da Universidade de São Paulo * Baseado no livro de Robert Britton

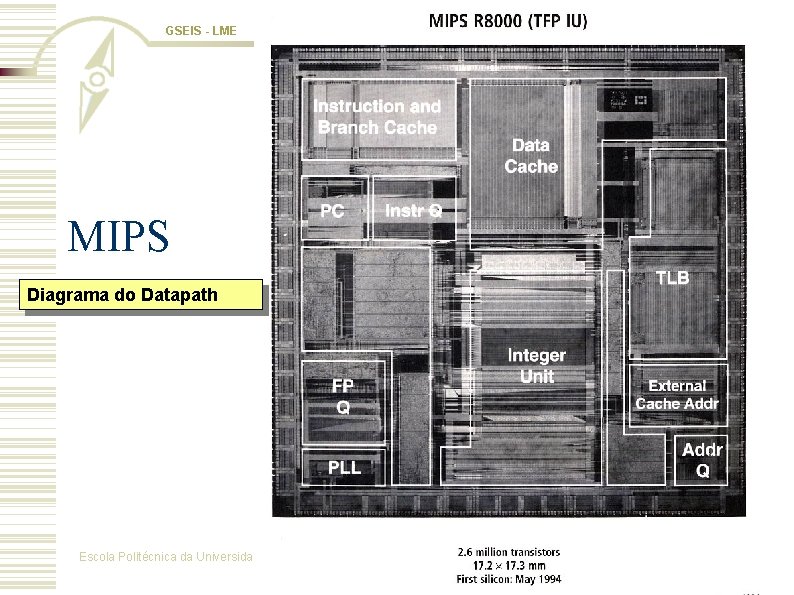

GSEIS - LME MIPS Diagrama do Datapath Escola Politécnica da Universidade de São Paulo

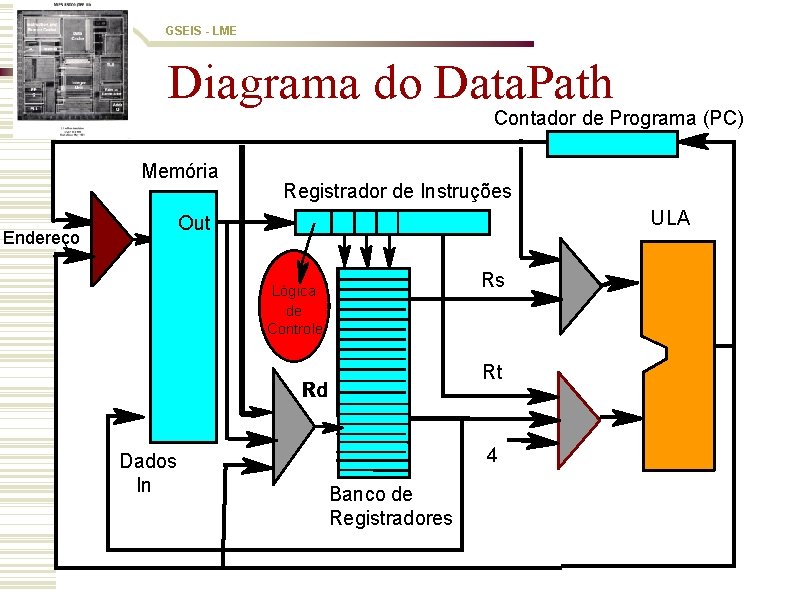

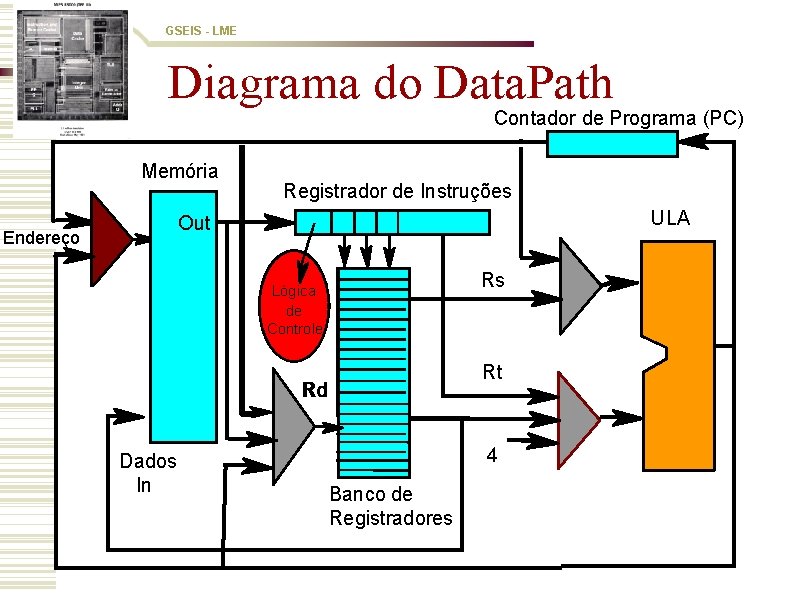

GSEIS - LME Diagrama do Data. Path Program de Counter (PC) Contador Programa Cache Memory Memória Out Endereço Address Instruction Register Registrador de Instruções ALU ULA Rs Rs Control Lógica Logic de Controle Rd Data In Dados In Rt Rt 44 Register Banco de. File Registradores Escola Politécnica da Universidade de São Paulo

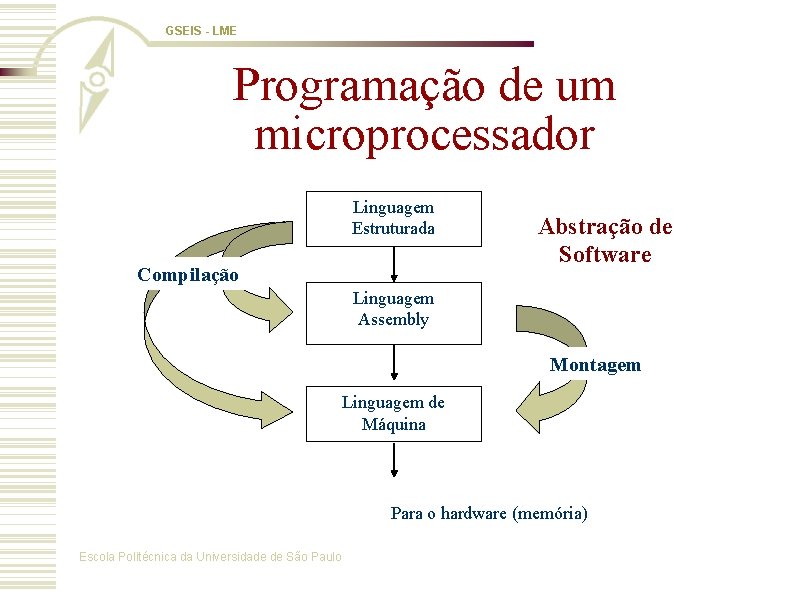

GSEIS - LME Programação de um microprocessador Linguagem Estruturada Compilação Abstração de Software Linguagem Assembly Montagem Linguagem de Máquina Para o hardware (memória) Escola Politécnica da Universidade de São Paulo

GSEIS - LME No nosso caso …. Pseudo-código Linguagem Assembly Montagem Linguagem de Máquina Escola Politécnica da Universidade de São Paulo

GSEIS - LME Arquitetura do MIPS Registradores disponíveis para o programador Conjunto de instruções Modos de endereçamento Tipos de dados Escola Politécnica da Universidade de São Paulo

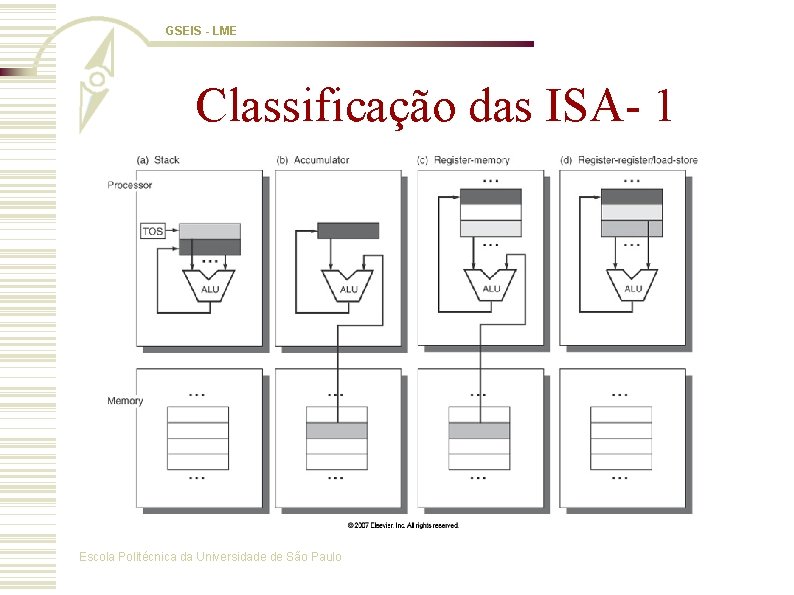

GSEIS - LME Classificação das ISA- 1 Escola Politécnica da Universidade de São Paulo

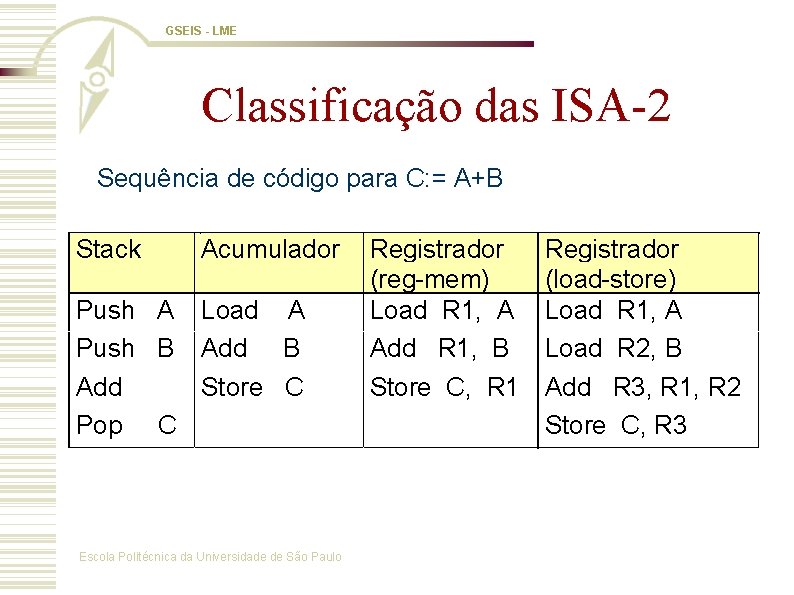

GSEIS - LME Classificação das ISA-2 Sequência de código para C: = A+B Stack Acumulador Push A Load A Push B Add Store C Pop C Registrador (reg-mem) Load R 1, A Add R 1, B Store C, R 1 Escola Politécnica da Universidade de São Paulo Registrador (load-store) Load R 1, A Load R 2, B Add R 3, R 1, R 2 Store C, R 3

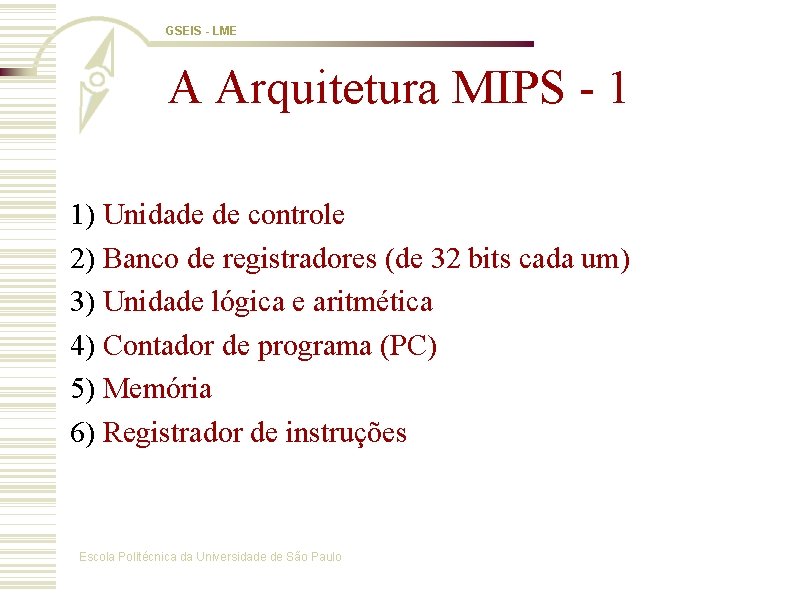

GSEIS - LME A Arquitetura MIPS - 1 1) Unidade de controle 2) Banco de registradores (de 32 bits cada um) 3) Unidade lógica e aritmética 4) Contador de programa (PC) 5) Memória 6) Registrador de instruções Escola Politécnica da Universidade de São Paulo

GSEIS - LME A Arquitetura MIPS - 2 • Incorpora todos os princípios fundamentais de todas as arquiteturas RISC contemporâneas: Memória contém dados e instruções Acesso a memória por instruções load-store Instruções diretamente executadas em hardware Registradores de propósito geral de 32 bits Tipo de Dados: byte, half-word, word e doubleword. Barramentos de 32 bits Escola Politécnica da Universidade de São Paulo

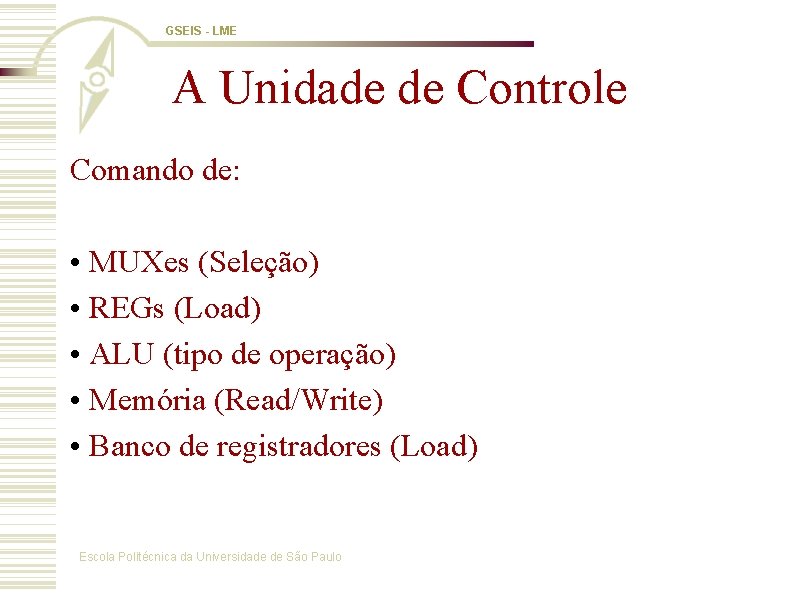

GSEIS - LME A Unidade de Controle Comando de: • MUXes (Seleção) • REGs (Load) • ALU (tipo de operação) • Memória (Read/Write) • Banco de registradores (Load) Escola Politécnica da Universidade de São Paulo

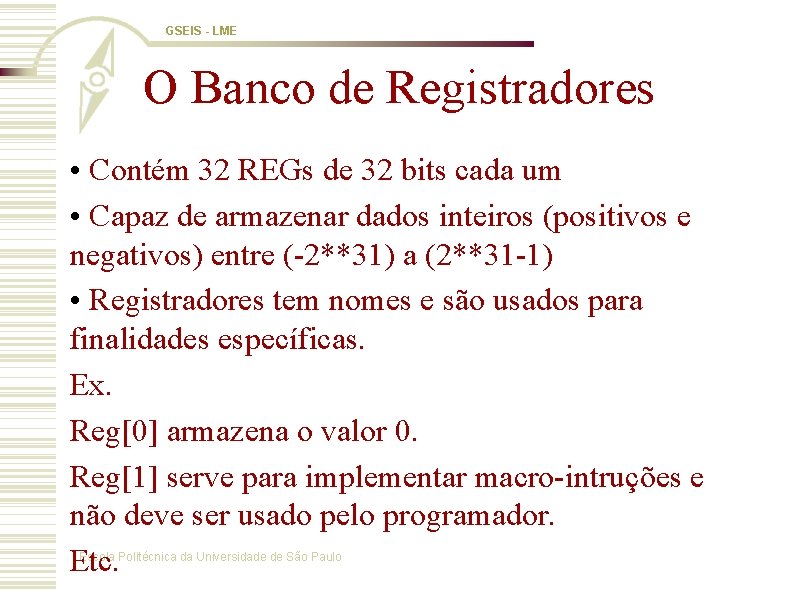

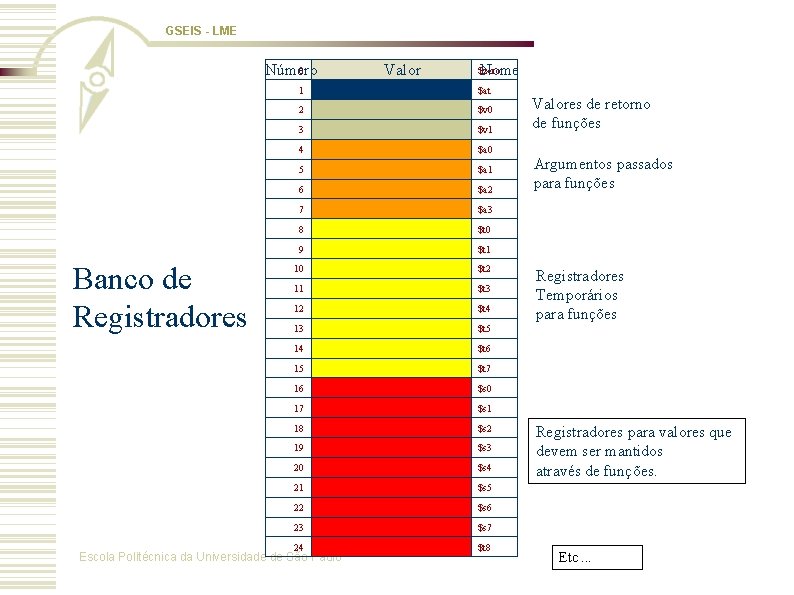

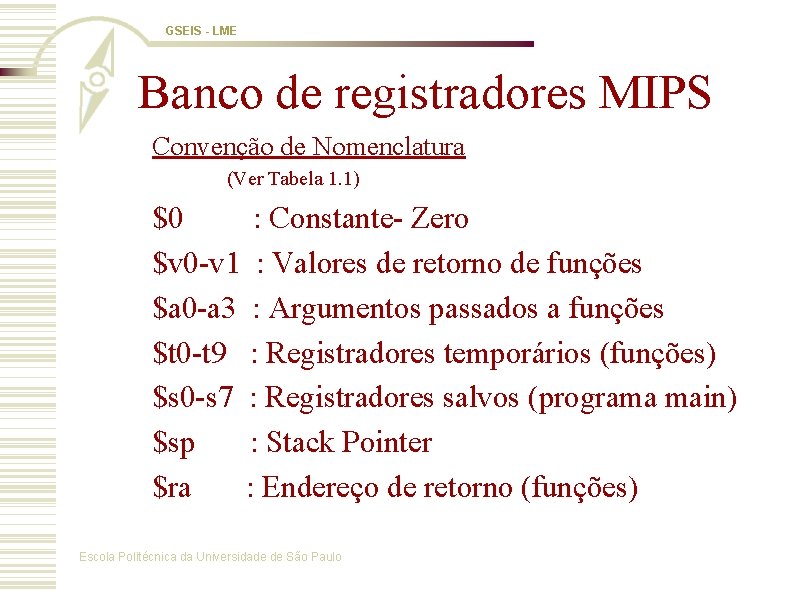

GSEIS - LME O Banco de Registradores • Contém 32 REGs de 32 bits cada um • Capaz de armazenar dados inteiros (positivos e negativos) entre (-2**31) a (2**31 -1) • Registradores tem nomes e são usados para finalidades específicas. Ex. Reg[0] armazena o valor 0. Reg[1] serve para implementar macro-intruções e não deve ser usado pelo programador. Etc. Escola Politécnica da Universidade de São Paulo

GSEIS - LME 0 Número Banco de Registradores Valor Nome $zero 1 $at 2 $v 0 3 $v 1 4 $a 0 5 $a 1 6 $a 2 7 $a 3 8 $t 0 9 $t 1 10 $t 2 11 $t 3 12 $t 4 13 $t 5 14 $t 6 15 $t 7 16 $s 0 17 $s 1 18 $s 2 19 $s 3 20 $s 4 21 $s 5 22 $s 6 23 $s 7 24 $t 8 Escola Politécnica da Universidade de São Paulo Valores de retorno de funções Argumentos passados para funções Registradores Temporários para funções Registradores para valores que devem ser mantidos através de funções. Etc. . .

GSEIS - LME Banco de registradores MIPS Convenção de Nomenclatura (Ver Tabela 1. 1) $0 : Constante- Zero $v 0 -v 1 : Valores de retorno de funções $a 0 -a 3 : Argumentos passados a funções $t 0 -t 9 : Registradores temporários (funções) $s 0 -s 7 : Registradores salvos (programa main) $sp : Stack Pointer $ra : Endereço de retorno (funções) Escola Politécnica da Universidade de São Paulo

GSEIS - LME PC e Memória PC contém o endereço da próxima instrução a ser executada. PC é iniciado pelo OS com o endereço da instrução inicial. Após a busca da instrução, o PC é incrementado (PC+4) ou recebe o valor calculado por alguma operação de desvio. Memória 4 Gbytes x 8 (2**32 bits de endereçamento e cada endereço armazena 8 bits) Escola Politécnica da Universidade de São Paulo

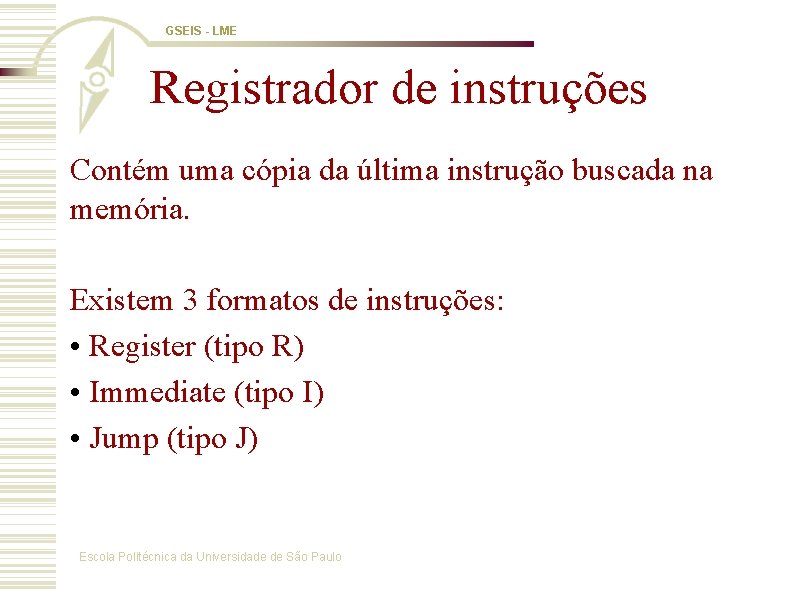

GSEIS - LME Registrador de instruções Contém uma cópia da última instrução buscada na memória. Existem 3 formatos de instruções: • Register (tipo R) • Immediate (tipo I) • Jump (tipo J) Escola Politécnica da Universidade de São Paulo

GSEIS - LME Formato de Instruções Formato Registrador – Tipo R Op-Code Rs Rt Rd 6 5 5 00000 5 Code 6 Formato Imediato – Tipo I Op-Code Rs Rt 16 - Bit Immediate Value 6 5 5 Formato Salto (Jump)- Tipo J 16 Op-Code 26 Bit Current Segment Address 6 Escola Politécnica da Universidade de São Paulo 26

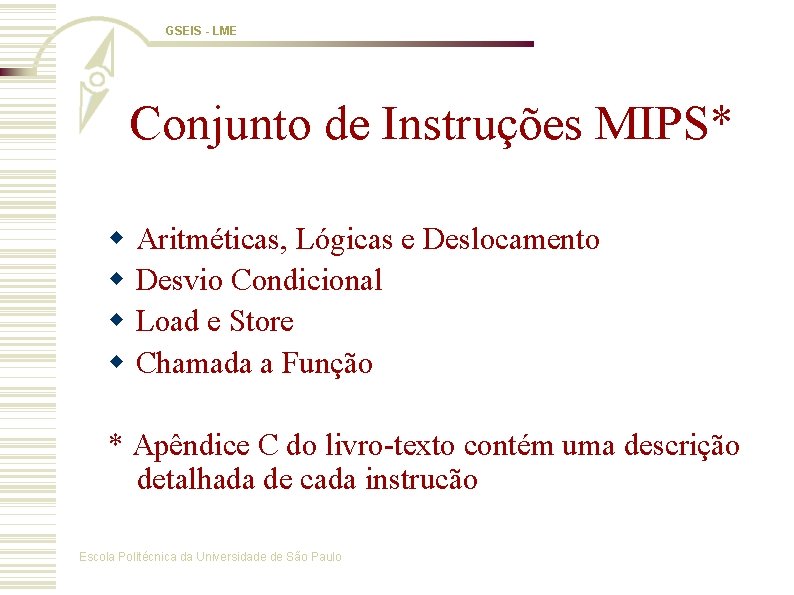

GSEIS - LME Conjunto de Instruções MIPS* Aritméticas, Lógicas e Deslocamento Desvio Condicional Load e Store Chamada a Função * Apêndice C do livro-texto contém uma descrição detalhada de cada instrucão Escola Politécnica da Universidade de São Paulo

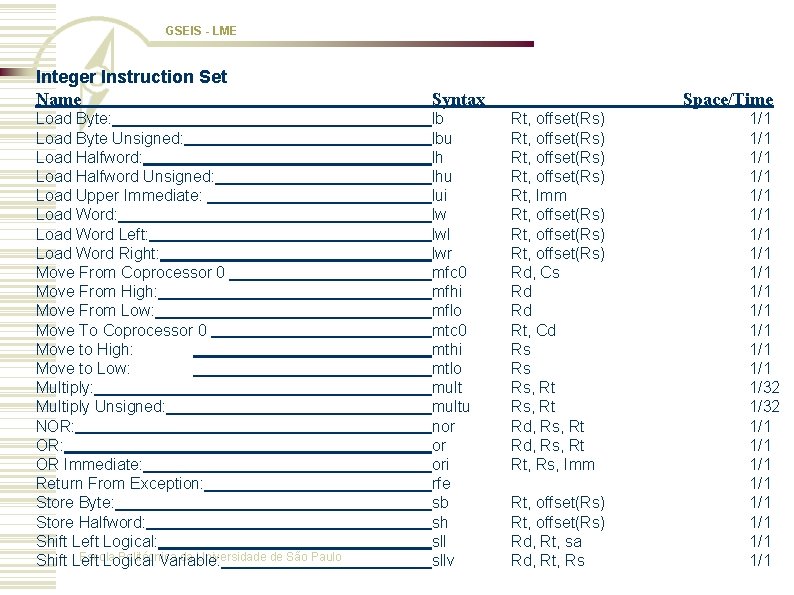

GSEIS - LME Quick Reference – Apêndice A Integer Instruction Set Name Syntax Space/Time Add: add Rd, Rs, Rt 1/1 Add Immediate: addi Rt, Rs, Imm 1/1 Add Immediate Unsigned: addiu Rt, Rs, Imm 1/1 Add Unsigned: addu Rd, Rs, Rt 1/1 And: and Rd, Rs, Rt 1/1 And Immediate: andi Rt, Rs, Imm 1/1 Branch if Equal: beq Rs, Rt, Label 1/1 Branch if Greater Than or Equal to Zero: bgez. Rs, Label Branch if Greater Than or Equal to Zero and Link: bgezal Rs, Label Branch if Greater Than Zero: bgtz Rs, Label 1/1 Branch if Less Than or Equal to Zero: blez Rs, Label Branch if Less Than Zero and Link: bltzal Rs, Label Branch if Less Than Zero: bltz Rs, Label 1/1 Branch if Not Equal: bne Rs, Rt, Label 1/1 Divide: div Rs, Rt 1/38 Divide Unsigned: divu Rs, Rt 1/38 Jump: j Label 1/1 Jump and Link: jal Label 1/1 Jump and Link Register: jalr Rd, Rs 1/1 Jump Register: jr Rs 1/1 Escola Politécnica da Universidade de São Paulo 1/1 1/1

GSEIS - LME Integer Instruction Set Name Syntax Load Byte: Load Byte Unsigned: Load Halfword Unsigned: Load Upper Immediate: Load Word Left: Load Word Right: Move From Coprocessor 0 Move From High: Move From Low: Move To Coprocessor 0 Move to High: Move to Low: Multiply Unsigned: NOR: OR Immediate: Return From Exception: Store Byte: Store Halfword: Shift Left Logical: Escola Politécnica da Universidade de São Paulo Shift Left Logical Variable: lb lbu lh lhu lui lw lwl lwr mfc 0 mfhi mflo mtc 0 mthi mtlo multu nor or ori rfe sb sh sllv Rt, offset(Rs) Rt, Imm Rt, offset(Rs) Rd, Cs Rd Rd Rt, Cd Rs Rs Rs, Rt Rd, Rs, Rt Rt, Rs, Imm Rt, offset(Rs) Rd, Rt, sa Rd, Rt, Rs Space/Time 1/1 1/1 1/1 1/1 1/32 1/1 1/1

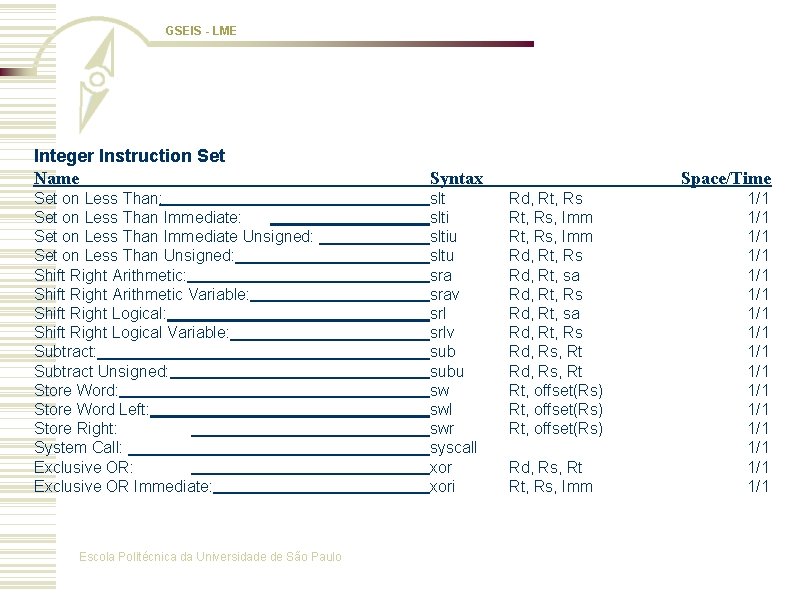

GSEIS - LME Integer Instruction Set Name Syntax Set on Less Than: Set on Less Than Immediate Unsigned: Set on Less Than Unsigned: Shift Right Arithmetic Variable: Shift Right Logical Variable: Subtract Unsigned: Store Word Left: Store Right: System Call: Exclusive OR Immediate: sltiu sltu srav srlv subu sw swl swr syscall xori Escola Politécnica da Universidade de São Paulo Rd, Rt, Rs, Imm Rd, Rt, Rs Rd, Rt, sa Rd, Rt, Rs Rd, Rs, Rt Rt, offset(Rs) Rd, Rs, Rt Rt, Rs, Imm Space/Time 1/1 1/1 1/1 1/1

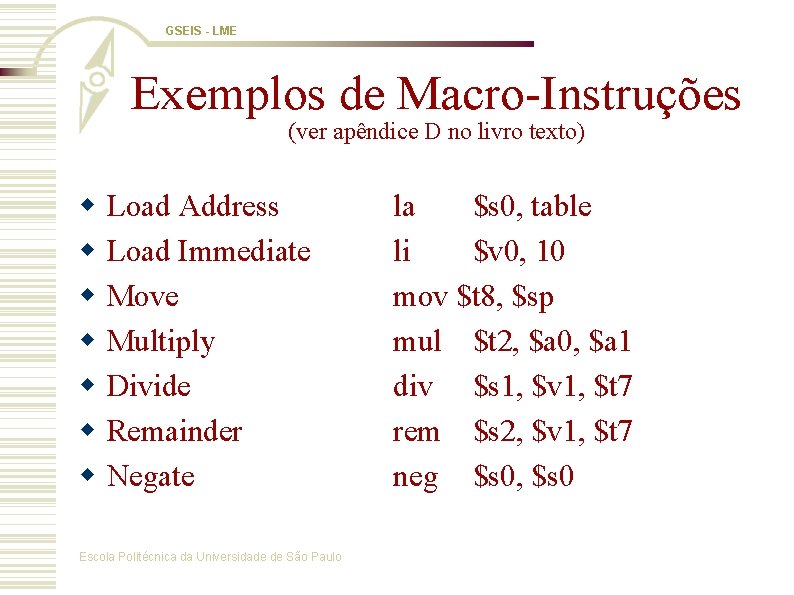

GSEIS - LME Exemplos de Macro-Instruções (ver apêndice D no livro texto) Load Address Load Immediate Move Multiply Divide Remainder Negate Escola Politécnica da Universidade de São Paulo la $s 0, table li $v 0, 10 mov $t 8, $sp mul $t 2, $a 0, $a 1 div $s 1, $v 1, $t 7 rem $s 2, $v 1, $t 7 neg $s 0, $s 0

GSEIS - LME Instrução Load Word: a instrução acessa o valor da memória e copia o valor encontrado num registrador. Exemplo: lw $s 1, 8($a 0) O endereço efetivo da memória a ser acessado é o valor da soma entre o conteúdo do registrador $a 0 (o endereço base) e o valor constante 8 (o deslocamento). A instrução equivalente em pseudocódigo seria: $s 1 = Mem[$a 0 + 8] Escola Politécnica da Universidade de São Paulo

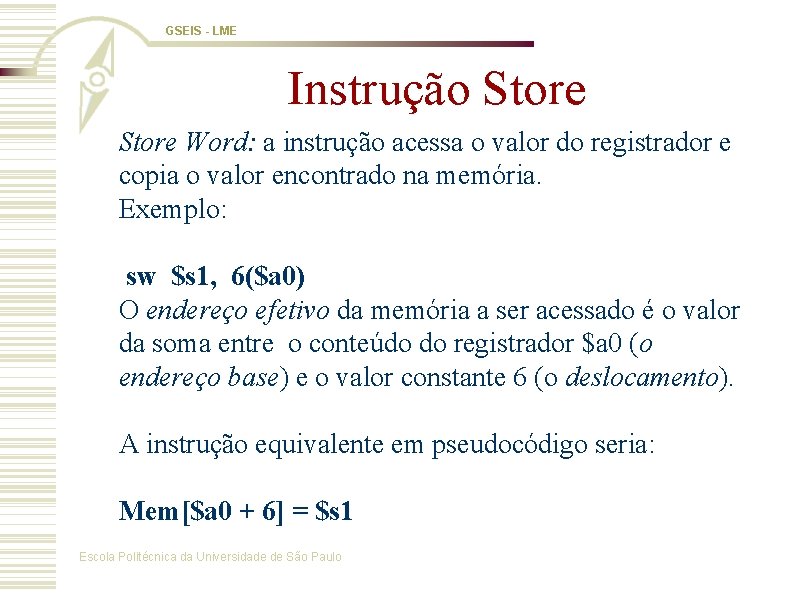

GSEIS - LME Instrução Store Word: a instrução acessa o valor do registrador e copia o valor encontrado na memória. Exemplo: sw $s 1, 6($a 0) O endereço efetivo da memória a ser acessado é o valor da soma entre o conteúdo do registrador $a 0 (o endereço base) e o valor constante 6 (o deslocamento). A instrução equivalente em pseudocódigo seria: Mem[$a 0 + 6] = $s 1 Escola Politécnica da Universidade de São Paulo

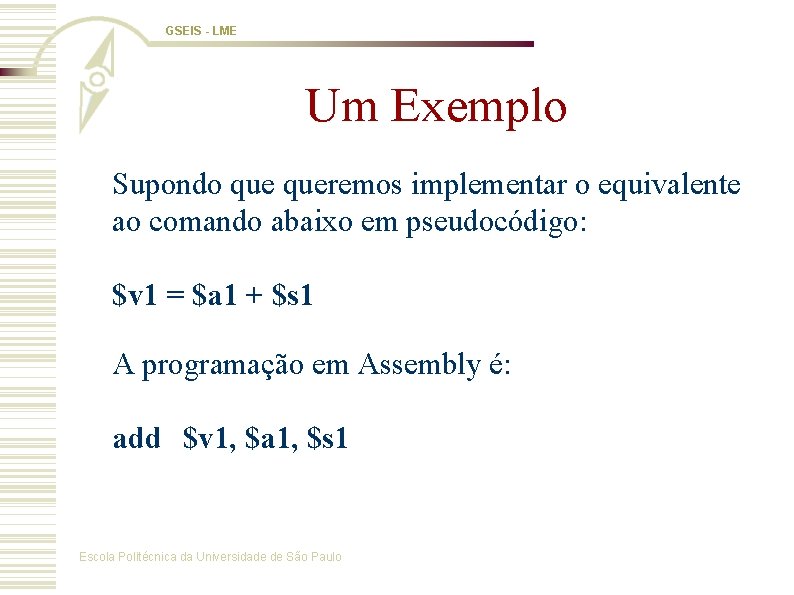

GSEIS - LME Um Exemplo Supondo queremos implementar o equivalente ao comando abaixo em pseudocódigo: $v 1 = $a 1 + $s 1 A programação em Assembly é: add $v 1, $a 1, $s 1 Escola Politécnica da Universidade de São Paulo

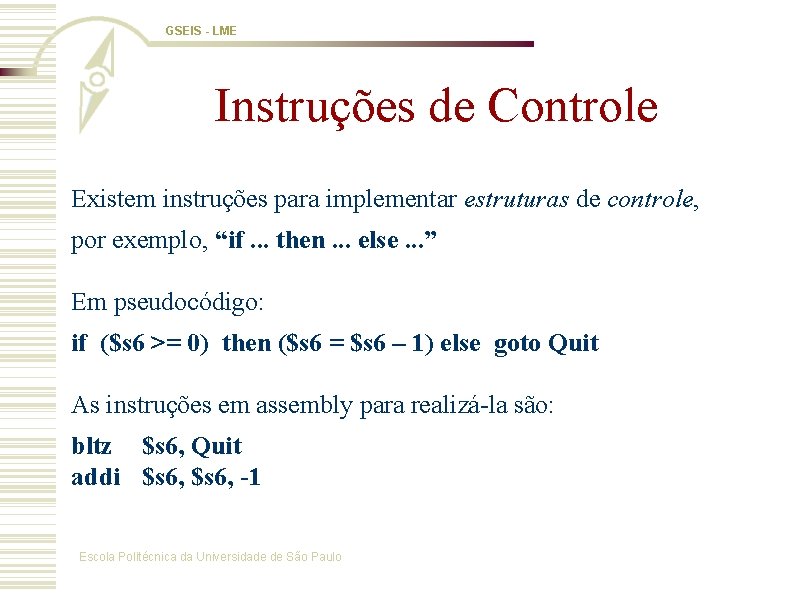

GSEIS - LME Instruções de Controle Existem instruções para implementar estruturas de controle, por exemplo, “if. . . then. . . else. . . ” Em pseudocódigo: if ($s 6 >= 0) then ($s 6 = $s 6 – 1) else goto Quit As instruções em assembly para realizá-la são: bltz $s 6, Quit addi $s 6, -1 Escola Politécnica da Universidade de São Paulo

GSEIS - LME Instrução de Multiplicação-1 A instrução “mult” multiplica dois valores binários de 32 bits e produz um produto de 64 bits que é armazenado em dois registradores especiais denominados High e Low. Neste caso, a destinação para o resultado é implicitamentendido (ex. mult $a 1, $s 1) O registrador High é carregado com os 32 bits mais significativos do produto; o registrador Low é carregado com os 32 bits menos significativos. Escola Politécnica da Universidade de São Paulo

GSEIS - LME Instrução de Multiplicação-2 Para mover uma cópia dos valores nos registradores High e Low para o banco de registradores, deve-se usar as instruções mfhi e mflo, respectivamente. O trecho de código a seguir mostra como o produto de 64 bits entre $a 1 X $s 1 pode ser movido para $v 0 e $v 1: mult $a 1, $s 1 mfhi $v 0 mflo $v 1 Escola Politécnica da Universidade de São Paulo

GSEIS - LME Instrução de Divisão A instrução de divisão é similar: o quociente é armazenado no registrador Low enquanto o resto é armazenado em High. Exemplo: div$a 1, $s 1 - divide o conteúdo de $a 1 pelo conteúdo de $s 1 mflo $v 0 - move o quociente para $v 0 mfhi $v 1 - move o resto para $v 1 Na arquitetura MIPS, a divisão por zero é indefinida. Cabe ao programador evitar a situação pelo controle do divisor. Escola Politécnica da Universidade de São Paulo

GSEIS - LME Tipos de endereçamento As operações Load/Store só admitem um tipo de endereçamento: Base address plus displacement Ex. lw $s 1, 8($a 0) Escola Politécnica da Universidade de São Paulo

GSEIS - LME Tipos de endereçamento lw $s 1, 8($a 0) Significa: Primeiro calcule o endereço da memória somando (conteúdo reg $a 0 + 8) Depois transfira o conteúdo deste endereço de memória para o reg $s 1 Em termos de pseudo-código: $s 1 = Mem($a 0+8) Escola Politécnica da Universidade de São Paulo

GSEIS - LME Execução passo-a-passo 1 – Instruction fetch 2 – Operand fetch 3 – Execute (op) 4 – Write back Escola Politécnica da Universidade de São Paulo

GSEIS - LME Diagrama do Data. Path Program de Counter (PC) Contador Programa Cache Memory Memória Out Endereço Address Instruction Register Registrador de Instruções ALU ULA Rs Rs Control Lógica Logic de Controle Rd Data In Dados In Rt Rt 44 Register Banco de. File Registradores Escola Politécnica da Universidade de São Paulo

![GSEIS - LME Sequência de Operações IR = Mem[PC] PC = PC + 4 GSEIS - LME Sequência de Operações IR = Mem[PC] PC = PC + 4](http://slidetodoc.com/presentation_image_h/a21b4c29cff89798fe4b7060e2b50ba1/image-34.jpg)

GSEIS - LME Sequência de Operações IR = Mem[PC] PC = PC + 4 Memória (lw/sw) Decodificar Instrução Desvios (beqz) Ler do Banco de Regs. Address = Rs + Offset R-Type sw lw If (Rs == 0 ) then PC = PC + Offset Memory[Address] = Rt Reg. File[Rt] = Memory[Address] Escola Politécnica da Universidade de São Paulo Reg. File[Rd] = Rs operation Rt

- Slides: 34