Grard The Hard Man behind the Soft Core

Gérard: The Hard Man behind the Soft Core Satnam Singh Microsoft Research, Cambridge UK The University of Birmingham

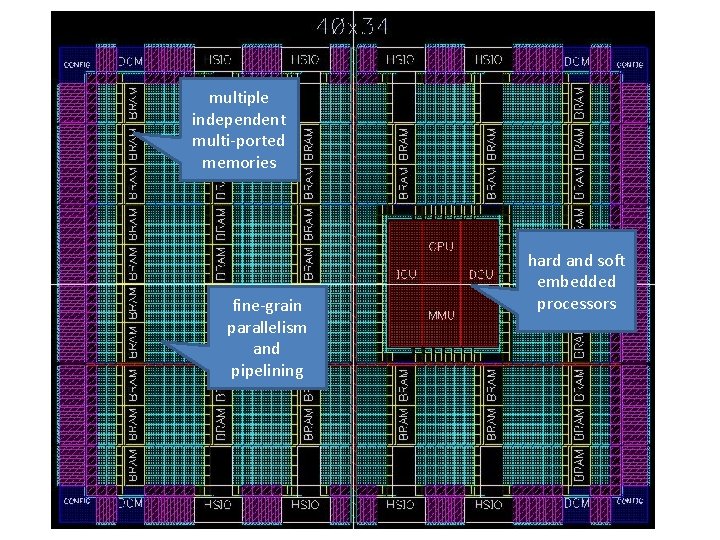

multiple independent multi-ported memories fine-grain parallelism and pipelining hard and soft embedded processors

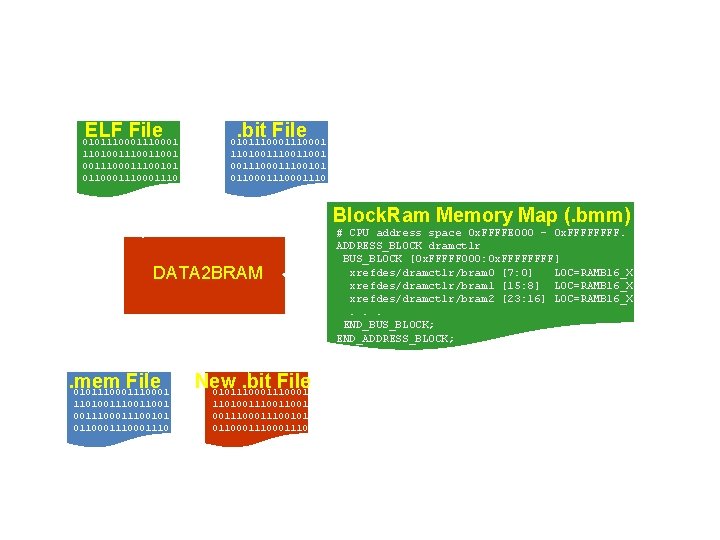

ELF File 0101110001 11010011001 0011100101 0110001110 . bit File 0101110001 11010011001 0011100101 0110001110 Block. Ram Memory Map (. bmm) DATA 2 BRAM . mem File 0101110001 11010011001 0011100101 0110001110 New. bit File 0101110001 11010011001 0011100101 0110001110 # CPU address space 0 x. FFFFE 000 - 0 x. FFFF. ADDRESS_BLOCK dramctlr BUS_BLOCK [0 x. FFFFF 000: 0 x. FFFF] xrefdes/dramctlr/bram 0 [7: 0] LOC=RAMB 16_X 0 Y 0; xrefdes/dramctlr/bram 1 [15: 8] LOC=RAMB 16_X 1 Y 0; xrefdes/dramctlr/bram 2 [23: 16] LOC=RAMB 16_X 2 Y 0; . . . END_BUS_BLOCK; END_ADDRESS_BLOCK;

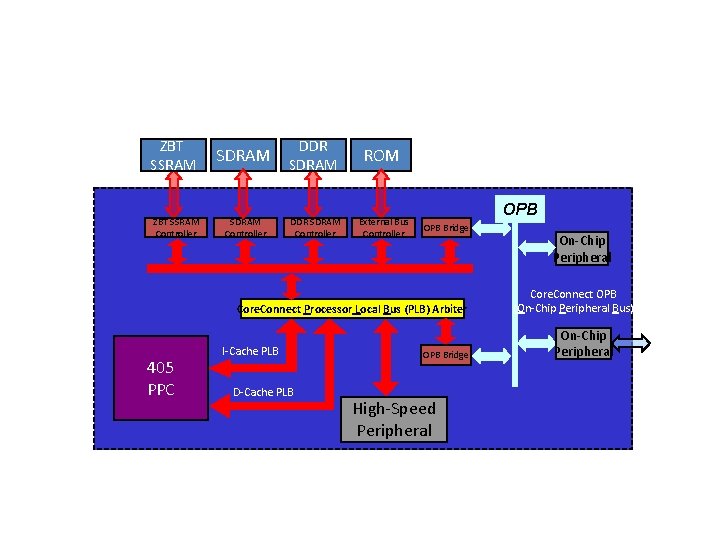

ZBT SSRAM SDRAM DDR SDRAM ROM ZBT SSRAM Controller SDRAM Controller DDR SDRAM Controller External Bus Controller OPB Bridge Core. Connect Processor Local Bus (PLB) Arbiter 405 PPC I-Cache PLB D-Cache PLB OPB Bridge High-Speed Peripheral On-Chip Peripheral Core. Connect OPB (On-Chip Peripheral Bus) On-Chip Peripheral

locks monitors condition variables spin locks priority inversion

PLDI 1998

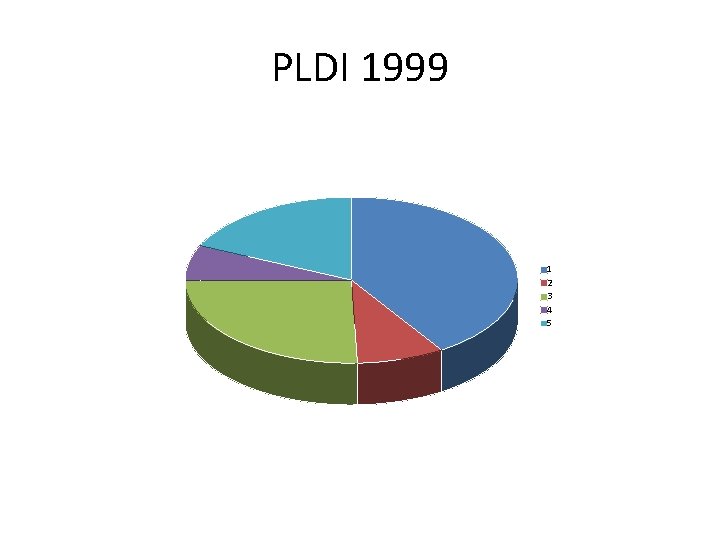

PLDI 1999 1 2 3 4 5

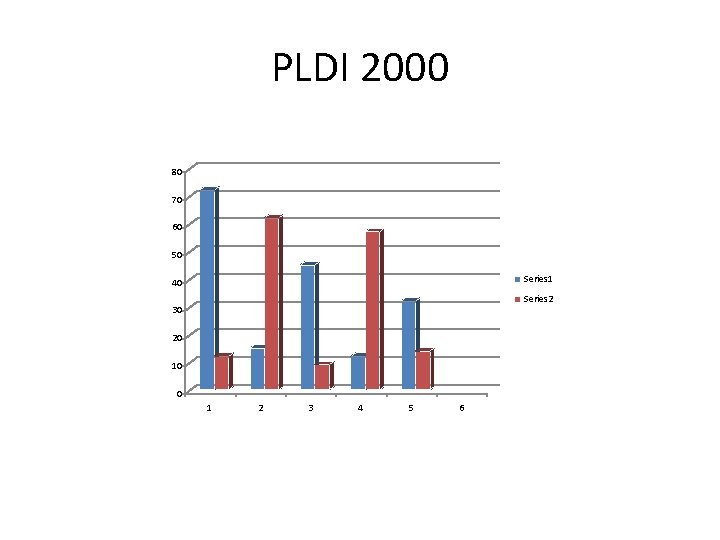

PLDI 2000 80 70 60 50 Series 1 40 Series 2 30 20 10 0 1 2 3 4 5 6

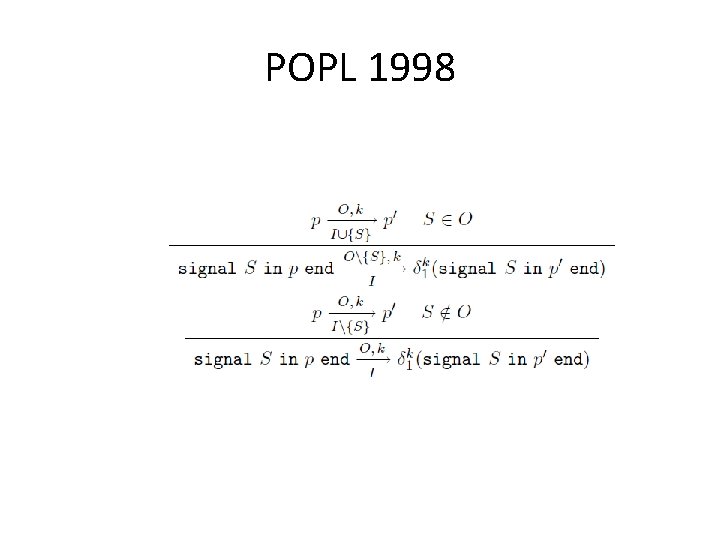

POPL 1998

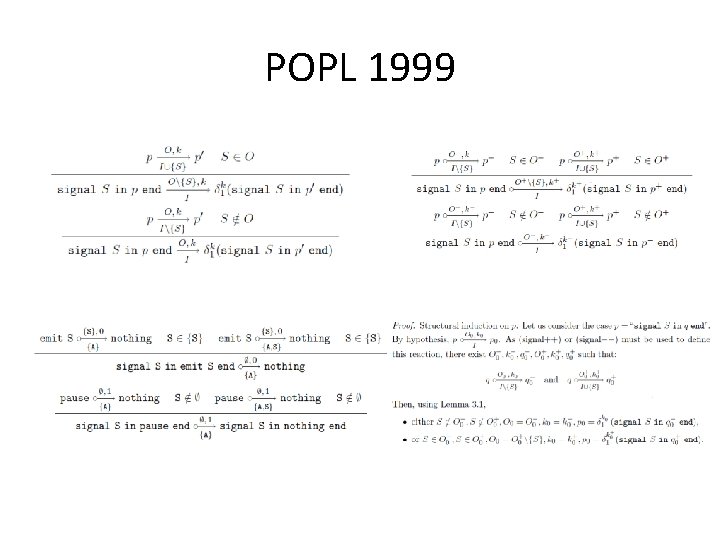

POPL 1999

POPL 2000

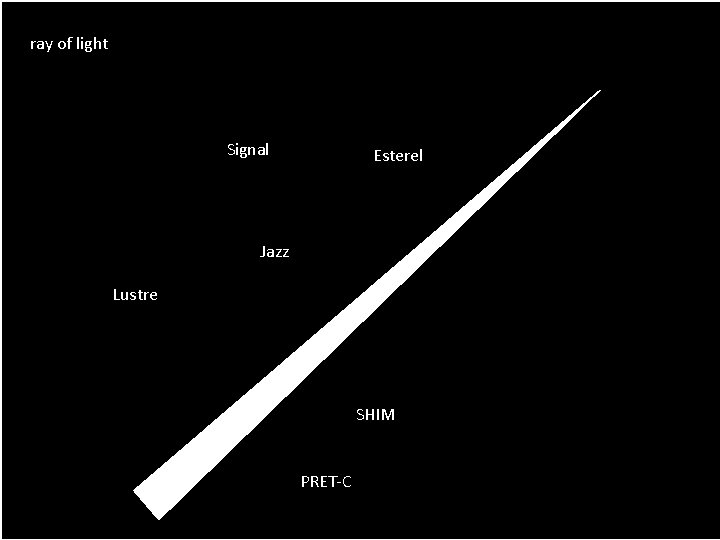

ray of light Signal Esterel Jazz Lustre SHIM PRET-C

San Jose, 6 June 2003

Sylvan Dissoubray

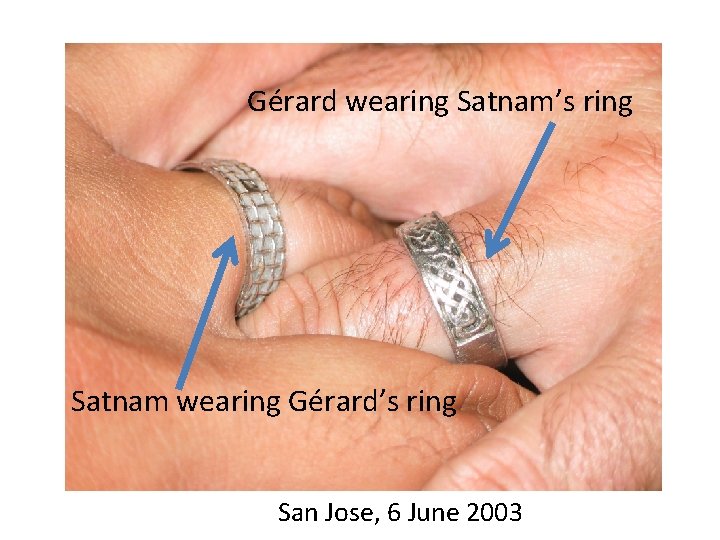

Gérard wearing Satnam’s ring Satnam wearing Gérard’s ring San Jose, 6 June 2003

Gérard Berry Nicolas Halbwachs Albert Benveniste Synchronous Programming Language Combat Team

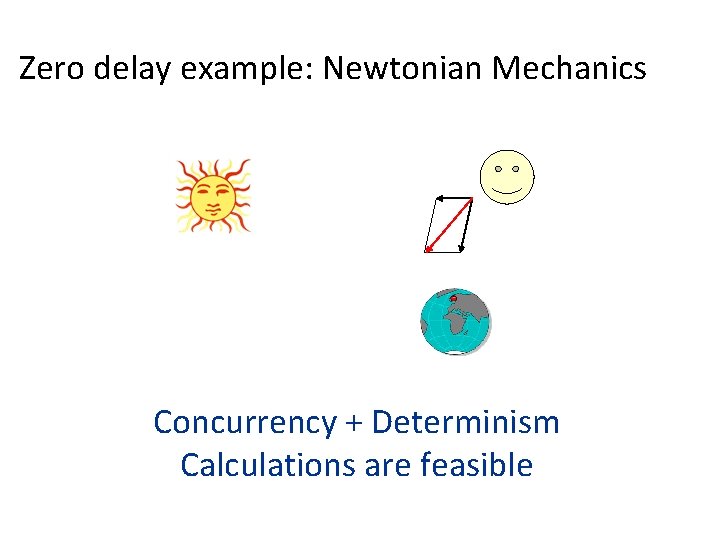

Zero delay example: Newtonian Mechanics Concurrency + Determinism Calculations are feasible

Predictable delay examples: sound, light, waves • Wait long enough, same result as 0 -delay ! • Zero delay and predictable delay are fully compatible • Constructive semantics is the unification • A theory of causality for reactive systems • Clocked digital circuits paradigm

![Safe State Machines Esterel code loop [ await A || await B ] ; Safe State Machines Esterel code loop [ await A || await B ] ;](http://slidetodoc.com/presentation_image_h/c198dafd0019ecb48bb5a3a8b9a540dd/image-27.jpg)

Safe State Machines Esterel code loop [ await A || await B ] ; emit O each R

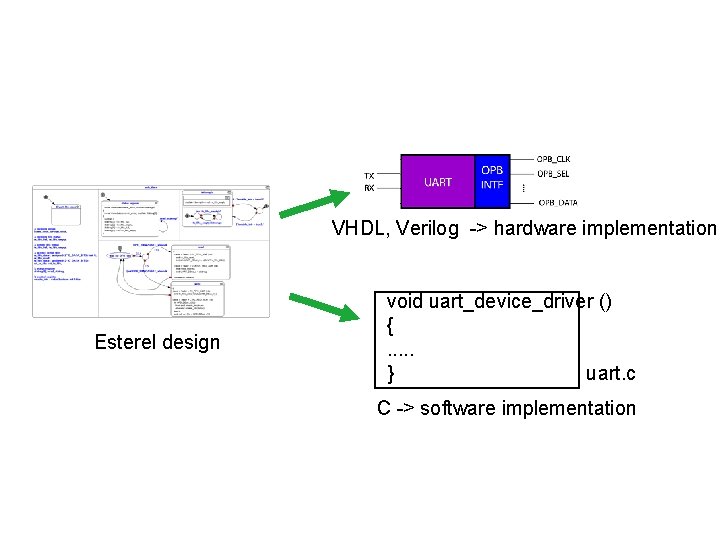

VHDL, Verilog -> hardware implementation Esterel design void uart_device_driver () {. . . uart. c } C -> software implementation

Hardware UART

Software UART

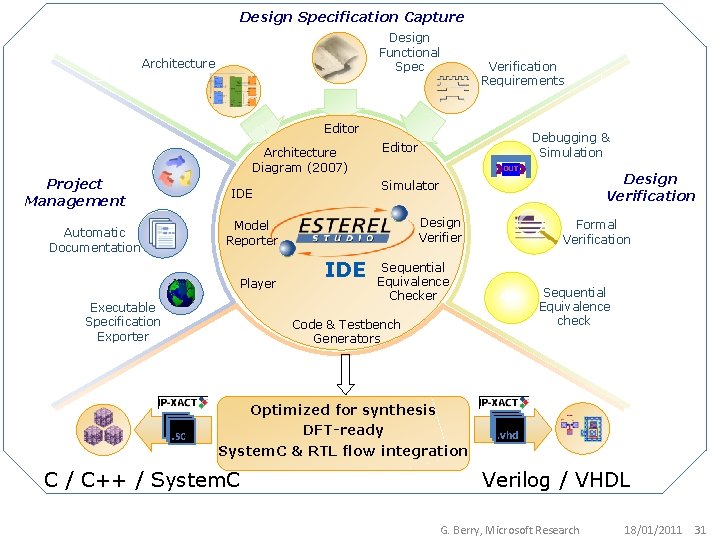

Design Specification Capture Design Functional Spec Architecture Verification Requirements Editor Project Structure Architecture Diagram (2007) Project Management DUT Design Verifier Model Reporter Player Executable Specification Exporter IDE Sequential Equivalence Checker Formal Verification Code & Testbench Generators . sc Optimized for synthesis DFT-ready System. C & RTL flow integration C / C++ / System. C Design Verification Simulator IDE Automatic Documentation Debugging & Simulation Editor Sequential Equivalence check . vhd Verilog / VHDL G. Berry, Microsoft Research 18/01/2011 31

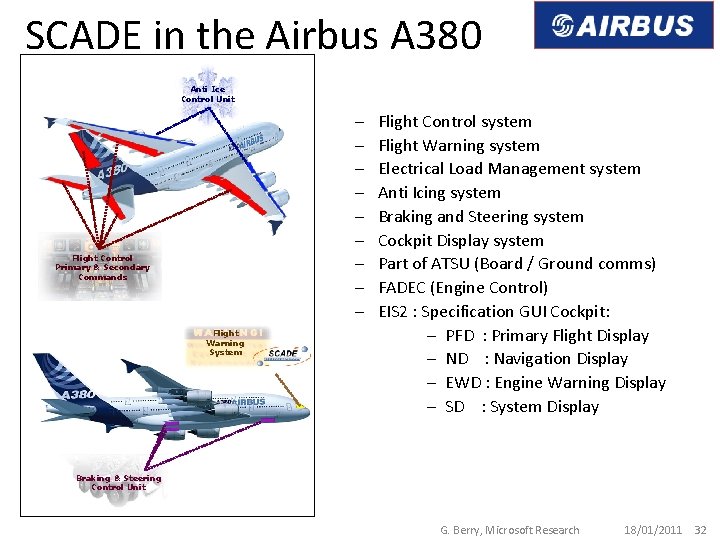

SCADE in the Airbus A 380 Anti Ice Control Unit – – – – – Flight Control Primary & Secondary Commands Flight Warning System Flight Control system Flight Warning system Electrical Load Management system Anti Icing system Braking and Steering system Cockpit Display system Part of ATSU (Board / Ground comms) FADEC (Engine Control) EIS 2 : Specification GUI Cockpit: – PFD : Primary Flight Display – ND : Navigation Display – EWD : Engine Warning Display – SD : System Display Braking & Steering Control Unit G. Berry, Microsoft Research 18/01/2011 32

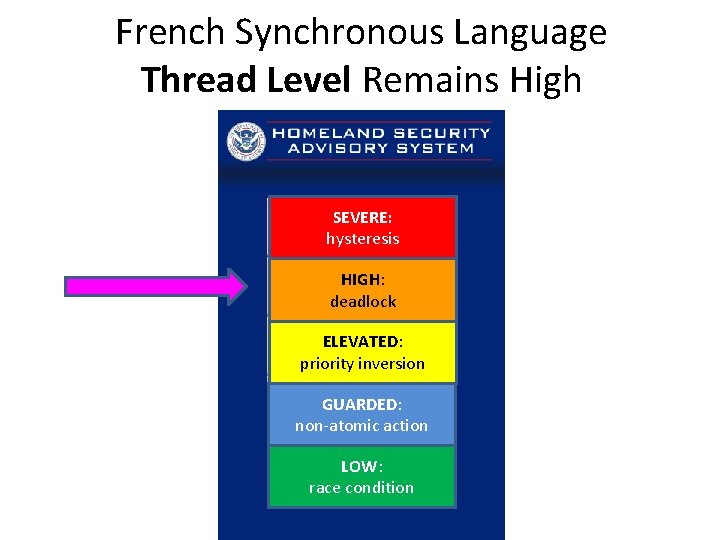

French Synchronous Language Thread Level Remains High SEVERE: hysteresis HIGH: deadlock ELEVATED: priority inversion GUARDED: non-atomic action LOW: race condition

begin … end static final void procedure if then else for while loop accept case

present gift then await scream end present Thank you Stephen Edwards

present gift then pause; every day do await thanks end every end present Thank you Stephen Edwards

abort nothing when bored Thank you Stephen Edwards

every day do nothing end every Thank you Stephen Edwards

run slowly Thank you Stephen Edwards

await falls ; every body do sustain disbelief end every Thank you Stephen Edwards

present case legally do run away end present Thank you Stephen Edwards

abort task when immediate objection Thank you Jens Brandt

abort run slowly || run fastly when sleepy Thank you Mike Kishinevsky

trap mouse in every loop do run cheese end every handle hair do run water end trap Thank you Mike Kishinevsky

Engine control software programmed in Esterel by non-French speaker

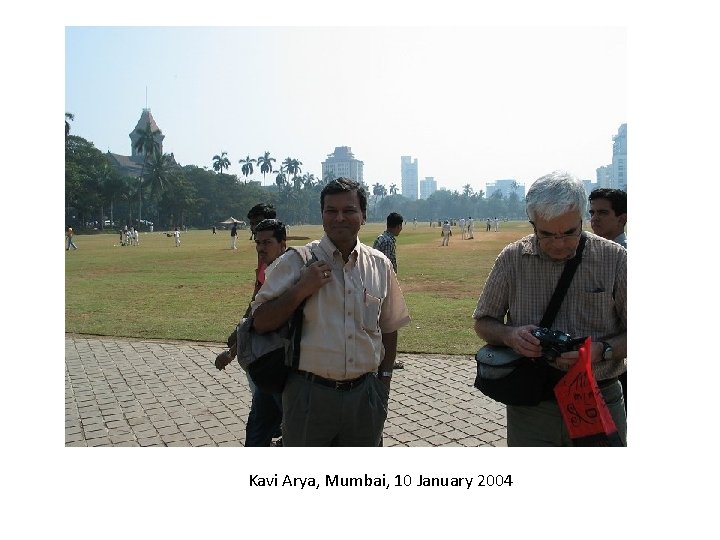

Kavi Arya, Mumbai, 10 January 2004

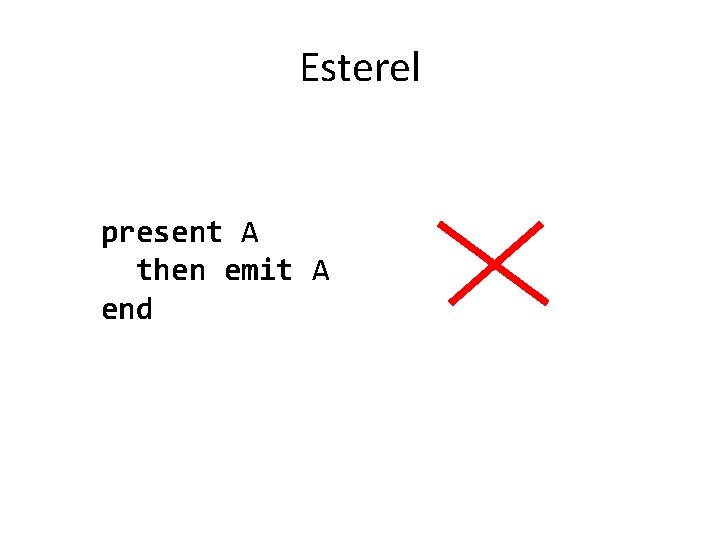

Esterel present A then emit A end

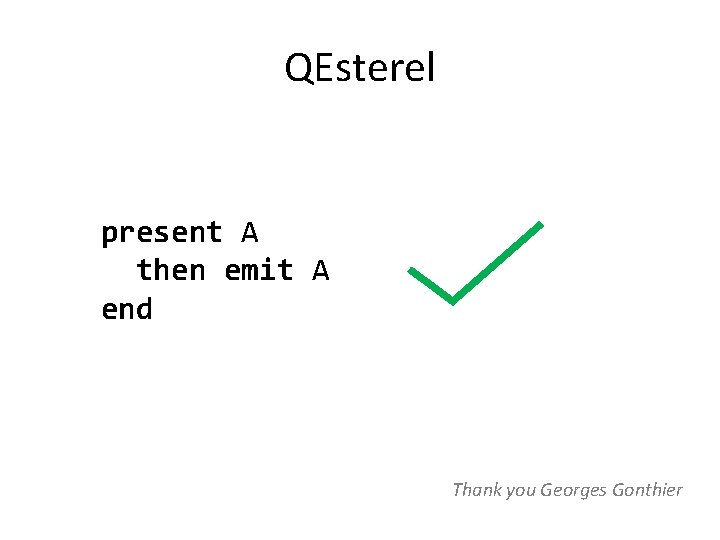

QEsterel present A then emit A end Thank you Georges Gonthier

Mike Kishinevsky

Mike Kishinevsky

- Slides: 53