Graduate Institute of Electronics Engineering NTU Digital System

- Slides: 11

Graduate Institute of Electronics Engineering, NTU Digital System Design Course Introduction Lecturer: 吳安宇 Date: 2004/02/20 ACCESS IC LAB

Advanced VLSI Graduate Institute of Electronics Engineering, NTU Contexts v Digital system design plays an important role in implementing digital functions in modern system-on-chip (SOC) design. v In this course, we will focus on developing the design skills for undergraduate students so that they can be familiar with state-of-theart digital front-end design skills and flow. 2004/02/20 台灣大學 吳安宇 教授 2

Advanced VLSI Graduate Institute of Electronics Engineering, NTU This course covers: v Firstly, we will introduce the Hardware Description Language (HDL). The chosen HDL is Verilog. We will formally cover v. The HDL grammar v. The coding guideline v. The synthesis guideline v. Modern cell-based synthesis flow v. Reuse Manual Methodology (RMM) 2004/02/20 台灣大學 吳安宇 教授 3

Advanced VLSI Graduate Institute of Electronics Engineering, NTU This course covers: v Secondly, we will ask students to design an advanced MIPS CPU. It is based on the knowledge of “Computer Organization and Design. ” The assignment covers v Instruction development. v HDL coding and simulation of major blocks such as Arithmetic Logic Unit (ALU) and Control Unit (CU). v Enhanced CPU design with Pipelining and Forwarding v Integration of whole design. v Thirdly, port the MIPS CPU design to FPGA board and perform emulation (optional) 2004/02/20 台灣大學 吳安宇 教授 4

Advanced VLSI Graduate Institute of Electronics Engineering, NTU Course Outline 2004/02/20 台灣大學 吳安宇 教授 5

Advanced VLSI Graduate Institute of Electronics Engineering, NTU Verilog HDL Outlines v v Overview of Verilog Hardware Describe Languages Modeling and Verification with Verilog-HDLs Logic Design with Behavior Models Introduction to synthesis with Verilog-HDLs v Synthesis of Combinational Circuits v Synthesis of Sequential Circuits v State machines & Datapath Controllers v Architecture and Algorithm v Coding Style 2004/02/20 台灣大學 吳安宇 教授 6

Advanced VLSI Graduate Institute of Electronics Engineering, NTU Advanced MIPS CPU Outlines v Overview of MIPS CPU Architecture v Instruction Sets v Arithmetic Logic Unit Design v Control Flow Design v Pipelining Architecture v Forwarding Architecture 2004/02/20 台灣大學 吳安宇 教授 7

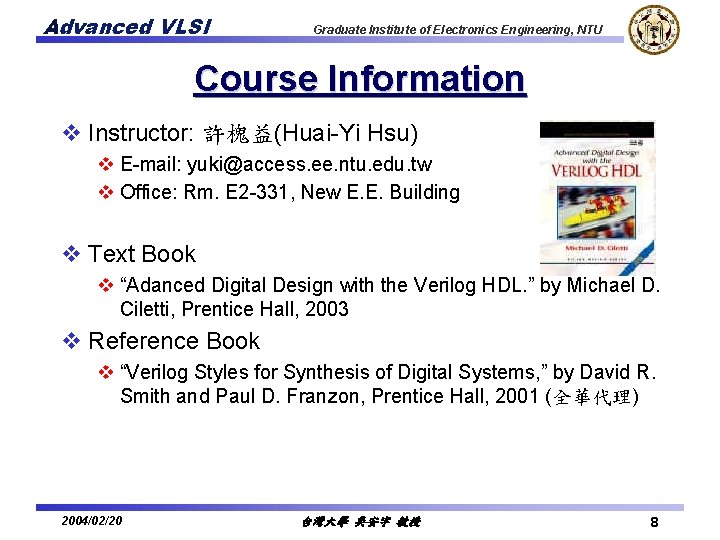

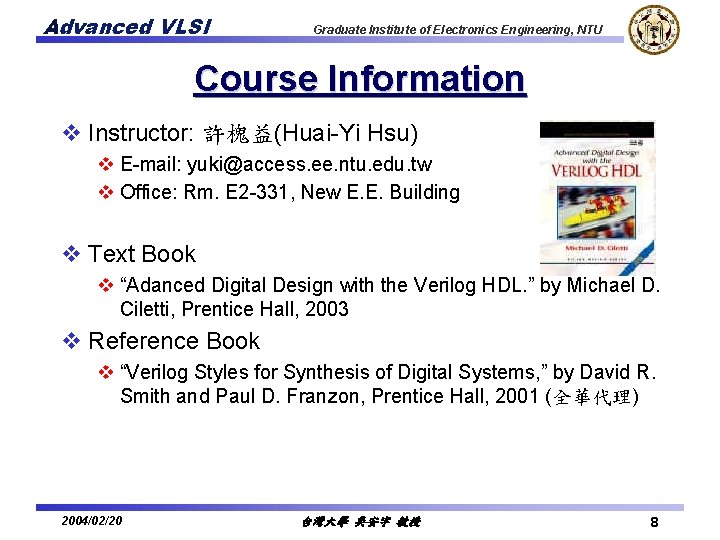

Advanced VLSI Graduate Institute of Electronics Engineering, NTU Course Information v Instructor: 許槐益(Huai-Yi Hsu) v E-mail: yuki@access. ee. ntu. edu. tw v Office: Rm. E 2 -331, New E. E. Building v Text Book v “Adanced Digital Design with the Verilog HDL. ” by Michael D. Ciletti, Prentice Hall, 2003 v Reference Book v “Verilog Styles for Synthesis of Digital Systems, ” by David R. Smith and Paul D. Franzon, Prentice Hall, 2001 (全華代理) 2004/02/20 台灣大學 吳安宇 教授 8

Advanced VLSI Graduate Institute of Electronics Engineering, NTU Reference Books v M. D. Ciletti, “Modeling, Synthesis, and Rapid Prototyping with the Verilog HDL, ” Prentice-Hall, 1999. v “Verilog HDL: A Guide to Digital Design and Synthesis, ” 2 nd ed. , by Samir Palnitkar, Sun. Soft, 2003 (全華代理) v “Reuse Methodology Manual for System-On-A-Chip Designs, ” 3 rd Edition, by Michael Keating, Pierre Bricaud, Kluwer Academic Publishers, 2002. v “Computer organization & design: The hardware/software interface, ” 2 nd edition, by David A. Patterson and John L. Hennessy, Morgan Kaufmann, 1998. v 黃英叡、江文啓、黃稚存、張銓淵編譯, “Verilog硬體描述語言, ” 全華書局, 2001. v 楊紹聖、蕭鳴均、李進福、蔡培元編譯, “Verilog數位電腦設計, ” 全華書局, 2001. 2004/02/20 台灣大學 吳安宇 教授 9

Advanced VLSI Graduate Institute of Electronics Engineering, NTU Course Grading v v Participation 2% (about four times). One mid-terms 22% Final Projects (demo and presentation) 36% Computer Labs and Homework (about four labs and ten homework) 40% 2004/02/20 台灣大學 吳安宇 教授 10

Advanced VLSI Graduate Institute of Electronics Engineering, NTU Background v v v Programming Language, Logic Design (basic) Computer Organization and Design (required) VLSI Design (optional) 2004/02/20 台灣大學 吳安宇 教授 11