Goal Build an ALU The Arithmetic Logic Unit

Goal: Build an ALU ®The Arithmetic Logic Unit or ALU is the device that performs arithmetic and logical operations in the computer. ® We will build it out of 4 basic building blocks. AND gate: performs the AND operation on 2 signals. OR gate: performs the OR operation on 2 signals. Inverter: inverts the incoming signal (o to 1, 1 to 0). Multiplexor: chooses between one out of several incoming signals. Computer Structure - The ALU 1/13

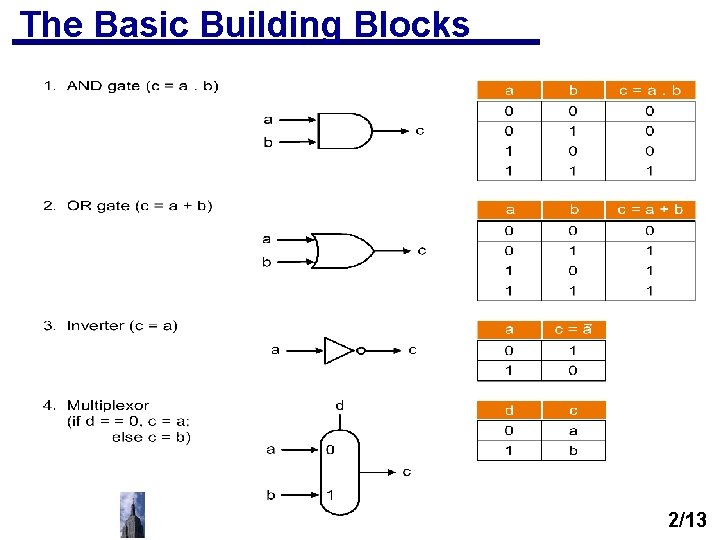

The Basic Building Blocks 2/13

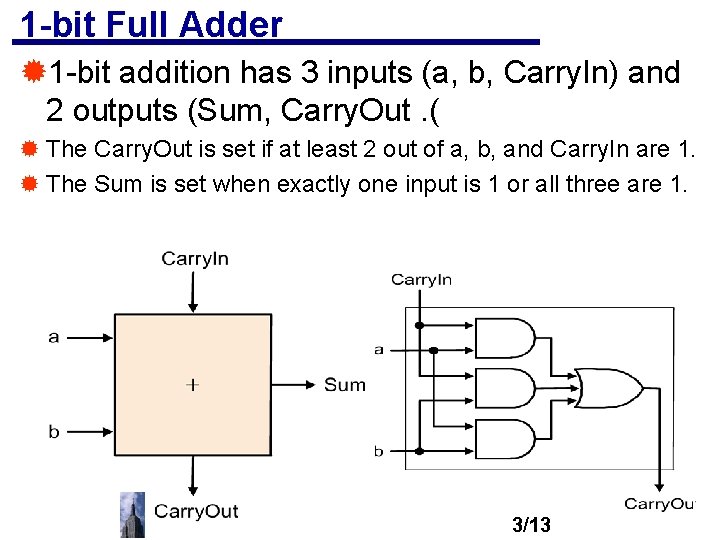

1 -bit Full Adder ® 1 -bit addition has 3 inputs (a, b, Carry. In) and 2 outputs (Sum, Carry. Out. ( ® The Carry. Out is set if at least 2 out of a, b, and Carry. In are 1. ® The Sum is set when exactly one input is 1 or all three are 1. 3/13

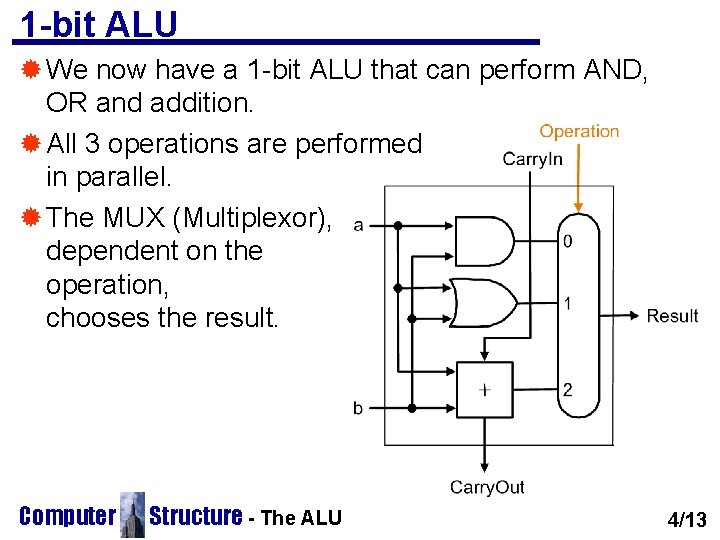

1 -bit ALU ® We now have a 1 -bit ALU that can perform AND, OR and addition. ® All 3 operations are performed in parallel. ® The MUX (Multiplexor), dependent on the operation, chooses the result. Computer Structure - The ALU 4/13

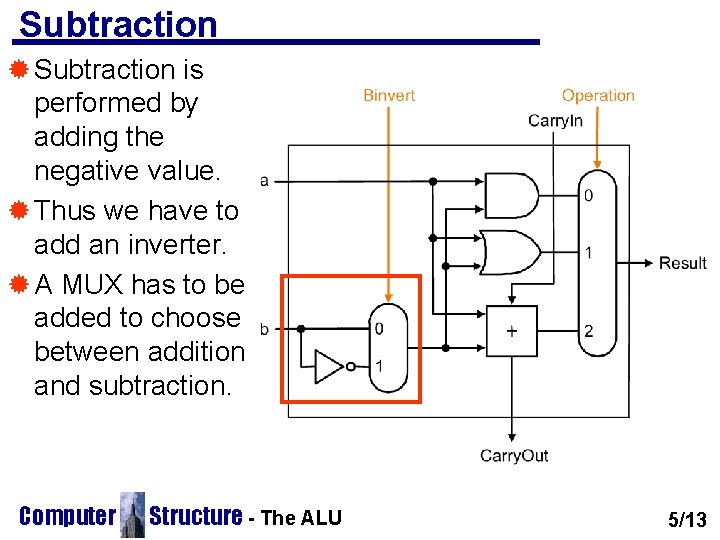

Subtraction ® Subtraction is performed by adding the negative value. ® Thus we have to add an inverter. ® A MUX has to be added to choose between addition and subtraction. Computer Structure - The ALU 5/13

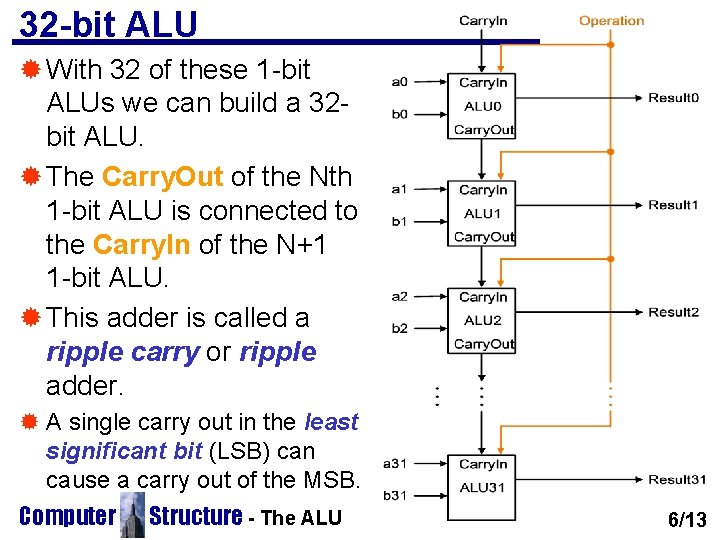

32 -bit ALU ® With 32 of these 1 -bit ALUs we can build a 32 bit ALU. ® The Carry. Out of the Nth 1 -bit ALU is connected to the Carry. In of the N+1 1 -bit ALU. ® This adder is called a ripple carry or ripple adder. ® A single carry out in the least significant bit (LSB) can cause a carry out of the MSB. Computer Structure - The ALU 6/13

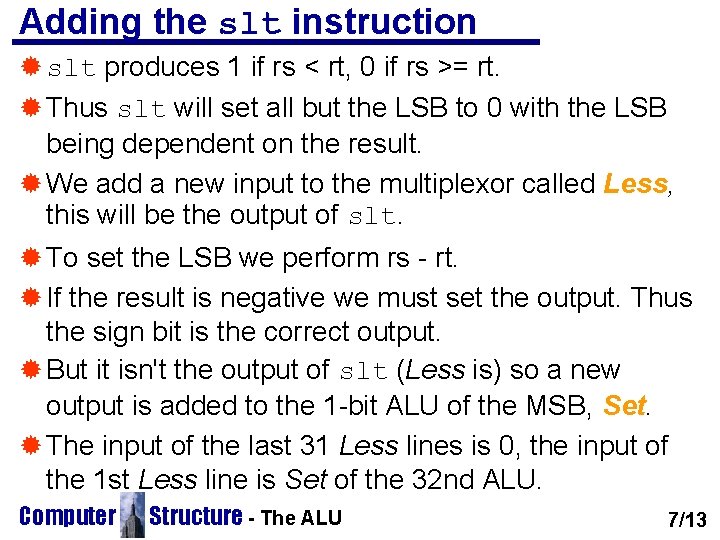

Adding the slt instruction ® slt produces 1 if rs < rt, 0 if rs >= rt. ® Thus slt will set all but the LSB to 0 with the LSB being dependent on the result. ® We add a new input to the multiplexor called Less, this will be the output of slt. ® To set the LSB we perform rs - rt. ® If the result is negative we must set the output. Thus the sign bit is the correct output. ® But it isn't the output of slt (Less is) so a new output is added to the 1 -bit ALU of the MSB, Set. ® The input of the last 31 Less lines is 0, the input of the 1 st Less line is Set of the 32 nd ALU. Computer Structure - The ALU 7/13

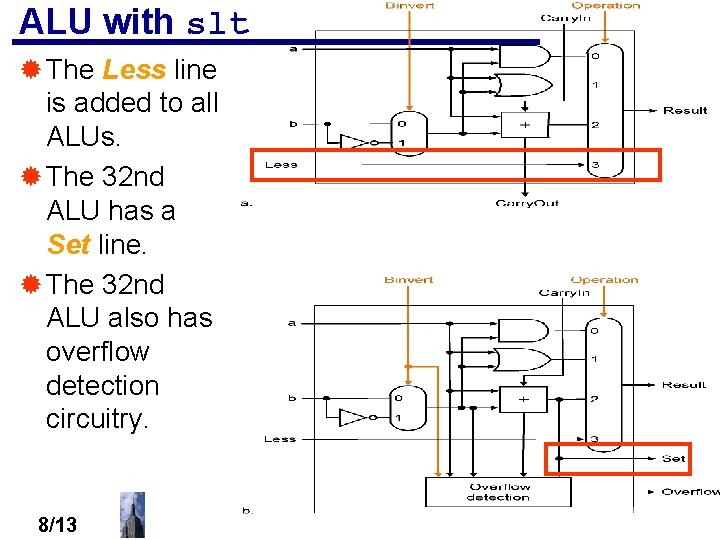

ALU with slt ® The Less line is added to all ALUs. ® The 32 nd ALU has a Set line. ® The 32 nd ALU also has overflow detection circuitry. 8/13

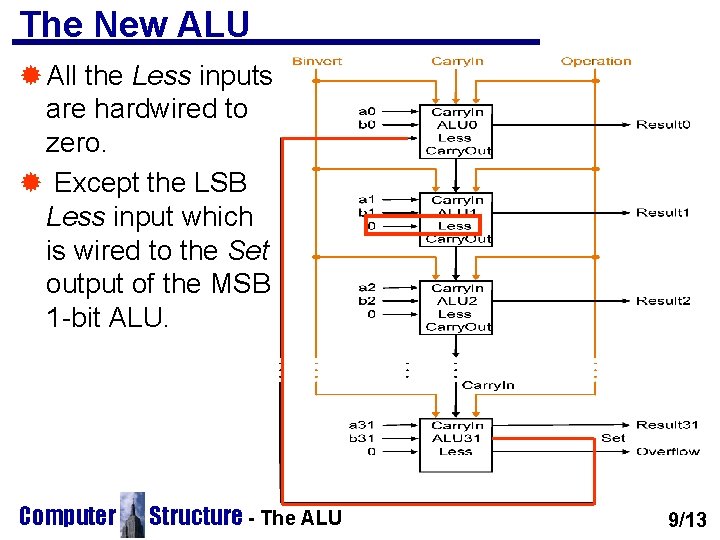

The New ALU ® All the Less inputs are hardwired to zero. ® Except the LSB Less input which is wired to the Set output of the MSB 1 -bit ALU. Computer Structure - The ALU 9/13

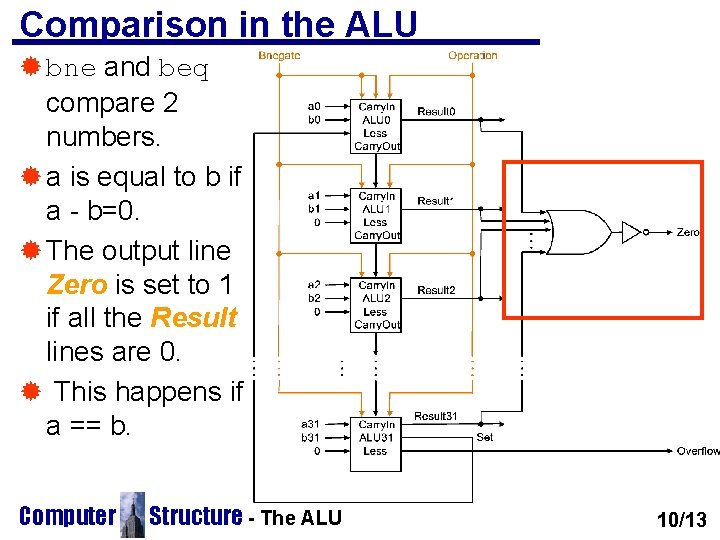

Comparison in the ALU ® bne and beq compare 2 numbers. ® a is equal to b if a - b=0. ® The output line Zero is set to 1 if all the Result lines are 0. ® This happens if a == b. Computer Structure - The ALU 10/13

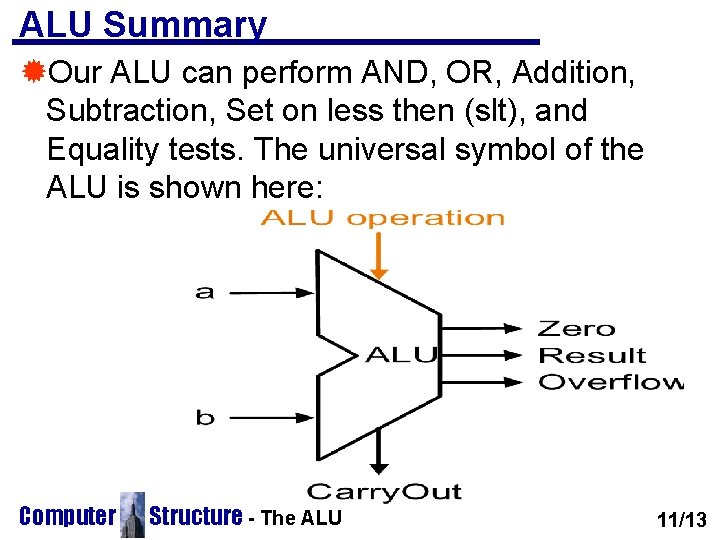

ALU Summary ®Our ALU can perform AND, OR, Addition, Subtraction, Set on less then (slt), and Equality tests. The universal symbol of the ALU is shown here: Computer Structure - The ALU 11/13

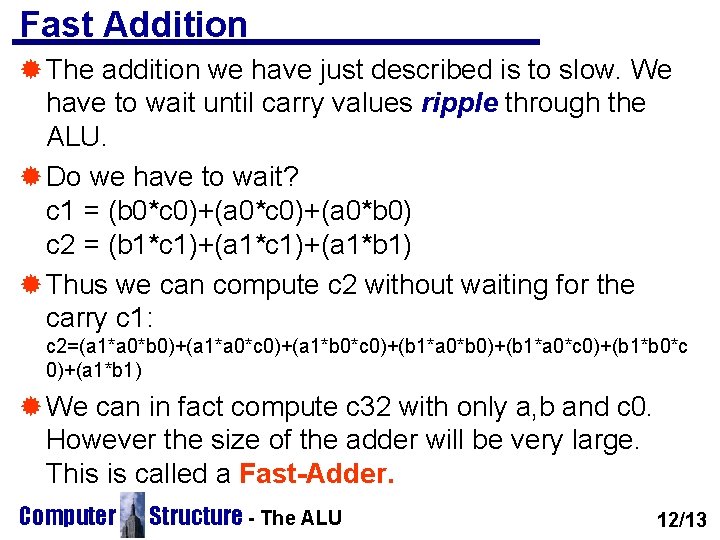

Fast Addition ® The addition we have just described is to slow. We have to wait until carry values ripple through the ALU. ® Do we have to wait? c 1 = (b 0*c 0)+(a 0*b 0) c 2 = (b 1*c 1)+(a 1*b 1) ® Thus we can compute c 2 without waiting for the carry c 1: c 2=(a 1*a 0*b 0)+(a 1*a 0*c 0)+(a 1*b 0*c 0)+(b 1*a 0*b 0)+(b 1*a 0*c 0)+(b 1*b 0*c 0)+(a 1*b 1) ® We can in fact compute c 32 with only a, b and c 0. However the size of the adder will be very large. This is called a Fast-Adder. Computer Structure - The ALU 12/13

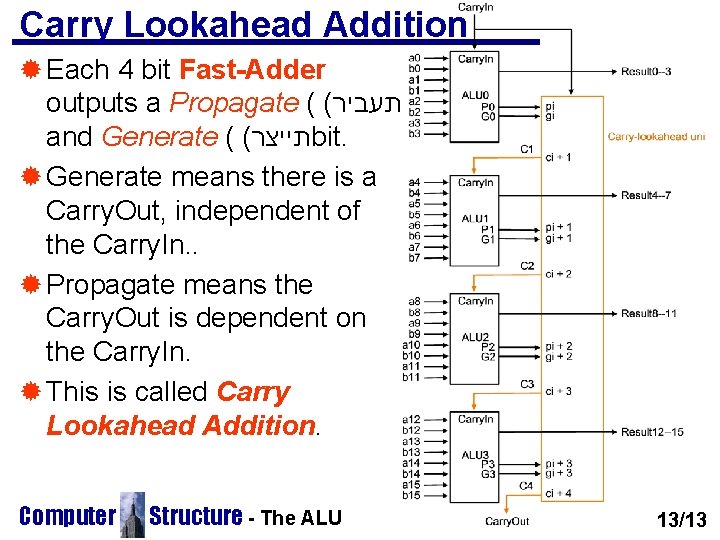

Carry Lookahead Addition ® Each 4 bit Fast-Adder outputs a Propagate ( ( תעביר and Generate ( ( תייצר bit. ® Generate means there is a Carry. Out, independent of the Carry. In. . ® Propagate means the Carry. Out is dependent on the Carry. In. ® This is called Carry Lookahead Addition. Computer Structure - The ALU 13/13

- Slides: 13