Global Semiconductor Packaging Materials Outlook Jan Vardaman President

Global Semiconductor Packaging Materials Outlook Jan Vardaman, President, Tech. Search International and Dan Tracy, Sr. Director Industry Research, SEMI 20 th/21 st January 2016

Global Semiconductor Packaging Materials Outlook Report-2015/2016 Edition • Unique and comprehensive report covering the market size, regional markets, market share, and forecast by packaging materials segment • Packaging materials markets are quantified, new opportunities are highlighted, and forecasts through 2019 are covered Laminate Substrates Liquid Encapsulants Leadframes Solder Balls Mold Compounds Wafer Level Packaging Dielectrics Underfill Thermal Interface Materials Bonding Wire Die Attach • Based on in-depth interviews and surveys of 160+ companies, including material suppliers, IDMs, packaging subcontractors, and fabless companies.

Outline • 2016 Outlook Summary (Dan Tracy) • Market Driver: Mobility (Jan Vardaman) • FO-WLP: A Disruptive Technology (Jan Vardaman) • Material Segment Trends (Jan Vardaman/Dan Tracy) • Summary

2016 Outlook Summary

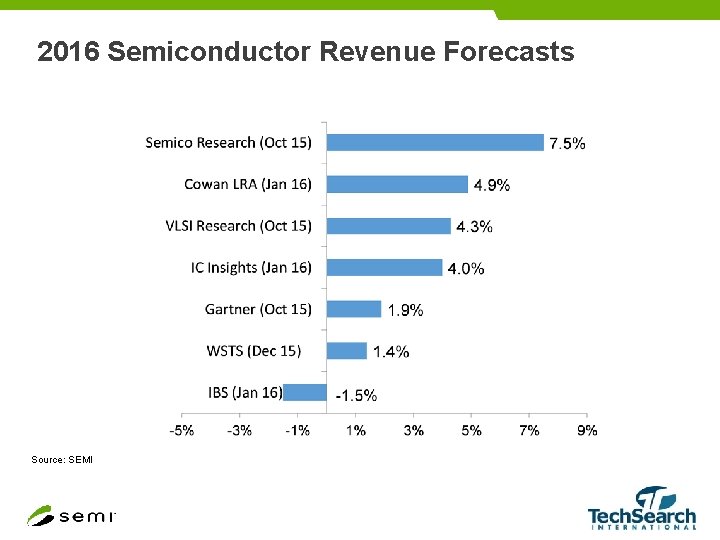

2016 Semiconductor Revenue Forecasts Source: SEMI

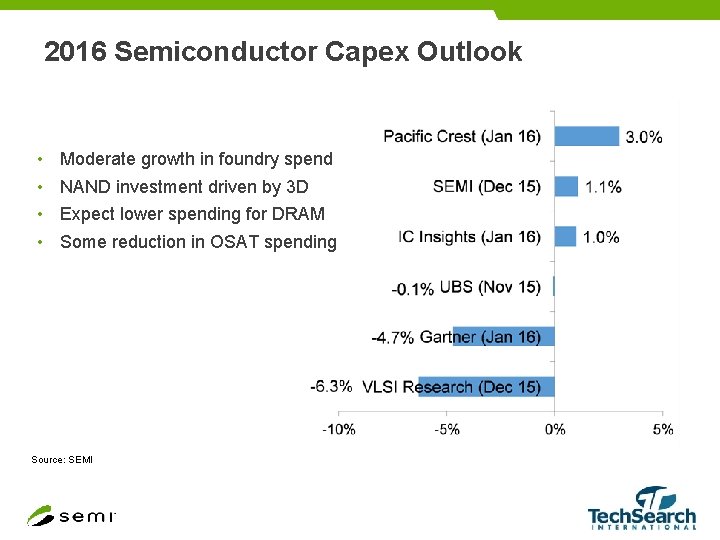

2016 Semiconductor Capex Outlook • • Moderate growth in foundry spend NAND investment driven by 3 D Expect lower spending for DRAM Some reduction in OSAT spending Source: SEMI

Market Driver: Mobility

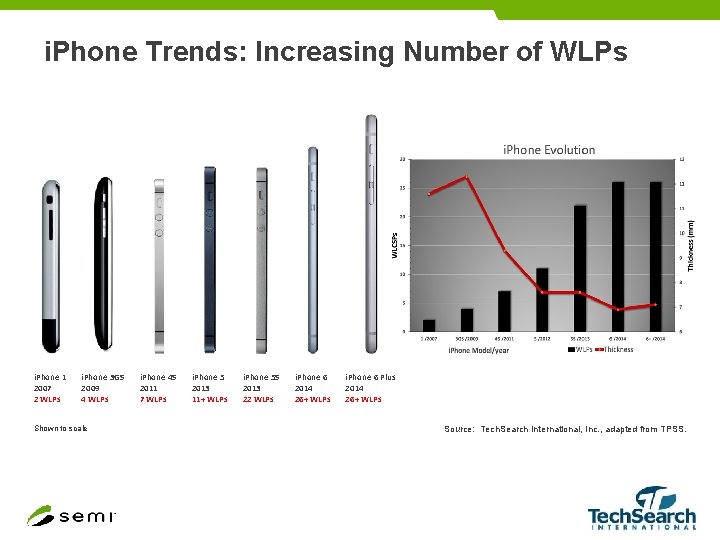

i. Phone Trends: Increasing Number of WLPs i. Phone 1 2007 2 WLPs i. Phone 3 GS 2009 4 WLPs Shown to scale i. Phone 4 S 2011 7 WLPs i. Phone 5 2013 11+ WLPs i. Phone 5 S 2013 22 WLPs i. Phone 6 2014 26+ WLPs i. Phone 6 Plus 2014 26+ WLPs Source: Tech. Search International, Inc. , adapted from TPSS.

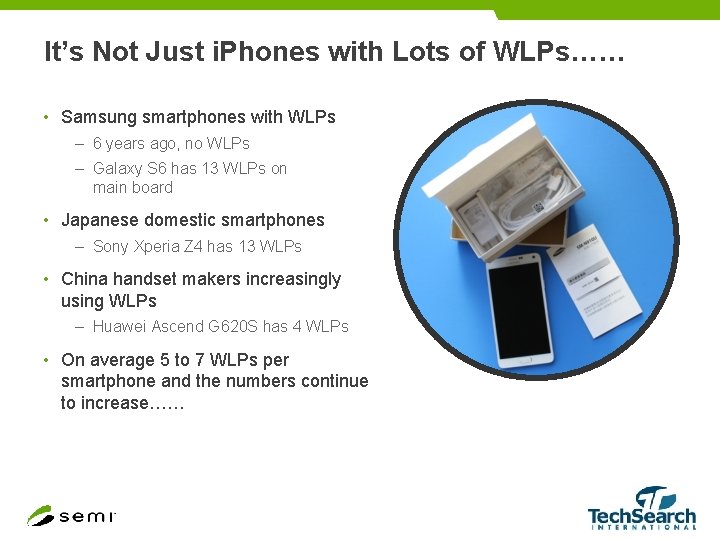

It’s Not Just i. Phones with Lots of WLPs…… • Samsung smartphones with WLPs – 6 years ago, no WLPs – Galaxy S 6 has 13 WLPs on main board • Japanese domestic smartphones – Sony Xperia Z 4 has 13 WLPs • China handset makers increasingly using WLPs – Huawei Ascend G 620 S has 4 WLPs • On average 5 to 7 WLPs per smartphone and the numbers continue to increase……

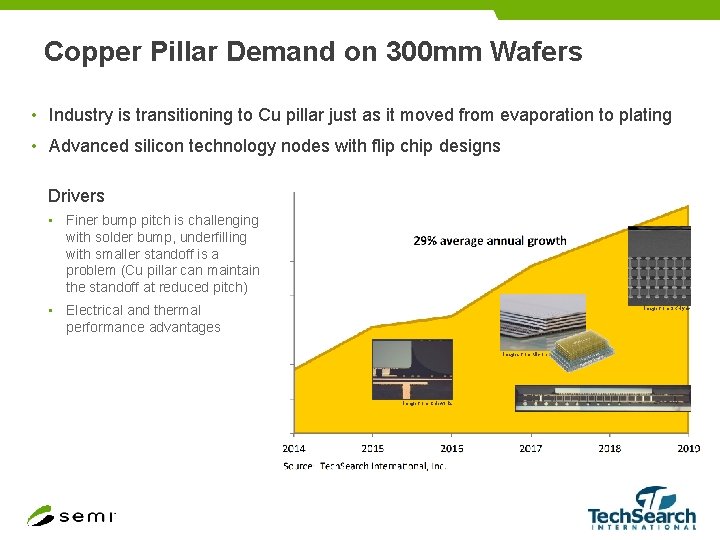

Copper Pillar Demand on 300 mm Wafers • Industry is transitioning to Cu pillar just as it moved from evaporation to plating • Advanced silicon technology nodes with flip chip designs Drivers • Finer bump pitch is challenging with solder bump, underfilling with smaller standoff is a problem (Cu pillar can maintain the standoff at reduced pitch) • Electrical and thermal performance advantages Image from SK Hynix Images from Micron Image from Chipworks

FO-WLP: A Disruptive Technology

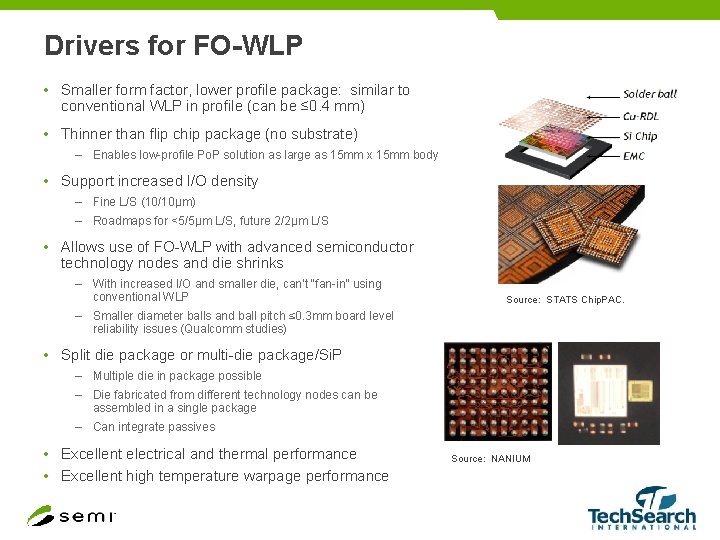

Drivers for FO-WLP • Smaller form factor, lower profile package: similar to conventional WLP in profile (can be ≤ 0. 4 mm) • Thinner than flip chip package (no substrate) – Enables low-profile Po. P solution as large as 15 mm x 15 mm body • Support increased I/O density – Fine L/S (10/10µm) – Roadmaps for <5/5µm L/S, future 2/2µm L/S • Allows use of FO-WLP with advanced semiconductor technology nodes and die shrinks – With increased I/O and smaller die, can’t “fan-in” using conventional WLP Source: STATS Chip. PAC. – Smaller diameter balls and ball pitch ≤ 0. 3 mm board level reliability issues (Qualcomm studies) • Split die package or multi-die package/Si. P – Multiple die in package possible – Die fabricated from different technology nodes can be assembled in a single package – Can integrate passives • Excellent electrical and thermal performance • Excellent high temperature warpage performance Source: NANIUM

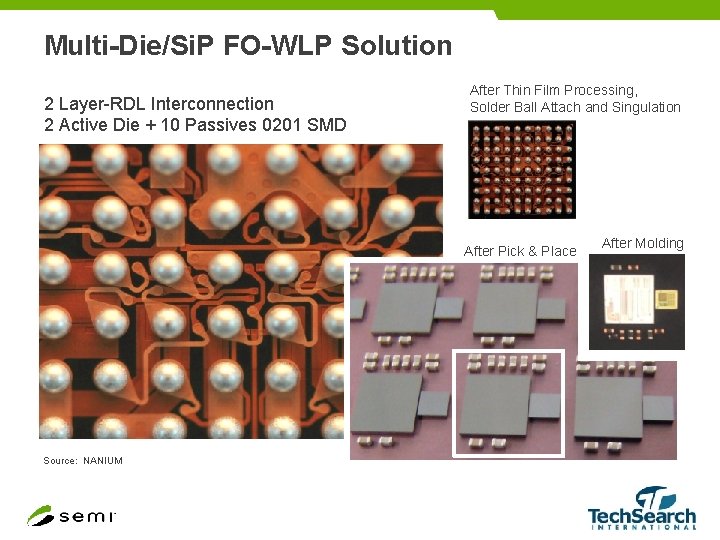

Multi-Die/Si. P FO-WLP Solution 2 Layer-RDL Interconnection 2 Active Die + 10 Passives 0201 SMD After Thin Film Processing, Solder Ball Attach and Singulation After Pick & Place Source: NANIUM After Molding

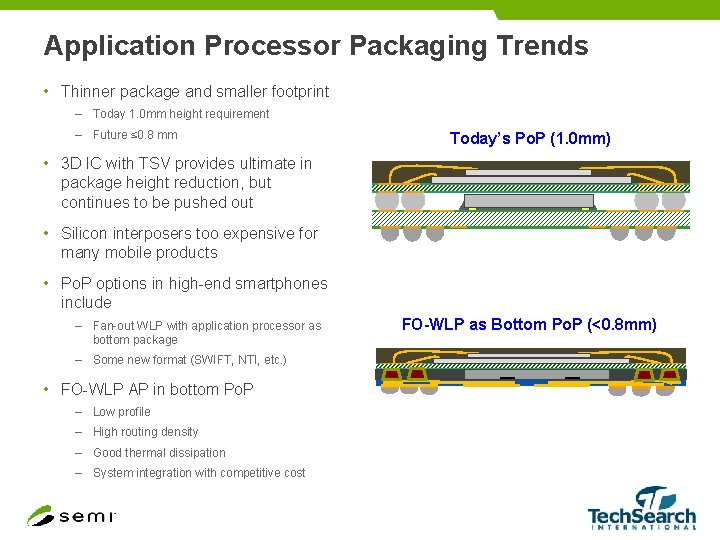

Application Processor Packaging Trends • Thinner package and smaller footprint – Today 1. 0 mm height requirement – Future ≤ 0. 8 mm Today’s Po. P (1. 0 mm) • 3 D IC with TSV provides ultimate in package height reduction, but continues to be pushed out • Silicon interposers too expensive for many mobile products • Po. P options in high-end smartphones include – Fan-out WLP with application processor as bottom package – Some new format (SWIFT, NTI, etc. ) • FO-WLP AP in bottom Po. P – Low profile – High routing density – Good thermal dissipation – System integration with competitive cost FO-WLP as Bottom Po. P (<0. 8 mm)

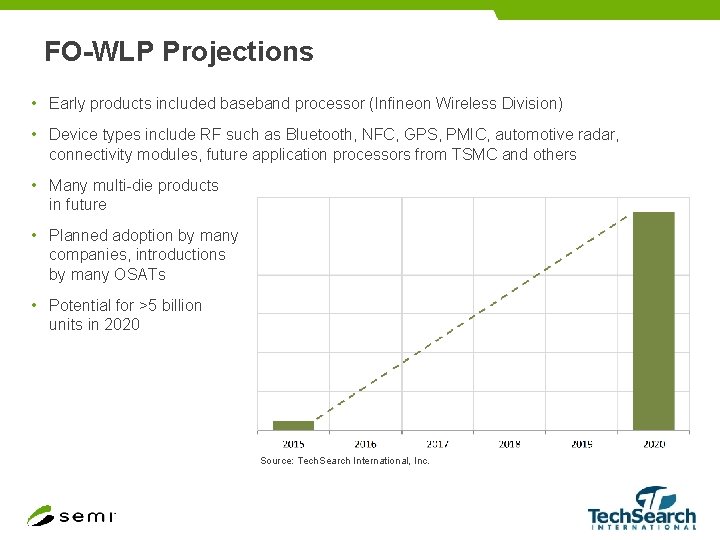

FO-WLP Projections • Early products included baseband processor (Infineon Wireless Division) • Device types include RF such as Bluetooth, NFC, GPS, PMIC, automotive radar, connectivity modules, future application processors from TSMC and others • Many multi-die products in future • Planned adoption by many companies, introductions by many OSATs • Potential for >5 billion units in 2020 Source: Tech. Search International, Inc.

Why is FO-WLP a Disruptive Technology? • No substrate! – Thin-film metallization used for substrate (can go below 5µm L/S) – No traditional laminate substrate (with multiple die, reduction of multiple substrates) – No underfill required – Most application processors had been using laminate substrate with flip chip bump interconnect • Multi-die configuration possible – Could function as system-in-package • Infrastructure changes – All packaging can take place at the foundry – OSAT assembly with non-traditional assembly line – Changes the way the industry approaches package design

Material Segment Trends

Underfill Market • Global market of ~$250 M • Many suppliers (30+) – Consolidation likely though new players entering market – Suppliers face continued price pressure • No-flow – Applied prior to chip placement, either on the wafer or substrate – Film-based, paste, and wafer applied • Growing use of mold compounds as underfill • Increased use of board-level underfill or edge underfill for some BGAs, CSPs, and WLPs – Apple underfills almost everything above a certain size – Micromax in India and many handset makers in China have almost no underfill Source: SEMI and Tech. Search International – Global Semiconductor Packaging Materials Outlook

Wafer Level Dielectrics • ~$90 M market currently • Requirements for new materials include: – Low moisture absorption (reduced outgassing at elevated temperatures) – Low stress (to match the CTE of the chip) and/or low modulus (for less wafer bow) – Low temperature cure (200 °C) – Lower dielectric constant – Higher resolution at thicker layers – Wide process windows – Enhanced board-level reliability performance – Desire for “standard” material for multi-layer applications Source: SEMI and Tech. Search International – Global Semiconductor Packaging Materials Outlook

Laminate Substrates • ~$7. 8 B market • Stable supply base • Good demand/supply balance in recent years • Flip chip substrate suppliers – Bump pitch trends drive finer features and higher substrate prices, but continued price pressure – Previously, focused on CPU and graphics applications – Now, the focus is on mobile applications – growth market but more cost sensitive and shorter development cycles – Laminate CSP outlook expected to be impacted by growth in FO-WLP Source: SEMI and Tech. Search International – Global Semiconductor Packaging Materials Outlook

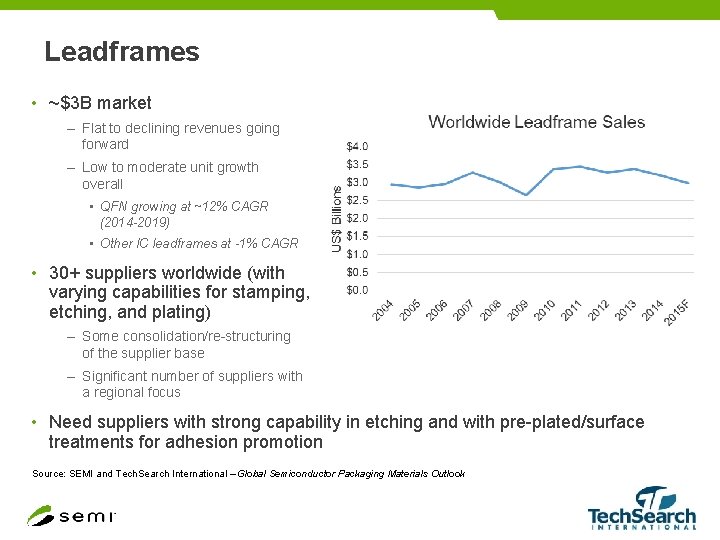

Leadframes • ~$3 B market – Flat to declining revenues going forward – Low to moderate unit growth overall • QFN growing at ~12% CAGR (2014 -2019) • Other IC leadframes at -1% CAGR • 30+ suppliers worldwide (with varying capabilities for stamping, etching, and plating) – Some consolidation/re-structuring of the supplier base – Significant number of suppliers with a regional focus • Need suppliers with strong capability in etching and with pre-plated/surface treatments for adhesion promotion Source: SEMI and Tech. Search International – Global Semiconductor Packaging Materials Outlook

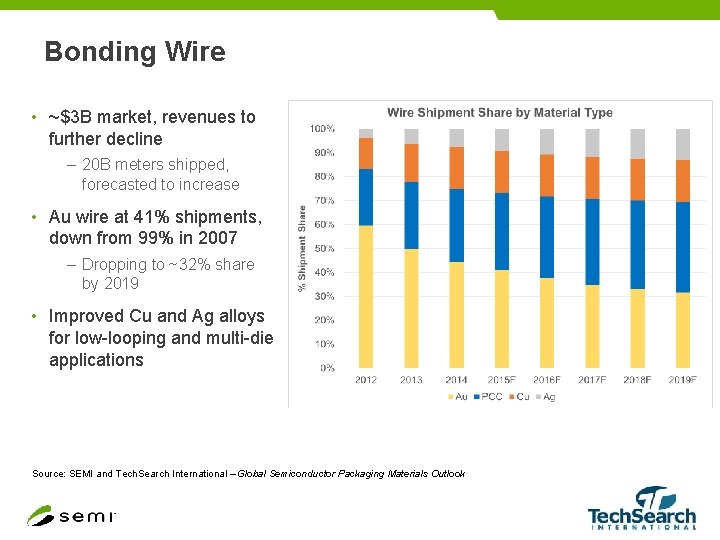

Bonding Wire • ~$3 B market, revenues to further decline – 20 B meters shipped, forecasted to increase • Au wire at 41% shipments, down from 99% in 2007 – Dropping to ~32% share by 2019 • Improved Cu and Ag alloys for low-looping and multi-die applications Source: SEMI and Tech. Search International – Global Semiconductor Packaging Materials Outlook

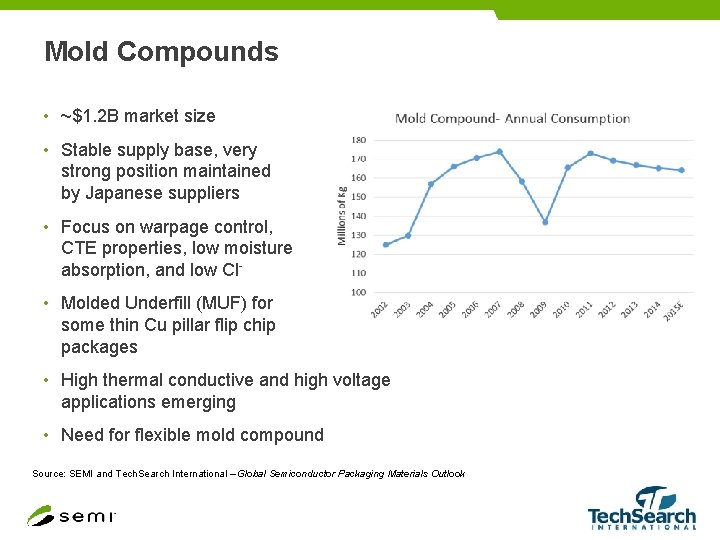

Mold Compounds • ~$1. 2 B market size • Stable supply base, very strong position maintained by Japanese suppliers • Focus on warpage control, CTE properties, low moisture absorption, and low Cl • Molded Underfill (MUF) for some thin Cu pillar flip chip packages • High thermal conductive and high voltage applications emerging • Need for flexible mold compound Source: SEMI and Tech. Search International – Global Semiconductor Packaging Materials Outlook

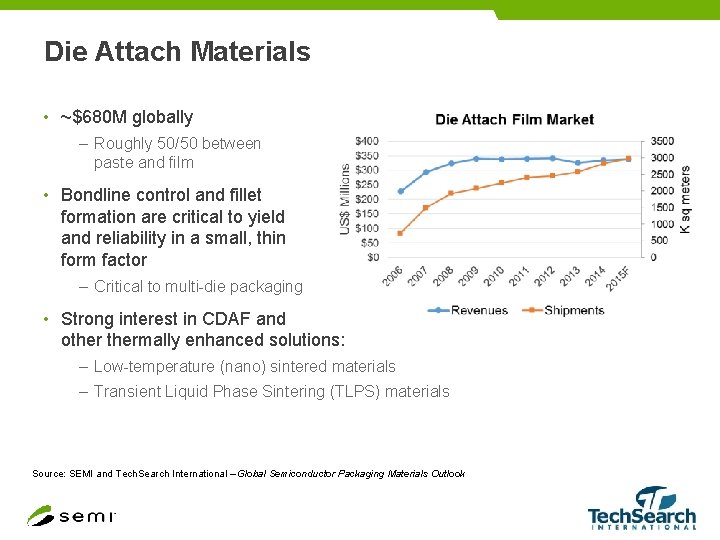

Die Attach Materials • ~$680 M globally – Roughly 50/50 between paste and film • Bondline control and fillet formation are critical to yield and reliability in a small, thin form factor – Critical to multi-die packaging • Strong interest in CDAF and othermally enhanced solutions: – Low-temperature (nano) sintered materials – Transient Liquid Phase Sintering (TLPS) materials Source: SEMI and Tech. Search International – Global Semiconductor Packaging Materials Outlook

Summary

Summary • 2016 Semiconductor Industry Outlook – Low-single digit revenue growth – Currently, Capex outlook ranges from negative to slightly positive • Packaging a key enabler of functionality in the mobile space • FO-WLP is a disruptive technology and will impact the consumption of semiconductor packaging materials • Material innovation focused on package integration and cost reduction

Q&A

Thank you for participating in today’s webinar! Global Semiconductor Packaging Materials Outlook Report-2015/2016 Edition For more information, contact: Jan Vardaman at Tech. Search International, jan@techseachinc. com Or Dan Tracy at SEMI, dtracy@semi. org To order the GSPMO report, visit: www. semi. org/en/node/58061 Or call SEMI customer service at 1. 877. 746. 7788 (toll free in the U. S. ) or 1. 408. 943. 6901 (International Callers).

- Slides: 28