Gerbang Nalar Elektronika Lanjut Oleh Eri Prasetyo Wibowo

Gerbang Nalar Elektronika Lanjut Oleh : Eri Prasetyo Wibowo

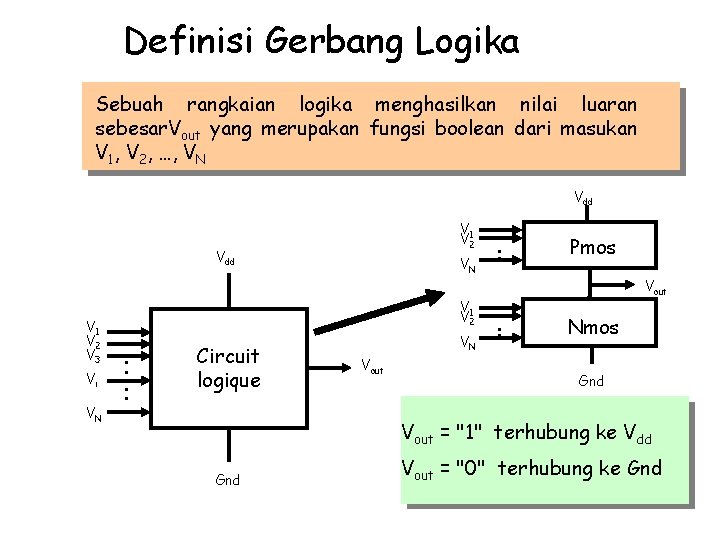

Definisi Gerbang Logika Sebuah rangkaian logika menghasilkan nilai luaran sebesar. Vout yang merupakan fungsi boolean dari masukan V 1, V 2, …, VN Vdd V 1 V 2 V 3 Vi VN VN V 1 V 2 . . Circuit logique VN Vout . . Pmos Vout . . Nmos Gnd Vout = "1" terhubung ke Vdd Gnd Vout = "0" terhubung ke Gnd

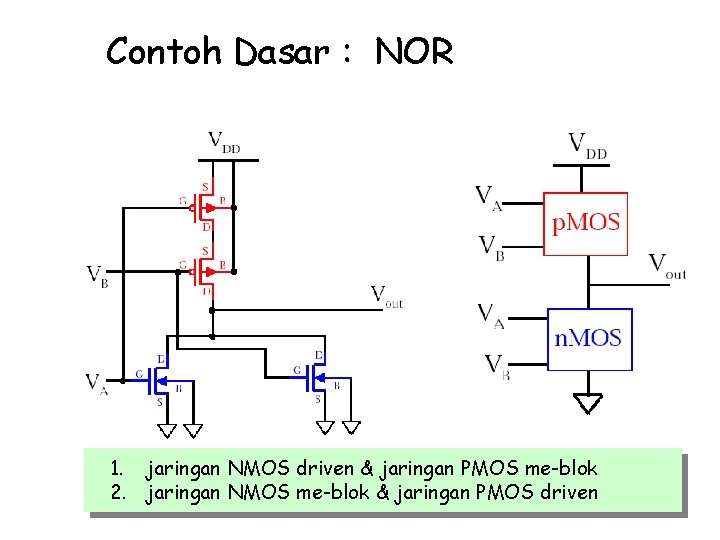

Contoh Dasar : NOR 1. jaringan NMOS driven & jaringan PMOS me-blok 2. jaringan NMOS me-blok & jaringan PMOS driven

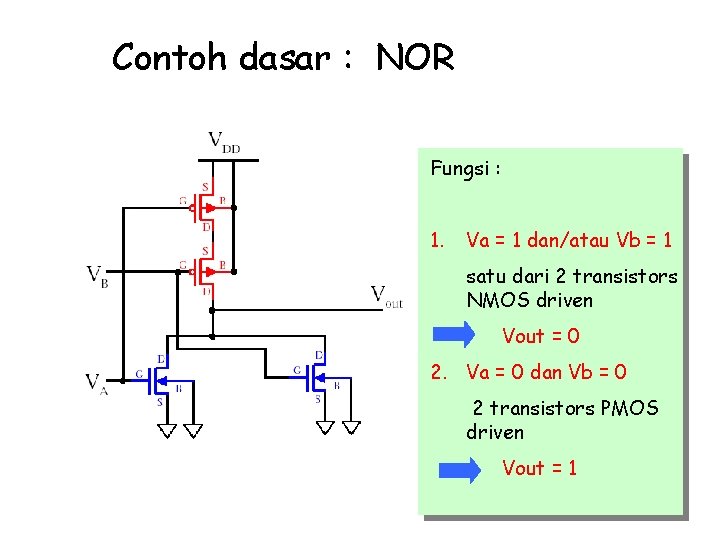

Contoh dasar : NOR Fungsi : 1. Va = 1 dan/atau Vb = 1 satu dari 2 transistors NMOS driven Vout = 0 2. Va = 0 dan Vb = 0 2 transistors PMOS driven Vout = 1

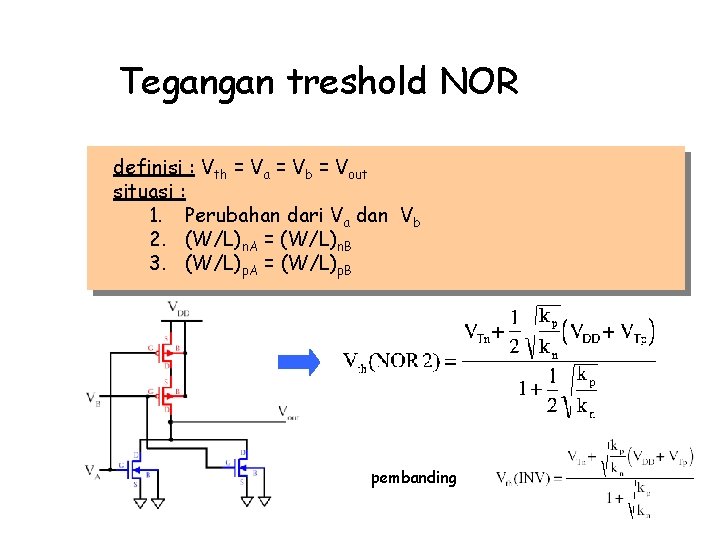

Tegangan treshold NOR definisi : Vth = Va = Vb = Vout situasi : 1. Perubahan dari Va dan Vb 2. (W/L)n. A = (W/L)n. B 3. (W/L)p. A = (W/L)p. B pembanding

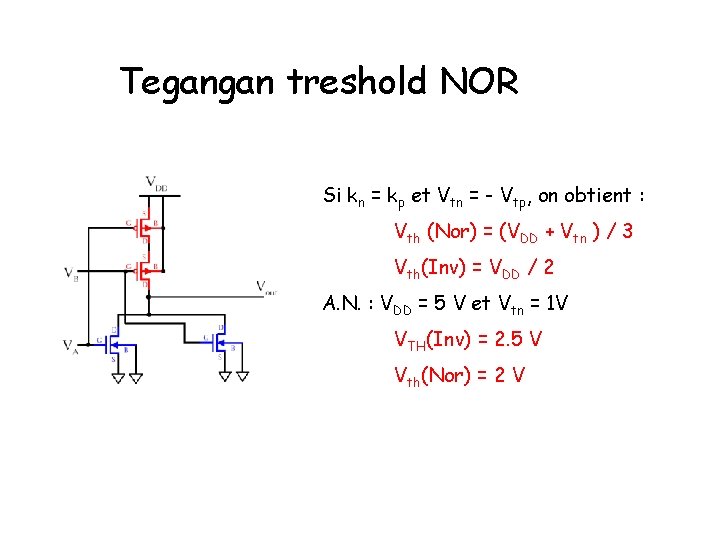

Tegangan treshold NOR Si kn = kp et Vtn = - Vtp, on obtient : Vth (Nor) = (VDD + Vtn ) / 3 Vth(Inv) = VDD / 2 A. N. : VDD = 5 V et Vtn = 1 V VTH(Inv) = 2. 5 V Vth(Nor) = 2 V

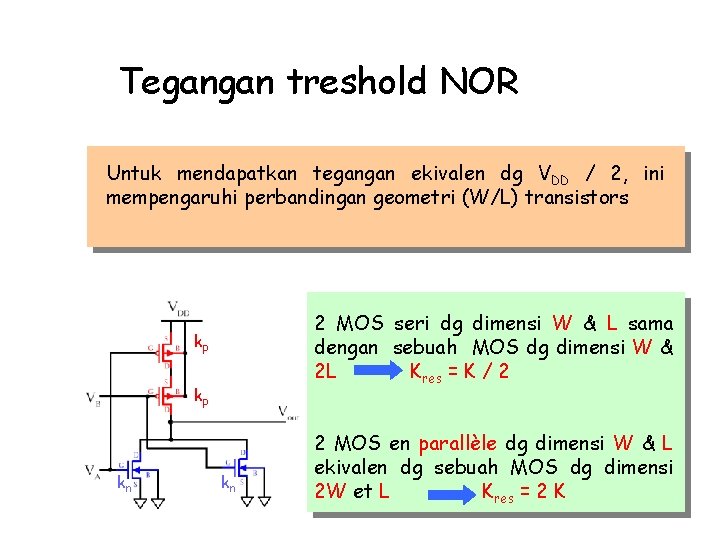

Tegangan treshold NOR Untuk mendapatkan tegangan ekivalen dg VDD / 2, ini mempengaruhi perbandingan geometri (W/L) transistors 2 MOS seri dg dimensi W & L sama dengan sebuah MOS dg dimensi W & 2 L Kres = K / 2 kp kp kn kn 2 MOS en parallèle dg dimensi W & L ekivalen dg sebuah MOS dg dimensi 2 W et L Kres = 2 K

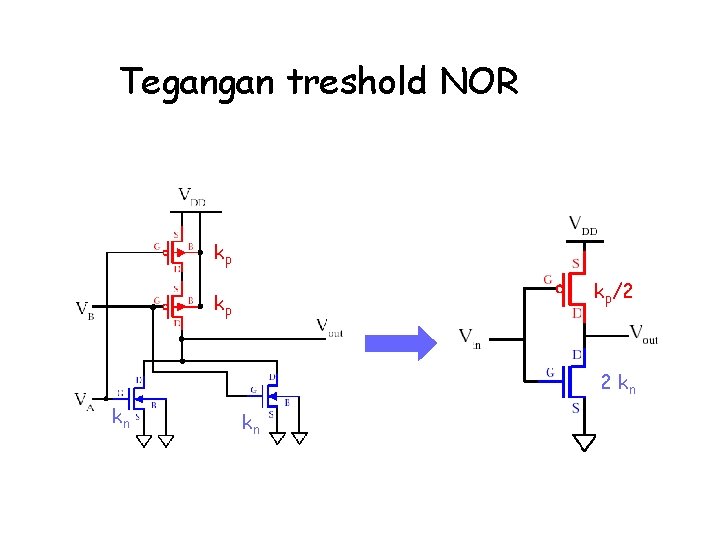

Tegangan treshold NOR kp kp/2 kp 2 kn kn kn

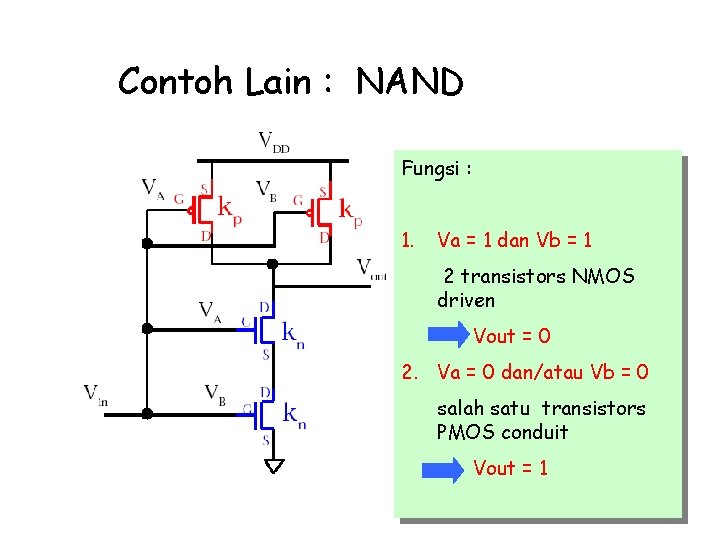

Contoh Lain : NAND Fungsi : 1. Va = 1 dan Vb = 1 2 transistors NMOS driven Vout = 0 2. Va = 0 dan/atau Vb = 0 salah satu transistors PMOS conduit Vout = 1

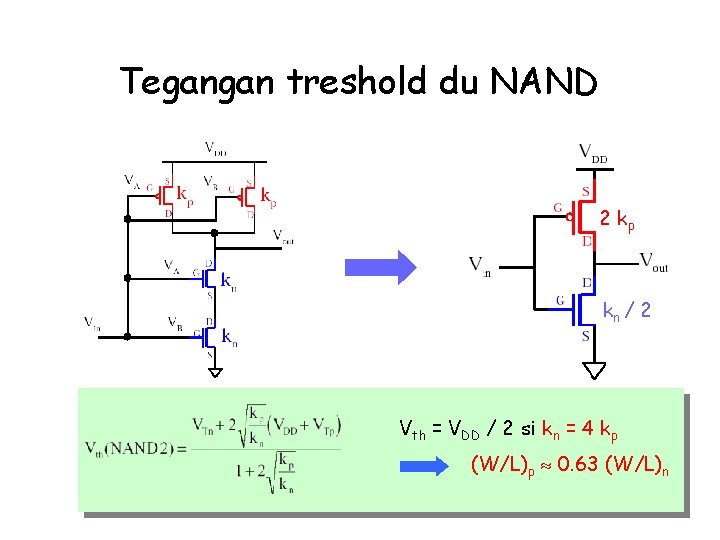

Tegangan treshold du NAND 2 kp kn / 2 Vth = VDD / 2 si kn = 4 kp (W/L)p 0. 63 (W/L)n

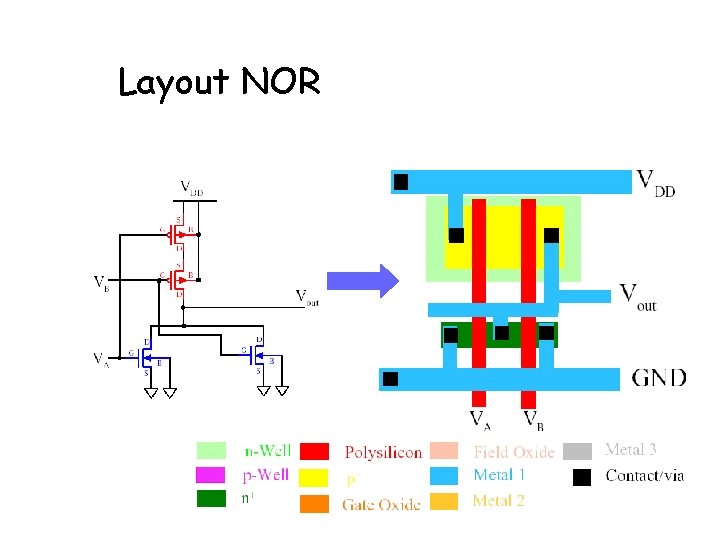

Layout NOR

Layout NAND

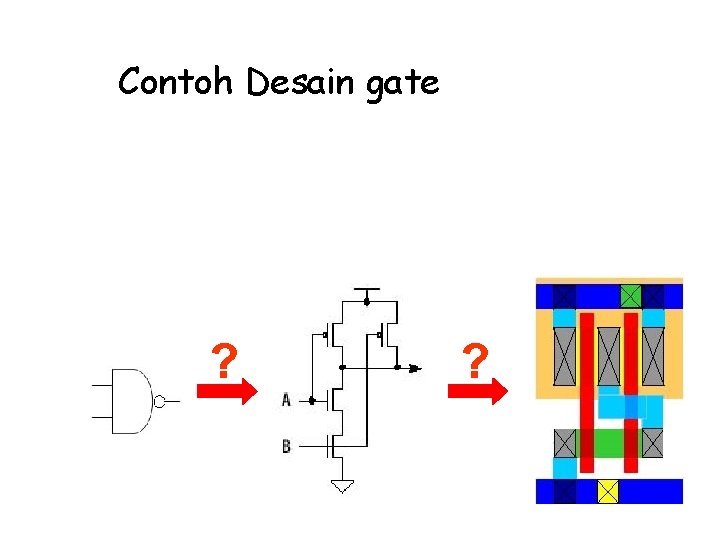

Contoh Desain gate ? ?

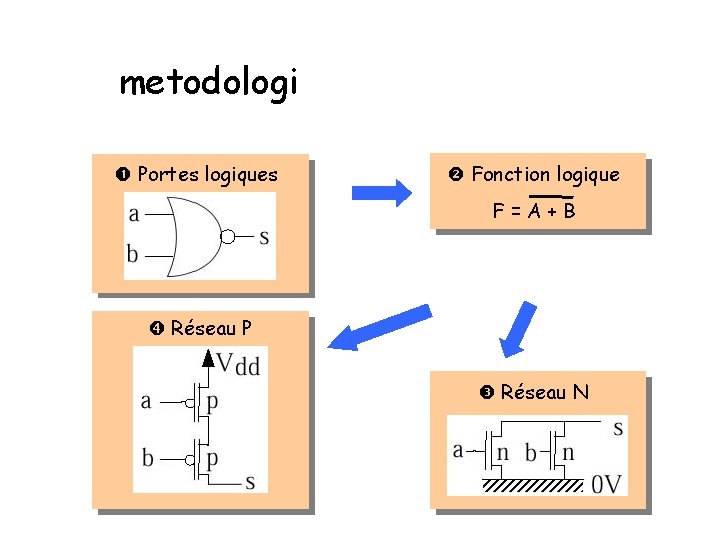

metodologi Portes logiques Fonction logique F=A+B Réseau P Réseau N

metodologi Réseau P Schéma électrique Réseau N

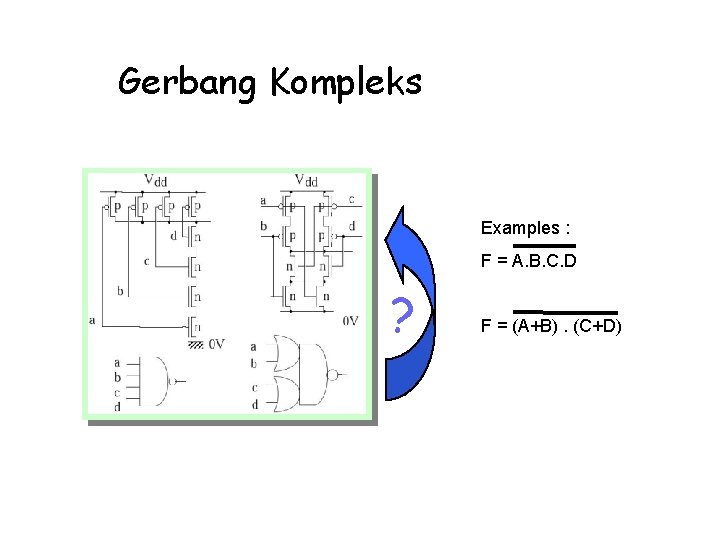

Gerbang Kompleks Examples : F = A. B. C. D ? F = (A+B). (C+D)

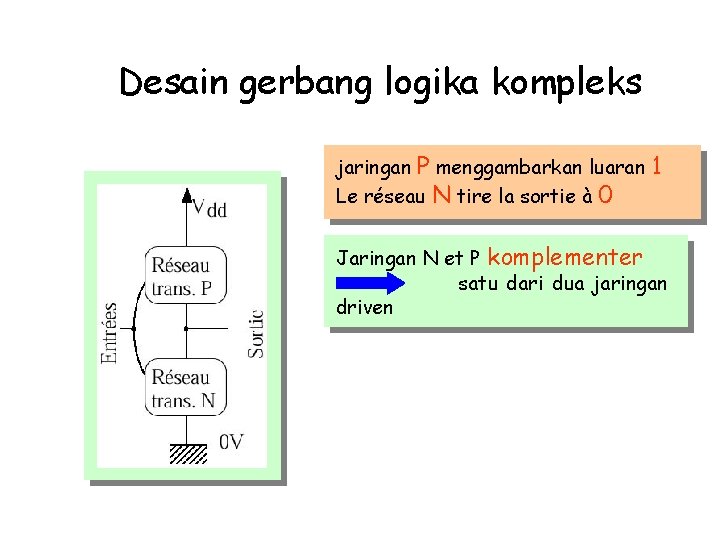

Desain gerbang logika kompleks jaringan P menggambarkan luaran Le réseau N tire la sortie à 0 1 Jaringan N et P komplementer satu dari dua jaringan driven

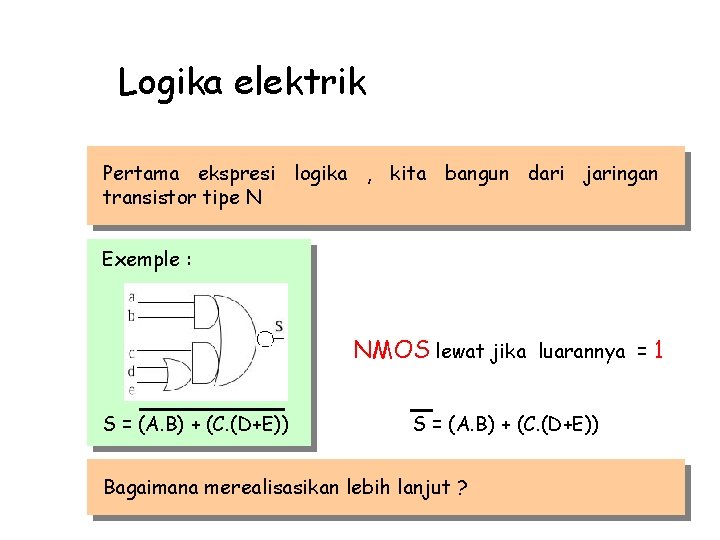

Logika elektrik Pertama ekspresi logika , kita bangun dari jaringan transistor tipe N Exemple : NMOS lewat jika luarannya = 1 S = (A. B) + (C. (D+E)) Bagaimana merealisasikan lebih lanjut ?

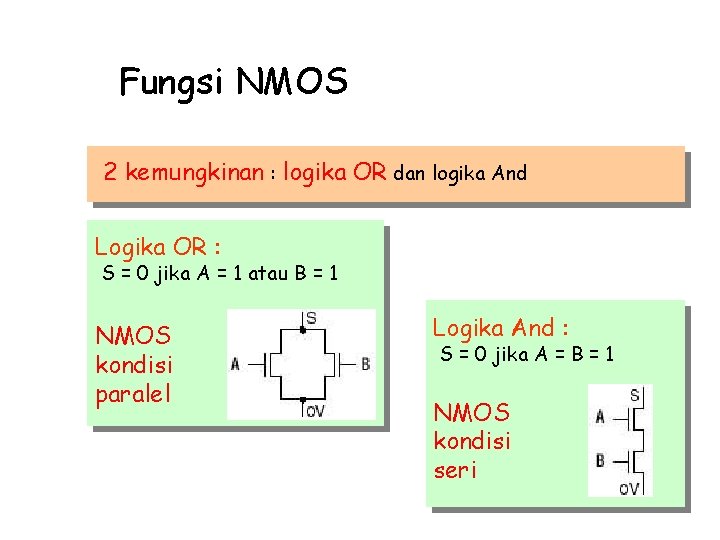

Fungsi NMOS 2 kemungkinan : logika OR dan logika And Logika OR : S = 0 jika A = 1 atau B = 1 NMOS kondisi paralel Logika And : S = 0 jika A = B = 1 NMOS kondisi seri

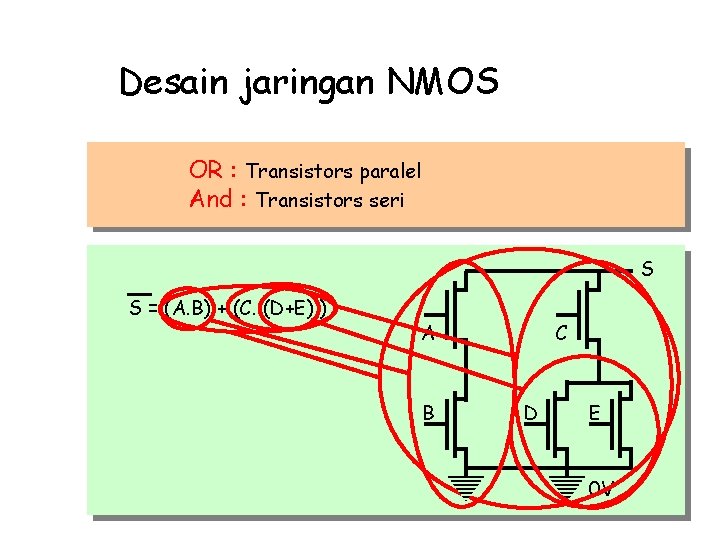

Desain jaringan NMOS OR : Transistors paralel And : Transistors seri S S = (A. B) + (C. (D+E) ) A B C D E 0 V

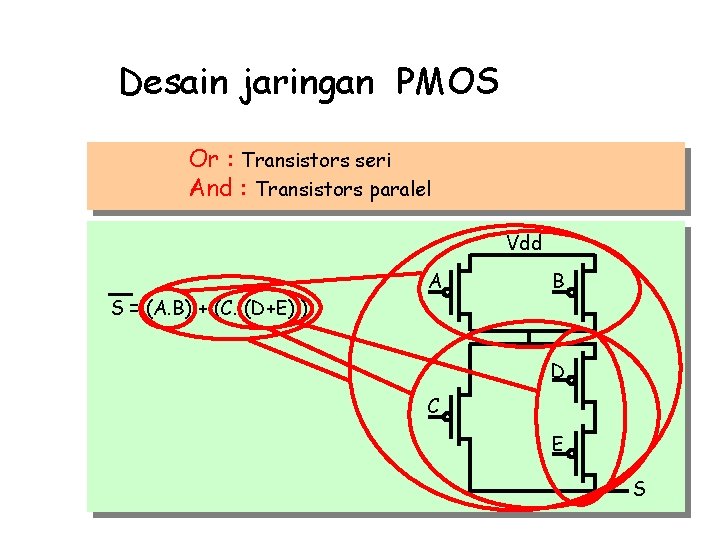

Desain jaringan PMOS Or : Transistors seri And : Transistors paralel Vdd S = (A. B) + (C. (D+E) ) A B D C E S

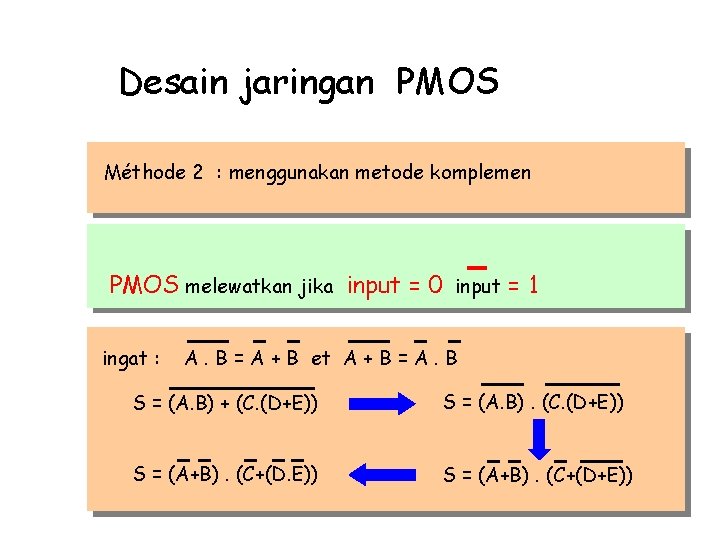

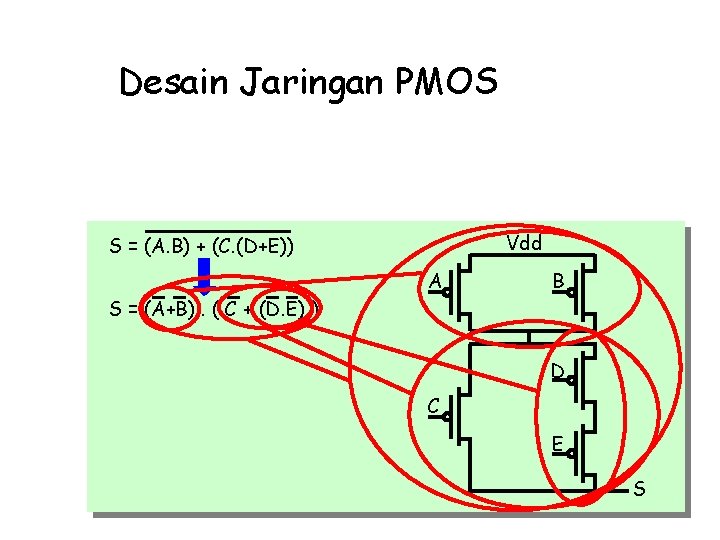

Desain jaringan PMOS Méthode 2 : menggunakan metode komplemen PMOS melewatkan jika input = 0 input = 1 ingat : A. B = A + B et A + B = A. B S = (A. B) + (C. (D+E)) S = (A. B). (C. (D+E)) S = (A+B). (C+(D+E))

Desain Jaringan PMOS Vdd S = (A. B) + (C. (D+E)) S = (A+B). ( C + (D. E) ) A B D C E S

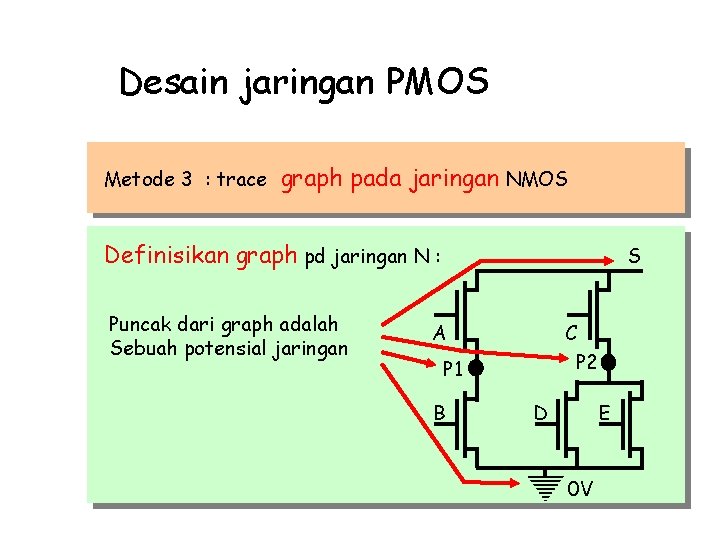

Desain jaringan PMOS Metode 3 : trace graph pada jaringan NMOS Definisikan graph pd jaringan N : Puncak dari graph adalah Sebuah potensial jaringan S A C P 2 P 1 B D E 0 V

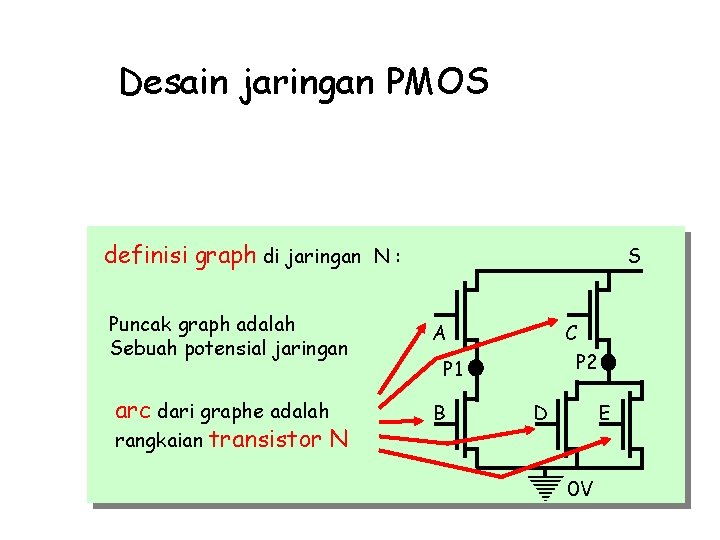

Desain jaringan PMOS definisi graph di jaringan N : S Puncak graph adalah Sebuah potensial jaringan A arc dari graphe adalah rangkaian transistor N B C P 2 P 1 D E 0 V

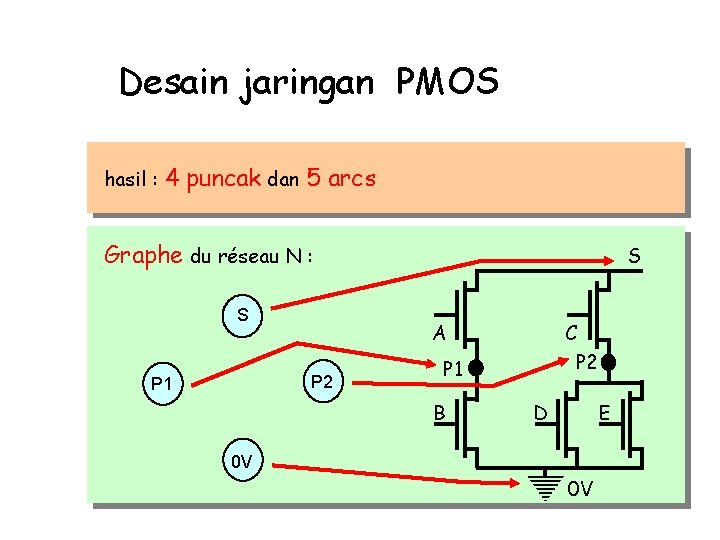

Desain jaringan PMOS hasil : 4 puncak dan 5 arcs Graphe du réseau N : S A P 2 P 1 S C P 2 P 1 B D E 0 V 0 V

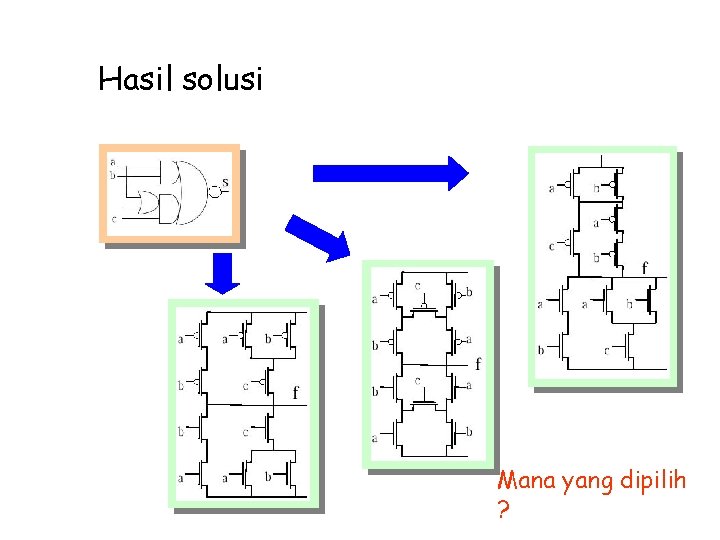

Hasil solusi Mana yang dipilih ?

- Slides: 27