Generic Array Logic GAL GAL is a family

- Slides: 9

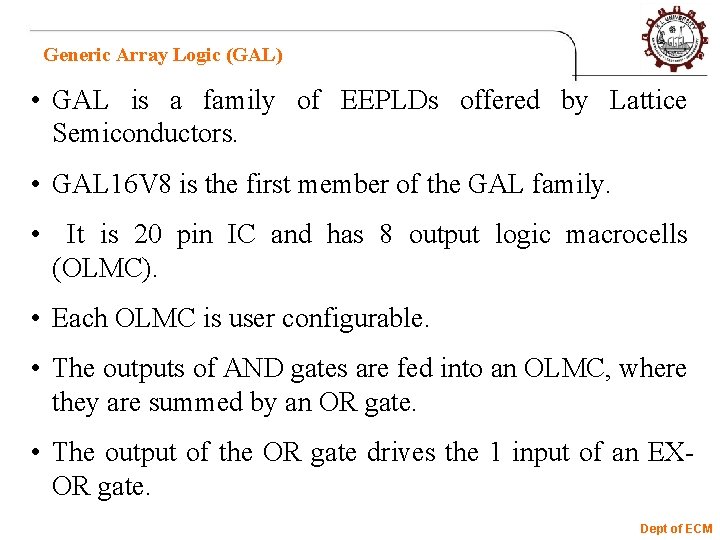

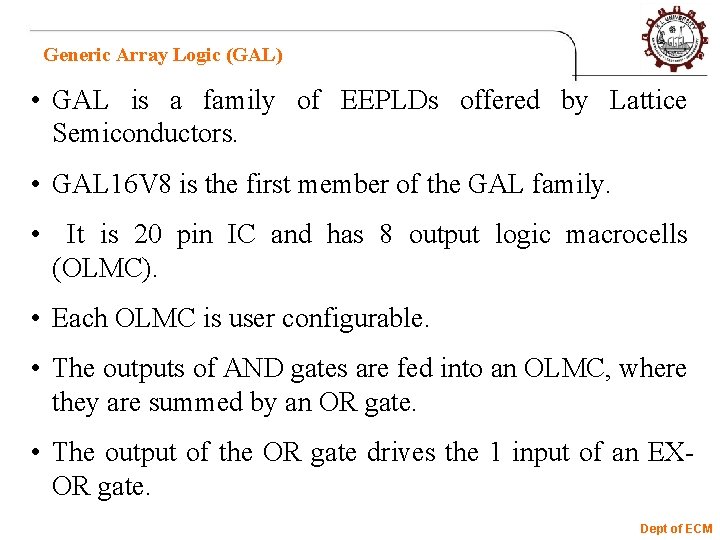

Generic Array Logic (GAL) • GAL is a family of EEPLDs offered by Lattice Semiconductors. • GAL 16 V 8 is the first member of the GAL family. • It is 20 pin IC and has 8 output logic macrocells (OLMC). • Each OLMC is user configurable. • The outputs of AND gates are fed into an OLMC, where they are summed by an OR gate. • The output of the OR gate drives the 1 input of an EXOR gate. Dept of ECM

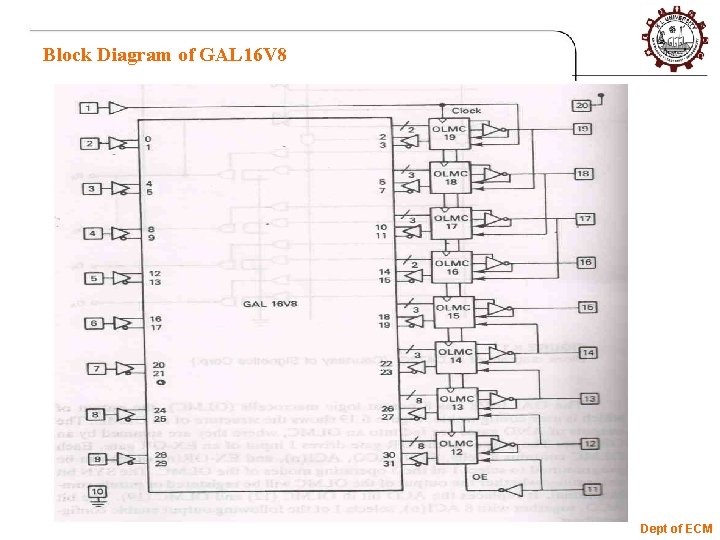

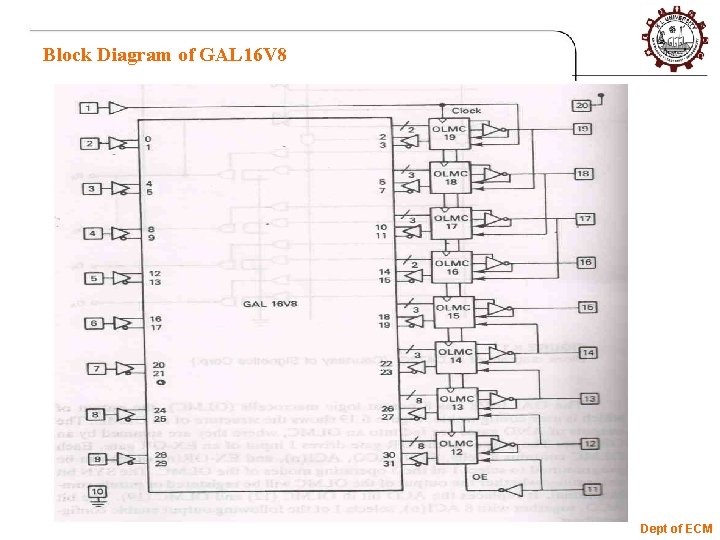

Block Diagram of GAL 16 V 8 Dept of ECM

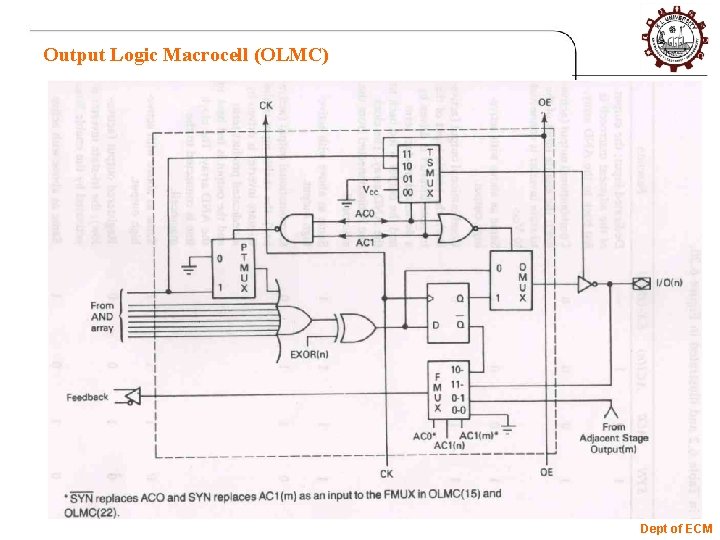

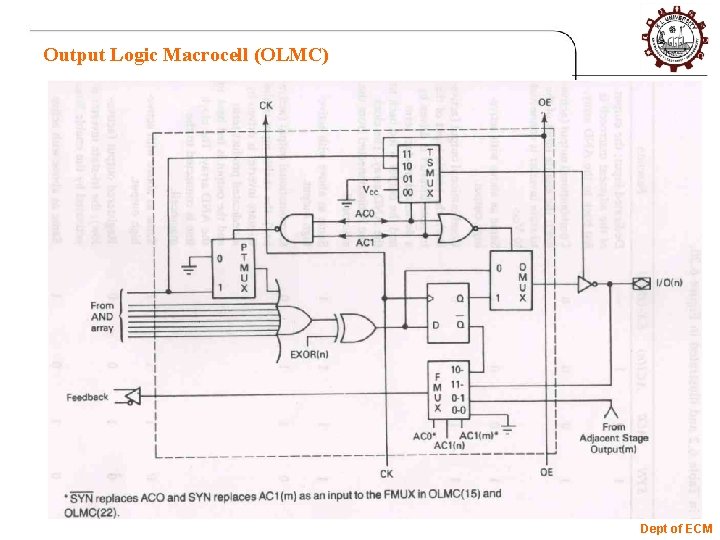

Output Logic Macrocell (OLMC) Dept of ECM

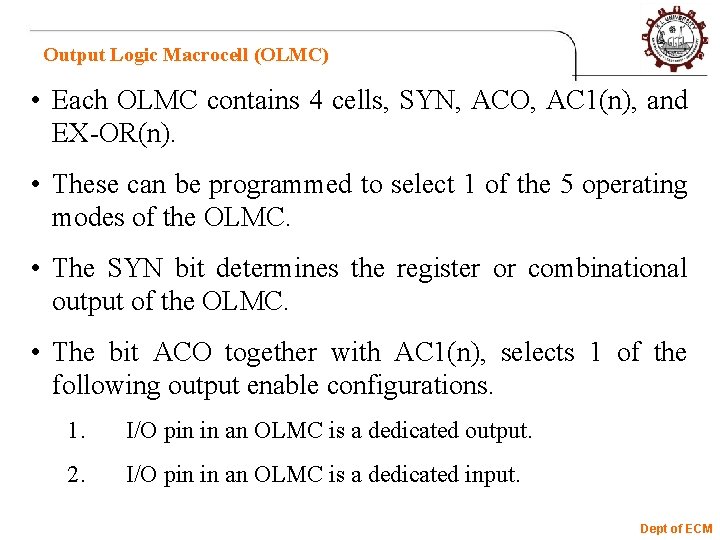

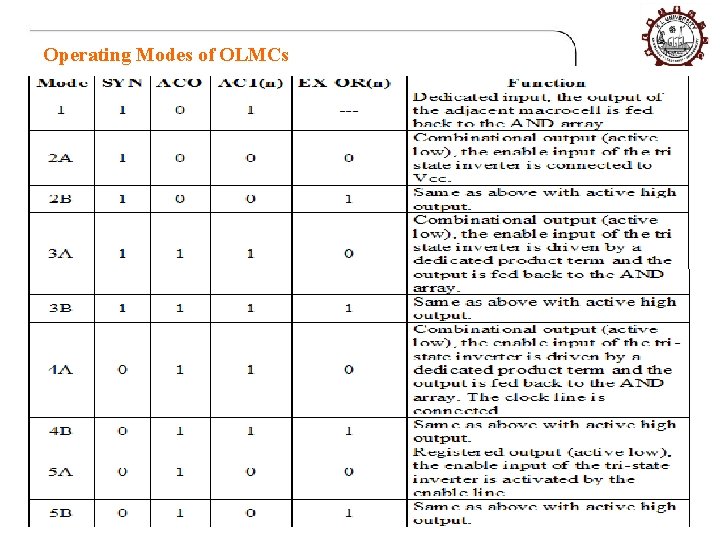

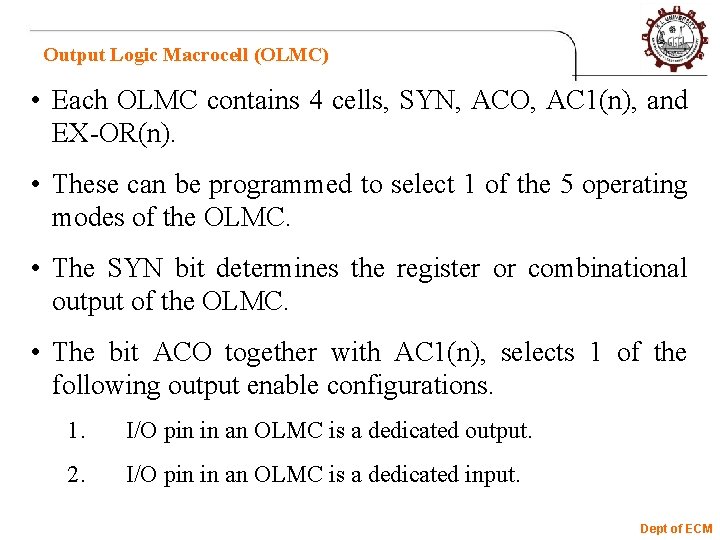

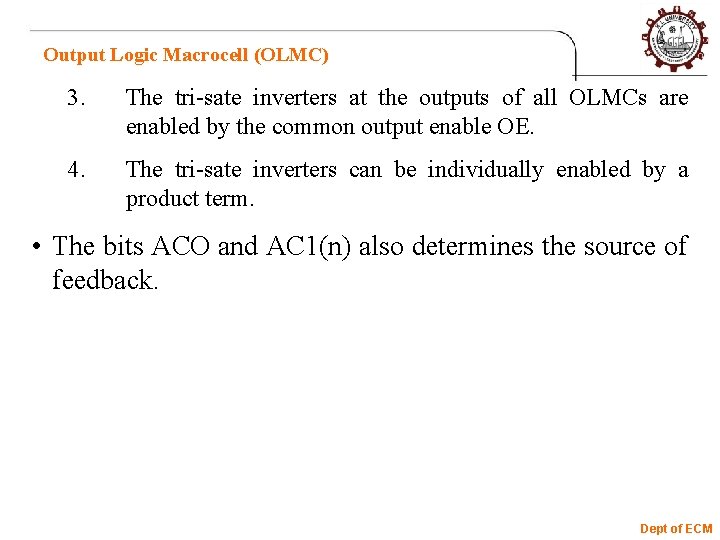

Output Logic Macrocell (OLMC) • Each OLMC contains 4 cells, SYN, ACO, AC 1(n), and EX-OR(n). • These can be programmed to select 1 of the 5 operating modes of the OLMC. • The SYN bit determines the register or combinational output of the OLMC. • The bit ACO together with AC 1(n), selects 1 of the following output enable configurations. 1. I/O pin in an OLMC is a dedicated output. 2. I/O pin in an OLMC is a dedicated input. Dept of ECM

Output Logic Macrocell (OLMC) 3. The tri-sate inverters at the outputs of all OLMCs are enabled by the common output enable OE. 4. The tri-sate inverters can be individually enabled by a product term. • The bits ACO and AC 1(n) also determines the source of feedback. Dept of ECM

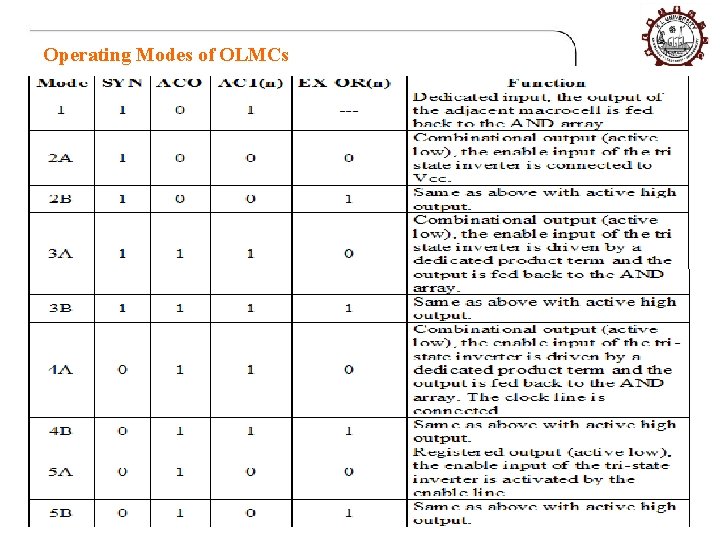

Operating Modes of OLMCs Dept of ECM

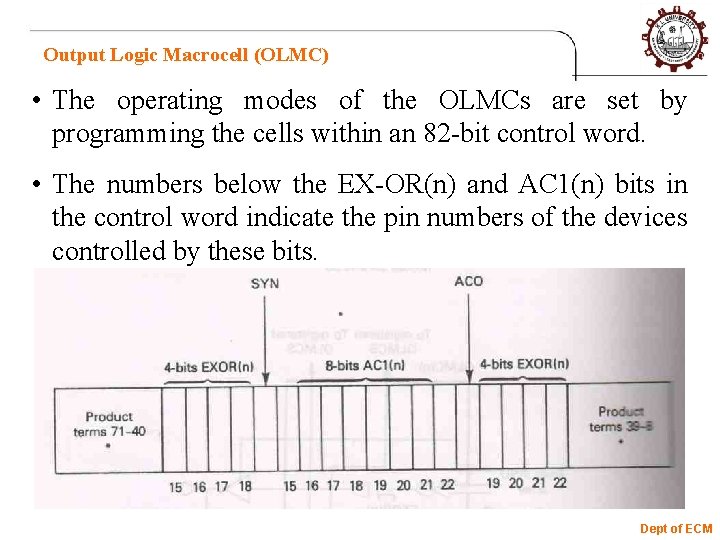

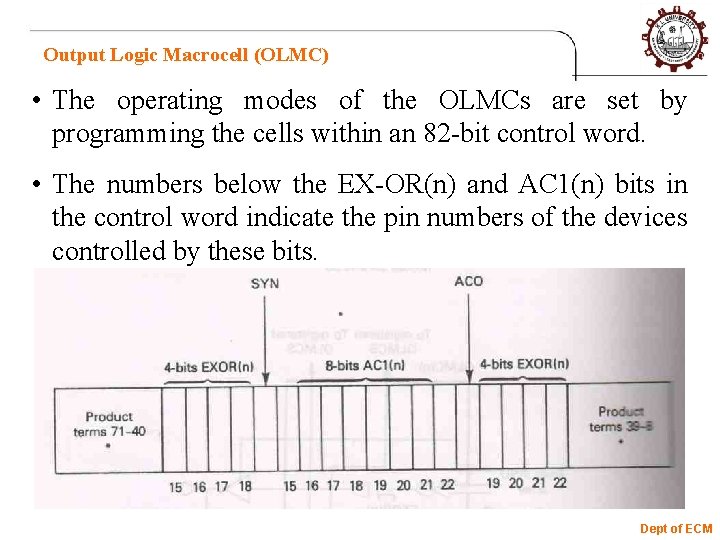

Output Logic Macrocell (OLMC) • The operating modes of the OLMCs are set by programming the cells within an 82 -bit control word. • The numbers below the EX-OR(n) and AC 1(n) bits in the control word indicate the pin numbers of the devices controlled by these bits. Dept of ECM

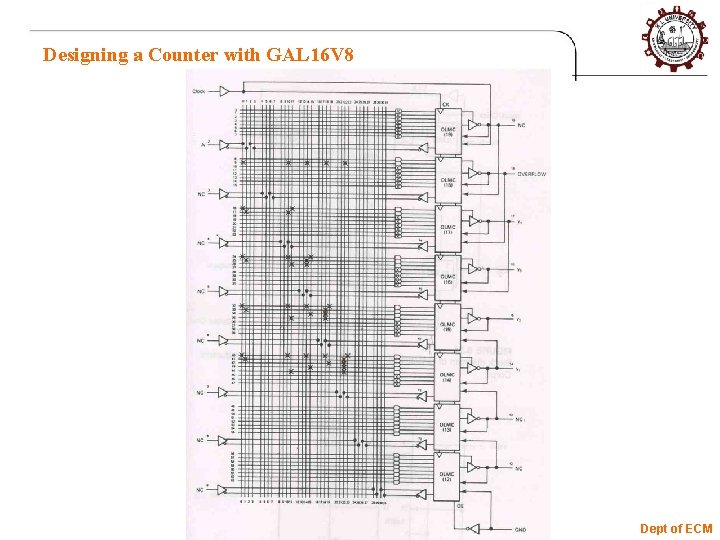

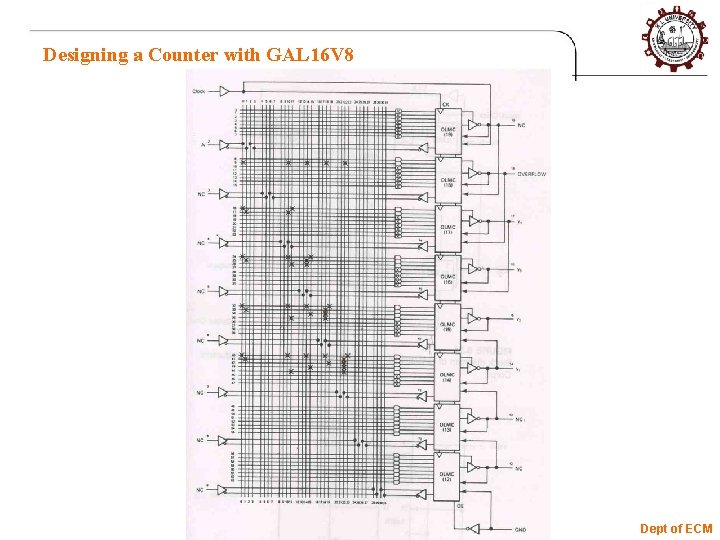

Designing a Counter with GAL 16 V 8 • Design a 4 -bit binary counter using GAL 16 V 8. The input to the counter is A, the count value is incremented if A = 1, and decremented if A = 0. The counter generates an overflow if the input A is made ‘ 1’ after a count of all 1’s and is reset to its initial states on the next clock pulse. Dept of ECM

Designing a Counter with GAL 16 V 8 Dept of ECM