Generating the Rectify code C and assembly code

Generating the “Rectify” code (C++ and assembly code) Prelaboratory assignment information Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada

Concepts n Concepts of C++ “stubs” n Forcing the test to fail n Generating valid “C++ code” to satisfy the tests n Need for “name mangling” for overloaded functions n How do you find out the name mangled name so it can be used in assembly code n Learning just enough Tiger. SHARC assembly code to make things “work” 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 2

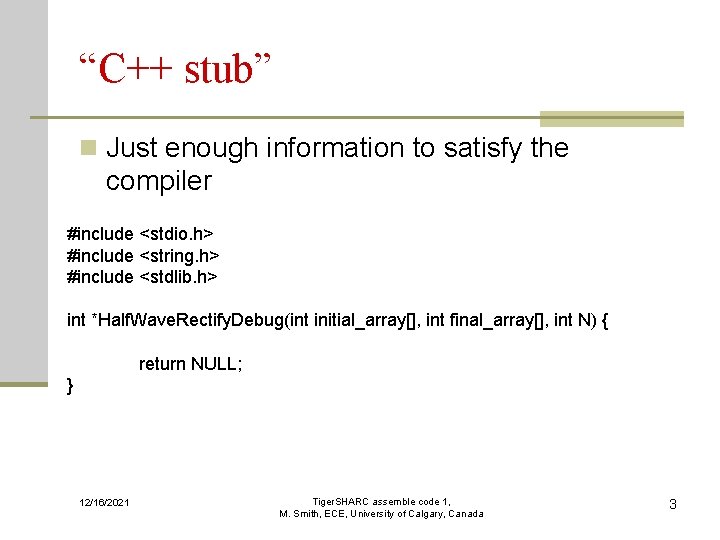

“C++ stub” n Just enough information to satisfy the compiler #include <stdio. h> #include <string. h> #include <stdlib. h> int *Half. Wave. Rectify. Debug(int initial_array[], int final_array[], int N) { return NULL; } 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 3

Integer rectify – force the tests to fail --- Test of the test 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 4

Passing integer rectify 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 5

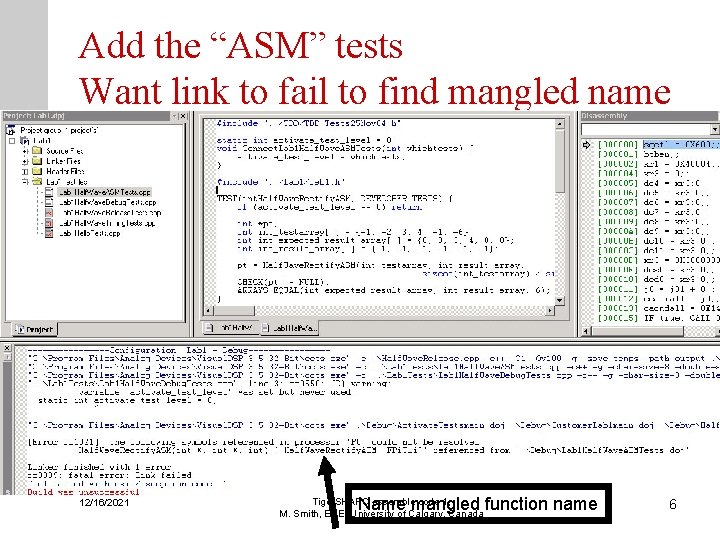

Add the “ASM” tests Want link to fail to find mangled name 12/16/2021 Name mangled function name Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 6

Generate assembly code n Do the code in steps, attempting to satisfy one test at a time n Learn “the assembler” in steps n Get “some idea” of the issues we need to learn about as we go along n Just enough knowledge “to get things to work” n Worry about full details later 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 7

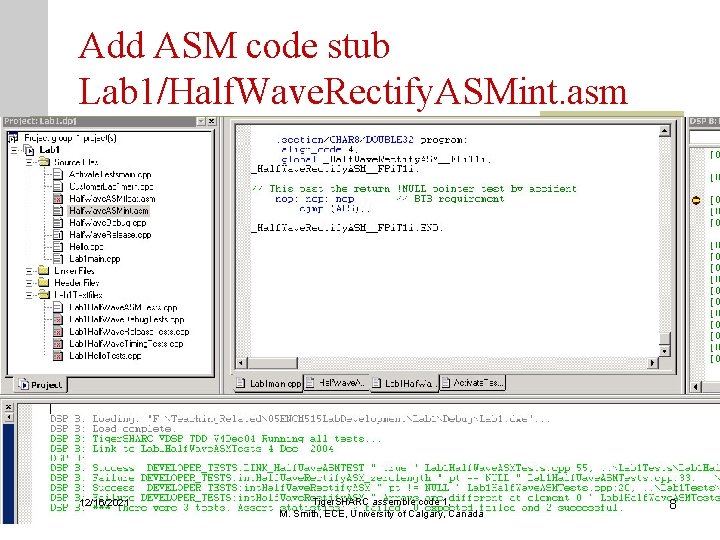

Add ASM code stub Lab 1/Half. Wave. Rectify. ASMint. asm 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 8

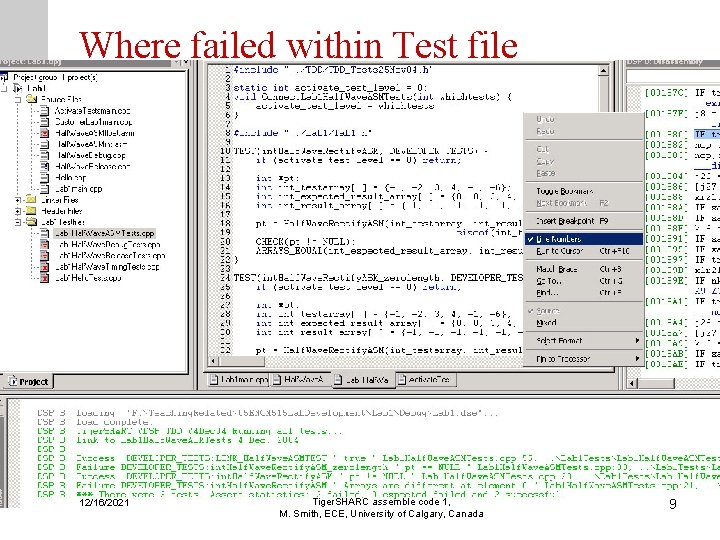

Where failed within Test file 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 9

What we have learned n We passed the “very general” test Managed to call and return from an assembly code and did not crash the system n We passed some specific tests in the test file “by accident” n Which tests and why did they pass? n n CJUMP – is the “way to return” from an assembly code function to “C++” n Instruction format is interesting nop; ; ; separate instructions executed together cjump; ; indicates the end of an “grouped” instruction When jumps are involved, Tiger. SHARC seems to prefer code that involves “four 32 -bit instruction: because of “BTB requirement” 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 10

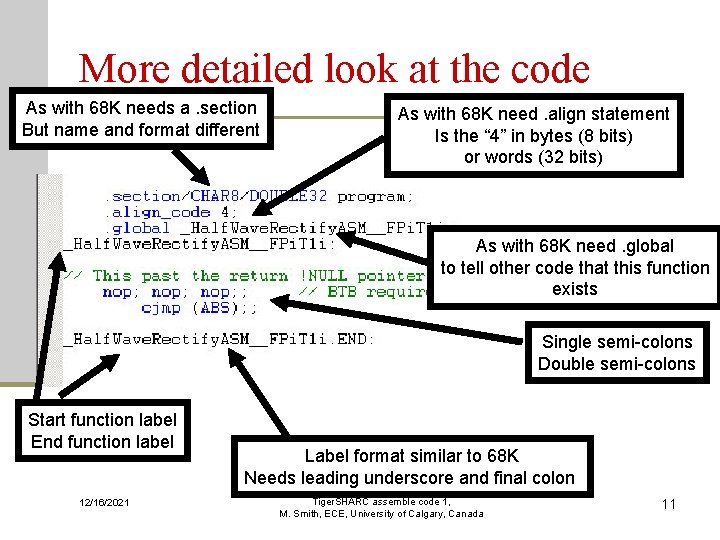

More detailed look at the code As with 68 K needs a. section But name and format different As with 68 K need. align statement Is the “ 4” in bytes (8 bits) or words (32 bits) As with 68 K need. global to tell other code that this function exists Single semi-colons Double semi-colons Start function label End function label 12/16/2021 Label format similar to 68 K Needs leading underscore and final colon Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 11

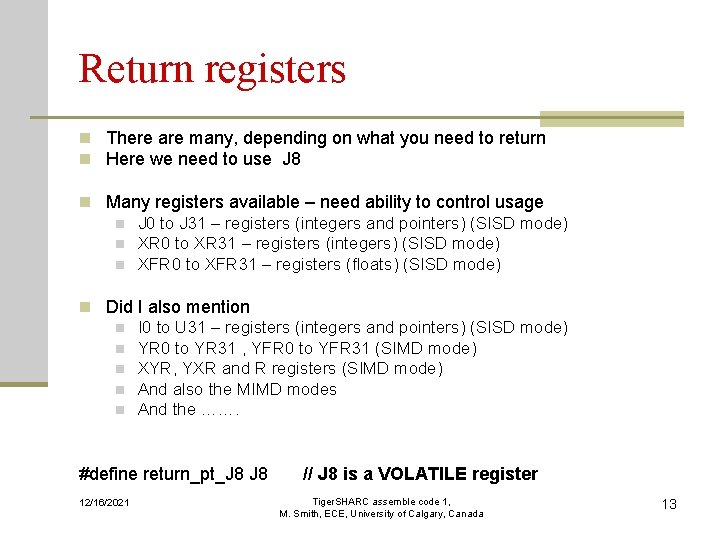

Need to know n How do we return “an integer pointer” n Need to look at “C++” manual for coding conventions n As with 68 K expect to have n Volatile registers – function variate registers, that DON’T need to be conserved n Non-volatile registers – function invariate registers, that DO need to be conserved 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 12

Return registers n There are many, depending on what you need to return n Here we need to use J 8 n Many registers available – need ability to control usage n J 0 to J 31 – registers (integers and pointers) (SISD mode) n XR 0 to XR 31 – registers (integers) (SISD mode) n XFR 0 to XFR 31 – registers (floats) (SISD mode) n Did I also mention n I 0 to U 31 – registers (integers and pointers) (SISD mode) n YR 0 to YR 31 , YFR 0 to YFR 31 (SIMD mode) n XYR, YXR and R registers (SIMD mode) n And also the MIMD modes n And the ……. #define return_pt_J 8 12/16/2021 // J 8 is a VOLATILE register Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 13

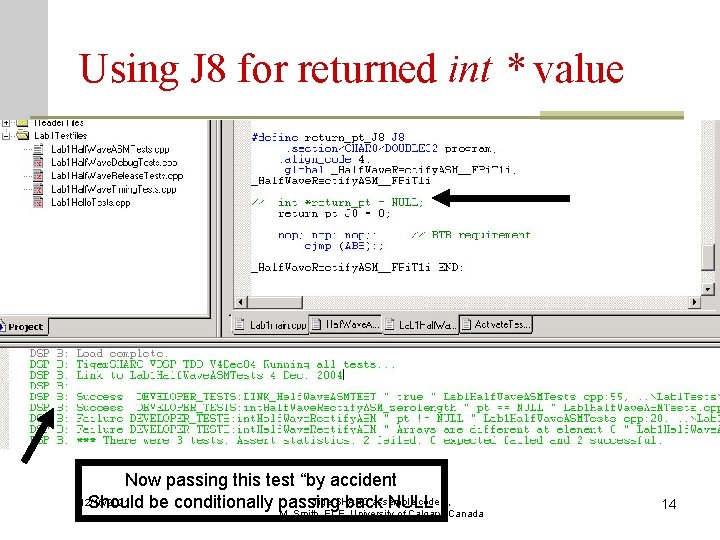

Using J 8 for returned int * value Now passing this test “by accident Tiger. SHARC assemble code 1, 12/16/2021 Should be conditionally passing back NULL M. Smith, ECE, University of Calgary, Canada 14

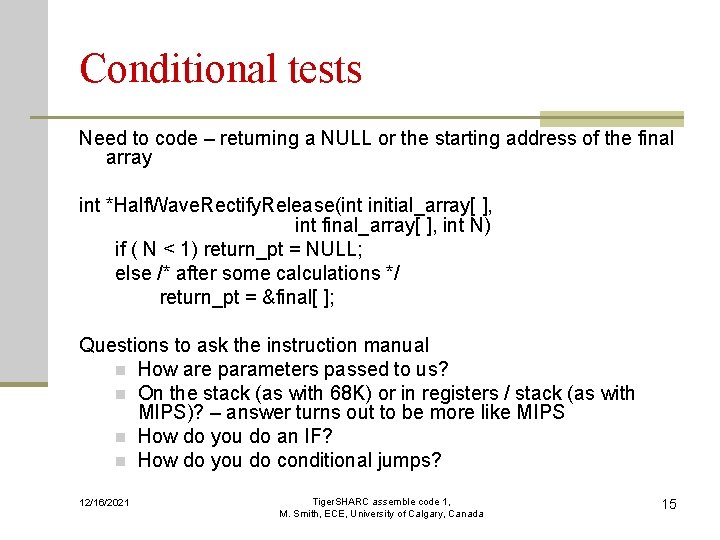

Conditional tests Need to code – returning a NULL or the starting address of the final array int *Half. Wave. Rectify. Release(int initial_array[ ], int final_array[ ], int N) if ( N < 1) return_pt = NULL; else /* after some calculations */ return_pt = &final[ ]; Questions to ask the instruction manual n How are parameters passed to us? n On the stack (as with 68 K) or in registers / stack (as with MIPS)? – answer turns out to be more like MIPS n How do you do an IF? n How do you do conditional jumps? 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 15

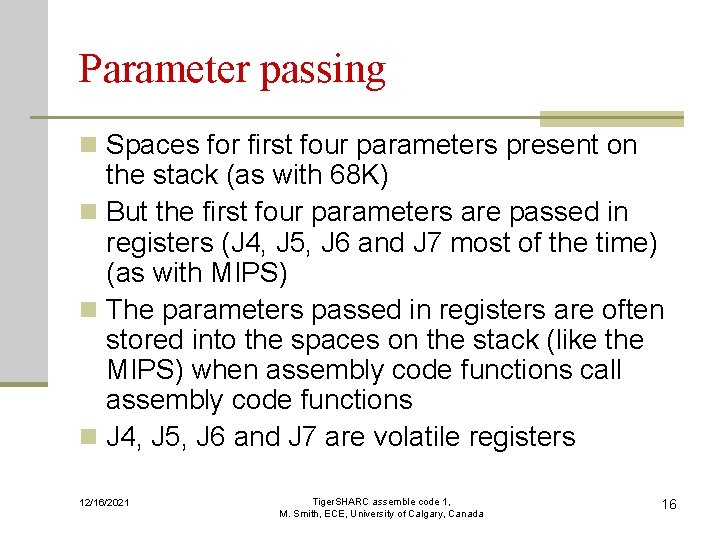

Parameter passing n Spaces for first four parameters present on the stack (as with 68 K) n But the first four parameters are passed in registers (J 4, J 5, J 6 and J 7 most of the time) (as with MIPS) n The parameters passed in registers are often stored into the spaces on the stack (like the MIPS) when assembly code functions call assembly code functions n J 4, J 5, J 6 and J 7 are volatile registers 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 16

![Coding convention // int *Half. Wave. Rectify. Release(int initial_array[ ], // int final_array[ ], Coding convention // int *Half. Wave. Rectify. Release(int initial_array[ ], // int final_array[ ],](http://slidetodoc.com/presentation_image_h2/0f857a266a5fad6df242ae4be23d7f41/image-17.jpg)

Coding convention // int *Half. Wave. Rectify. Release(int initial_array[ ], // int final_array[ ], int N) #define initial_pt_inpar 1 #define final_pt_inpar 2 #define M_J 6_inpar 3 #define return_pt_J 8 12/16/2021 J 4 J 5 J 6 J 8 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 17

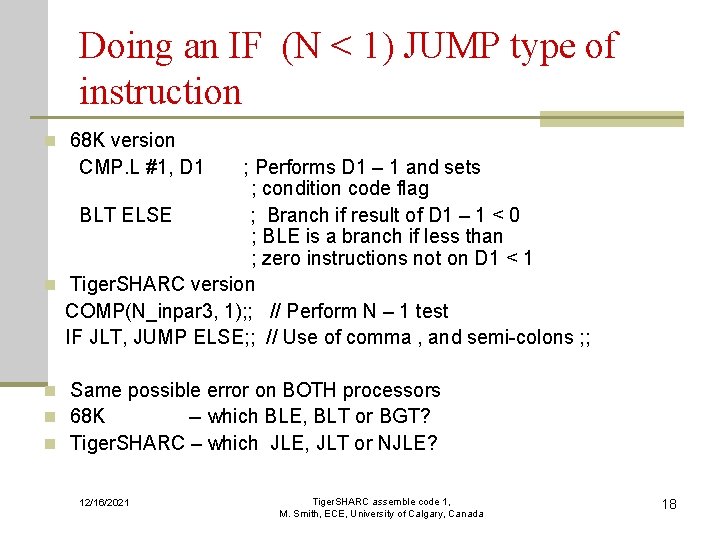

Doing an IF (N < 1) JUMP type of instruction n 68 K version CMP. L #1, D 1 ; Performs D 1 – 1 and sets ; condition code flag BLT ELSE ; Branch if result of D 1 – 1 < 0 ; BLE is a branch if less than ; zero instructions not on D 1 < 1 n Tiger. SHARC version COMP(N_inpar 3, 1); ; // Perform N – 1 test IF JLT, JUMP ELSE; ; // Use of comma , and semi-colons ; ; n Same possible error on BOTH processors n 68 K -- which BLE, BLT or BGT? n Tiger. SHARC – which JLE, JLT or NJLE? 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 18

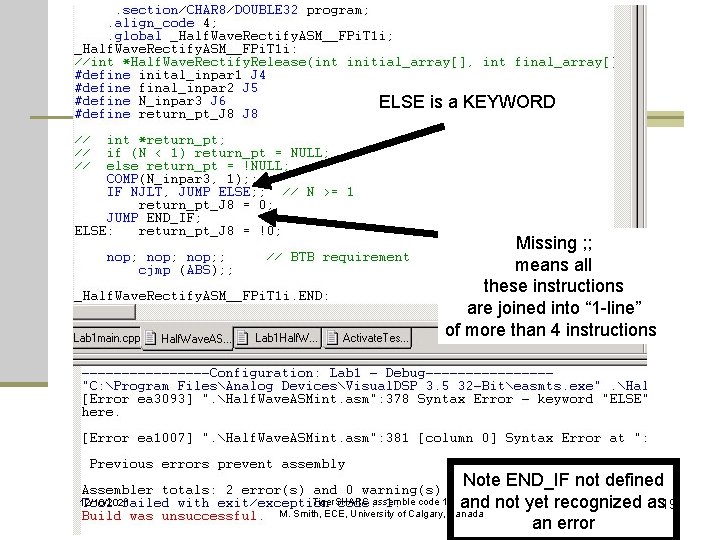

ELSE is a KEYWORD Missing ; ; means all these instructions are joined into “ 1 -line” of more than 4 instructions 12/16/2021 Note END_IF not defined Tiger. SHARC assemble code 1, and not yet recognized as 19 M. Smith, ECE, University of Calgary, Canada an error

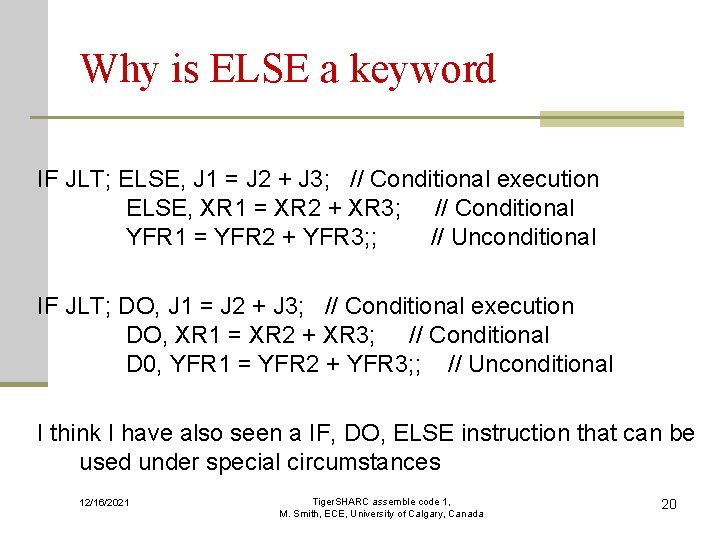

Why is ELSE a keyword IF JLT; ELSE, J 1 = J 2 + J 3; // Conditional execution ELSE, XR 1 = XR 2 + XR 3; // Conditional YFR 1 = YFR 2 + YFR 3; ; // Unconditional IF JLT; DO, J 1 = J 2 + J 3; // Conditional execution DO, XR 1 = XR 2 + XR 3; // Conditional D 0, YFR 1 = YFR 2 + YFR 3; ; // Unconditional I think I have also seen a IF, DO, ELSE instruction that can be used under special circumstances 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 20

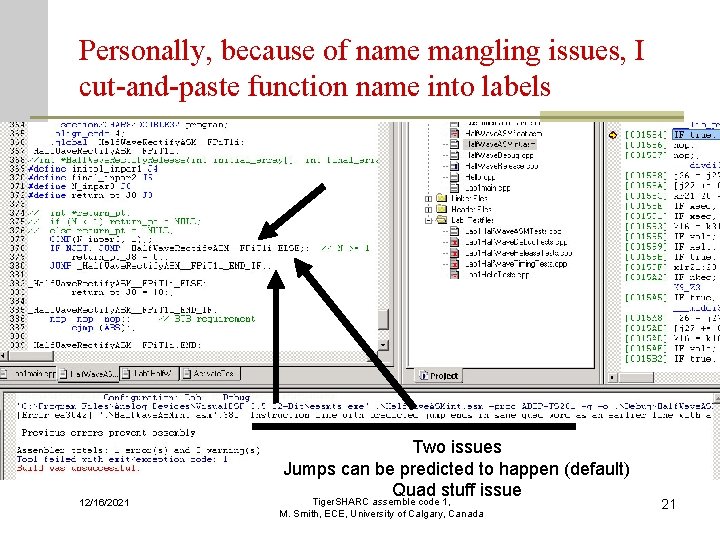

Personally, because of name mangling issues, I cut-and-paste function name into labels 12/16/2021 Two issues Jumps can be predicted to happen (default) Quad stuff issue Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 21

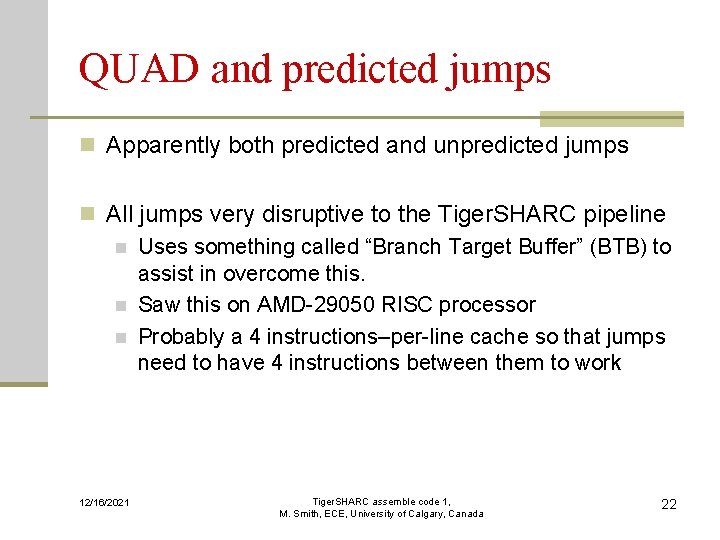

QUAD and predicted jumps n Apparently both predicted and unpredicted jumps n All jumps very disruptive to the Tiger. SHARC pipeline n Uses something called “Branch Target Buffer” (BTB) to assist in overcome this. n Saw this on AMD-29050 RISC processor n Probably a 4 instructions–per-line cache so that jumps need to have 4 instructions between them to work 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 22

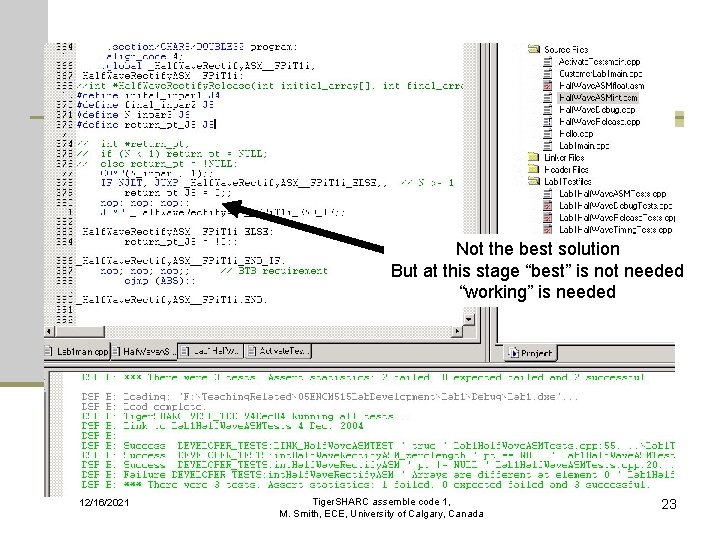

Not the best solution But at this stage “best” is not needed “working” is needed 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 23

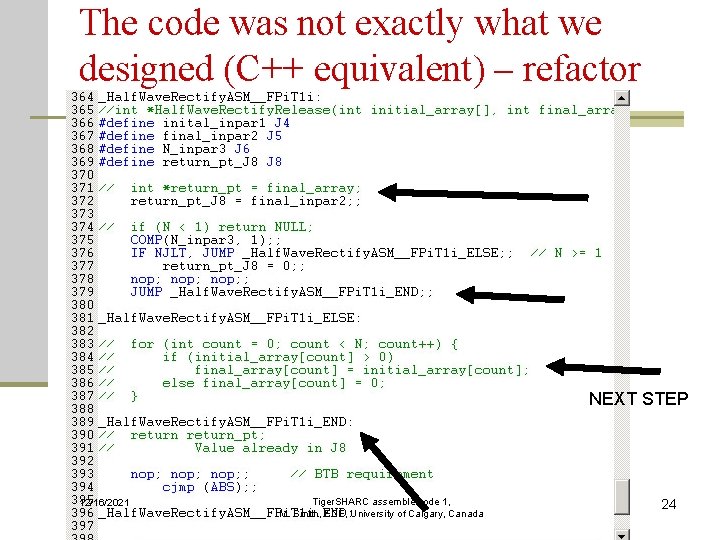

The code was not exactly what we designed (C++ equivalent) – refactor and retest after the refactoring NEXT STEP 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 24

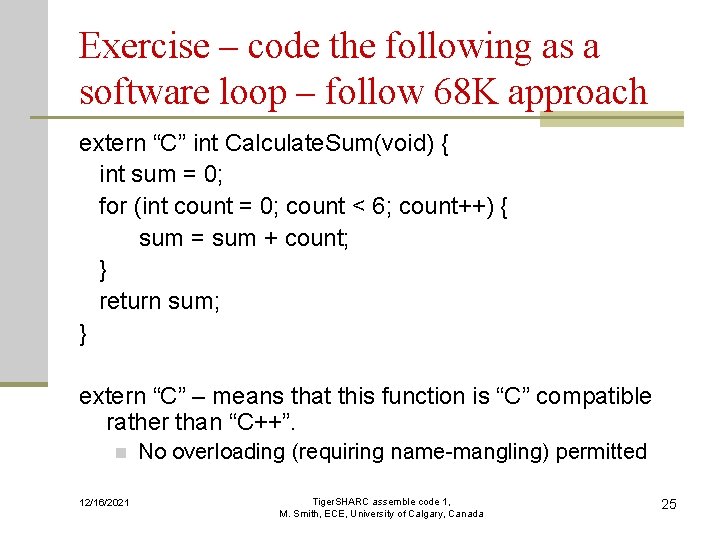

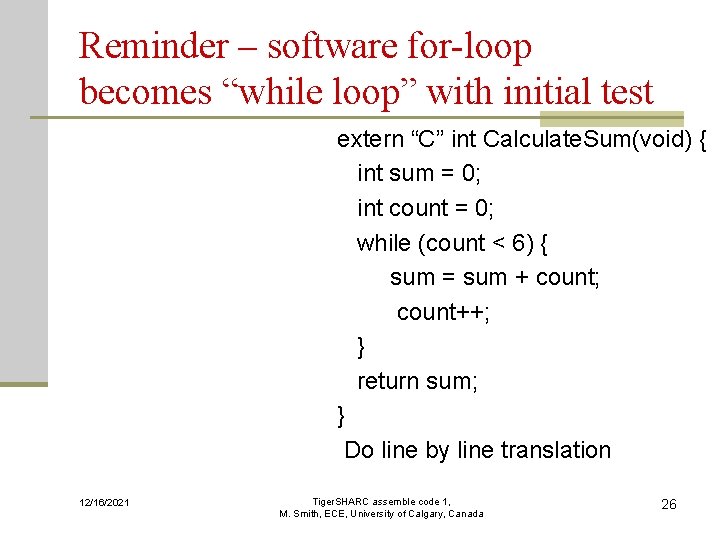

Exercise – code the following as a software loop – follow 68 K approach extern “C” int Calculate. Sum(void) { int sum = 0; for (int count = 0; count < 6; count++) { sum = sum + count; } return sum; } extern “C” – means that this function is “C” compatible rather than “C++”. n 12/16/2021 No overloading (requiring name-mangling) permitted Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 25

Reminder – software for-loop becomes “while loop” with initial test extern “C” int Calculate. Sum(void) { int sum = 0; int count = 0; while (count < 6) { sum = sum + count; count++; } return sum; } Do line by line translation 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 26

Concepts n Concepts of C++ “stubs” n Forcing the test to fail n Generating valid “C++ code” to satisfy the tests n Need for “name mangling” for overloaded functions n How do you find out the name mangled name so it can be used in assembly code n Learning just enough Tiger. SHARC assembly code to make things “work” 12/16/2021 Tiger. SHARC assemble code 1, M. Smith, ECE, University of Calgary, Canada 27

- Slides: 27