Generate Statement A generate statement provides a mechanism

![generate-label: for generale-identifierin discrete-range generate concurrent-statements end generate [ generate-label]; generate-label: for generale-identifierin discrete-range generate concurrent-statements end generate [ generate-label];](https://slidetodoc.com/presentation_image_h/09486e1663d62b824fb89b921866ab5a/image-5.jpg)

![the if-generation scheme. genarate-label: if expression generate concurrent-statements end generate [ generete-label ] ; the if-generation scheme. genarate-label: if expression generate concurrent-statements end generate [ generete-label ] ;](https://slidetodoc.com/presentation_image_h/09486e1663d62b824fb89b921866ab5a/image-8.jpg)

![Block Syntax (Simple) Label : BLOCK [Declartive part] Begin (Concurrent statements) End BLOCK label; Block Syntax (Simple) Label : BLOCK [Declartive part] Begin (Concurrent statements) End BLOCK label;](https://slidetodoc.com/presentation_image_h/09486e1663d62b824fb89b921866ab5a/image-13.jpg)

![Guarded Block syntax Label : BLOCK (guard expression) [Declarative part] Begin (Concurrent guarded and Guarded Block syntax Label : BLOCK (guard expression) [Declarative part] Begin (Concurrent guarded and](https://slidetodoc.com/presentation_image_h/09486e1663d62b824fb89b921866ab5a/image-15.jpg)

- Slides: 17

Generate Statement • A generate statement provides a mechanism for iterative or conditional elaboration of a portion of description. • The iterative elaboration of a description is a convenient mechanism to instantiate and replicate concurrent statements. • The replication index is either a constant or a generic. • This is often used to instantiate and connect components.

Generate Statement(Cont. ) • The conditional elaboration enables the conditional instantiation of a concurrent statement usually based on a constant or a generic. • This is often used to conditionally instantiate a component or a concurrent procedure.

Generate • It is equivalent to the sequential statement LOOP. • It allows a section of code to be repeated a number of times, thus creating several instances of the same assignments.

There are two forms of the generate statement. 1. Using the for-generate scheme, concurrent statements can be replicated a predetermined number of times. 2. With the if-generation scheme, concurrent statements can be conditionally selected for execution.

![generatelabel for generaleidentifierin discreterange generate concurrentstatements end generate generatelabel generate-label: for generale-identifierin discrete-range generate concurrent-statements end generate [ generate-label];](https://slidetodoc.com/presentation_image_h/09486e1663d62b824fb89b921866ab5a/image-5.jpg)

generate-label: for generale-identifierin discrete-range generate concurrent-statements end generate [ generate-label];

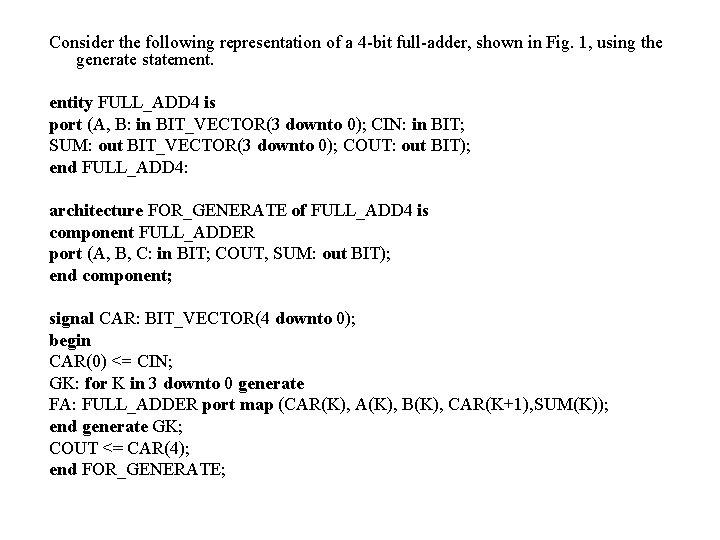

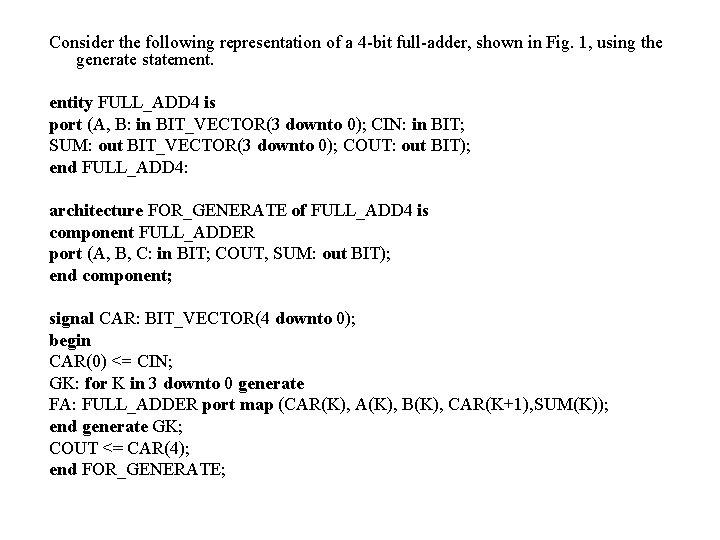

Consider the following representation of a 4 -bit full-adder, shown in Fig. 1, using the generate statement. entity FULL_ADD 4 is port (A, B: in BIT_VECTOR(3 downto 0); CIN: in BIT; SUM: out BIT_VECTOR(3 downto 0); COUT: out BIT); end FULL_ADD 4: architecture FOR_GENERATE of FULL_ADD 4 is component FULL_ADDER port (A, B, C: in BIT; COUT, SUM: out BIT); end component; signal CAR: BIT_VECTOR(4 downto 0); begin CAR(0) <= CIN; GK: for K in 3 downto 0 generate FA: FULL_ADDER port map (CAR(K), A(K), B(K), CAR(K+1), SUM(K)); end generate GK; COUT <= CAR(4); end FOR_GENERATE;

After elaboration, the generate statement is expanded to FA(3): FULL_ADDER port map (CAR(3), A(3), B(3), CAR(4), SUM(3)); FA(2): FULL_ADDER port map (CAR(2), A(2), B(2), CAR(3), SUM(2)); FA(1): FULL_ADDER port map (CAR(1), A(1), B(1), CAR(2), SUM(1)); FA(0): FULL_ADDER port map (CAR(0), A(0), B(0), CAR(1), SUM(0));

![the ifgeneration scheme genaratelabel if expression generate concurrentstatements end generate generetelabel the if-generation scheme. genarate-label: if expression generate concurrent-statements end generate [ generete-label ] ;](https://slidetodoc.com/presentation_image_h/09486e1663d62b824fb89b921866ab5a/image-8.jpg)

the if-generation scheme. genarate-label: if expression generate concurrent-statements end generate [ generete-label ] ;

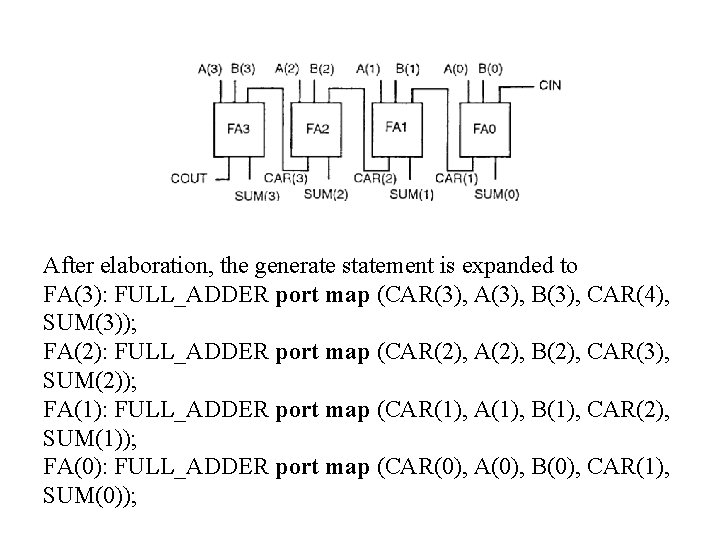

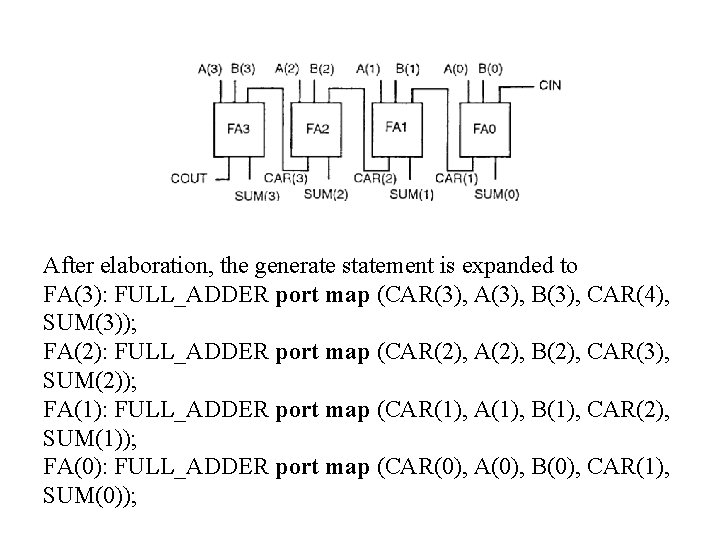

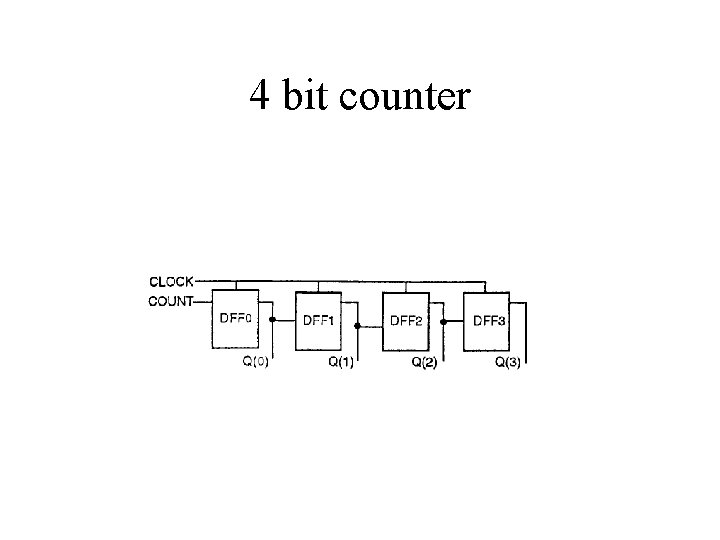

entity COUNTER 4 is port (COUNT, CLOCK: in BIT; Q: buffer BIT_VECTOR(0 to 3)); end COUNTER 4; architecture IF_GENERATE of COUNTER 4 is component D_FLIP_FLOP port (D, CLK: in BIT; Q: out BIT); end component; begin GK: for K in 0 to 3 generate GKO: if K = 0 generate DFF: D_FLIP_FLOP port map (COUNT, CLOCK, Q(K)); end generate GK 0; GK 1_3: if K > 0 generate DFF: D_FLIP_FLOP port map (Q(K-1), CLOCK, Q(K)); end generate GK 1_3; end generate GK; end IF_GENERATE;

4 bit counter

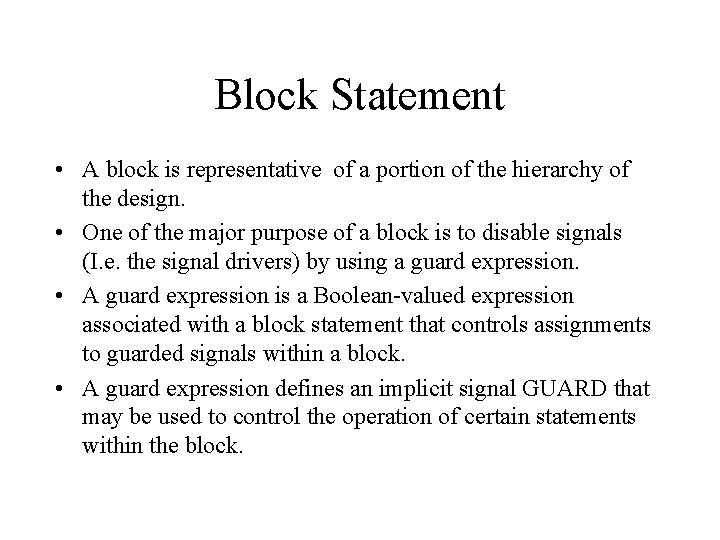

Block Statement • A block is representative of a portion of the hierarchy of the design. • One of the major purpose of a block is to disable signals (I. e. the signal drivers) by using a guard expression. • A guard expression is a Boolean-valued expression associated with a block statement that controls assignments to guarded signals within a block. • A guard expression defines an implicit signal GUARD that may be used to control the operation of certain statements within the block.

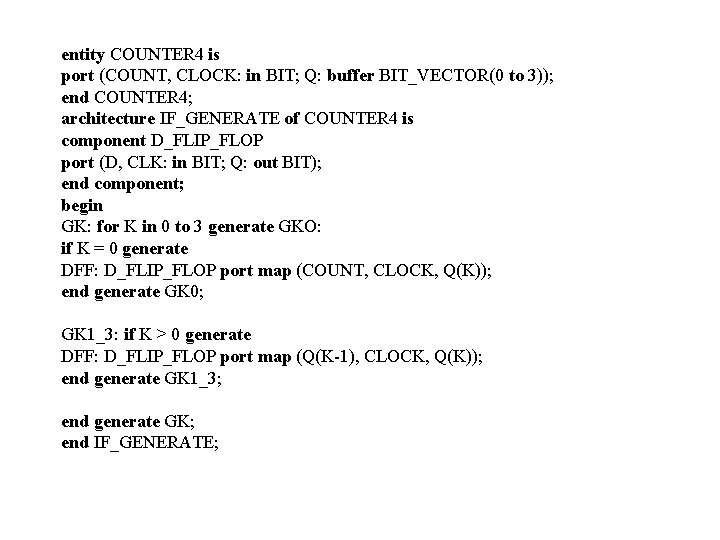

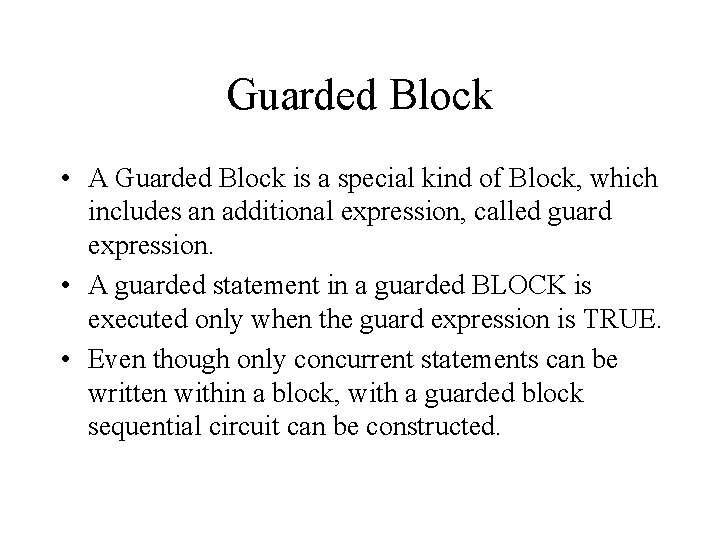

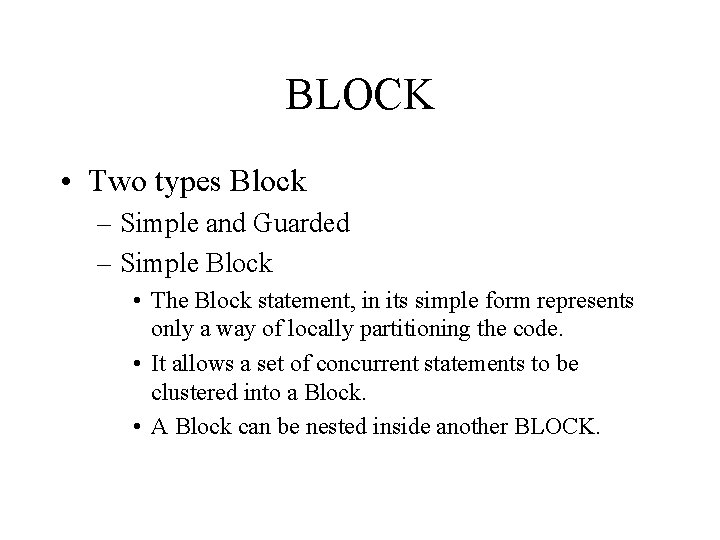

BLOCK • Two types Block – Simple and Guarded – Simple Block • The Block statement, in its simple form represents only a way of locally partitioning the code. • It allows a set of concurrent statements to be clustered into a Block. • A Block can be nested inside another BLOCK.

![Block Syntax Simple Label BLOCK Declartive part Begin Concurrent statements End BLOCK label Block Syntax (Simple) Label : BLOCK [Declartive part] Begin (Concurrent statements) End BLOCK label;](https://slidetodoc.com/presentation_image_h/09486e1663d62b824fb89b921866ab5a/image-13.jpg)

Block Syntax (Simple) Label : BLOCK [Declartive part] Begin (Concurrent statements) End BLOCK label;

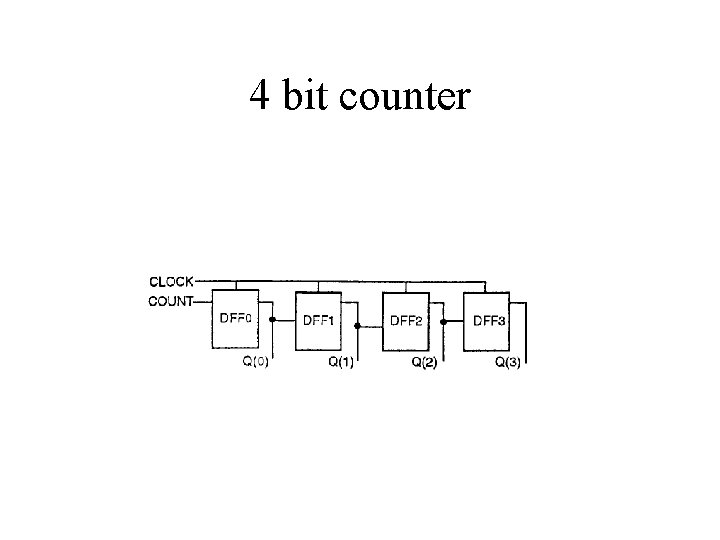

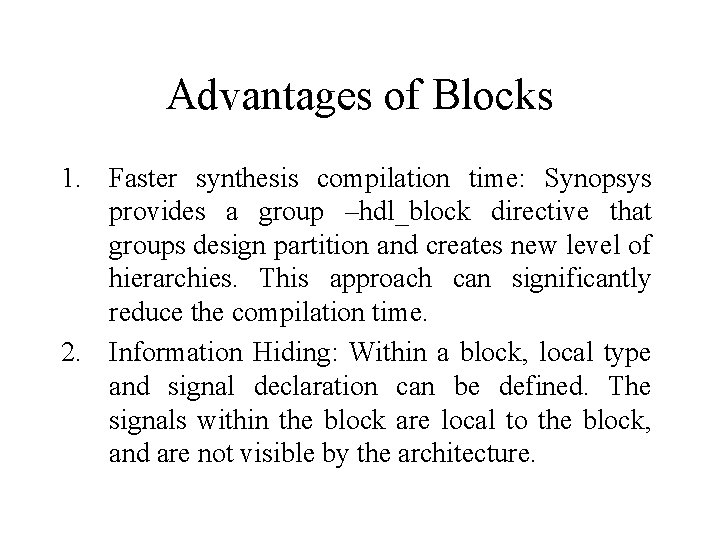

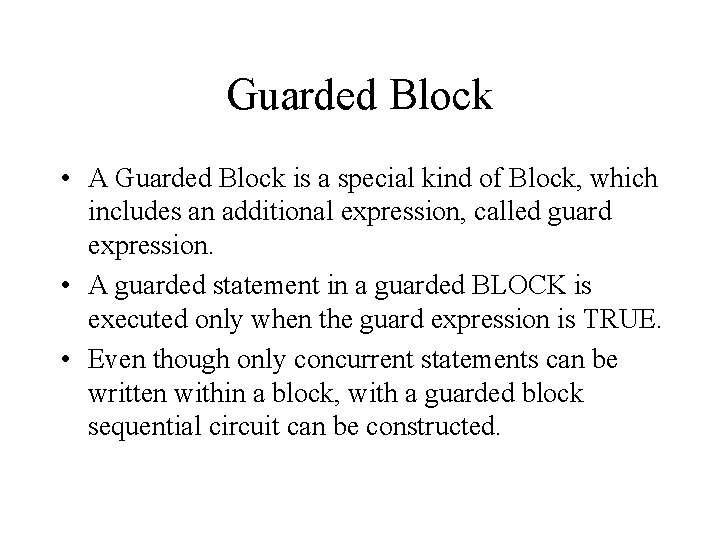

Guarded Block • A Guarded Block is a special kind of Block, which includes an additional expression, called guard expression. • A guarded statement in a guarded BLOCK is executed only when the guard expression is TRUE. • Even though only concurrent statements can be written within a block, with a guarded block sequential circuit can be constructed.

![Guarded Block syntax Label BLOCK guard expression Declarative part Begin Concurrent guarded and Guarded Block syntax Label : BLOCK (guard expression) [Declarative part] Begin (Concurrent guarded and](https://slidetodoc.com/presentation_image_h/09486e1663d62b824fb89b921866ab5a/image-15.jpg)

Guarded Block syntax Label : BLOCK (guard expression) [Declarative part] Begin (Concurrent guarded and unguarded statements) End BLOCK label;

Advantages of Blocks 1. Faster synthesis compilation time: Synopsys provides a group –hdl_block directive that groups design partition and creates new level of hierarchies. This approach can significantly reduce the compilation time. 2. Information Hiding: Within a block, local type and signal declaration can be defined. The signals within the block are local to the block, and are not visible by the architecture.

Advt. Of blocks (cont. . ) 3. Declaration of partition interfaces: The block header enables the definition of local generics, ports and port maps. All synthesizer vendors do not necessarily support block headers. 4. Visibility into architecture: Since a block is a concurrent statement of an architecture, a block has visibility into ports and signals of the architecture and into the declaration of the component within the architecture. A block also has visibility into packages, constants and types declared in the entity and architecture.