G Gerbang XOR dan Gerbang XNOR 1 Gerbang

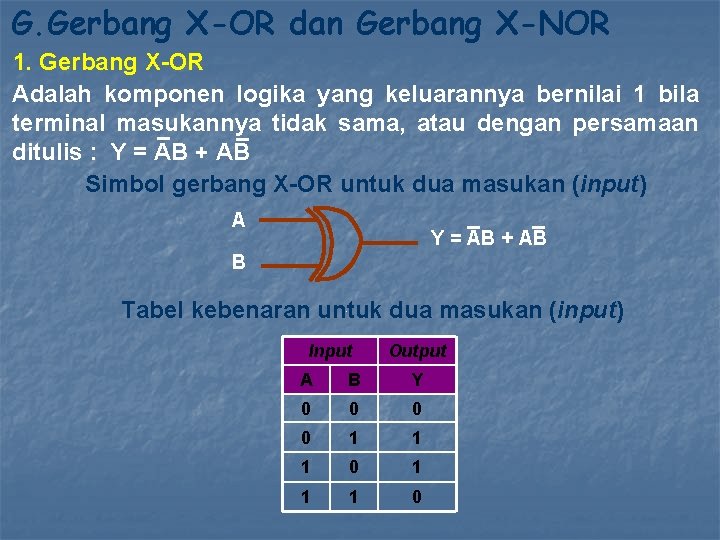

G. Gerbang X-OR dan Gerbang X-NOR 1. Gerbang X-OR Adalah komponen logika yang keluarannya bernilai 1 bila terminal masukannya tidak sama, atau dengan persamaan ditulis : Y = AB + AB Simbol gerbang X-OR untuk dua masukan (input) A Y = AB + AB B. Tabel kebenaran untuk dua masukan (input) Input Output A B Y 0 0 1 1 1 0

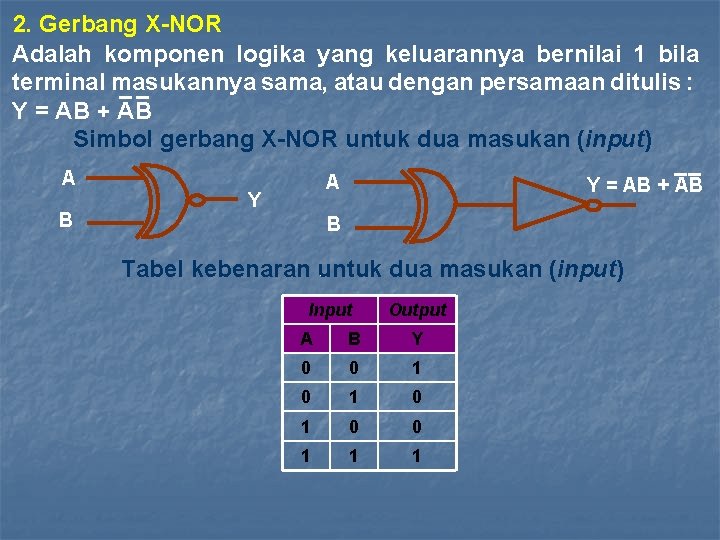

2. Gerbang X-NOR Adalah komponen logika yang keluarannya bernilai 1 bila terminal masukannya sama, atau dengan persamaan ditulis : Y = AB + AB Simbol gerbang X-NOR untuk dua masukan (input) A B A Y Y = AB + AB B. Tabel kebenaran untuk dua masukan (input) Input Output A B Y 0 0 1 0 1 0 0 1 1 1

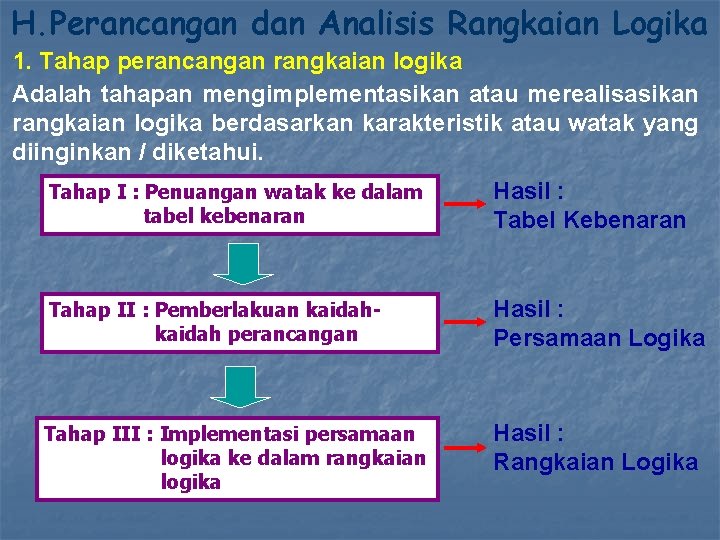

H. Perancangan dan Analisis Rangkaian Logika 1. Tahap perancangan rangkaian logika Adalah tahapan mengimplementasikan atau merealisasikan rangkaian logika berdasarkan karakteristik atau watak yang diinginkan / diketahui. Tahap I : Penuangan watak ke dalam tabel kebenaran Hasil : Tabel Kebenaran Tahap II : Pemberlakuan kaidah perancangan Hasil : Persamaan Logika Tahap III : Implementasi persamaan logika ke dalam rangkaian logika Hasil : Rangkaian Logika

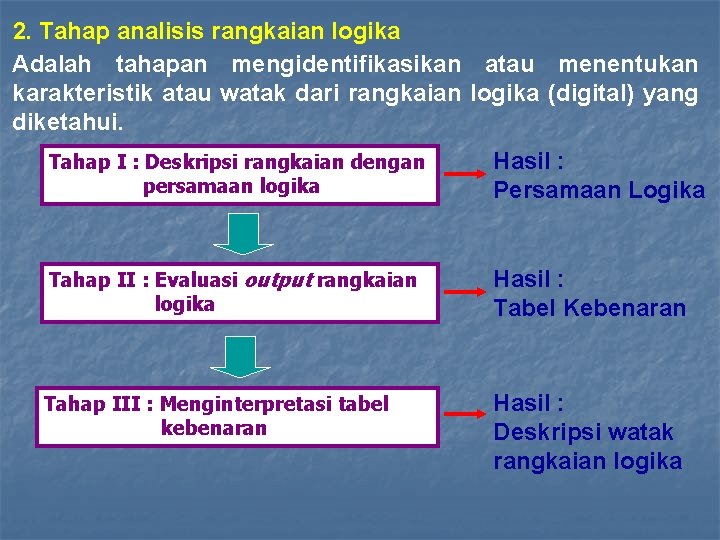

2. Tahap analisis rangkaian logika Adalah tahapan mengidentifikasikan atau menentukan karakteristik atau watak dari rangkaian logika (digital) yang diketahui. Tahap I : Deskripsi rangkaian dengan persamaan logika Hasil : Persamaan Logika Tahap II : Evaluasi output rangkaian logika Hasil : Tabel Kebenaran Tahap III : Menginterpretasi tabel kebenaran Hasil : Deskripsi watak rangkaian logika

I. Hukum dan Peraturan Aljabar Boolean adalah aljabar yang menangani persoalan logika. Aljabar Boolean menggunakan beberapa hukum yang sama seperti aljabar biasa, untuk fungsi OR (Y = A+B) adalah Boolean penambahan dan fungsi AND (Y = A. B) adalah Boolean perkalian. Ada 3 hukum pada aljabar boolean yang sama dengan aljabar biasa. 1. Hukum pertukaran (komutatif) a). Penambahan: A+B = B+A b). Perkalian: A. B = B. A Hukum ini menyebabkan beberapa variabel OR atau AND tidak menjadi masalah.

2. Hukum asosiatif a). Penambahan: A+(B+C) = (A+B)+C b). Perkalian: A. (B. C) = (A. B). C Hukum ini menyebabkan penggabungan beberapa variabel OR atau AND bersamaan tidak menjadi masalah. 3. Hukum distributif a). A. (B+C) = AB+AC b). (A+B)(C+D) = AC+AD+BC+BD Hukum ini menampilkan metode untuk mengembangkan persamaan yang mengandung OR dan AND. Tiga hukum ini mempunyai kebenaran untuk beberapa bilangan variabel. Hukum penambahan dapat dipakai pada Y = A+BC+D untuk bentuk persamaan Y = BC+A+D. Teorema lain yang digunakan dalam gerbang digital adalah teorema de Morgan.

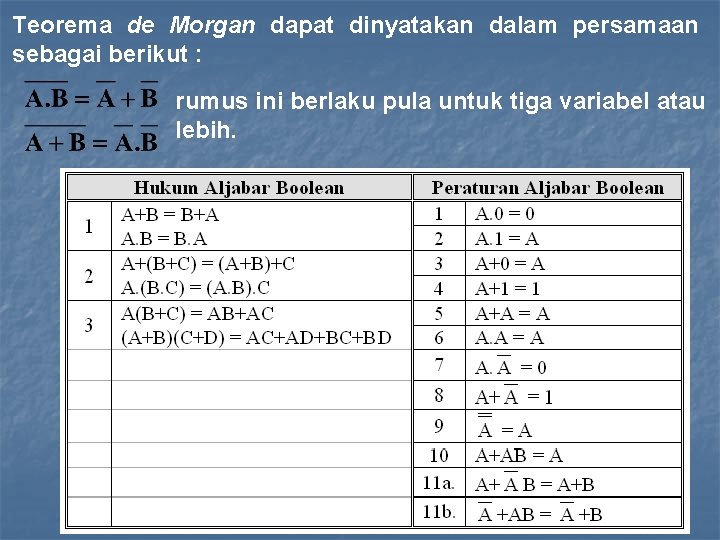

Teorema de Morgan dapat dinyatakan dalam persamaan sebagai berikut : rumus ini berlaku pula untuk tiga variabel atau lebih.

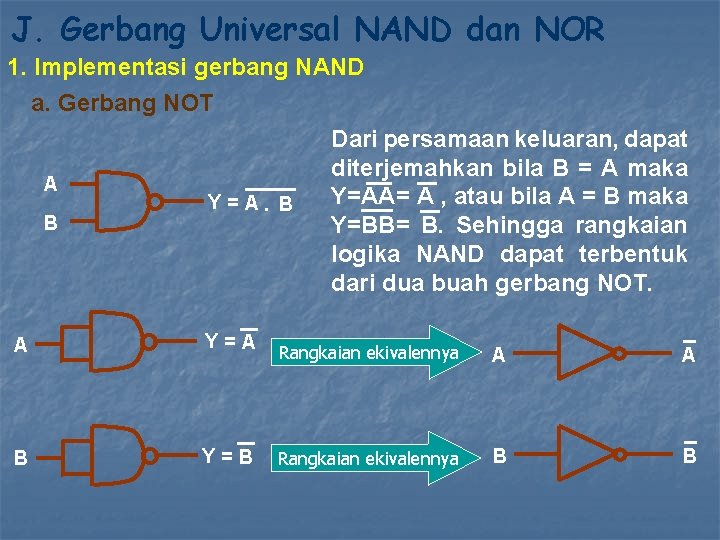

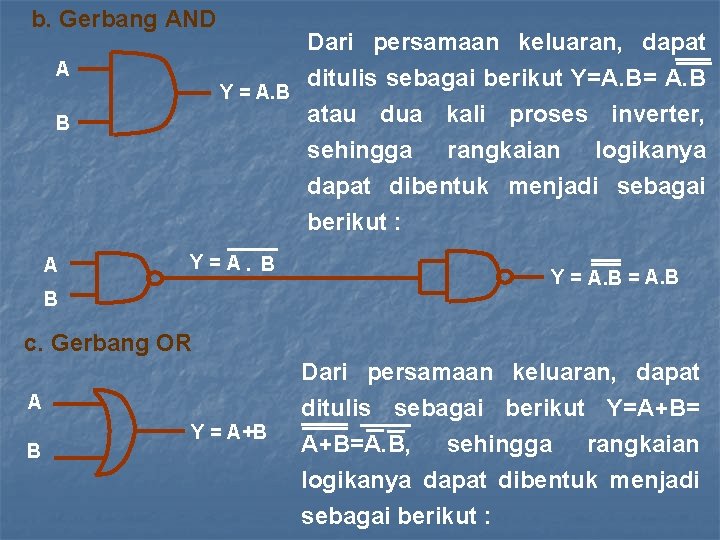

J. Gerbang Universal NAND dan NOR 1. Implementasi gerbang NAND a. Gerbang NOT Dari persamaan keluaran, dapat diterjemahkan bila B = A maka A Y=AA= A , atau bila A = B maka Y= A. B B Y=BB= B. Sehingga rangkaian logika NAND dapat terbentuk dari dua buah gerbang NOT. A Y=A B Y=B Rangkaian ekivalennya A A Rangkaian ekivalennya B B

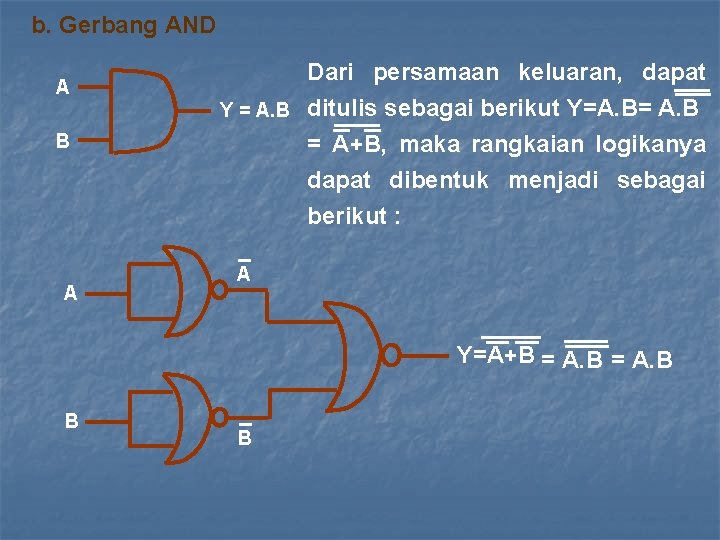

b. Gerbang AND A B A Dari persamaan keluaran, dapat ditulis sebagai berikut Y=A. B= A. B Y = A. B atau dua kali proses inverter, sehingga rangkaian logikanya dapat dibentuk menjadi sebagai berikut : Y= A. B B Y = A. B c. Gerbang OR A B Y = A+B Dari persamaan keluaran, dapat ditulis sebagai berikut Y=A+B=A. B, sehingga rangkaian logikanya dapat dibentuk menjadi sebagai berikut :

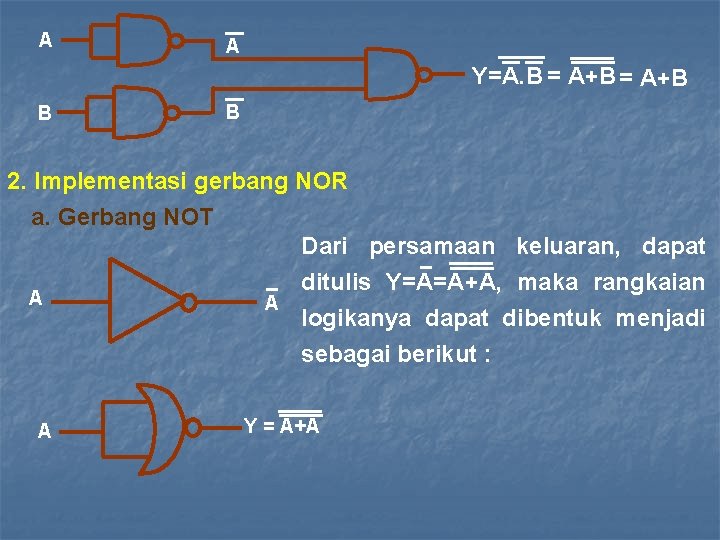

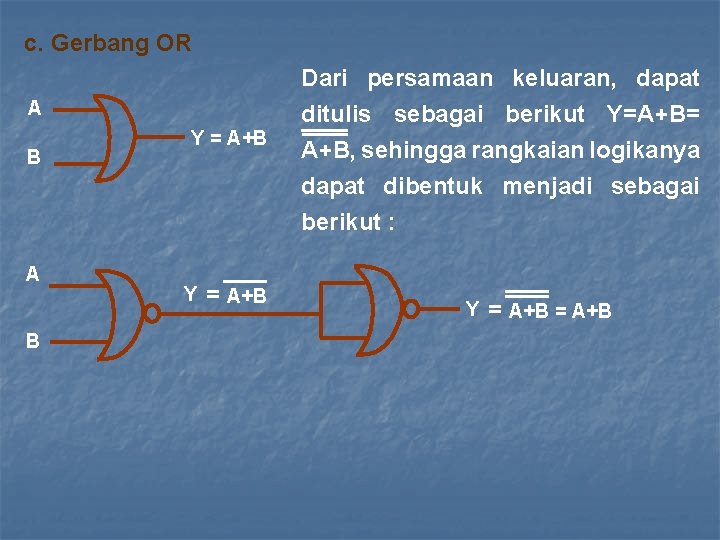

A A Y=A. B = A+B B B 2. Implementasi gerbang NOR a. Gerbang NOT A A Dari persamaan keluaran, dapat ditulis Y=A=A+A, maka rangkaian A logikanya dapat dibentuk menjadi sebagai berikut : Y = A+A

b. Gerbang AND A B A Dari persamaan keluaran, dapat Y = A. B ditulis sebagai berikut Y=A. B= A. B = A+B, maka rangkaian logikanya dapat dibentuk menjadi sebagai berikut : A Y=A+B = A. B B B

c. Gerbang OR A B Y = A+B Dari persamaan keluaran, dapat ditulis sebagai berikut Y=A+B= A+B, sehingga rangkaian logikanya dapat dibentuk menjadi sebagai berikut : Y = A+B

- Slides: 12