G F Dalla Betta G Soncini Appunti di

G. - F. Dalla Betta, G. Soncini. Appunti di Elettronica 2. Capitolo III Porte logiche digitali in tecnologia CMOS III. 1. Parametri caratteristici III. 2. Richiami sui transistori MOS III. 3. Logiche CMOS statiche III. 4. Logiche CMOS dinamiche Esempi ed Esercizi 1

Introduzione • Con il termine Famiglie Logiche (FL) si indica un particolare modo di realizzare in forma integrata le funzioni logiche elementari (NOR, NAND, . . . ), che differisce da altri sotto il profilo circuitale e/o tecnologico. • Le FL realizzate con circuiti integrati in silicio si dividono in due grandi gruppi, bipolari e MOS, ciascuno dei quali ulteriormente suddiviso in rapporto alle diverse caratteristiche tecnologiche e circuitali dei componenti utilizzati. • Oltre alle FL di tipo bipolare e MOS in silicio, è opportuno ricordare i circuiti realizzati in Arseniuro di Gallio (Ga. As) e altri semiconduttori compositi (III-V) per il rilevante interesse strategico nelle applicazioni ad alta velocità (in particolare per le telecomunicazioni). 2

3 III. 1. Parametri caratteristici Livelli logici Soglia logica Margini di immunità ai disturbi Ritardo di propagazione Dissipazione di potenza Prodotto ritardo-consumo Fan-out e Fan-in Livello d’integrazione, costo ed affidabilità

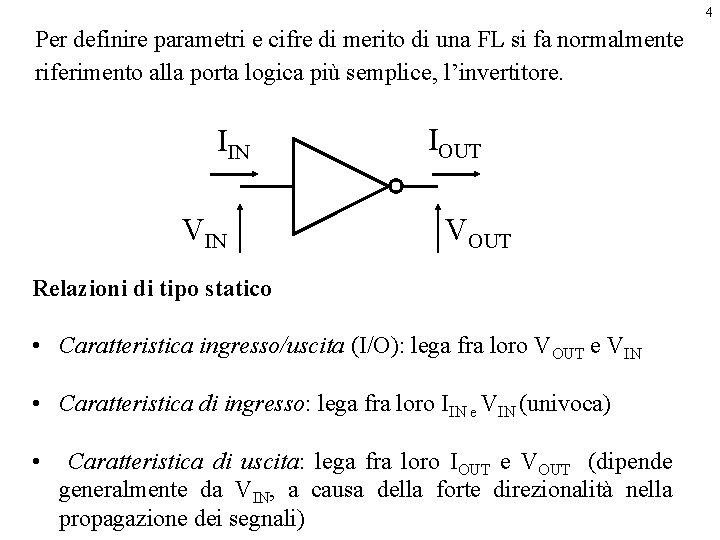

4 Per definire parametri e cifre di merito di una FL si fa normalmente riferimento alla porta logica più semplice, l’invertitore. IIN VIN IOUT VOUT Relazioni di tipo statico • Caratteristica ingresso/uscita (I/O): lega fra loro VOUT e VIN • Caratteristica di ingresso: lega fra loro IIN e VIN (univoca) • Caratteristica di uscita: lega fra loro IOUT e VOUT (dipende generalmente da VIN, a causa della forte direzionalità nella propagazione dei segnali)

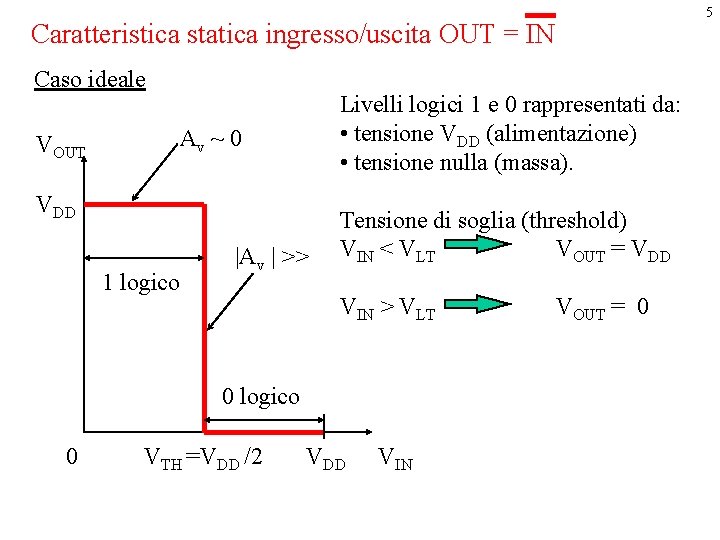

5 Caratteristica statica ingresso/uscita OUT = IN Caso ideale VOUT Livelli logici 1 e 0 rappresentati da: • tensione VDD (alimentazione) • tensione nulla (massa). Av ~ 0 VDD 1 logico |Av | >> Tensione di soglia (threshold) VIN < VLT VOUT = VDD VIN > VLT 0 logico 0 VTH =VDD /2 VDD VIN VOUT = 0

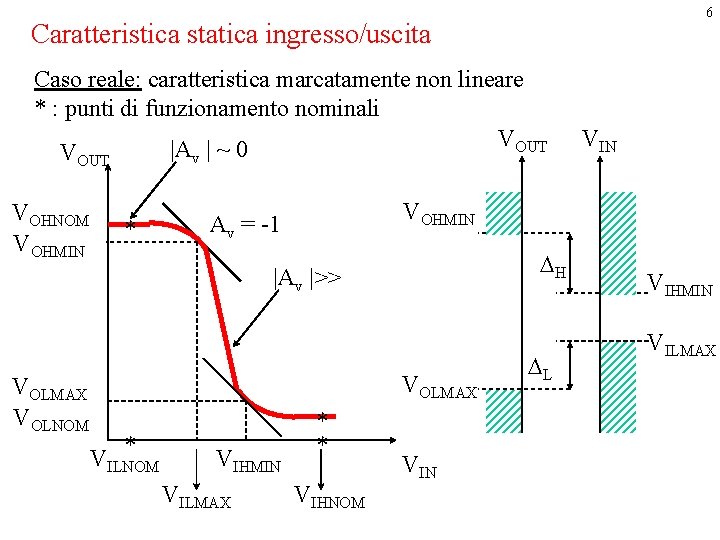

6 Caratteristica statica ingresso/uscita Caso reale: caratteristica marcatamente non lineare * : punti di funzionamento nominali VOUT |Av | ~ 0 VOUT VOHNOM VOHMIN * VOHMIN Av = -1 DH |Av |>> VOLMAX VOLNOM VOLMAX * VILNOM VIHMIN VILMAX VIN * * VIHNOM VIN DL VIHMIN VILMAX

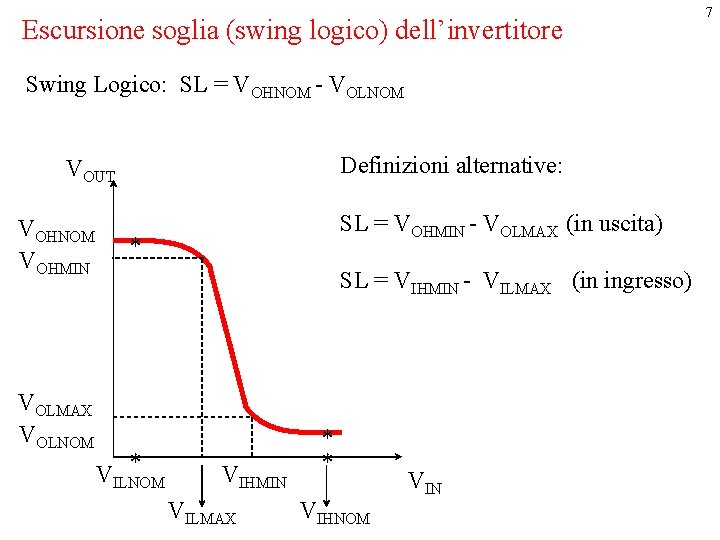

Escursione soglia (swing logico) dell’invertitore Swing Logico: SL = VOHNOM - VOLNOM Definizioni alternative: VOUT VOHNOM VOHMIN VOLMAX VOLNOM SL = VOHMIN - VOLMAX (in uscita) * SL = VIHMIN - VILMAX (in ingresso) * VILNOM VIHMIN VILMAX * * VIHNOM VIN 7

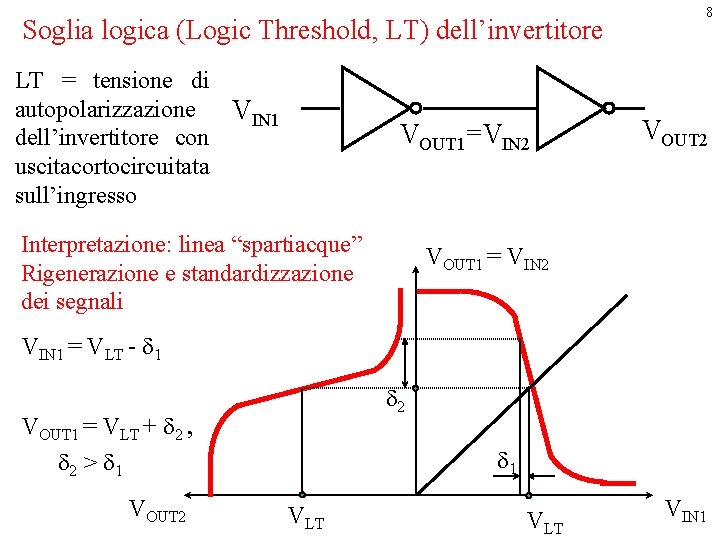

Soglia logica (Logic Threshold, LT) dell’invertitore LT = tensione di autopolarizzazione VIN 1 dell’invertitore con uscitacortocircuitata sull’ingresso VOUT 1=VIN 2 Interpretazione: linea “spartiacque” Rigenerazione e standardizzazione dei segnali 8 VOUT 2 VOUT 1 = VIN 2 VIN 1 = VLT - d 1 d 2 VOUT 1 = VLT + d 2 , d 2 > d 1 VOUT 2 d 1 VLT VIN 1

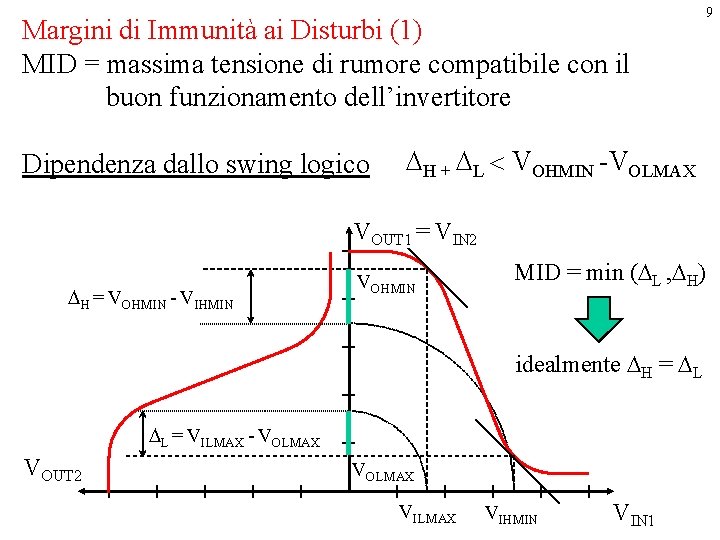

Margini di Immunità ai Disturbi (1) MID = massima tensione di rumore compatibile con il buon funzionamento dell’invertitore Dipendenza dallo swing logico 9 DH + DL < VOHMIN -VOLMAX VOUT 1 = VIN 2 DH = VOHMIN - VIHMIN VOHMIN MID = min (DL , DH) idealmente DH = DL DL = VILMAX - VOLMAX VOUT 2 VOLMAX VIHMIN VIN 1

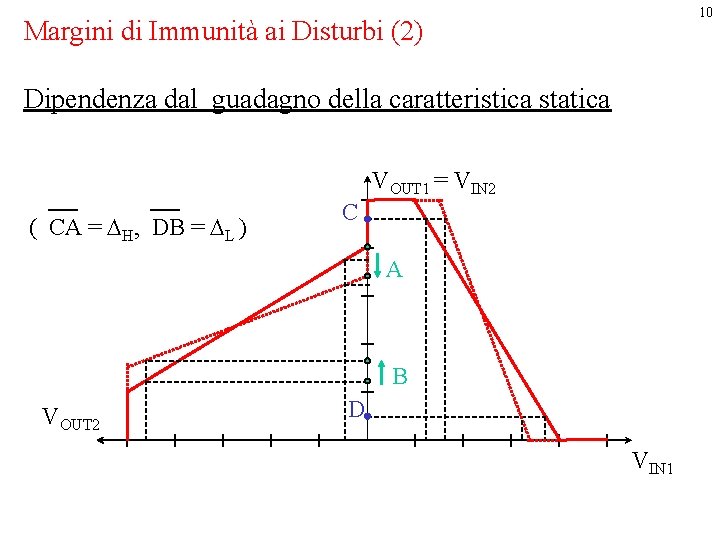

10 Margini di Immunità ai Disturbi (2) Dipendenza dal guadagno della caratteristica statica VOUT 1 = VIN 2 ( CA = DH, DB = DL ) C A B VOUT 2 D VIN 1

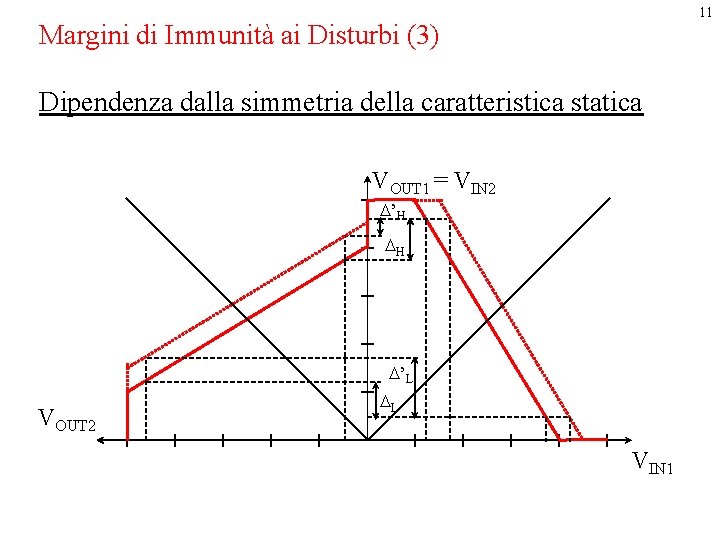

11 Margini di Immunità ai Disturbi (3) Dipendenza dalla simmetria della caratteristica statica VOUT 1 = VIN 2 D’H DH D’L VOUT 2 DL VIN 1

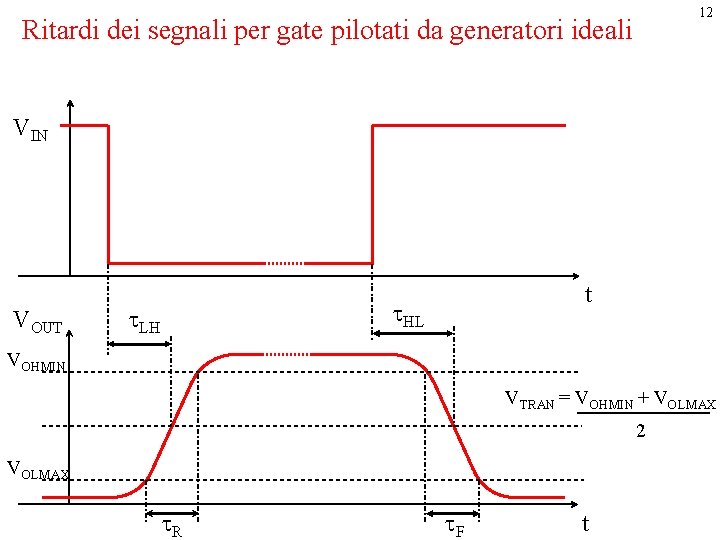

12 Ritardi dei segnali per gate pilotati da generatori ideali VIN VOUT t t. HL t. LH VOHMIN VTRAN = VOHMIN + VOLMAX 2 VOLMAX t. R t. F t

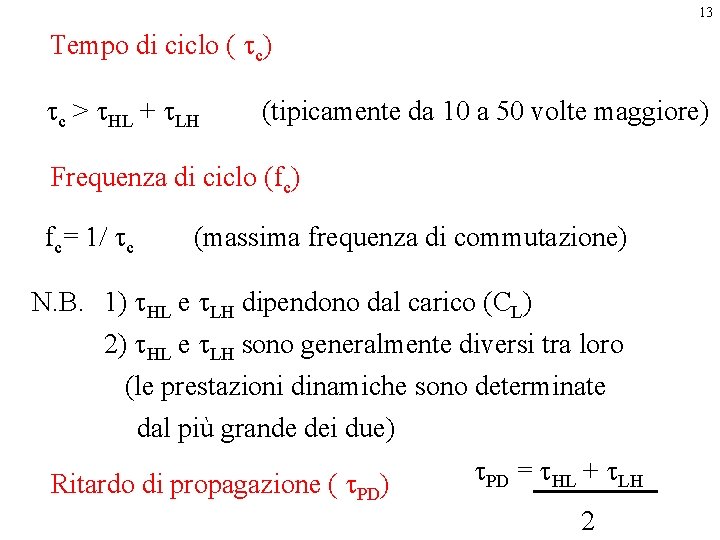

13 Tempo di ciclo ( tc) tc > t. HL + t. LH (tipicamente da 10 a 50 volte maggiore) Frequenza di ciclo (fc) fc= 1/ tc (massima frequenza di commutazione) N. B. 1) t. HL e t. LH dipendono dal carico (CL) 2) t. HL e t. LH sono generalmente diversi tra loro (le prestazioni dinamiche sono determinate dal più grande dei due) Ritardo di propagazione ( t. PD) t. PD = t. HL + t. LH 2

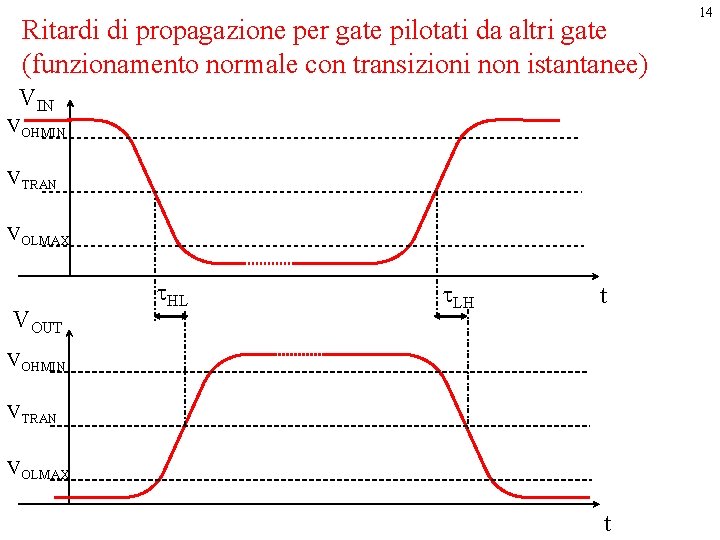

Ritardi di propagazione per gate pilotati da altri gate (funzionamento normale con transizioni non istantanee) VIN VOHMIN VTRAN VOLMAX VOUT t. HL t. LH t VOHMIN VTRAN VOLMAX t 14

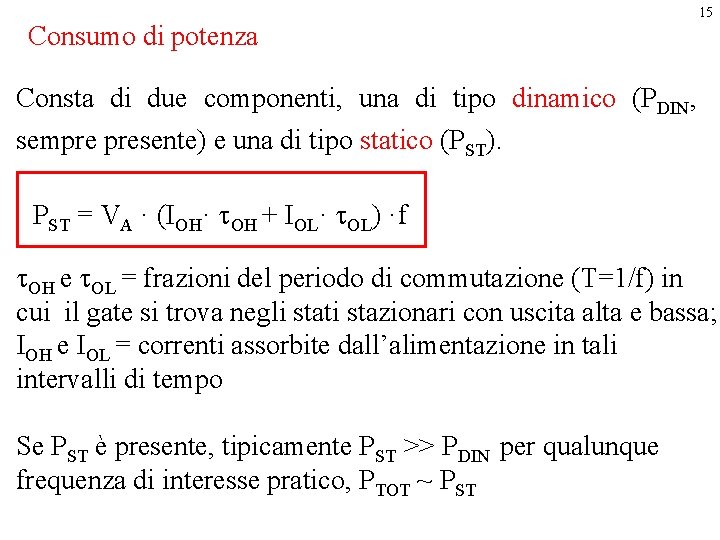

Consumo di potenza 15 Consta di due componenti, una di tipo dinamico (PDIN, sempre presente) e una di tipo statico (PST). PST = VA · (IOH· t. OH + IOL· t. OL) ·f t. OH e t. OL = frazioni del periodo di commutazione (T=1/f) in cui il gate si trova negli stati stazionari con uscita alta e bassa; IOH e IOL = correnti assorbite dall’alimentazione in tali intervalli di tempo Se PST è presente, tipicamente PST >> PDIN per qualunque frequenza di interesse pratico, PTOT ~ PST

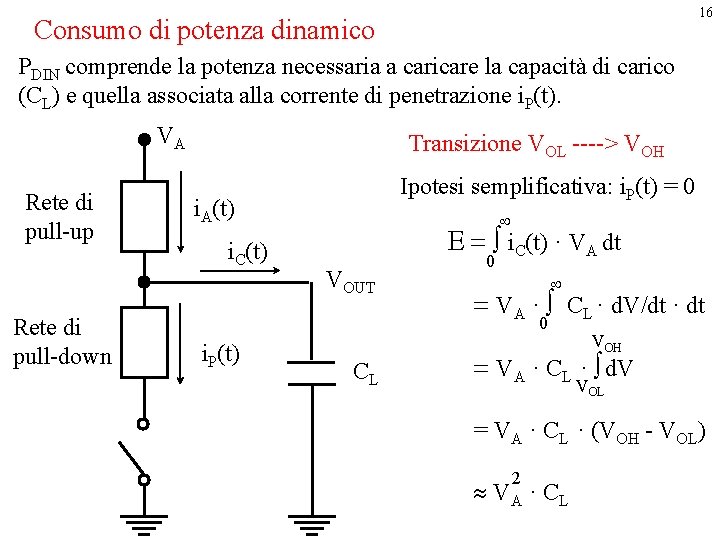

16 Consumo di potenza dinamico PDIN comprende la potenza necessaria a caricare la capacità di carico (CL) e quella associata alla corrente di penetrazione i. P(t). VA Rete di pull-up Rete di pull-down Transizione VOL ----> VOH Ipotesi semplificativa: i. P(t) = 0 i. A(t) i. C(t) ¥ E = ò i. C(t) · VA dt VOUT 0 ¥ = VA · ò CL · d. V/dt · dt 0 i. P(t) CL VOH = VA · CL · ò d. V VOL = VA · CL · (VOH - VOL) 2 VA · C L

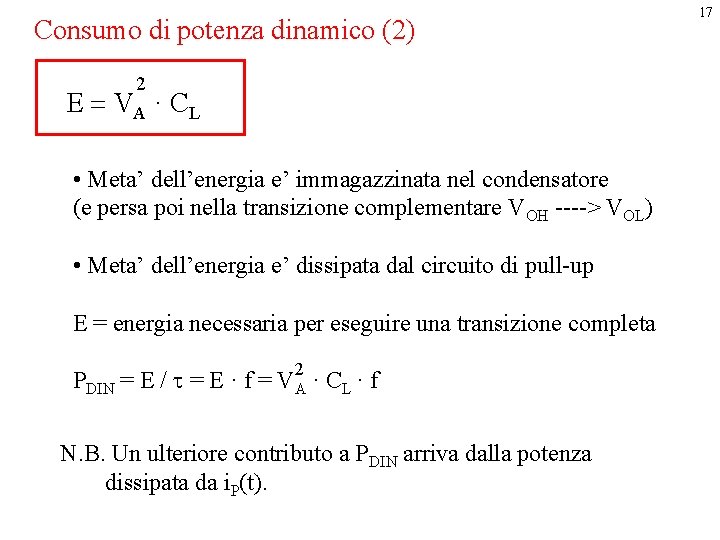

Consumo di potenza dinamico (2) 2 E = VA · C L • Meta’ dell’energia e’ immagazzinata nel condensatore (e persa poi nella transizione complementare VOH ----> VOL) • Meta’ dell’energia e’ dissipata dal circuito di pull-up E = energia necessaria per eseguire una transizione completa 2 PDIN = E / t = E · f = VA · CL · f N. B. Un ulteriore contributo a PDIN arriva dalla potenza dissipata da i. P(t). 17

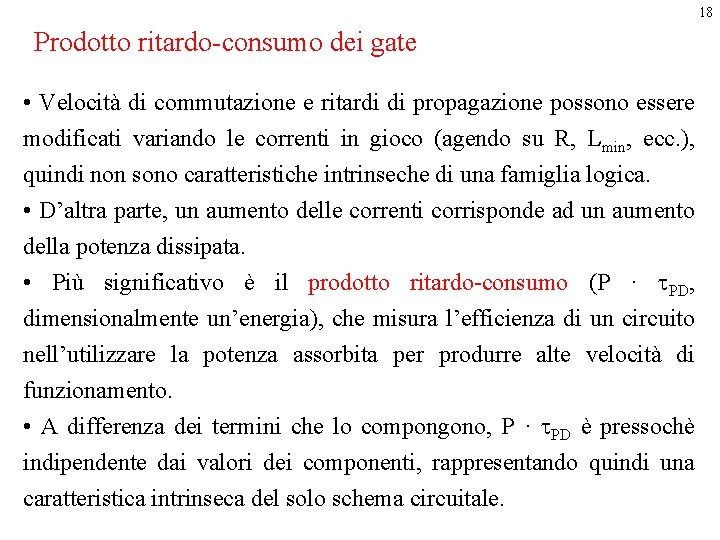

18 Prodotto ritardo-consumo dei gate • Velocità di commutazione e ritardi di propagazione possono essere modificati variando le correnti in gioco (agendo su R, Lmin, ecc. ), quindi non sono caratteristiche intrinseche di una famiglia logica. • D’altra parte, un aumento delle correnti corrisponde ad un aumento della potenza dissipata. • Più significativo è il prodotto ritardo-consumo (P · t. PD, dimensionalmente un’energia), che misura l’efficienza di un circuito nell’utilizzare la potenza assorbita per produrre alte velocità di funzionamento. • A differenza dei termini che lo compongono, P · t. PD è pressochè indipendente dai valori dei componenti, rappresentando quindi una caratteristica intrinseca del solo schema circuitale.

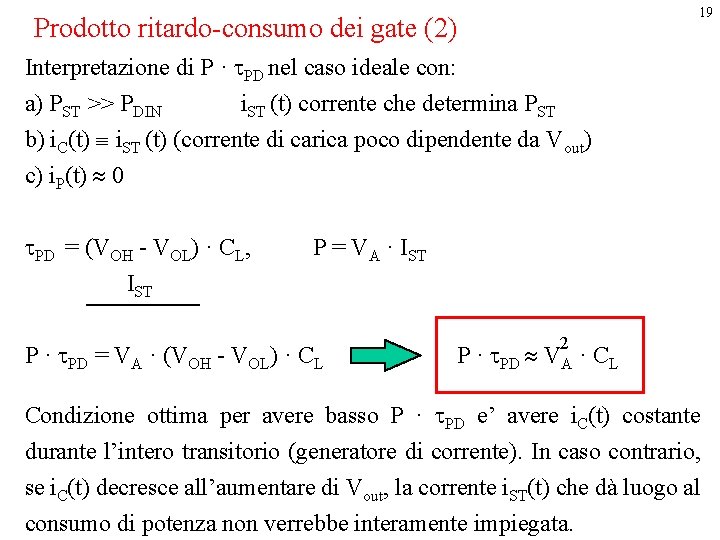

19 Prodotto ritardo-consumo dei gate (2) Interpretazione di P · t. PD nel caso ideale con: a) PST >> PDIN i. ST (t) corrente che determina PST b) i. C(t) º i. ST (t) (corrente di carica poco dipendente da Vout) c) i. P(t) 0 t. PD = (VOH - VOL) · CL, IST P = VA · IST P · t. PD = VA · (VOH - VOL) · CL 2 P · t. PD VA · CL Condizione ottima per avere basso P · t. PD e’ avere i. C(t) costante durante l’intero transitorio (generatore di corrente). In caso contrario, se i. C(t) decresce all’aumentare di Vout, la corrente i. ST(t) che dà luogo al consumo di potenza non verrebbe interamente impiegata.

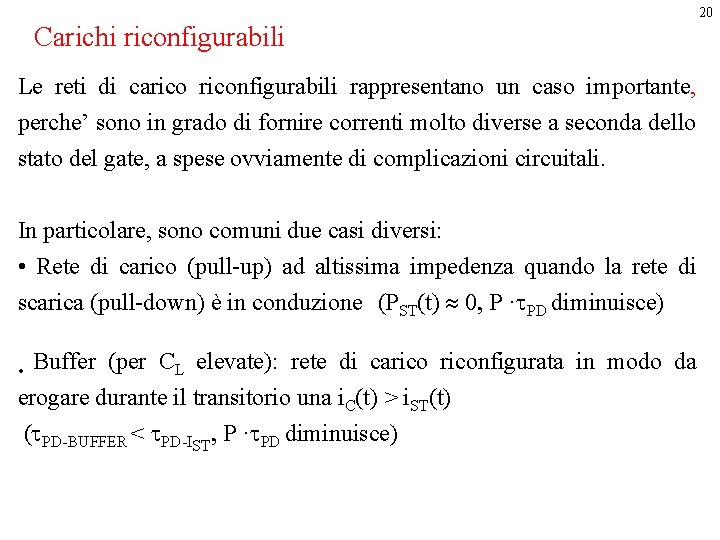

20 Carichi riconfigurabili Le reti di cariconfigurabili rappresentano un caso importante, perche’ sono in grado di fornire correnti molto diverse a seconda dello stato del gate, a spese ovviamente di complicazioni circuitali. In particolare, sono comuni due casi diversi: • Rete di carico (pull-up) ad altissima impedenza quando la rete di scarica (pull-down) è in conduzione (PST(t) 0, P ·t. PD diminuisce) Buffer (per CL elevate): rete di cariconfigurata in modo da erogare durante il transitorio una i. C(t) > i. ST(t) (t. PD-BUFFER < t. PD-IST, P ·t. PD diminuisce) •

Fan-Out • I gate di ciascuna FL devono funzionare rispettando un insieme di specifiche, che riguardano parametri sia statici che dinamici. • Le prestazioni dipendono dal carico che un gate deve pilotare, costituito tipicamente da un certo numero (N) di altri gate elementari. - CL (e quindi t. PD ) proporzionale a N; - VOH e/o VOL possono dipendere dalla corrente erogata al (o assorbita dal) carico in condizioni stazionarie (e quindi da N). • Esiste un numero massimo di gate che può essere pilotato senza violazioni delle varie specifiche; il più grande numero di gate pilotabili nel rispetto dell’intero insieme di specifiche qualificano una FL è detto Fan-Out. • Per i circuiti CMOS, il Fan-Out è determinato essenzialmente da considerazioni di tipo dinamico (CL massima compatibile con una certa velocita’). 21

22 Fan-In • Considerazioni analoghe valgono per l’ingresso dei circuiti, portando alla definizione del Fan-In, che è il massimo numero di gate connettibili in ingresso ad un circuito nel rispetto di tutte le sue specifiche. • Nonostante l’apparente simmetria delle definizioni, i due parametri hanno una rilevanza molto diversa: mentre il Fan-Out rappresenta una caratteristica di fondamentale importanza, raramente il limitato Fan-In costituisce un problema serio.

Livello d’integrazione, costo e affidabilità • Il livello di integrazione (gate/cm 2) dipende dalla struttura e dalla tecnologia dei circuiti ed è costantemente aumentato col progresso della microelettronica, portando a componenti più complessi e quindi più costosi e con maggior probabilità di guasti e malfunzionamenti. • Tuttavia l’incremento del numero di funzioni elementari (gate) su un chip ha largamente compensato questi effetti globali, apportando un costante miglioramento dei parametri specifici e riducendo il costo per gate in modo proporzionale all’aumento del livello di integrazione. • Una cifra di merito “complessiva” e’ la resa funzionale (functional throughput), che fornisce un’indicazione del numero di operazioni eseguibili per unità di area (vantaggio del CMOS sul bipolare). 23

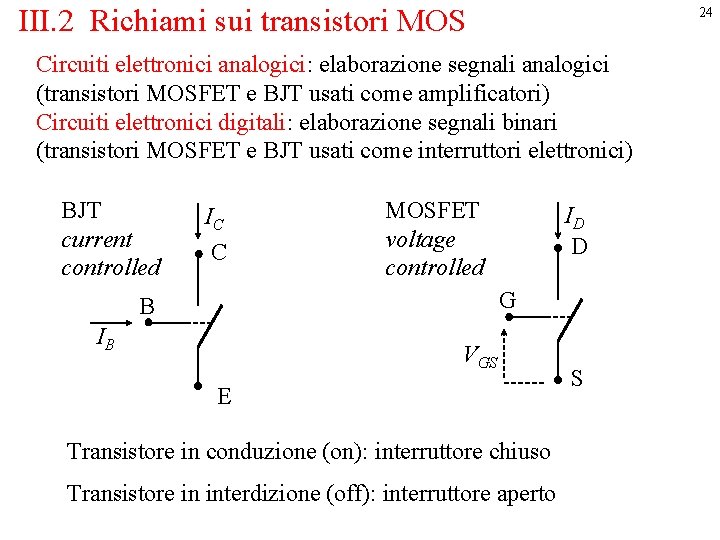

III. 2 Richiami sui transistori MOS 24 Circuiti elettronici analogici: elaborazione segnali analogici (transistori MOSFET e BJT usati come amplificatori) Circuiti elettronici digitali: elaborazione segnali binari (transistori MOSFET e BJT usati come interruttori elettronici) BJT current controlled IC C MOSFET voltage controlled ID D G B IB VGS E Transistore in conduzione (on): interruttore chiuso Transistore in interdizione (off): interruttore aperto S

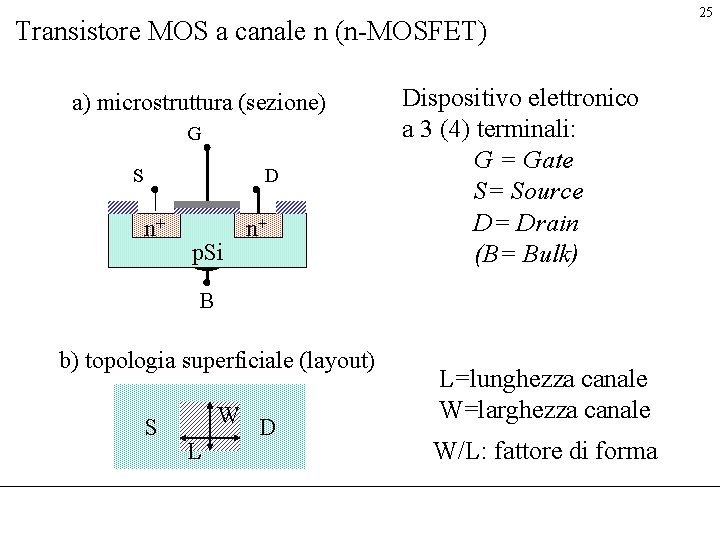

Transistore MOS a canale n (n-MOSFET) a) microstruttura (sezione) G S D n+ p. Si n+ Dispositivo elettronico a 3 (4) terminali: G = Gate S= Source D= Drain (B= Bulk) B b) topologia superficiale (layout) S L W D L=lunghezza canale W=larghezza canale W/L: fattore di forma 25

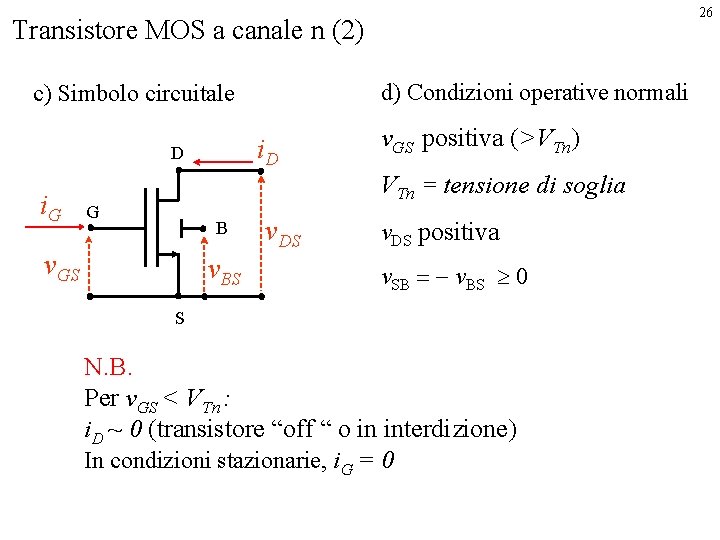

26 Transistore MOS a canale n (2) d) Condizioni operative normali c) Simbolo circuitale i. D D i. G v. GS positiva (>VTn) VTn = tensione di soglia G B v. GS v. BS v. DS positiva v. SB = - v. BS ³ 0 S N. B. Per v. GS < VTn : i. D ~ 0 (transistore “off “ o in interdizione) In condizioni stazionarie, i. G = 0

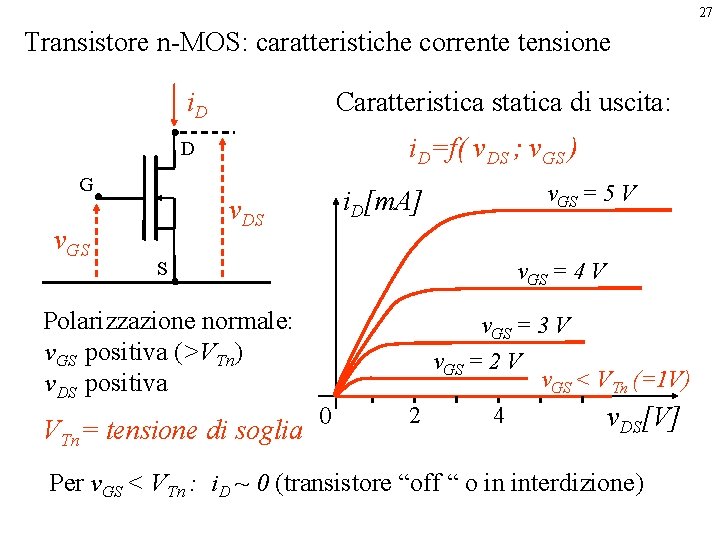

27 Transistore n-MOS: caratteristiche corrente tensione i. D Caratteristica statica di uscita: i. D=f( v. DS ; v. GS ) D G v. GS i. D[m. A] v. DS S Polarizzazione normale: v. GS positiva (>VTn) v. DS positiva VTn= tensione di soglia v. GS = 5 V v. GS = 4 V 0 v. GS = 3 V v. GS = 2 V v. GS < VTn (=1 V) 2 4 v. DS[V] Per v. GS < VTn : i. D ~ 0 (transistore “off “ o in interdizione)

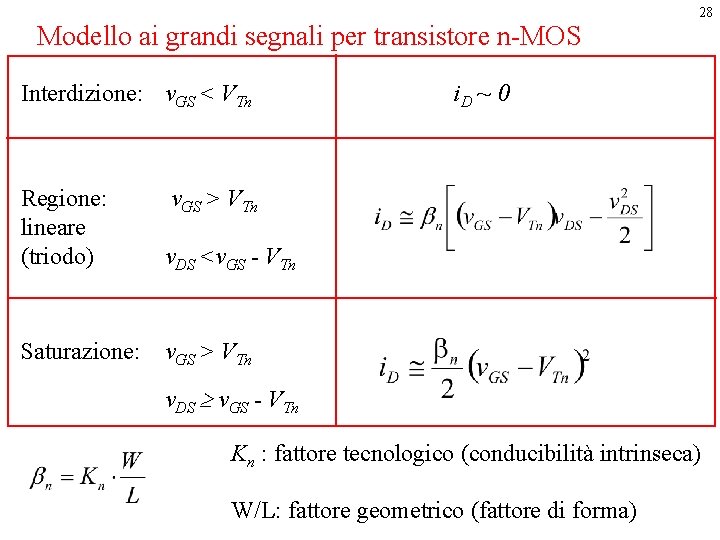

Modello ai grandi segnali per transistore n-MOS Interdizione: v. GS < VTn Regione: lineare (triodo) v. DS <v. GS - VTn Saturazione: v. GS > VTn 28 i. D ~ 0 v. GS > VTn v. DS ³ v. GS - VTn Kn : fattore tecnologico (conducibilità intrinseca) W/L: fattore geometrico (fattore di forma)

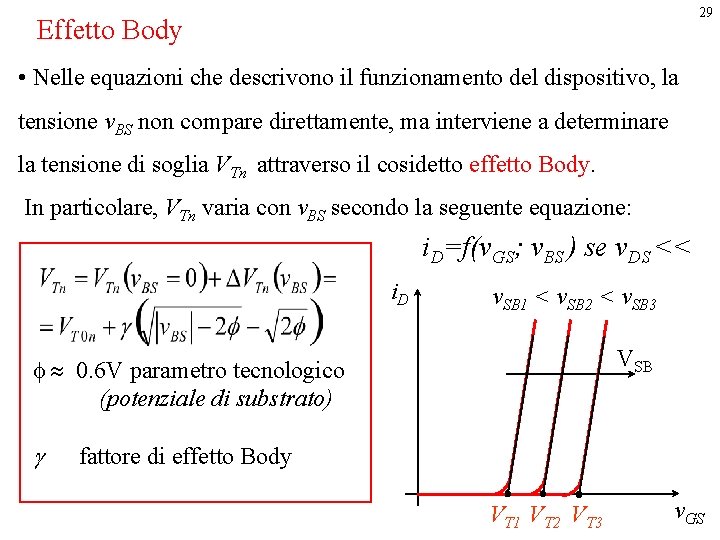

29 Effetto Body • Nelle equazioni che descrivono il funzionamento del dispositivo, la tensione v. BS non compare direttamente, ma interviene a determinare la tensione di soglia VTn attraverso il cosidetto effetto Body. In particolare, VTn varia con v. BS secondo la seguente equazione: i. D=f(v. GS; v. BS ) se v. DS << i. D v. SB 1 < v. SB 2 < v. SB 3 VSB 0. 6 V parametro tecnologico (potenziale di substrato) g fattore di effetto Body VT 1 VT 2 VT 3 v. GS

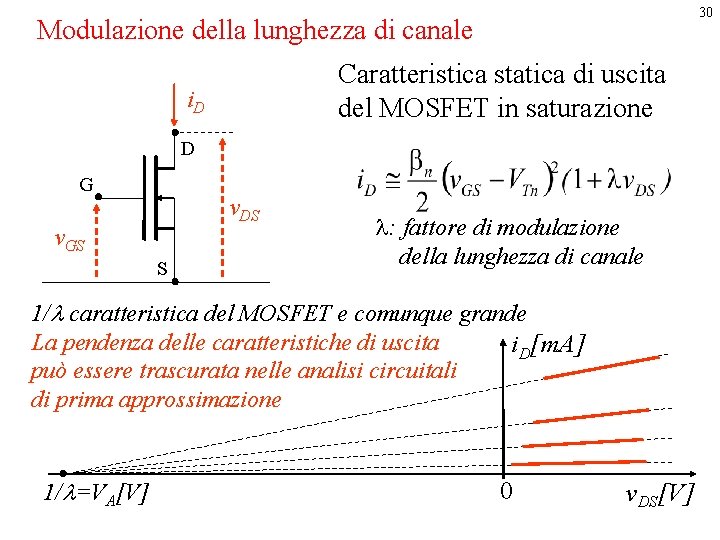

30 Modulazione della lunghezza di canale Caratteristica statica di uscita del MOSFET in saturazione i. D D G v. DS v. GS S l: fattore di modulazione della lunghezza di canale 1/ caratteristica del MOSFET e comunque grande La pendenza delle caratteristiche di uscita i. D[m. A] può essere trascurata nelle analisi circuitali di prima approssimazione 1/ =VA[V] 0 v. DS[V]

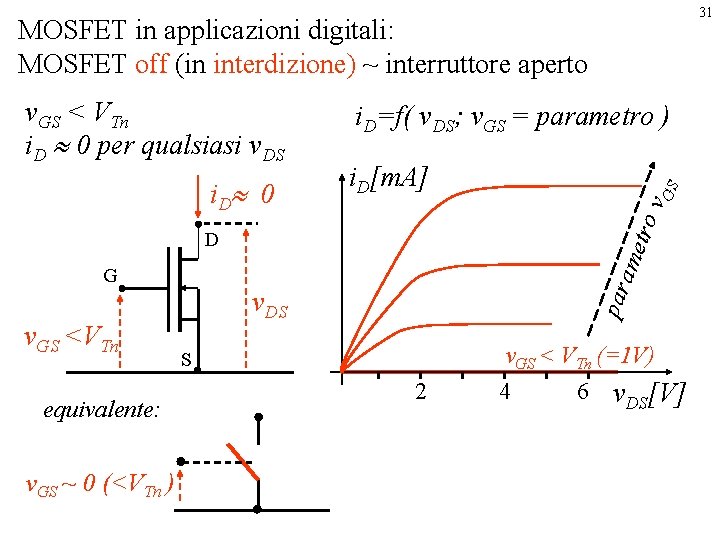

31 MOSFET in applicazioni digitali: MOSFET off (in interdizione) ~ interruttore aperto v. GS <VTn equivalente: v. GS ~ 0 (<VTn ) par ame D G S i. D[m. A] tro i D 0 i. D=f( v. DS; v. GS = parametro ) v. GS < VTn i. D 0 per qualsiasi v. DS S 2 v. GS < VTn (=1 V) 4 6 v. DS[V]

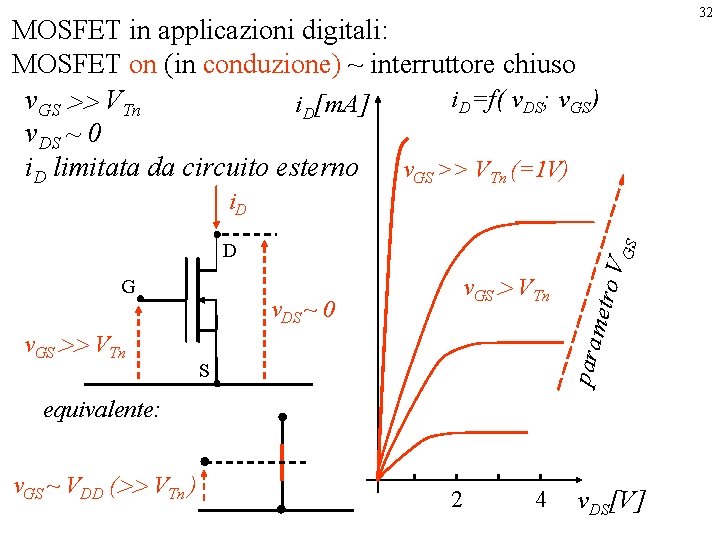

32 MOSFET in applicazioni digitali: MOSFET on (in conduzione) ~ interruttore chiuso i. D=f( v. DS; v. GS) v. GS VTn i. D[m. A] v. DS ~ 0 i. D limitata da circuito esterno v. GS >> VTn (=1 V) i. D v. GS VTn v. DS ~ 0 S o. V v. GS VTn para metr G GS D equivalente: v. GS ~ VDD ( VTn ) 2 4 v. DS[V]

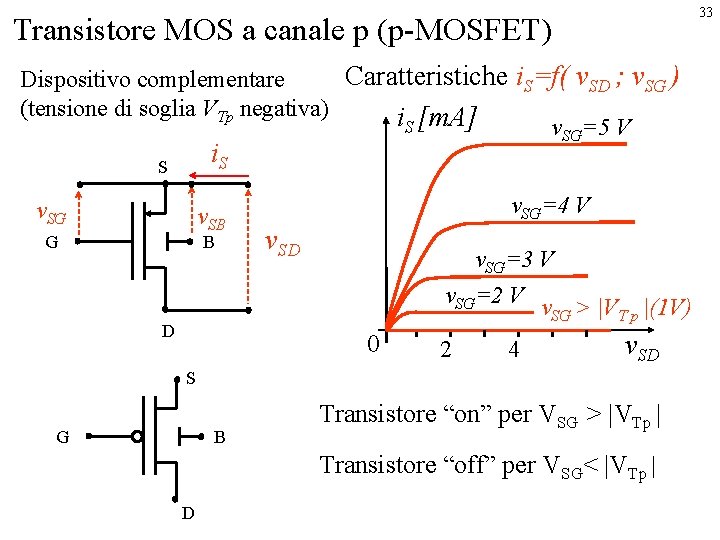

33 Transistore MOS a canale p (p-MOSFET) Caratteristiche i. S=f( v. SD ; v. SG ) Dispositivo complementare (tensione di soglia VTp negativa) i. S [m. A] v. SG=5 V i. S S v. SG v. SB B G v. SG=4 V v. SD v. SG=3 V v. SG=2 V v > |V |(1 V) SG Tp D 0 2 4 v. SD S B G Transistore “on” per VSG > |VTp | Transistore “off” per VSG< |VTp | D

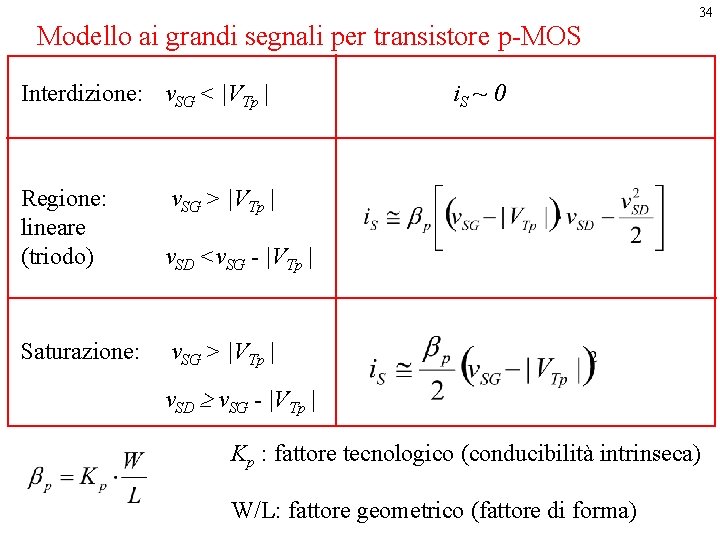

Modello ai grandi segnali per transistore p-MOS Interdizione: v. SG < |VTp | Regione: lineare (triodo) v. SD <v. SG - |VTp | Saturazione: v. SG > |VTp | 34 i. S ~ 0 v. SG > |VTp | v. SD ³ v. SG - |VTp | Kp : fattore tecnologico (conducibilità intrinseca) W/L: fattore geometrico (fattore di forma)

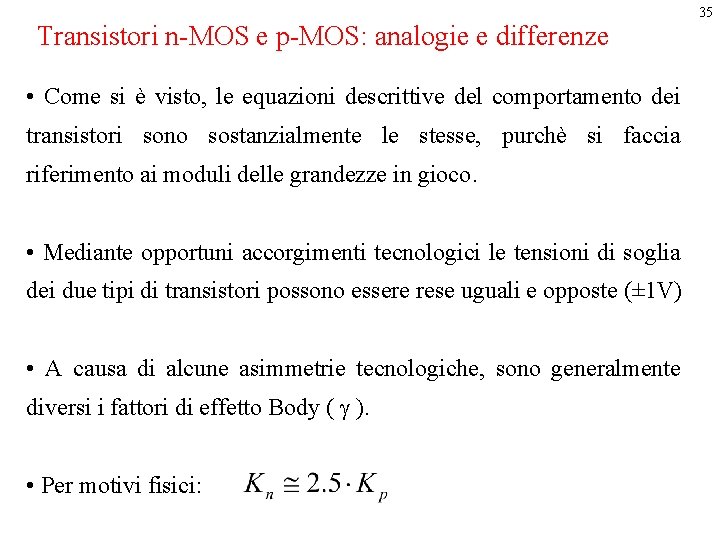

Transistori n-MOS e p-MOS: analogie e differenze • Come si è visto, le equazioni descrittive del comportamento dei transistori sono sostanzialmente le stesse, purchè si faccia riferimento ai moduli delle grandezze in gioco. • Mediante opportuni accorgimenti tecnologici le tensioni di soglia dei due tipi di transistori possono essere rese uguali e opposte (± 1 V) • A causa di alcune asimmetrie tecnologiche, sono generalmente diversi i fattori di effetto Body ( g ). • Per motivi fisici: 35

36 Evoluzione storica Famiglie Logiche MOS statiche (a rapporto) Logiche n-MOS dinamiche statiche Logiche CMOS dinamiche

III. 3. Logiche CMOS statiche • La tecnologia CMOS (Complementary MOS) è quella che occupa il ruolo più importante nell’intero panorama della moderna microelettronica • Le logiche CMOS, infatti, consentono di ottenere le migliori prestazioni tra tutte le altre: in particolare, basso consumo di potenza (esenti da consumo statico), ampio swing logico e margine di immunità ai disturbi, alte densità di integrazione. • Accanto alle logiche CMOS pienamente complementari (FCMOS), esistono varianti che utilizzano prevalentemente i transistori n. MOS e funzionano in modo dinamico. • La tecnologia CMOS consente l’utilizzo anche di transistori bipolari (anche se con caratteristiche non ottimali) che possono essere sfruttati per pilotare efficamente carichi capacitivi elevati. Questa filosofia ha trovato la sua massima espressione nelle logiche Bi-CMOS. 37

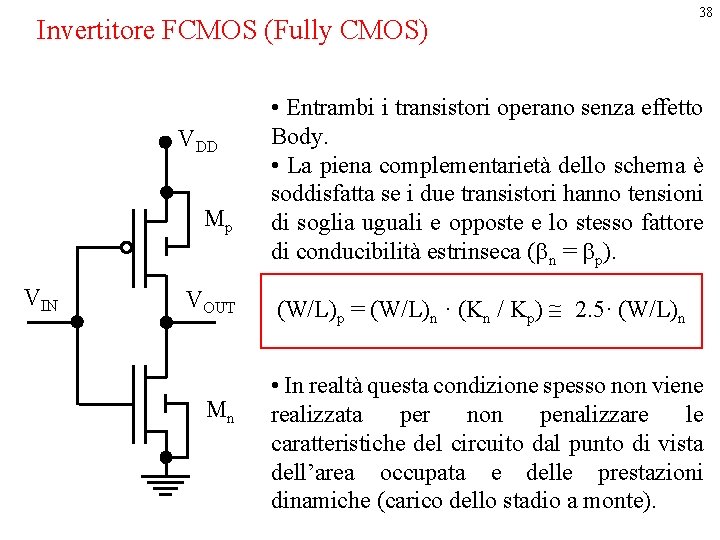

Invertitore FCMOS (Fully CMOS) VDD Mp VIN VOUT Mn 38 • Entrambi i transistori operano senza effetto Body. • La piena complementarietà dello schema è soddisfatta se i due transistori hanno tensioni di soglia uguali e opposte e lo stesso fattore di conducibilità estrinseca (bn = bp). (W/L)p = (W/L)n · (Kn / Kp) @ 2. 5· (W/L)n • In realtà questa condizione spesso non viene realizzata per non penalizzare le caratteristiche del circuito dal punto di vista dell’area occupata e delle prestazioni dinamiche (carico dello stadio a monte).

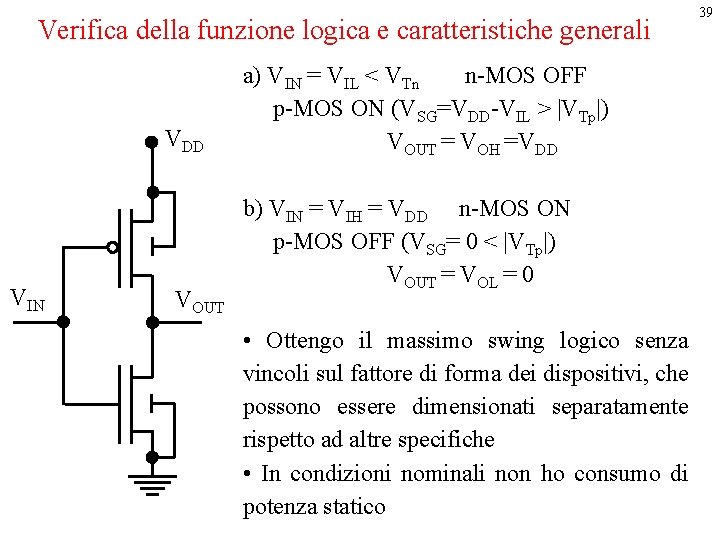

Verifica della funzione logica e caratteristiche generali VDD VIN VOUT a) VIN = VIL < VTn n-MOS OFF p-MOS ON (VSG=VDD-VIL > |VTp|) VOUT = VOH =VDD b) VIN = VIH = VDD n-MOS ON p-MOS OFF (VSG= 0 < |VTp|) VOUT = VOL = 0 • Ottengo il massimo swing logico senza vincoli sul fattore di forma dei dispositivi, che possono essere dimensionati separatamente rispetto ad altre specifiche • In condizioni nominali non ho consumo di potenza statico 39

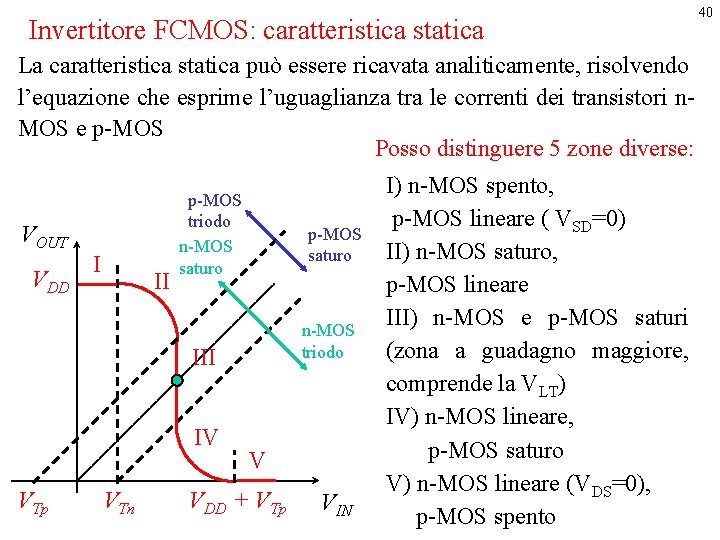

Invertitore FCMOS: caratteristica statica La caratteristica statica può essere ricavata analiticamente, risolvendo l’equazione che esprime l’uguaglianza tra le correnti dei transistori n. MOS e p-MOS Posso distinguere 5 zone diverse: VOUT VDD I II p-MOS triodo n-MOS saturo p-MOS saturo n-MOS triodo III IV VTp VTn V VDD + VTp VIN I) n-MOS spento, p-MOS lineare ( VSD=0) II) n-MOS saturo, p-MOS lineare III) n-MOS e p-MOS saturi (zona a guadagno maggiore, comprende la VLT) IV) n-MOS lineare, p-MOS saturo V) n-MOS lineare (VDS=0), p-MOS spento 40

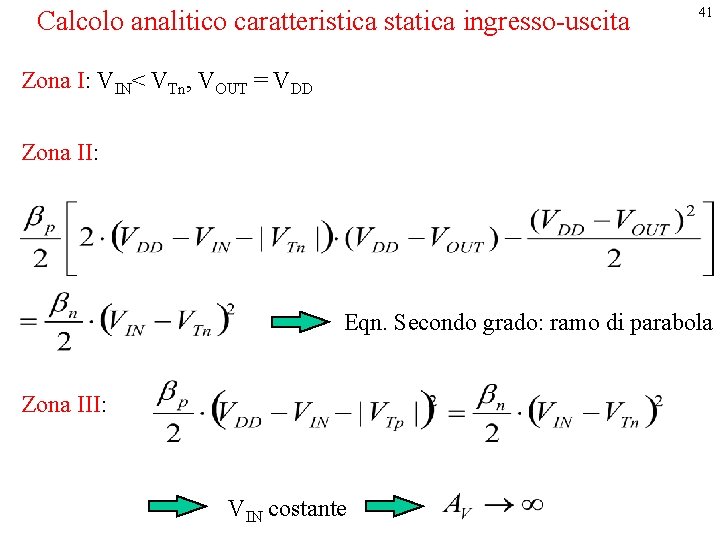

Calcolo analitico caratteristica statica ingresso-uscita 41 Zona I: VIN< VTn, VOUT = VDD Zona II: Eqn. Secondo grado: ramo di parabola Zona III: VIN costante

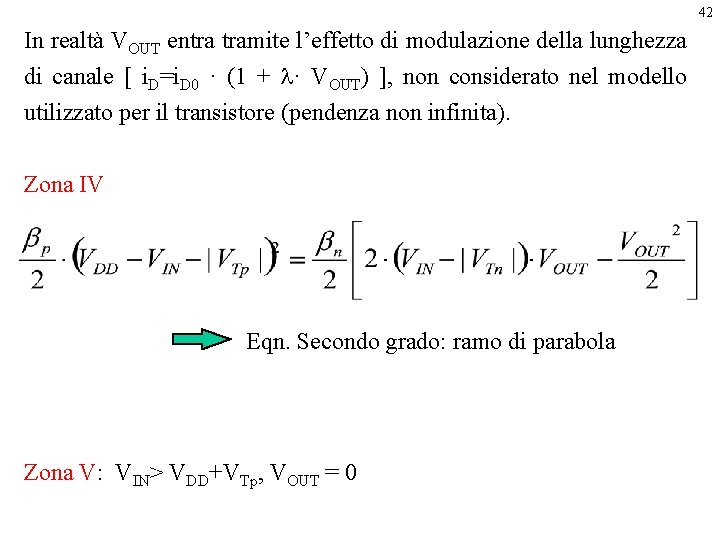

42 In realtà VOUT entra tramite l’effetto di modulazione della lunghezza di canale [ i. D=i. D 0 · (1 + l· VOUT) ], non considerato nel modello utilizzato per il transistore (pendenza non infinita). Zona IV Eqn. Secondo grado: ramo di parabola Zona V: VIN> VDD+VTp, VOUT = 0

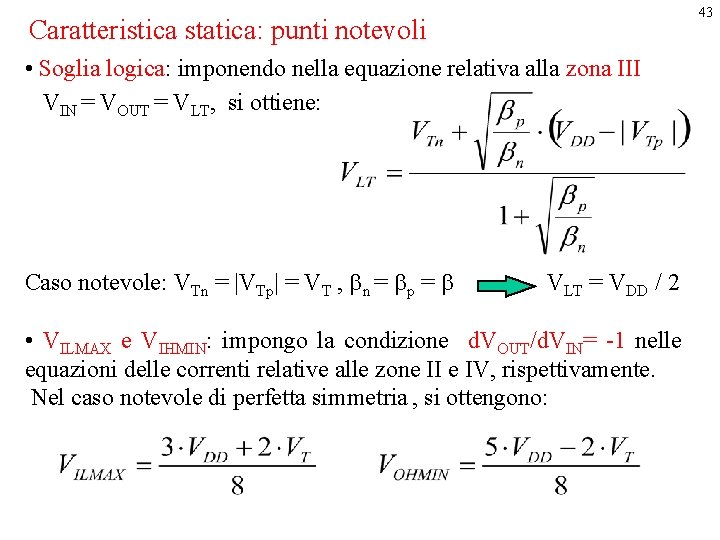

43 Caratteristica statica: punti notevoli • Soglia logica: imponendo nella equazione relativa alla zona III VIN = VOUT = VLT, si ottiene: Caso notevole: VTn = |VTp| = VT , bn = bp = b VLT = VDD / 2 • VILMAX e VIHMIN: impongo la condizione d. VOUT/d. VIN= -1 nelle equazioni delle correnti relative alle zone II e IV, rispettivamente. Nel caso notevole di perfetta simmetria , si ottengono:

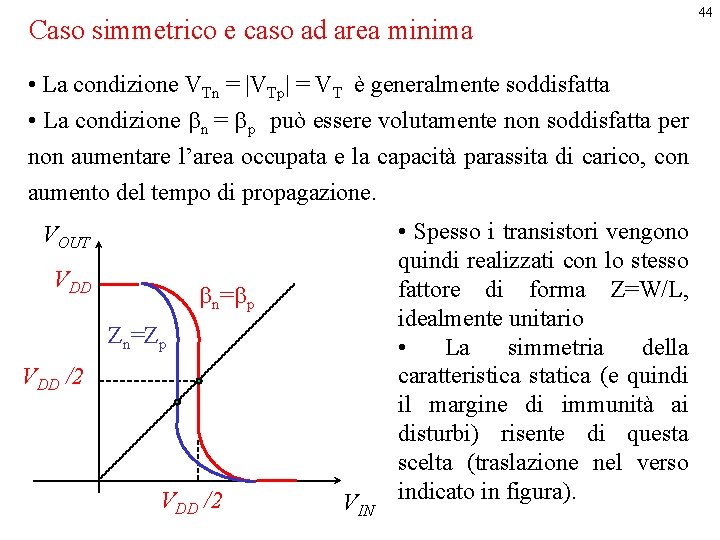

Caso simmetrico e caso ad area minima • La condizione VTn = |VTp| = VT è generalmente soddisfatta • La condizione bn = bp può essere volutamente non soddisfatta per non aumentare l’area occupata e la capacità parassita di carico, con aumento del tempo di propagazione. VOUT VDD bn=bp Zn=Zp VDD /2 VIN • Spesso i transistori vengono quindi realizzati con lo stesso fattore di forma Z=W/L, idealmente unitario • La simmetria della caratteristica statica (e quindi il margine di immunità ai disturbi) risente di questa scelta (traslazione nel verso indicato in figura). 44

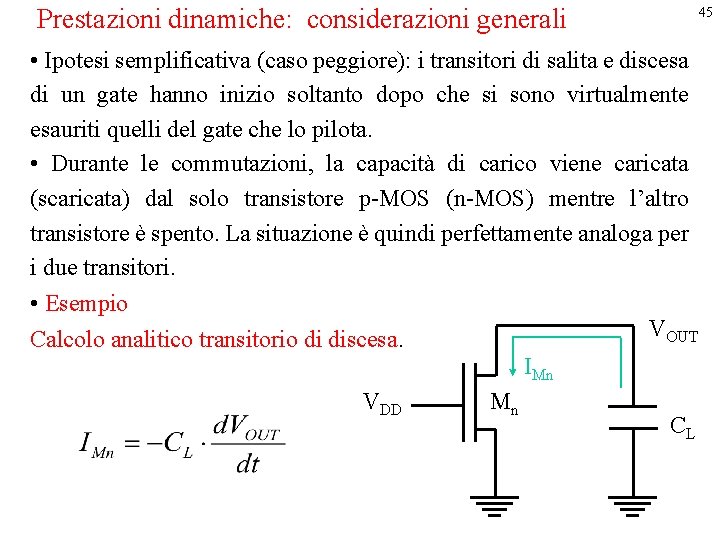

Prestazioni dinamiche: considerazioni generali • Ipotesi semplificativa (caso peggiore): i transitori di salita e discesa di un gate hanno inizio soltanto dopo che si sono virtualmente esauriti quelli del gate che lo pilota. • Durante le commutazioni, la capacità di carico viene caricata (scaricata) dal solo transistore p-MOS (n-MOS) mentre l’altro transistore è spento. La situazione è quindi perfettamente analoga per i due transitori. • Esempio VOUT Calcolo analitico transitorio di discesa. IMn VDD Mn CL 45

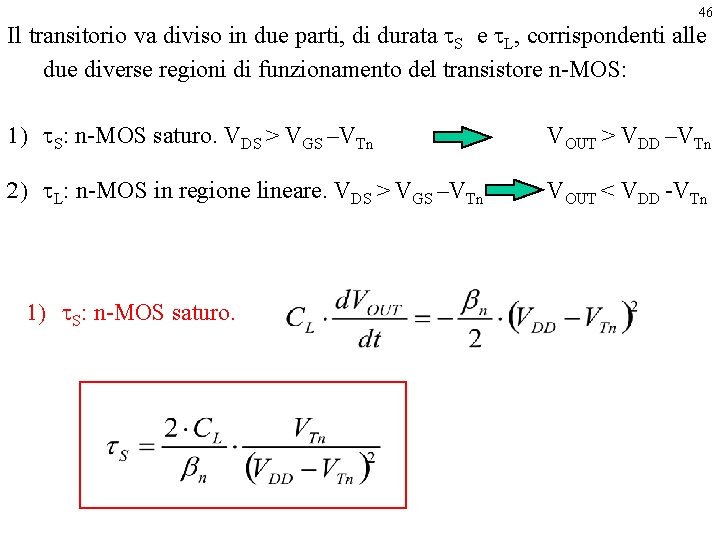

46 Il transitorio va diviso in due parti, di durata t. S e t. L, corrispondenti alle due diverse regioni di funzionamento del transistore n-MOS: 1) t. S: n-MOS saturo. VDS > VGS –VTn VOUT > VDD –VTn 2) t. L: n-MOS in regione lineare. VDS > VGS –VTn VOUT < VDD -VTn 1) t. S: n-MOS saturo.

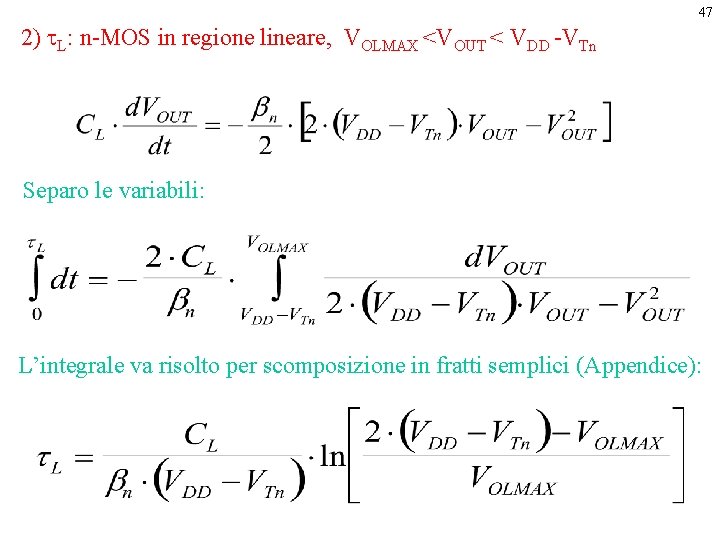

47 2) t. L: n-MOS in regione lineare, VOLMAX <VOUT < VDD -VTn Separo le variabili: L’integrale va risolto per scomposizione in fratti semplici (Appendice):

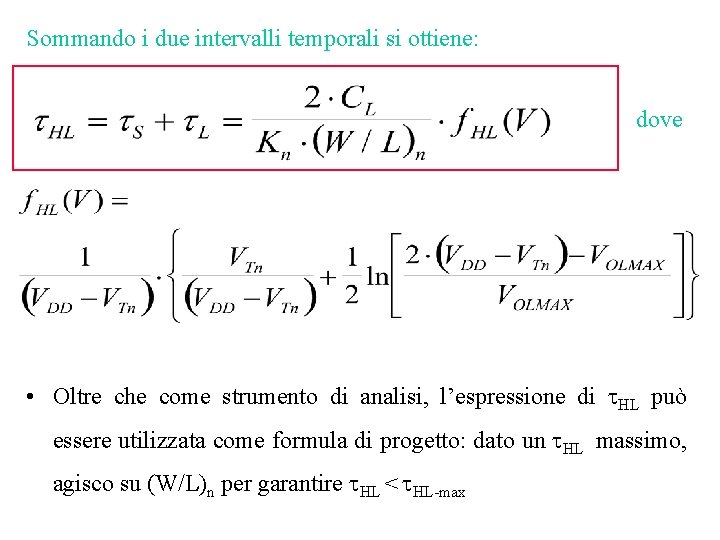

Sommando i due intervalli temporali si ottiene: dove • Oltre che come strumento di analisi, l’espressione di t. HL può essere utilizzata come formula di progetto: dato un t. HL massimo, agisco su (W/L)n per garantire t. HL < t. HL-max

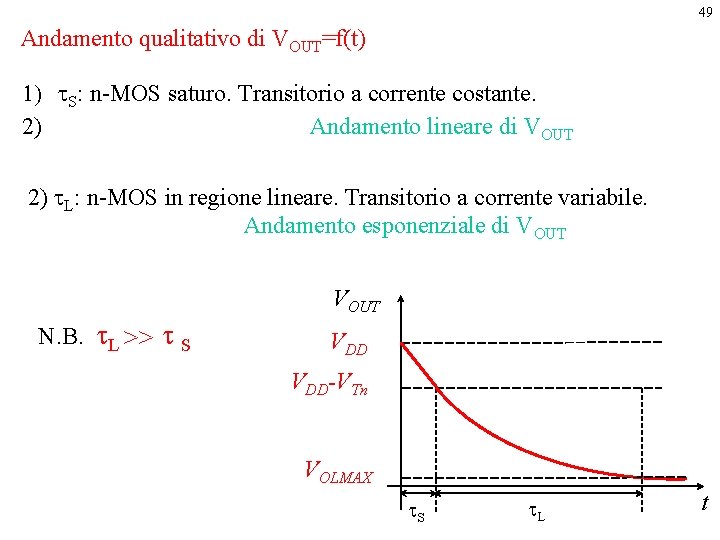

49 Andamento qualitativo di VOUT=f(t) 1) t. S: n-MOS saturo. Transitorio a corrente costante. 2) Andamento lineare di VOUT 2) t. L: n-MOS in regione lineare. Transitorio a corrente variabile. Andamento esponenziale di VOUT N. B. t. L >> t S VOUT VDD-VTn VOLMAX t. S t. L t

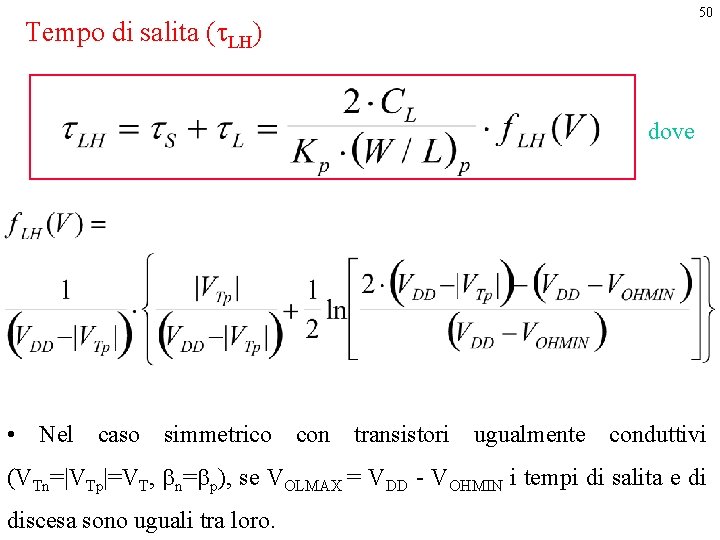

50 Tempo di salita (t. LH) dove • Nel caso simmetrico con transistori ugualmente conduttivi (VTn=|VTp|=VT, bn=bp), se VOLMAX = VDD - VOHMIN i tempi di salita e di discesa sono uguali tra loro.

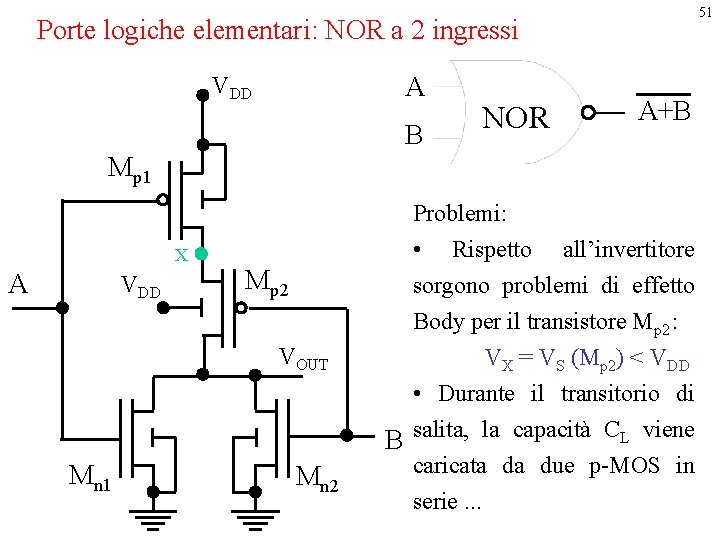

51 Porte logiche elementari: NOR a 2 ingressi A VDD B NOR A+B Mp 1 X A VDD Problemi: • Rispetto all’invertitore sorgono problemi di effetto Mp 2 VOUT Mn 1 Mn 2 Body per il transistore Mp 2 : VX = VS (Mp 2) < VDD • Durante il transitorio di B salita, la capacità CL viene caricata da due p-MOS in serie. . .

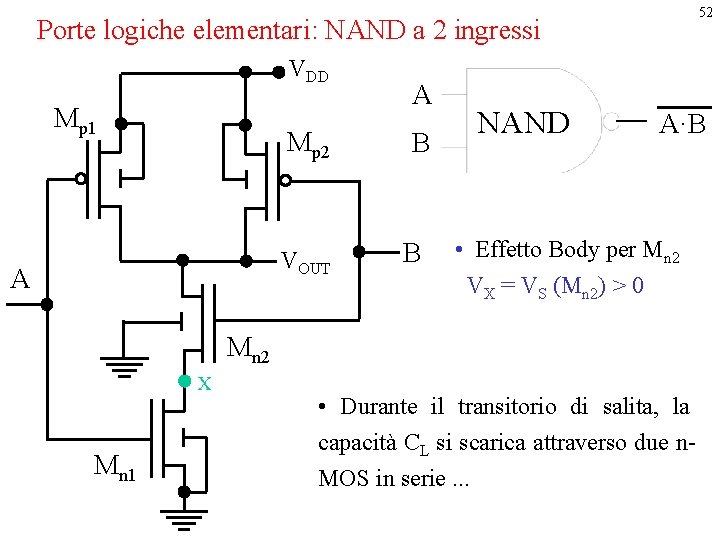

52 Porte logiche elementari: NAND a 2 ingressi VDD Mp 1 Mp 2 VOUT A A B B NAND A·B • Effetto Body per Mn 2 VX = VS (Mn 2) > 0 Mn 2 X Mn 1 • Durante il transitorio di salita, la capacità CL si scarica attraverso due n. MOS in serie. . .

Confronto NAND - NOR • Dal punto di vista statico, non ci sono motivi per preferire un tipo di gate all’altro (gate equivalenti). • Dal punto di vista dinamico, invece, la diversa conducibilità dei due tipi di transistori (Kn > Kp ) fa sì che, a parità di prestazioni, il NAND (n-MOS in serie) occupi meno area del NOR (p-MOS in serie); analogamente, a parità di area occupata il NAND è più veloce del NOR. • Queste considerazioni assumono importanza crescente con l’aumento del numero di ingressi dei circuiti. • Per quanto riguarda l’effetto Body, infine, si osservi che pur essendo generalmente gn > gp , gli svantaggi del NOR vengono compensati solo in parte. 53

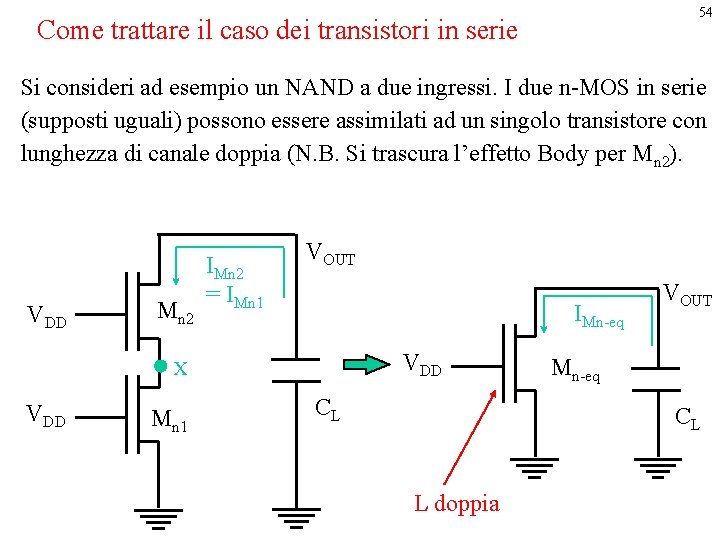

54 Come trattare il caso dei transistori in serie Si consideri ad esempio un NAND a due ingressi. I due n-MOS in serie (supposti uguali) possono essere assimilati ad un singolo transistore con lunghezza di canale doppia (N. B. Si trascura l’effetto Body per Mn 2). VDD Mn 2 IMn 2 = IMn 1 VOUT IMn-eq VDD X VDD Mn 1 CL VOUT Mn-eq CL L doppia

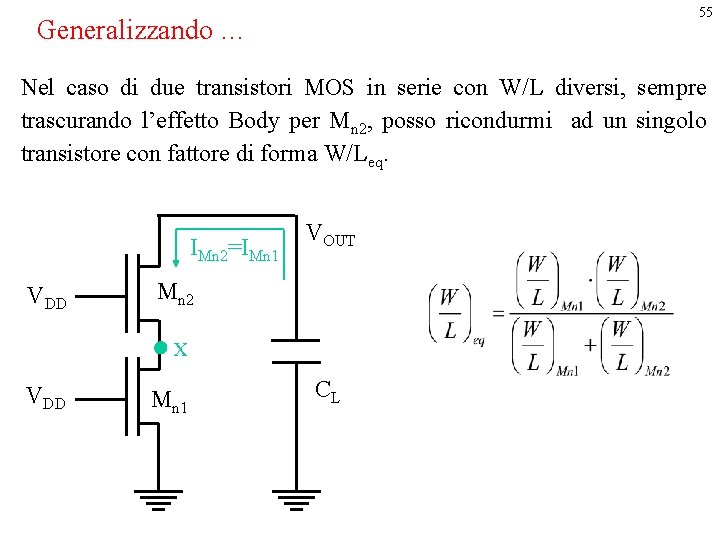

55 Generalizzando … Nel caso di due transistori MOS in serie con W/L diversi, sempre trascurando l’effetto Body per Mn 2, posso ricondurmi ad un singolo transistore con fattore di forma W/Leq. IMn 2=IMn 1 VDD VOUT Mn 2 X VDD Mn 1 CL

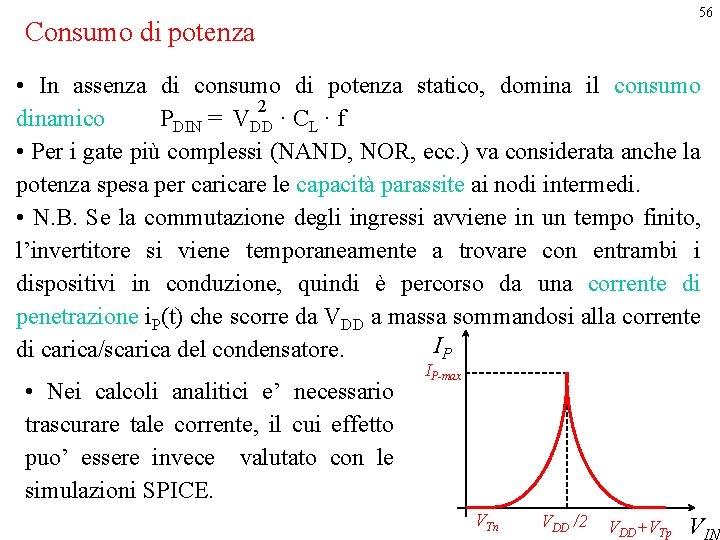

56 Consumo di potenza • In assenza di consumo di potenza statico, domina il consumo 2 dinamico PDIN = VDD · CL · f • Per i gate più complessi (NAND, NOR, ecc. ) va considerata anche la potenza spesa per caricare le capacità parassite ai nodi intermedi. • N. B. Se la commutazione degli ingressi avviene in un tempo finito, l’invertitore si viene temporaneamente a trovare con entrambi i dispositivi in conduzione, quindi è percorso da una corrente di penetrazione i. P(t) che scorre da VDD a massa sommandosi alla corrente IP di carica/scarica del condensatore. • Nei calcoli analitici e’ necessario trascurare tale corrente, il cui effetto puo’ essere invece valutato con le simulazioni SPICE. IP-max VTn VDD /2 VDD+VTp VIN

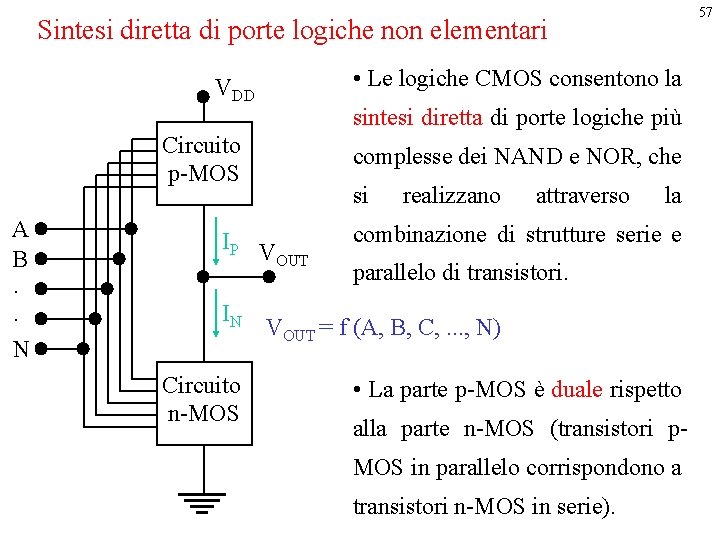

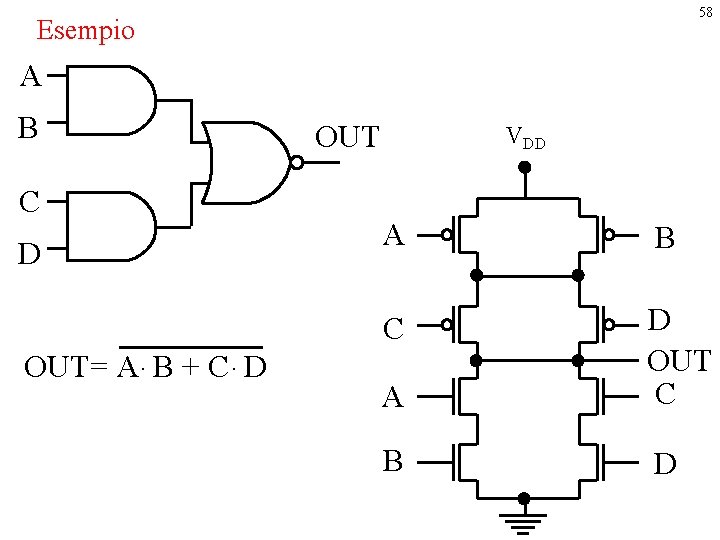

57 Sintesi diretta di porte logiche non elementari • Le logiche CMOS consentono la VDD sintesi diretta di porte logiche più Circuito p-MOS A B. . N complesse dei NAND e NOR, che si IP V OUT IN Circuito n-MOS realizzano attraverso la combinazione di strutture serie e parallelo di transistori. VOUT = f (A, B, C, . . . , N) • La parte p-MOS è duale rispetto alla parte n-MOS (transistori p. MOS in parallelo corrispondono a transistori n-MOS in serie).

58 Esempio A B C D OUT= A· B + C· D OUT VDD A B C A D OUT C B D

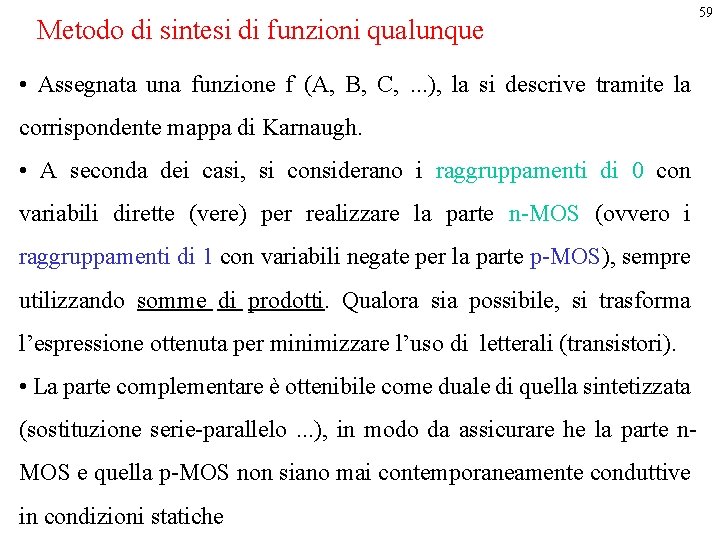

Metodo di sintesi di funzioni qualunque • Assegnata una funzione f (A, B, C, . . . ), la si descrive tramite la corrispondente mappa di Karnaugh. • A seconda dei casi, si considerano i raggruppamenti di 0 con variabili dirette (vere) per realizzare la parte n-MOS (ovvero i raggruppamenti di 1 con variabili negate per la parte p-MOS), sempre utilizzando somme di prodotti. Qualora sia possibile, si trasforma l’espressione ottenuta per minimizzare l’uso di letterali (transistori). • La parte complementare è ottenibile come duale di quella sintetizzata (sostituzione serie-parallelo. . . ), in modo da assicurare he la parte n. MOS e quella p-MOS non siano mai contemporaneamente conduttive in condizioni statiche 59

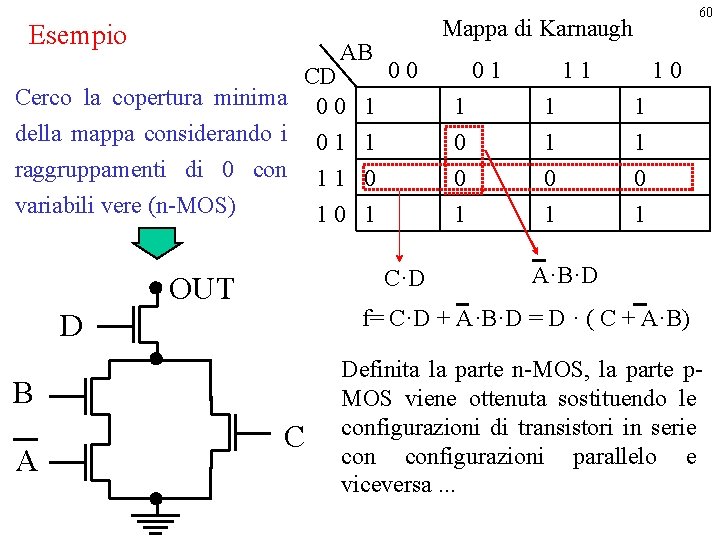

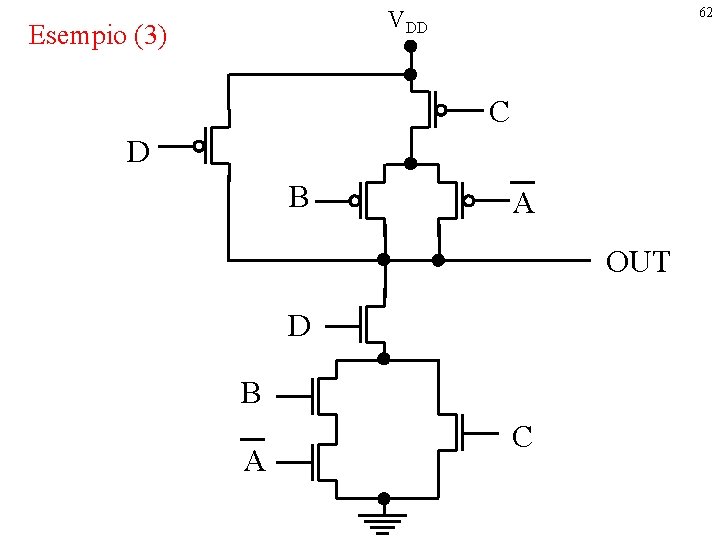

Esempio Mappa di Karnaugh AB 00 CD Cerco la copertura minima 0 0 1 della mappa considerando i 0 1 1 raggruppamenti di 0 con 1 1 0 variabili vere (n-MOS) 10 1 C·D OUT 01 11 10 1 1 1 1 0 1 0 1 A·B·D f= C·D + A·B·D = D · ( C + A·B) D B A 60 C Definita la parte n-MOS, la parte p. MOS viene ottenuta sostituendo le configurazioni di transistori in serie configurazioni parallelo e viceversa. . .

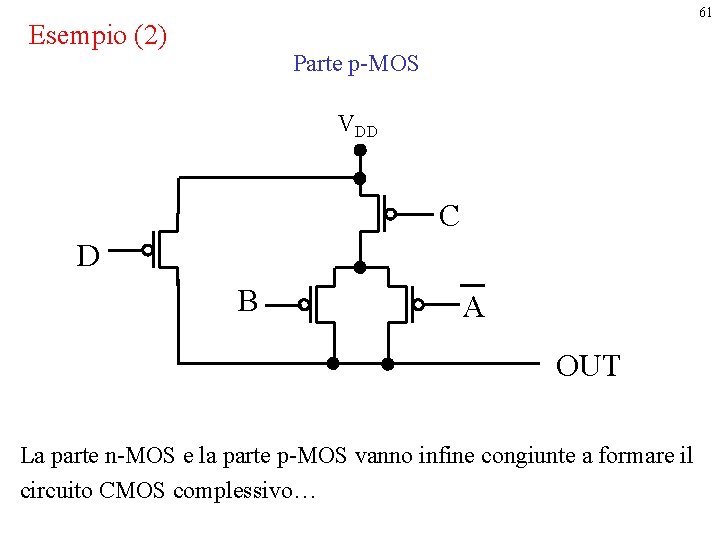

61 Esempio (2) Parte p-MOS VDD C D B A OUT La parte n-MOS e la parte p-MOS vanno infine congiunte a formare il circuito CMOS complessivo…

62 VDD Esempio (3) C D B A OUT D B A C

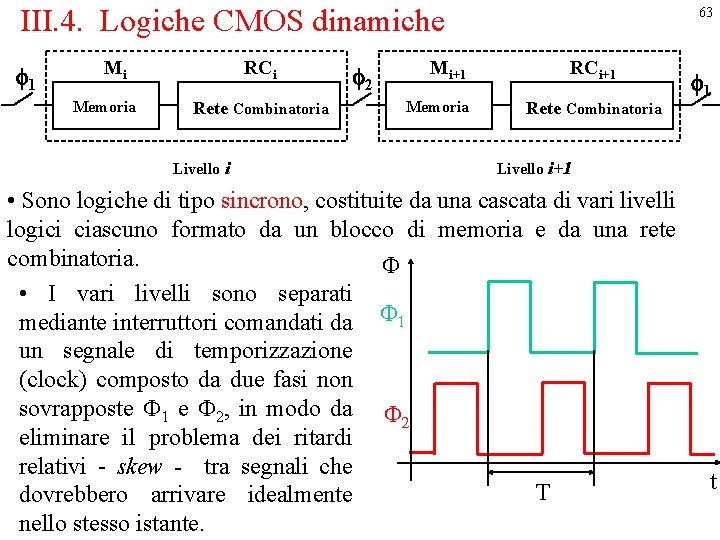

III. 4. Logiche CMOS dinamiche f 1 Mi Memoria RCi Rete Combinatoria Livello i f 2 Mi+1 Memoria 63 RCi+1 Rete Combinatoria f 1 Livello i+1 • Sono logiche di tipo sincrono, costituite da una cascata di vari livelli logici ciascuno formato da un blocco di memoria e da una rete combinatoria. F • I vari livelli sono separati mediante interruttori comandati da F 1 un segnale di temporizzazione (clock) composto da due fasi non sovrapposte F 1 e F 2, in modo da F 2 eliminare il problema dei ritardi relativi - skew - tra segnali che T dovrebbero arrivare idealmente nello stesso istante. t

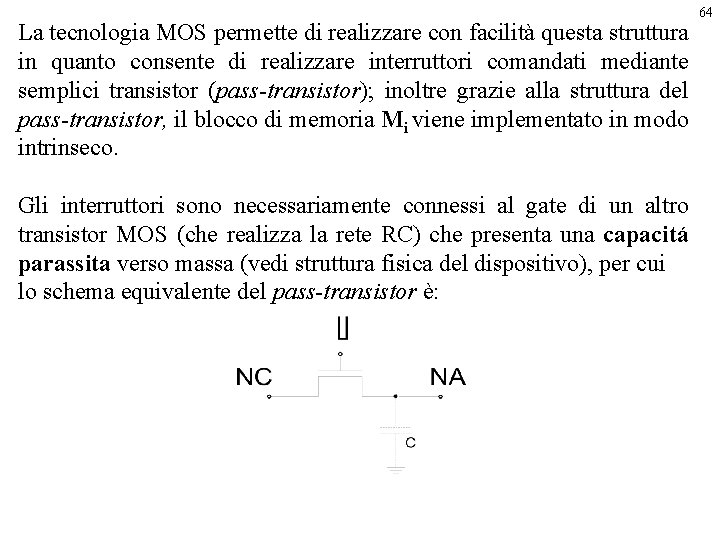

La tecnologia MOS permette di realizzare con facilità questa struttura in quanto consente di realizzare interruttori comandati mediante semplici transistor (pass-transistor); inoltre grazie alla struttura del pass-transistor, il blocco di memoria Mi viene implementato in modo intrinseco. Gli interruttori sono necessariamente connessi al gate di un altro transistor MOS (che realizza la rete RC) che presenta una capacitá parassita verso massa (vedi struttura fisica del dispositivo), per cui lo schema equivalente del pass-transistor è: 64

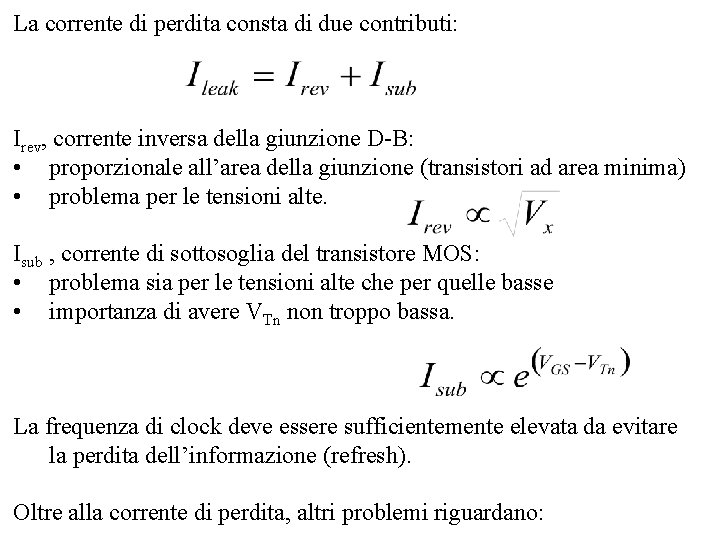

65 Non idealità del pass-transistor n-MOS In realtà il pass-transistor non é un interruttore ideale: ha una resistenza non nulla quando e’ acceso (logiche dinamiche piu’ lente delle statiche) ed inoltre ha una corrente di perdita quando e’ spento che puo’ scaricare la capacità parassita Cx degradando l’informazione memorizzata sul nodo ad alta impedenza. Ileak Isub Irev Giunzione D-B Cj CX

La corrente di perdita consta di due contributi: Irev, corrente inversa della giunzione D-B: • proporzionale all’area della giunzione (transistori ad area minima) • problema per le tensioni alte. Isub , corrente di sottosoglia del transistore MOS: • problema sia per le tensioni alte che per quelle basse • importanza di avere VTn non troppo bassa. La frequenza di clock deve essere sufficientemente elevata da evitare la perdita dell’informazione (refresh). Oltre alla corrente di perdita, altri problemi riguardano:

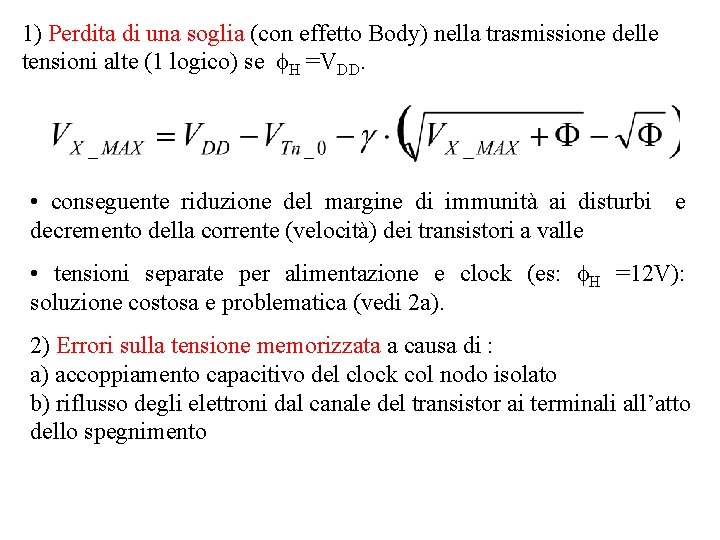

1) Perdita di una soglia (con effetto Body) nella trasmissione delle tensioni alte (1 logico) se H =VDD. • conseguente riduzione del margine di immunità ai disturbi e decremento della corrente (velocità) dei transistori a valle • tensioni separate per alimentazione e clock (es: H =12 V): soluzione costosa e problematica (vedi 2 a). 2) Errori sulla tensione memorizzata a causa di : a) accoppiamento capacitivo del clock col nodo isolato b) riflusso degli elettroni dal canale del transistor ai terminali all’atto dello spegnimento

F CA CB VIN DQ DQ a) Partitore capacitivo … b) FH VX CX FL FT t

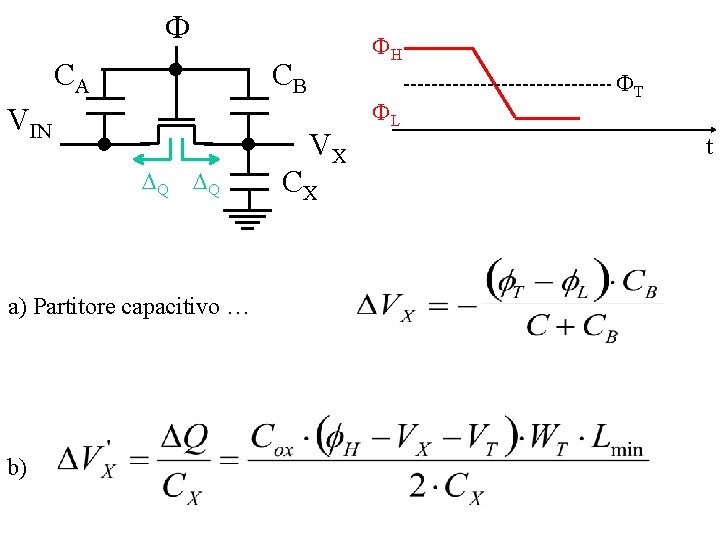

69 Transfer gate CMOS Simbolo F VIN IX VX CX F Svantaggio: • servono due tensioni di comando complementari. Vantaggi: • trasmissione delle tensioni alte senza perdita di una soglia rispetto a VDD (p-MOS sempre acceso) • maggiore velocità di trasmissione dei segnali (transistori in parallelo, corrente maggiore) • dato che F commutano in senso opposto, gli effetti del loro accoppiamento col nodo X isolato si cancellano (in prima approx. ) • i riflussi di elettroni e lacune dal canale al nodo X isolato si compensano in larga misura

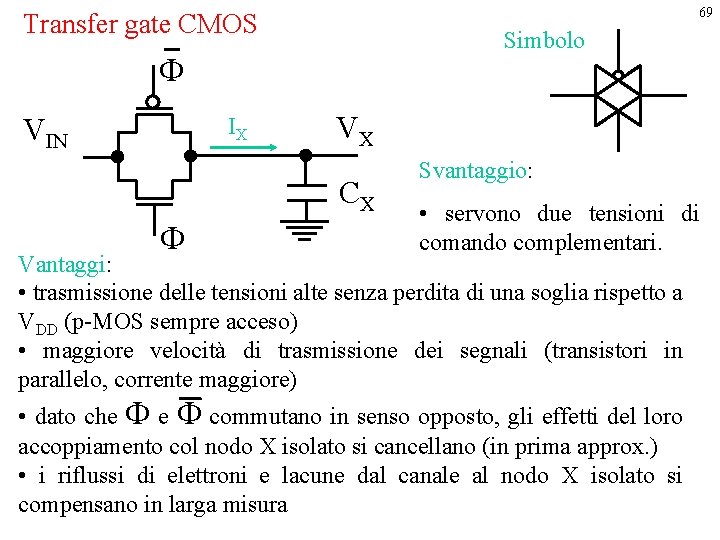

Analisi comportamento dinamico (trasferimento 1 logico). 0 VDD VX A seconda del valore di VX si possono distinguere tre regioni di funzionamento: Regione 1 n-MOS saturo p-MOS saturo VDD 0 Regione 2 Regione 3 n-MOS saturo n-MOS spento p-MOS lineare |VTp| VDD-VTn VDD La resistenza equivalente del transfer gate CMOS puo’ essere calcolata come parallelo tra la resistenza del transistore n (Rn) e quella del transistore p (Rp). VX

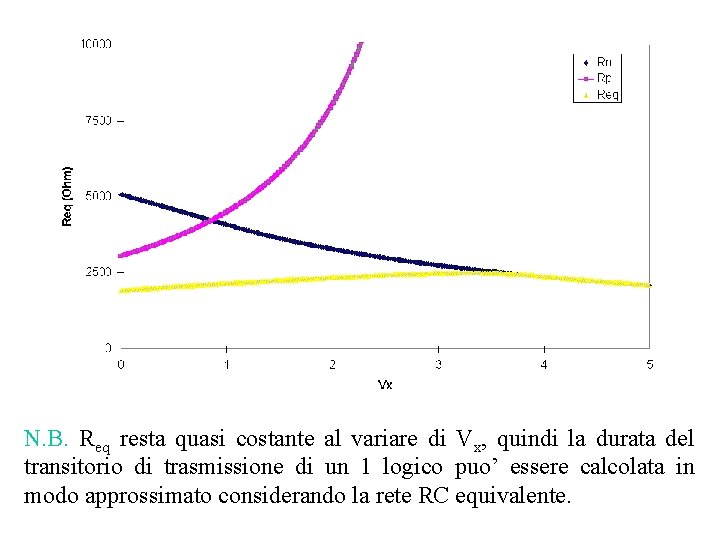

N. B. Req resta quasi costante al variare di Vx, quindi la durata del transitorio di trasmissione di un 1 logico puo’ essere calcolata in modo approssimato considerando la rete RC equivalente.

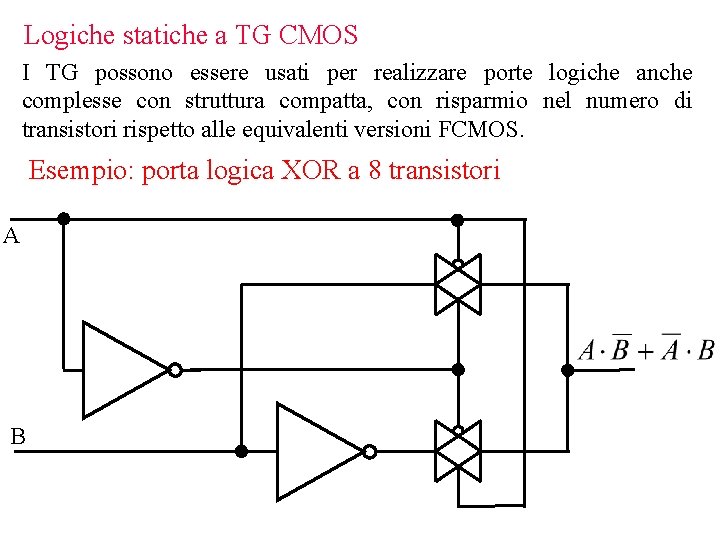

Logiche statiche a TG CMOS I TG possono essere usati per realizzare porte logiche anche complesse con struttura compatta, con risparmio nel numero di transistori rispetto alle equivalenti versioni FCMOS. Esempio: porta logica XOR a 8 transistori A B

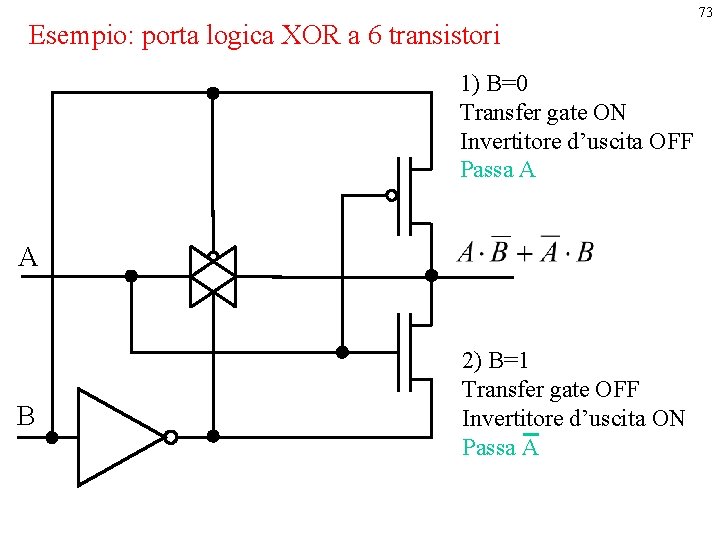

Esempio: porta logica XOR a 6 transistori 1) B=0 Transfer gate ON Invertitore d’uscita OFF Passa A A B 2) B=1 Transfer gate OFF Invertitore d’uscita ON Passa A 73

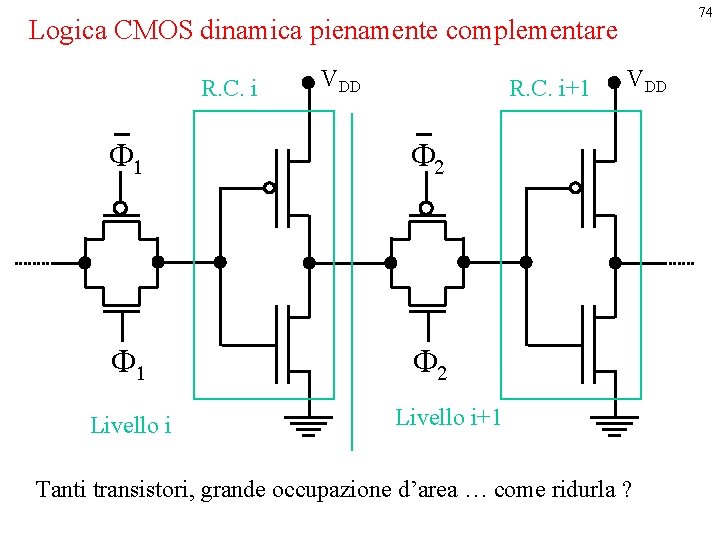

74 Logica CMOS dinamica pienamente complementare R. C. i VDD R. C. i+1 F 2 F 1 F 2 Livello i VDD Livello i+1 Tanti transistori, grande occupazione d’area … come ridurla ?

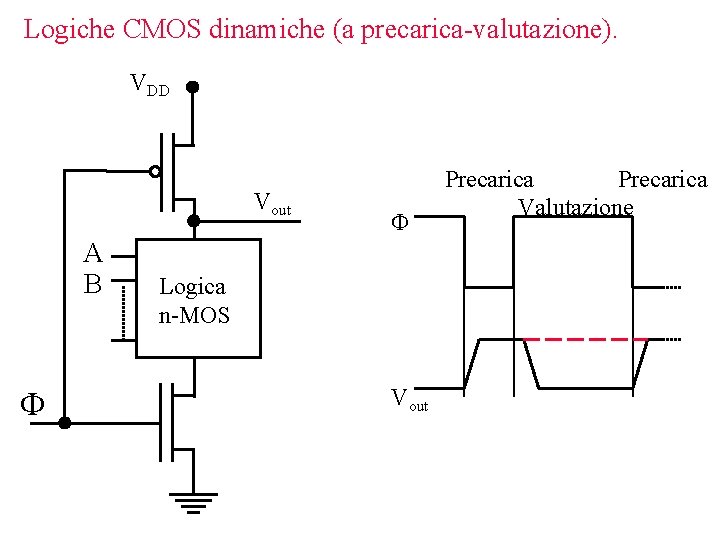

Logiche CMOS dinamiche (a precarica-valutazione). VDD Vout A B F F Logica n-MOS Vout Precarica Valutazione

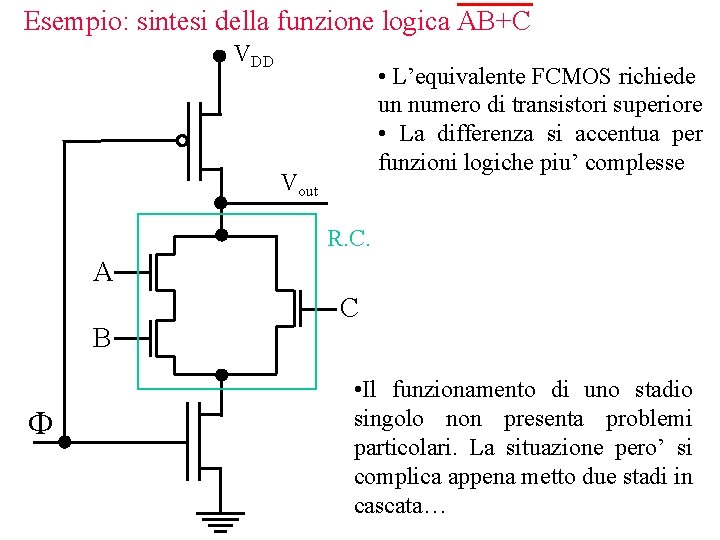

Esempio: sintesi della funzione logica AB+C VDD • L’equivalente FCMOS richiede un numero di transistori superiore • La differenza si accentua per funzioni logiche piu’ complesse Vout R. C. A B F C • Il funzionamento di uno stadio singolo non presenta problemi particolari. La situazione pero’ si complica appena metto due stadi in cascata…

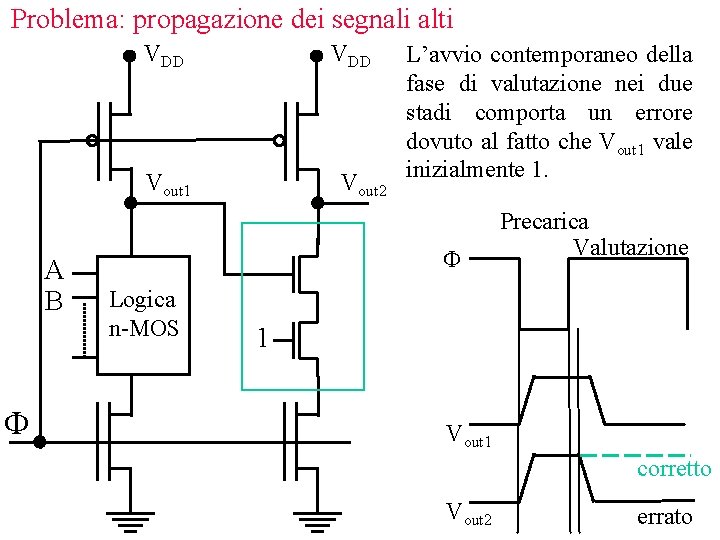

Problema: propagazione dei segnali alti VDD Vout 1 A B F Vout 2 L’avvio contemporaneo della fase di valutazione nei due stadi comporta un errore dovuto al fatto che Vout 1 vale inizialmente 1. F Logica n-MOS Precarica Valutazione 1 Vout 1 corretto Vout 2 errato

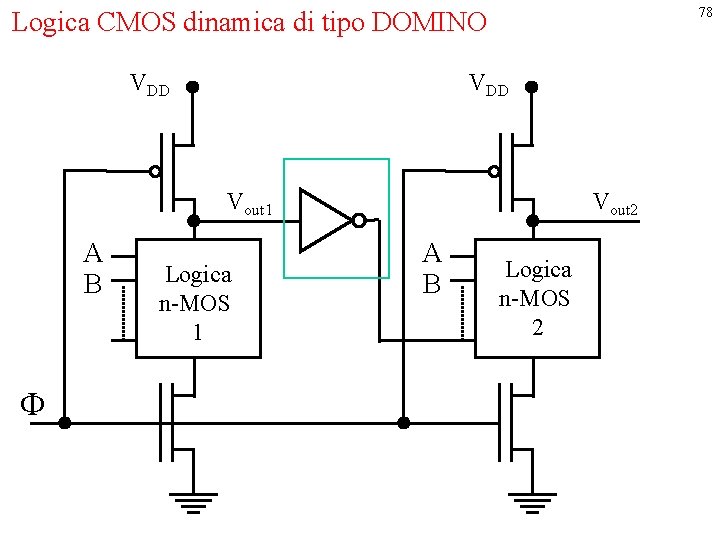

78 Logica CMOS dinamica di tipo DOMINO VDD Vout 1 A B F Logica n-MOS 1 Vout 2 A B Logica n-MOS 2

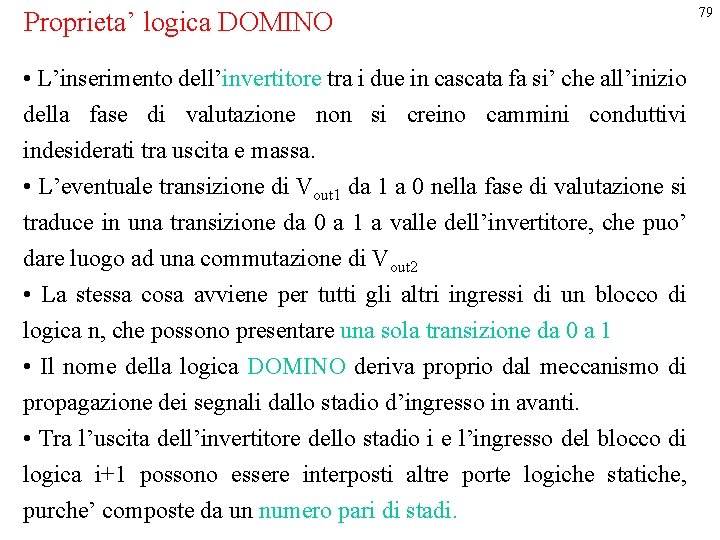

Proprieta’ logica DOMINO • L’inserimento dell’invertitore tra i due in cascata fa si’ che all’inizio della fase di valutazione non si creino cammini conduttivi indesiderati tra uscita e massa. • L’eventuale transizione di Vout 1 da 1 a 0 nella fase di valutazione si traduce in una transizione da 0 a 1 a valle dell’invertitore, che puo’ dare luogo ad una commutazione di Vout 2 • La stessa cosa avviene per tutti gli altri ingressi di un blocco di logica n, che possono presentare una sola transizione da 0 a 1 • Il nome della logica DOMINO deriva proprio dal meccanismo di propagazione dei segnali dallo stadio d’ingresso in avanti. • Tra l’uscita dell’invertitore dello stadio i e l’ingresso del blocco di logica i+1 possono essere interposti altre porte logiche statiche, purche’ composte da un numero pari di stadi. 79

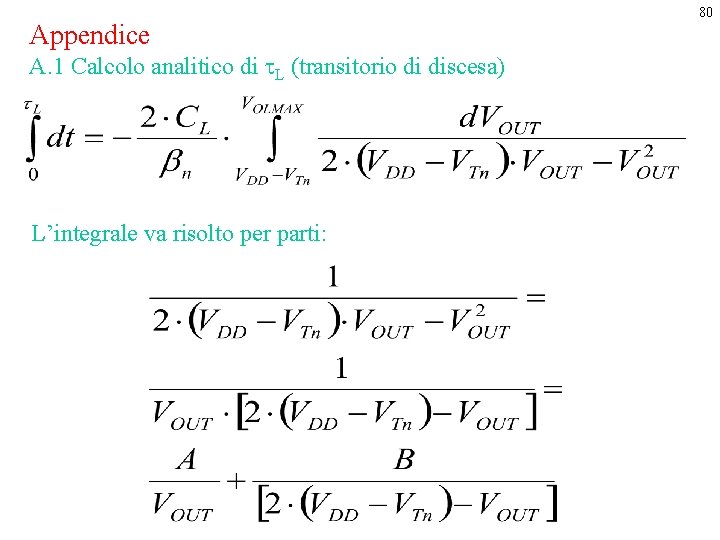

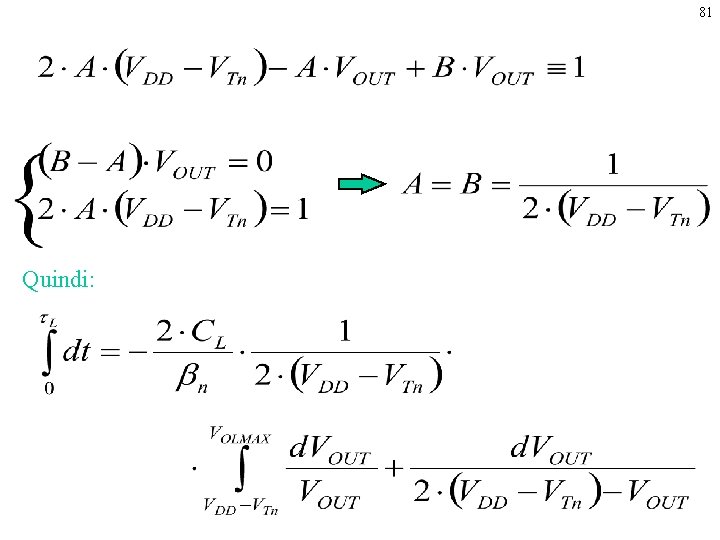

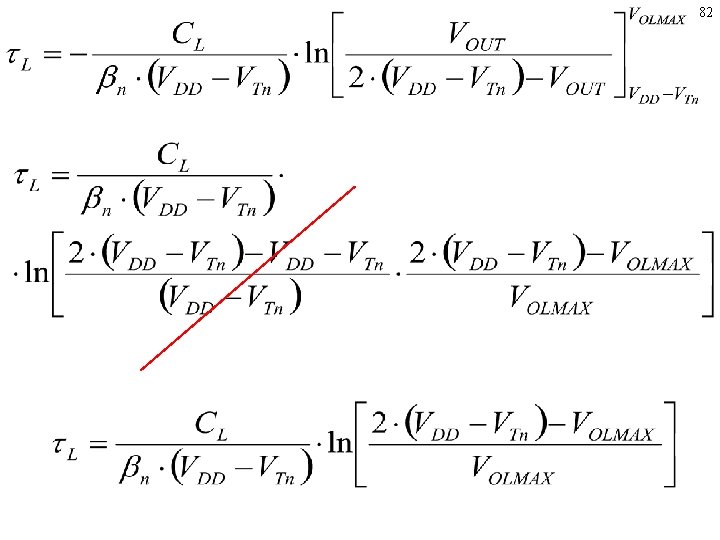

Appendice A. 1 Calcolo analitico di t. L (transitorio di discesa) L’integrale va risolto per parti: 80

81 Quindi:

82

- Slides: 82