FVTX High Multiplicity Trigger for Run 15 Toru

- Slides: 22

FVTX High Multiplicity Trigger for Run 15 Toru Nagashima, Yomei Fukushima Itaru Nakagawa Feb. 23 Rad. Lab meeting 1

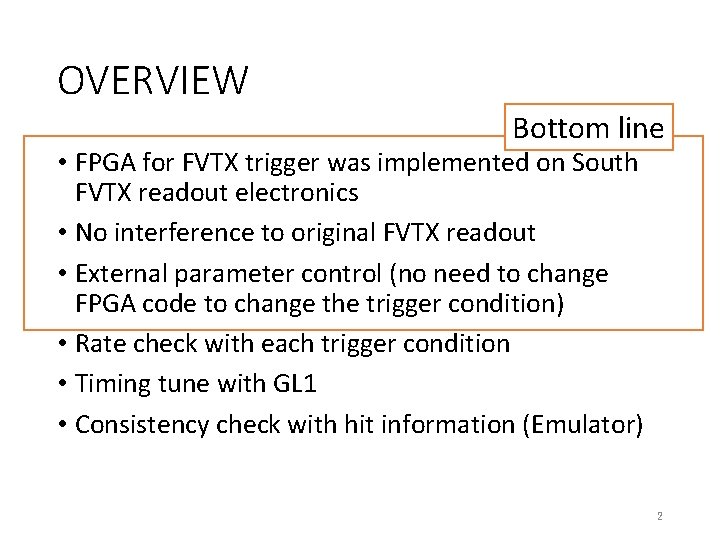

OVERVIEW Bottom line • FPGA for FVTX trigger was implemented on South FVTX readout electronics • No interference to original FVTX readout • External parameter control (no need to change FPGA code to change the trigger condition) • Rate check with each trigger condition • Timing tune with GL 1 • Consistency check with hit information (Emulator) 2

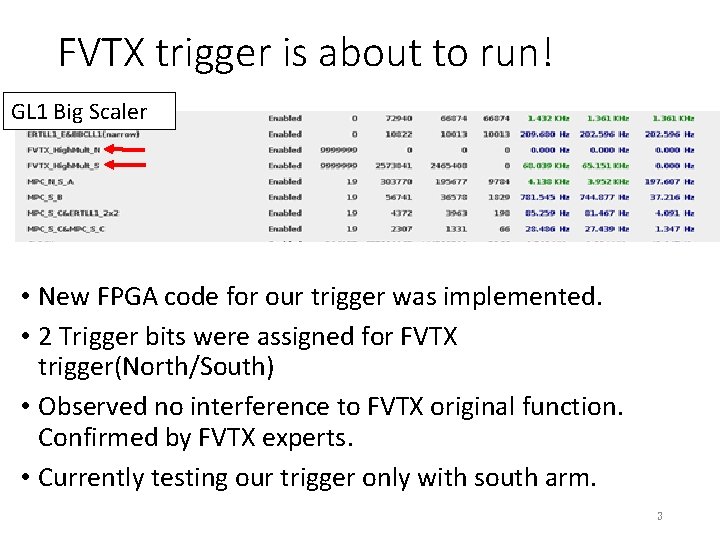

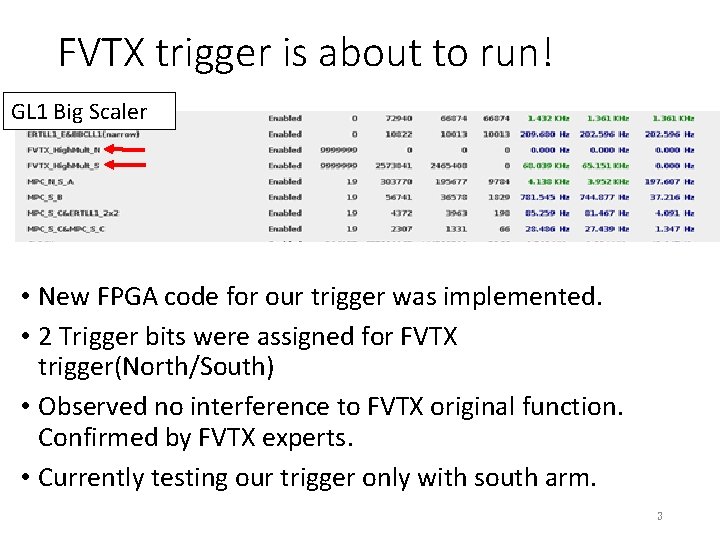

FVTX trigger is about to run! GL 1 Big Scaler • New FPGA code for our trigger was implemented. • 2 Trigger bits were assigned for FVTX trigger(North/South) • Observed no interference to FVTX original function. Confirmed by FVTX experts. • Currently testing our trigger only with south arm. 3

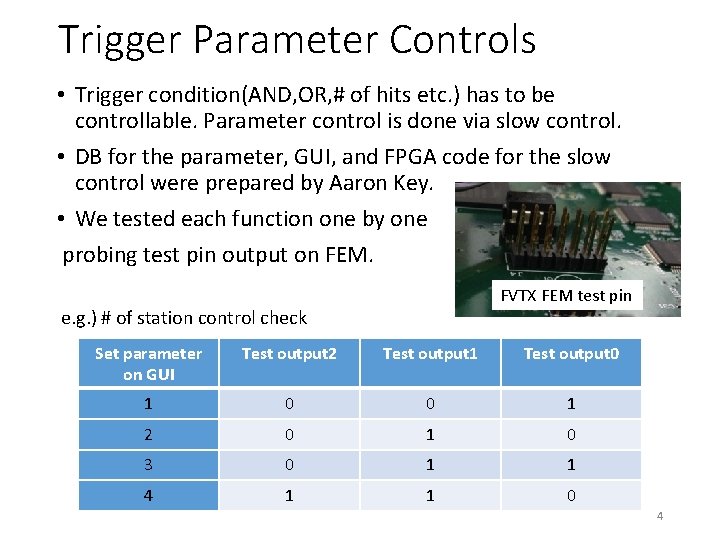

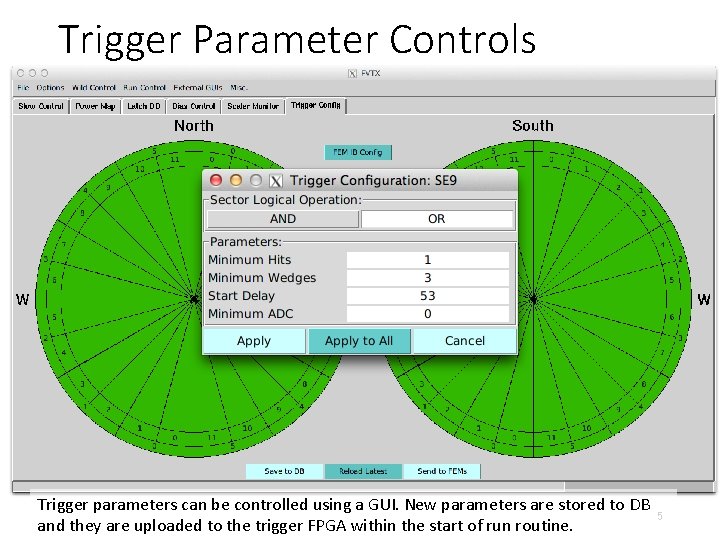

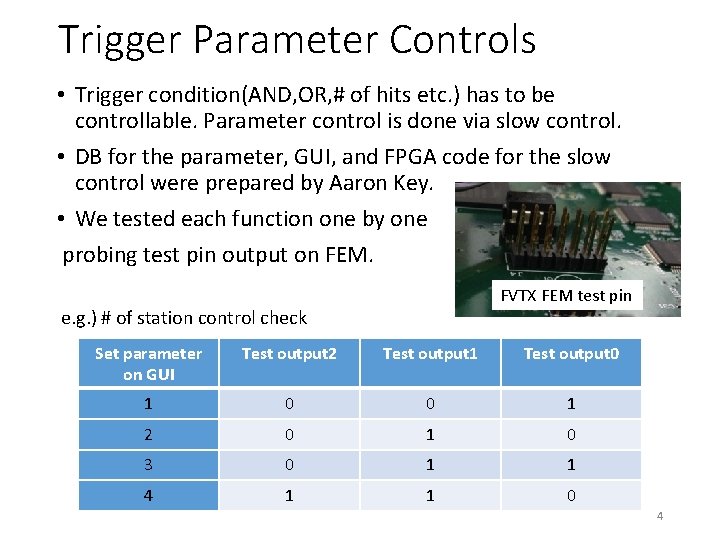

Trigger Parameter Controls • Trigger condition(AND, OR, # of hits etc. ) has to be controllable. Parameter control is done via slow control. • DB for the parameter, GUI, and FPGA code for the slow control were prepared by Aaron Key. • We tested each function one by one probing test pin output on FEM. FVTX FEM test pin e. g. ) # of station control check Set parameter on GUI Test output 2 Test output 1 Test output 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 1 0 4

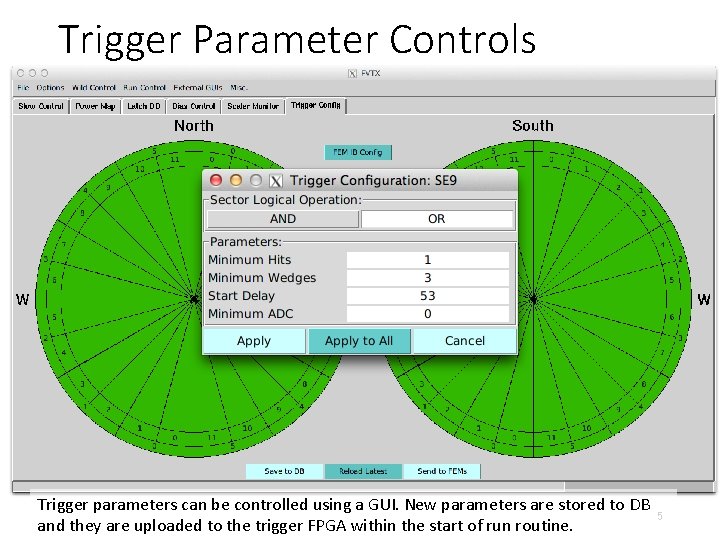

Trigger Parameter Controls Trigger parameters can be controlled using a GUI. New parameters are stored to DB and they are uploaded to the trigger FPGA within the start of run routine. 5

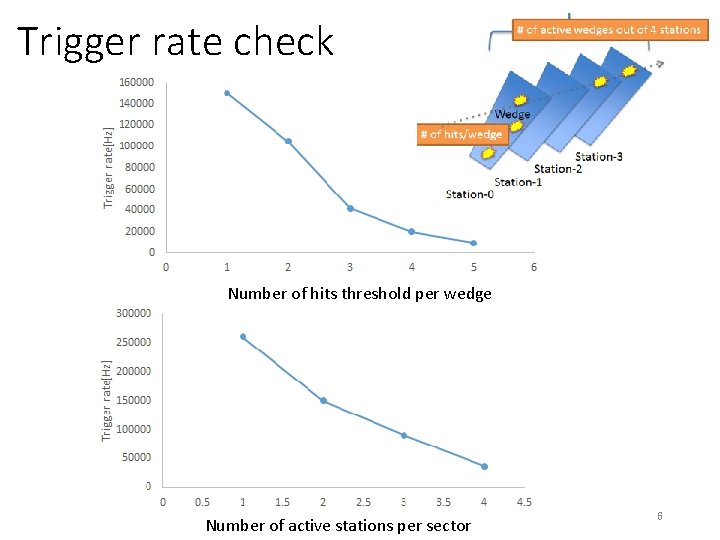

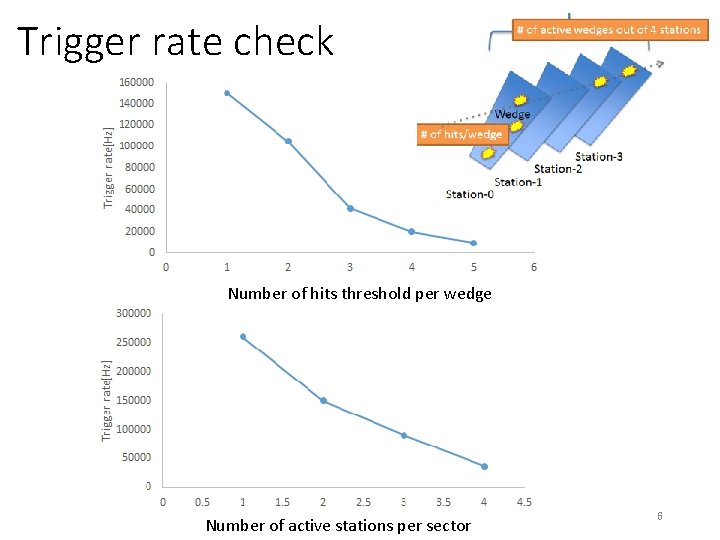

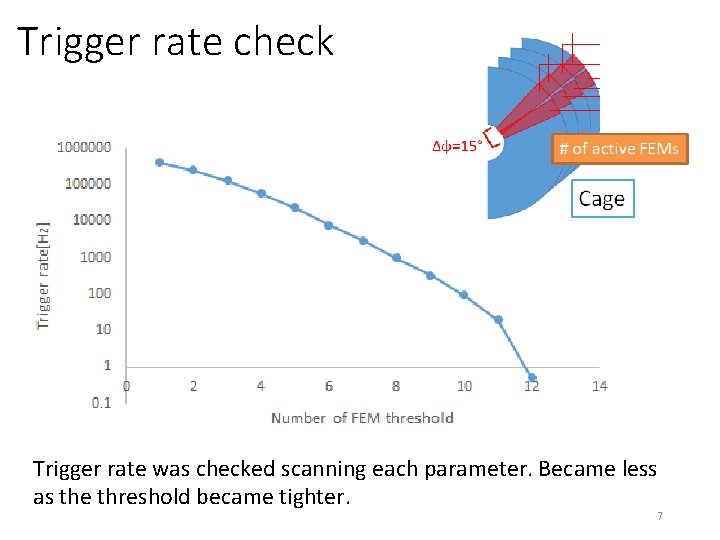

Trigger rate check Number of hits threshold per wedge Number of active stations per sector 6

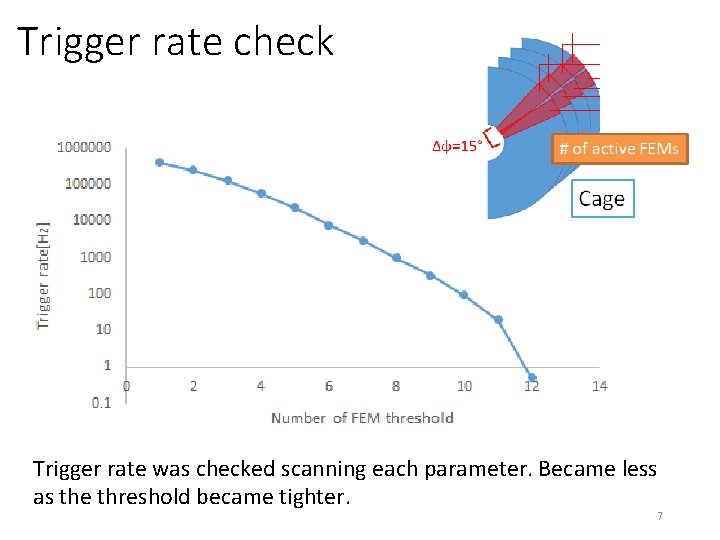

Trigger rate check Trigger rate was checked scanning each parameter. Became less as the threshold became tighter. 7

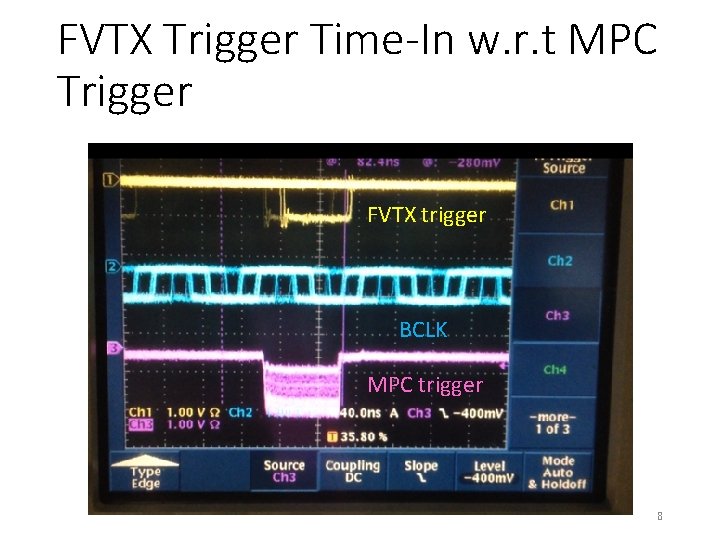

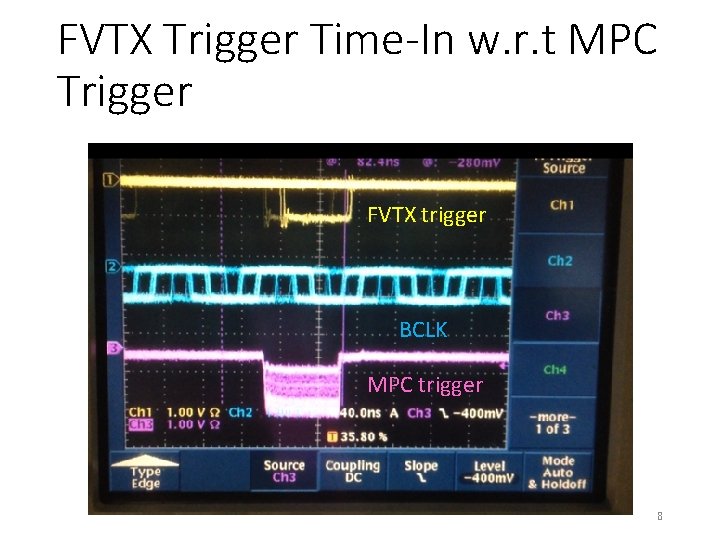

FVTX Trigger Time-In w. r. t MPC Trigger FVTX trigger BCLK MPC trigger 8

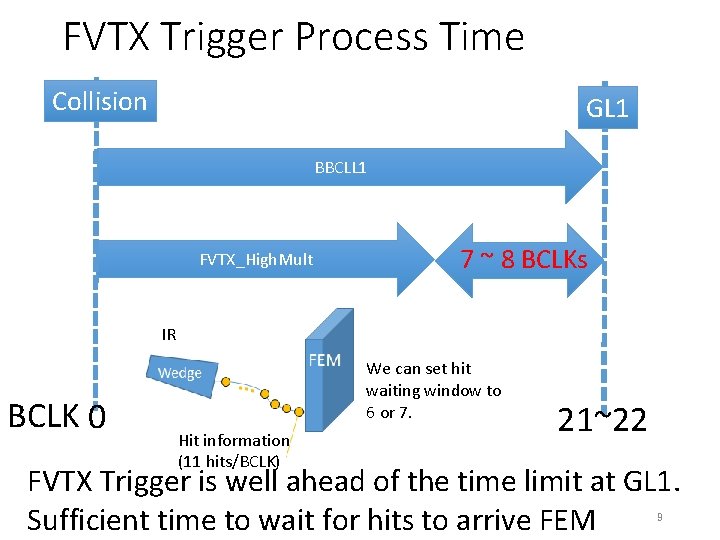

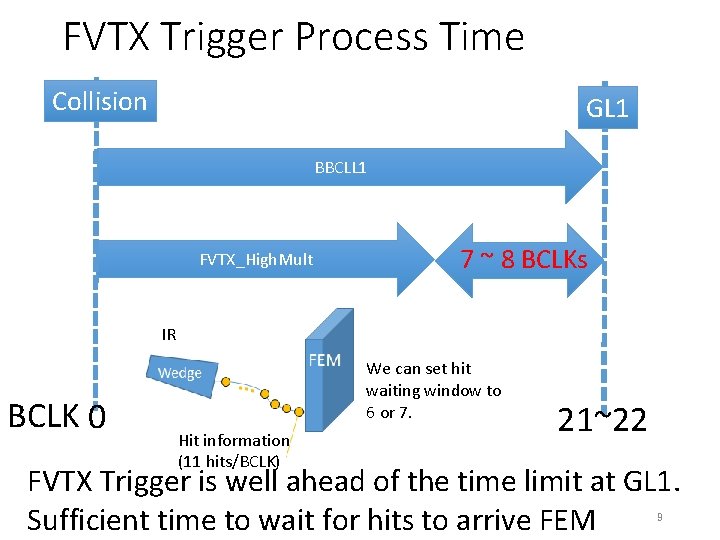

FVTX Trigger Process Time Collision GL 1 BBCLL 1 FVTX_High. Mult 7 ~ 8 BCLKs IR BCLK 0 We can set hit waiting window to 6 or 7. Hit information (11 hits/BCLK) 21~22 FVTX Trigger is well ahead of the time limit at GL 1. Sufficient time to wait for hits to arrive FEM 9

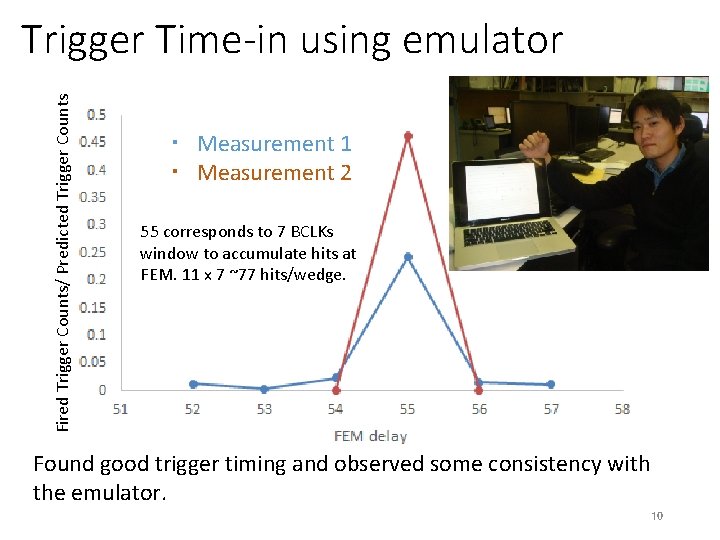

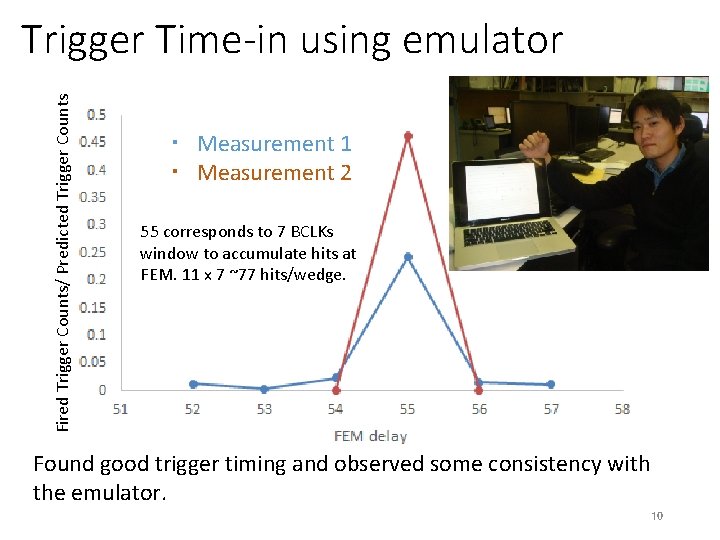

Fired Trigger Counts/ Predicted Trigger Counts Trigger Time-in using emulator ・ Measurement 1 ・ Measurement 2 55 corresponds to 7 BCLKs window to accumulate hits at FEM. 11 x 7 ~77 hits/wedge. Found good trigger timing and observed some consistency with the emulator. 10

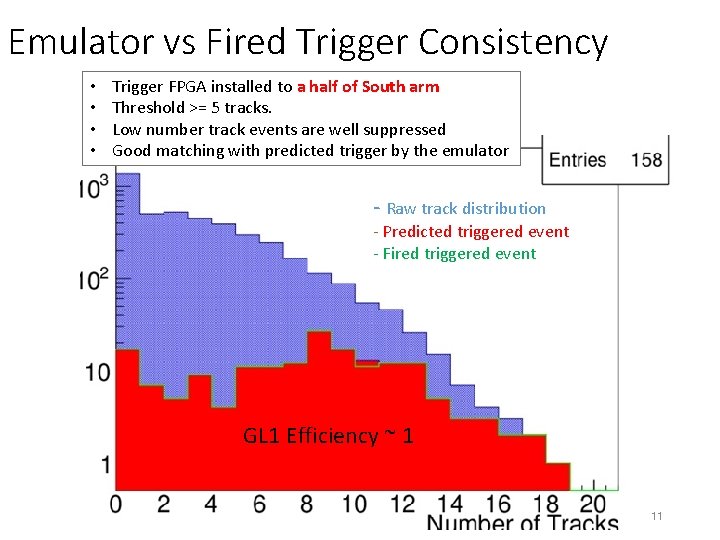

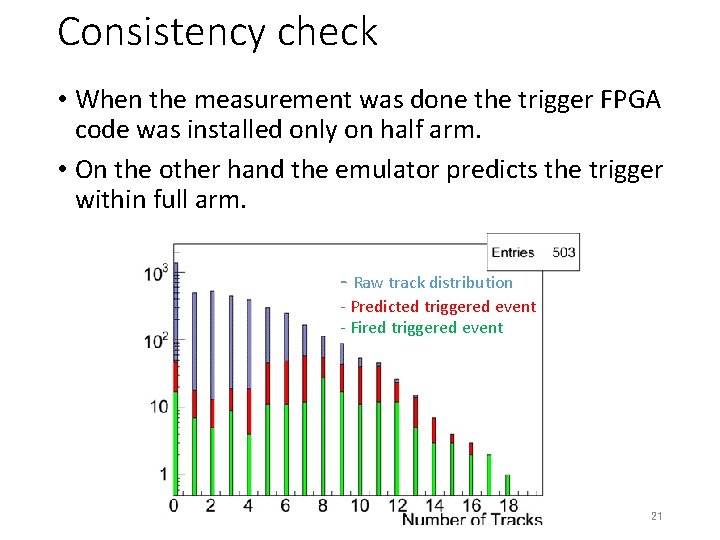

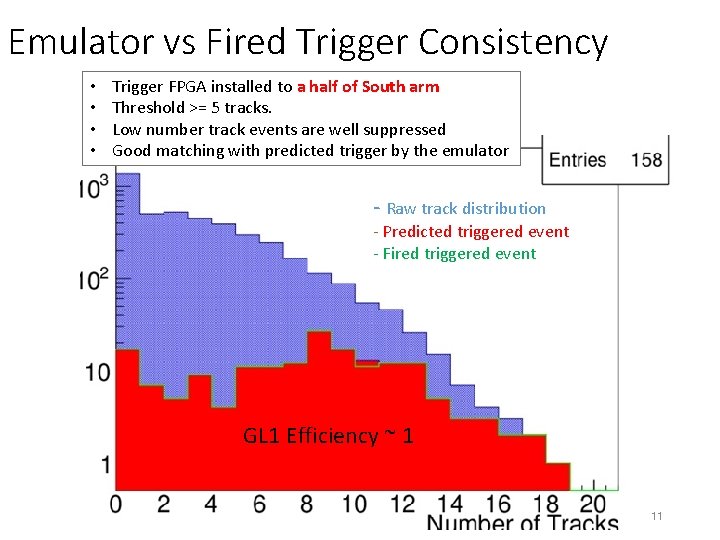

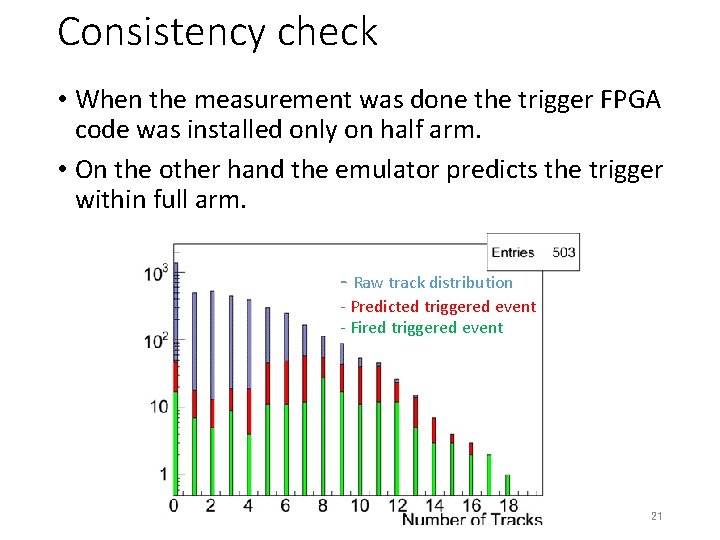

Emulator vs Fired Trigger Consistency • • Trigger FPGA installed to a half of South arm Threshold >= 5 tracks. Low number track events are well suppressed Good matching with predicted trigger by the emulator - Raw track distribution - Predicted triggered event - Fired triggered event GL 1 Efficiency ~ 1 11

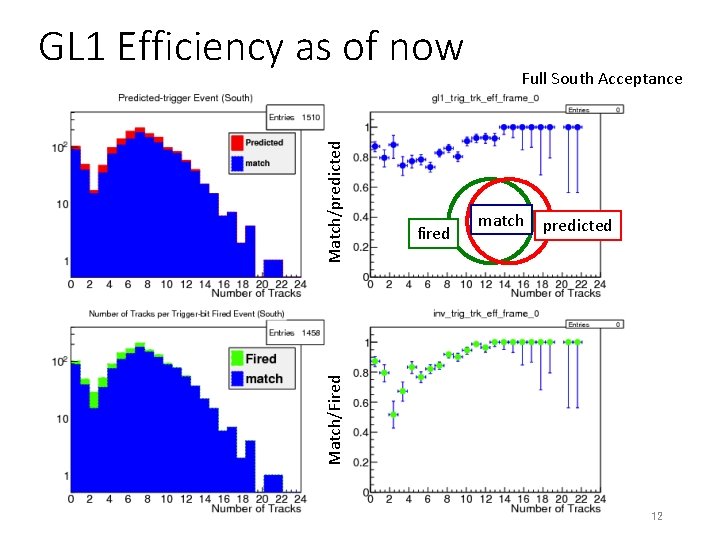

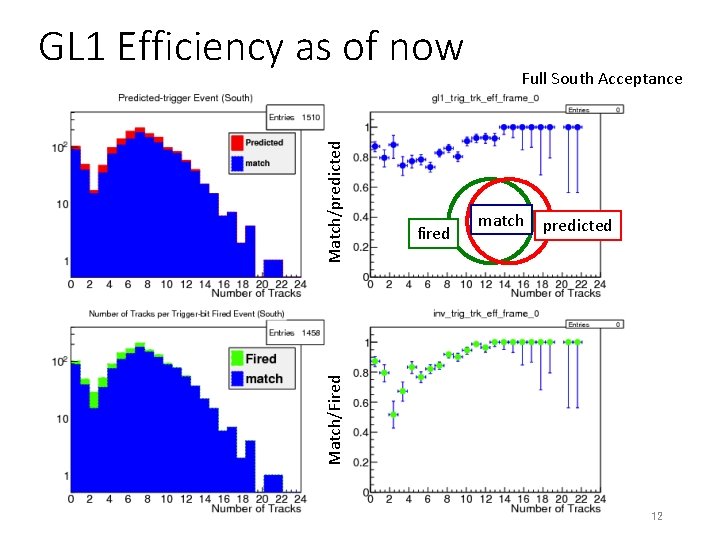

fired Full South Acceptance match predicted Match/Fired Match/predicted GL 1 Efficiency as of now 12

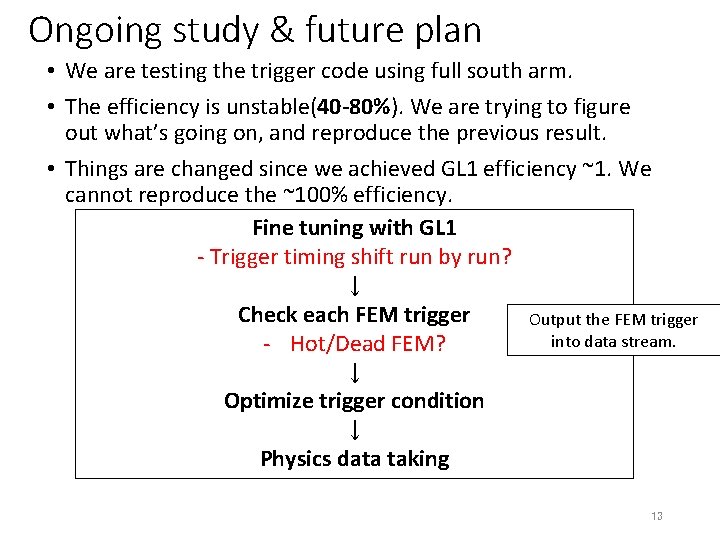

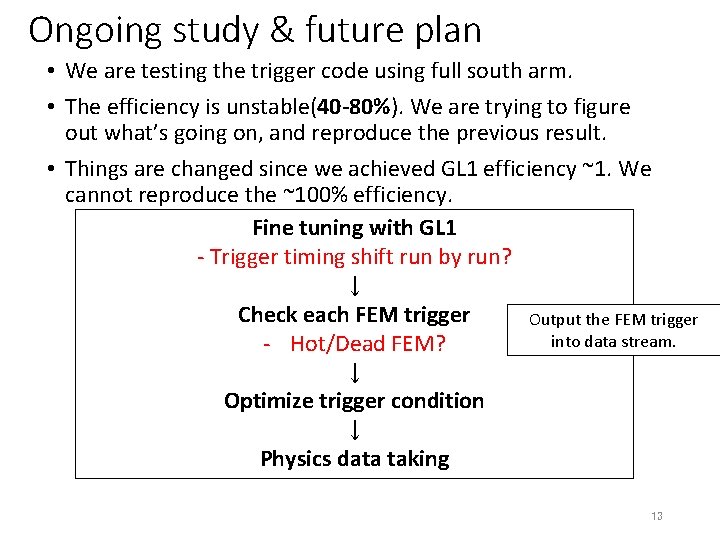

Ongoing study & future plan • We are testing the trigger code using full south arm. • The efficiency is unstable(40 -80%). We are trying to figure out what’s going on, and reproduce the previous result. • Things are changed since we achieved GL 1 efficiency ~1. We cannot reproduce the ~100% efficiency. Fine tuning with GL 1 - Trigger timing shift run by run? ↓ Check each FEM trigger Output the FEM trigger into data stream. - Hot/Dead FEM? ↓ Optimize trigger condition ↓ Physics data taking 13

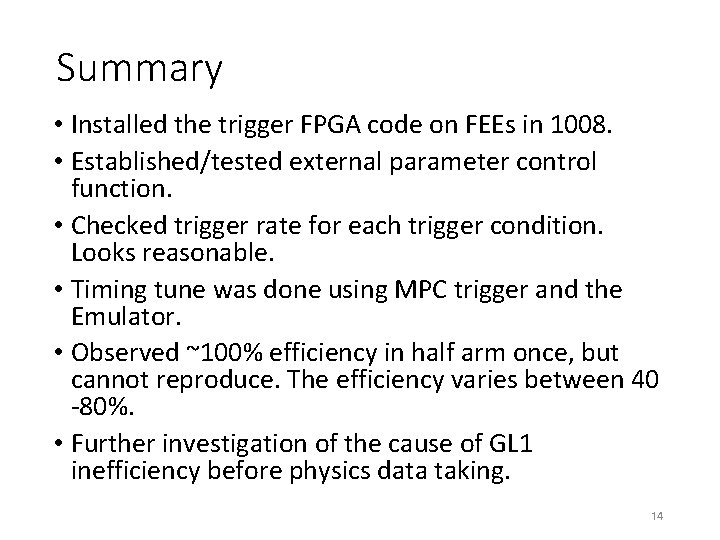

Summary • Installed the trigger FPGA code on FEEs in 1008. • Established/tested external parameter control function. • Checked trigger rate for each trigger condition. Looks reasonable. • Timing tune was done using MPC trigger and the Emulator. • Observed ~100% efficiency in half arm once, but cannot reproduce. The efficiency varies between 40 -80%. • Further investigation of the cause of GL 1 inefficiency before physics data taking. 14

Backup 15

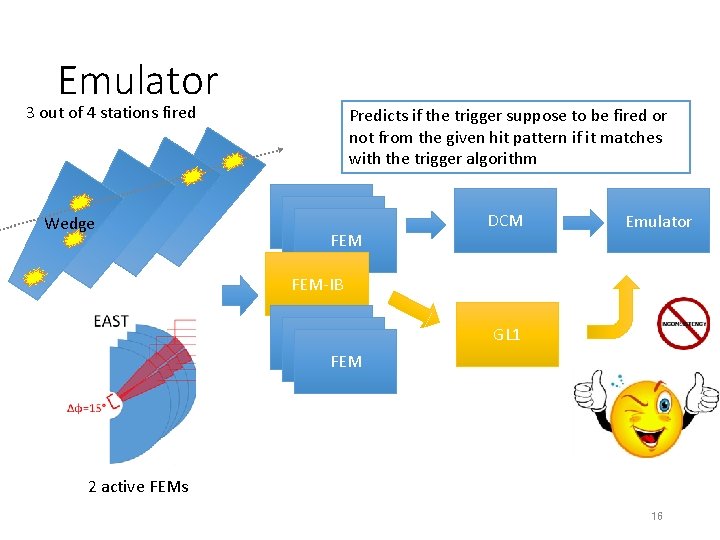

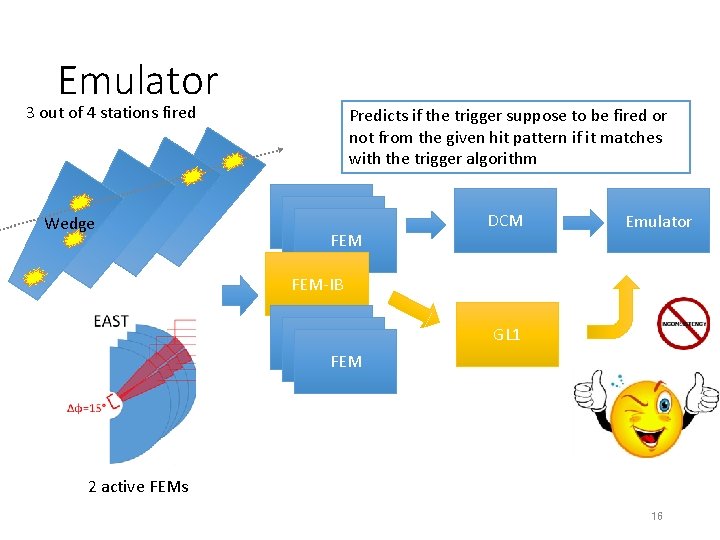

Emulator 3 out of 4 stations fired Wedge Predicts if the trigger suppose to be fired or not from the given hit pattern if it matches with the trigger algorithm FEM FEM DCM Emulator FEM-IB FEM FEM GL 1 2 active FEMs 16

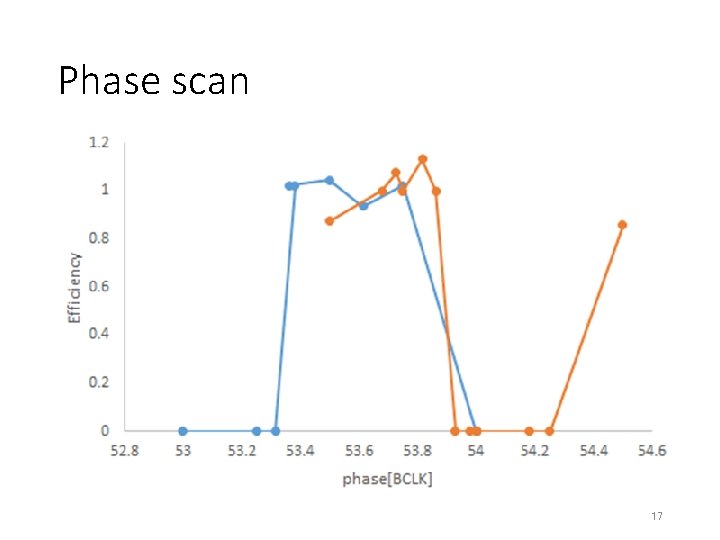

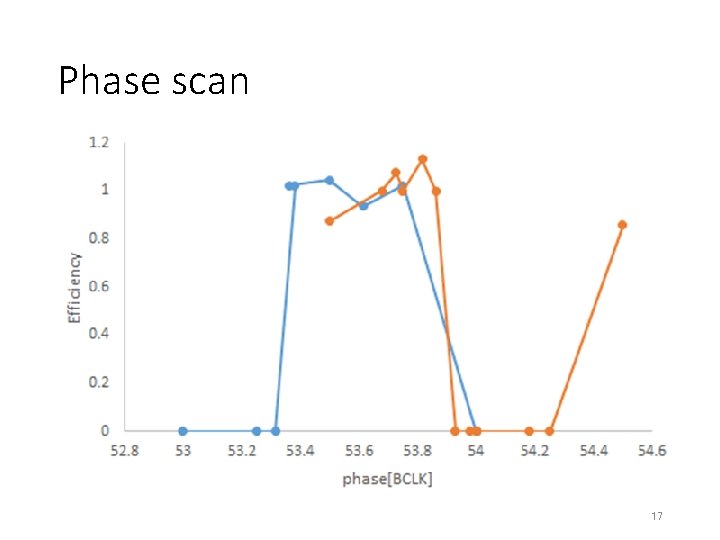

Phase scan 17

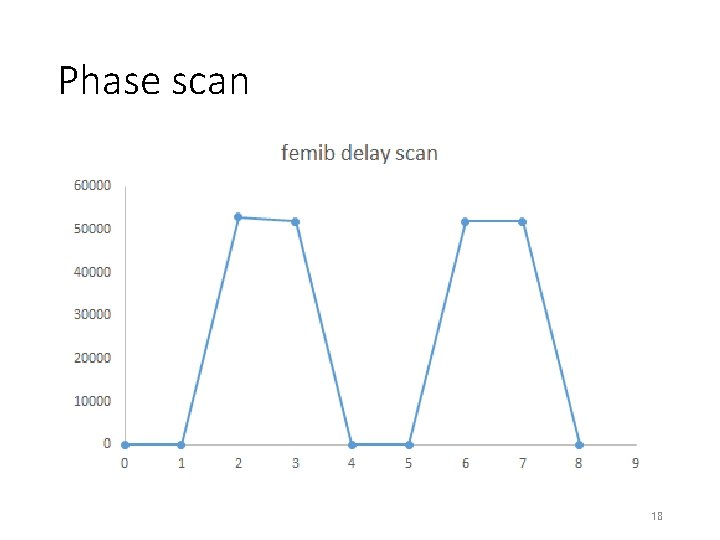

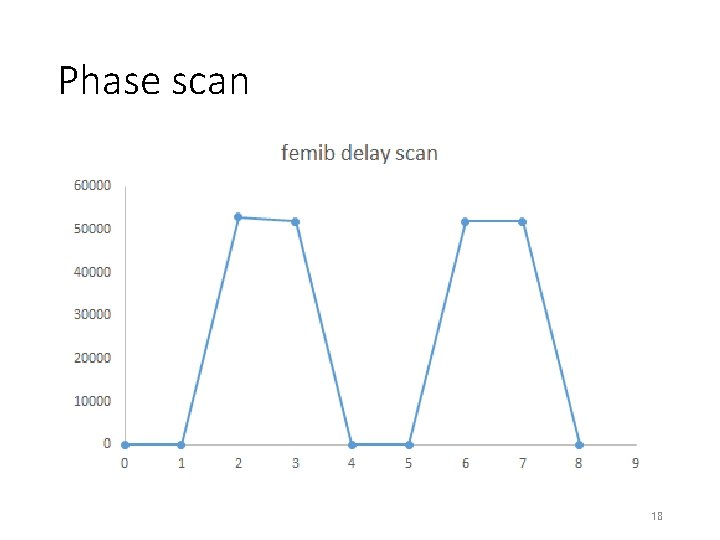

Phase scan 18

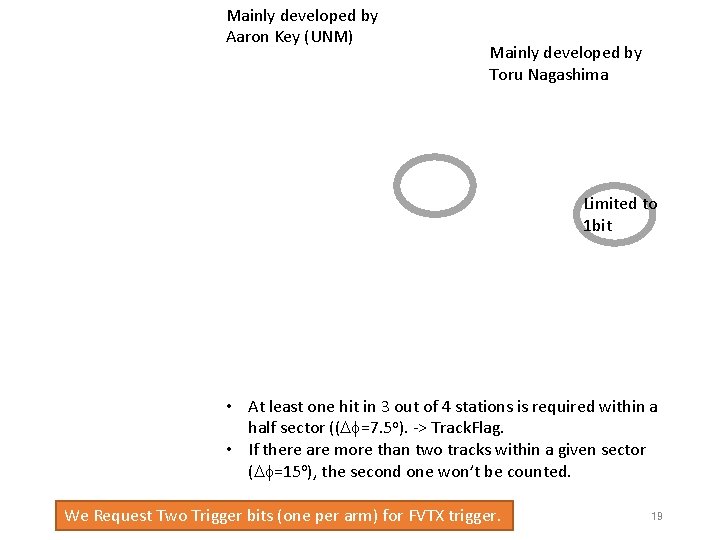

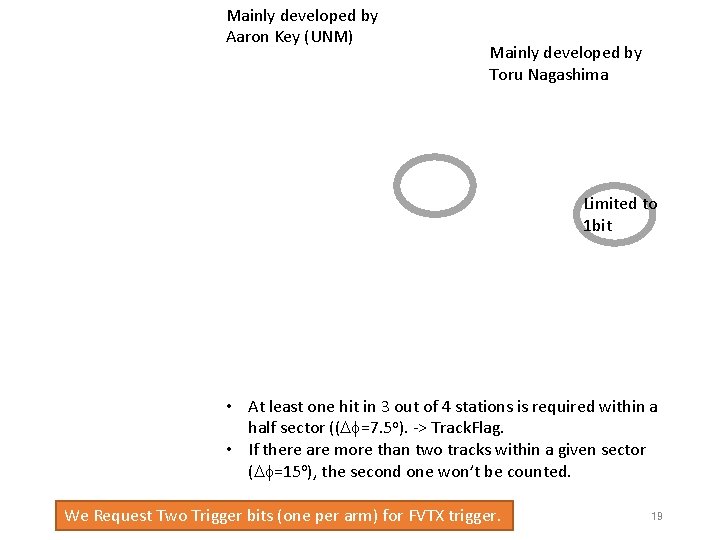

Mainly developed by Aaron Key (UNM) Mainly developed by Toru Nagashima Limited to 1 bit • At least one hit in 3 out of 4 stations is required within a half sector ((Df=7. 5 o). -> Track. Flag. • If there are more than two tracks within a given sector (Df=15 o), the second one won’t be counted. We Request Two Trigger bits (one per arm) for FVTX trigger. 19

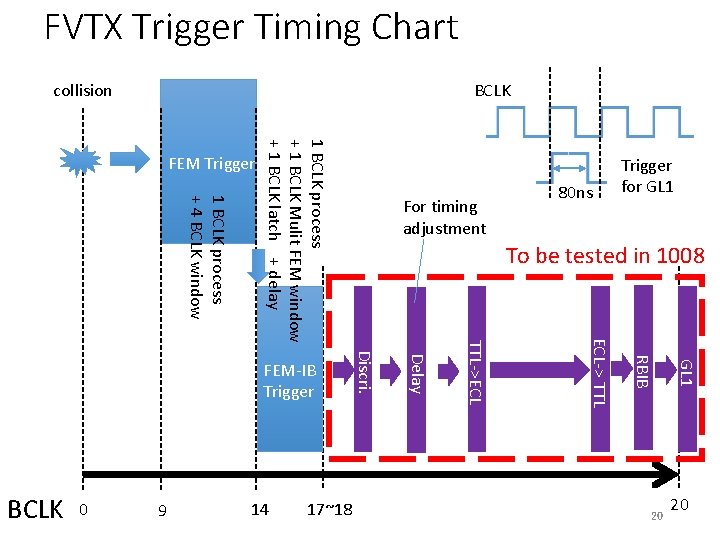

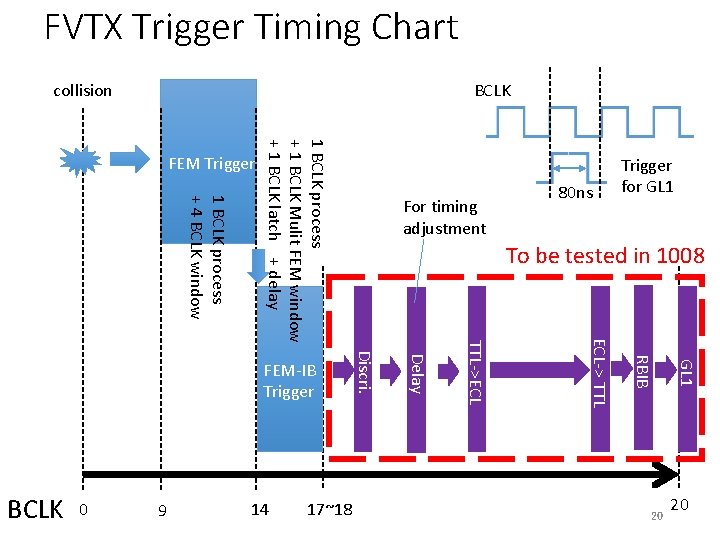

FVTX Trigger Timing Chart collision BCLK 1 BCLK process + 4 BCLK window 1 BCLK process + 1 BCLK Mulit FEM window + 1 BCLK latch + delay FEM Trigger 20 GL 1 17~18 RBIB 14 ECL-> TTL 9 TTL->ECL 0 Delay BCLK 80 ns To be tested in 1008 Discri. FEM-IB Trigger For timing adjustment Trigger for GL 1 20

Consistency check • When the measurement was done the trigger FPGA code was installed only on half arm. • On the other hand the emulator predicts the trigger within full arm. - Raw track distribution - Predicted triggered event - Fired triggered event 21

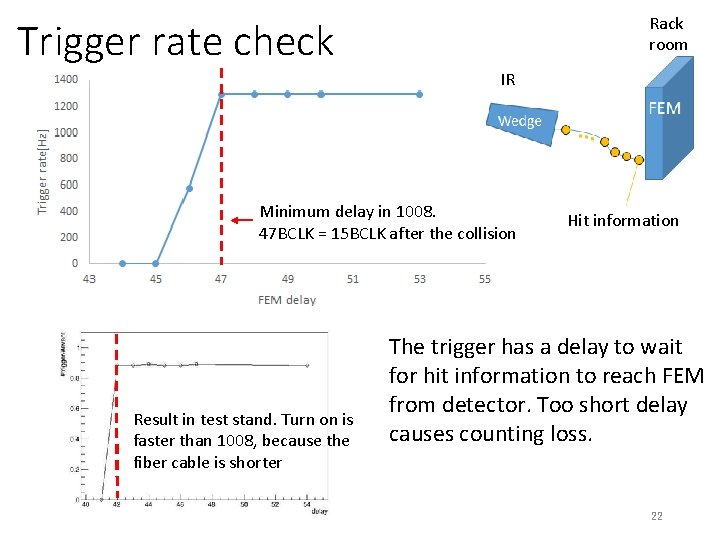

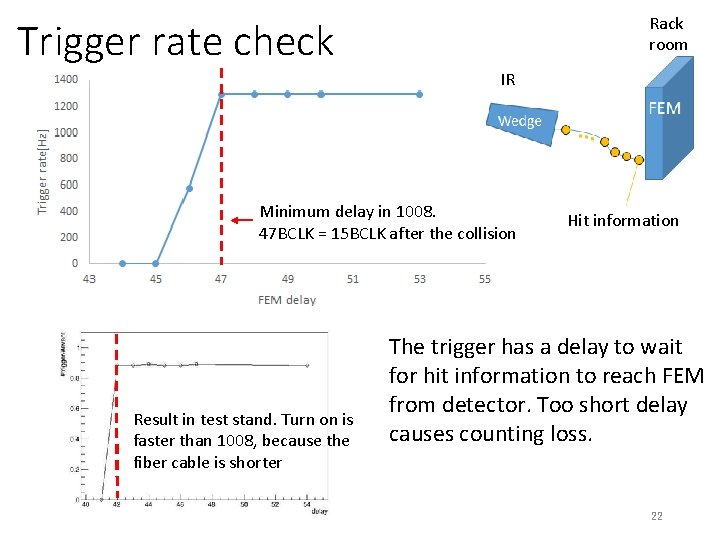

Rack room Trigger rate check IR Minimum delay in 1008. 47 BCLK = 15 BCLK after the collision Result in test stand. Turn on is faster than 1008, because the fiber cable is shorter Hit information The trigger has a delay to wait for hit information to reach FEM from detector. Too short delay causes counting loss. 22