Functions of Combinational Logic Outline Basic Adders Parallel

Functions of Combinational Logic

Outline • • Basic Adders Parallel Binary Adders Comparator Decoders Encoders Code Converters Multiplexers Parity Generators/Checkers

Design Procedure of Combinational Circuits The design of a combinational circuit starts from the specification of the problem and end up in a logic circuit diagram or a set of Boolean expression (functions) from which the logic diagram can be obtained. The procedure involves the following step: – From the specification of the circuit, determine the required number of inputs and outputs and assign a symbol for each. – Derive the truth table that defines the required relationship between inputs and outputs. – Obtain the simplified Boolean functions for each output as a function of the input variables. – Draw the logic diagram and verify the correctness of the design.

Design Procedure of Combinational Circuits • Some times the truth table has so many entries and it becomes so difficult to design a circuit based on the previous approach. • Combinational circuits (digital functions) that posses an inherent well-defined regularity can usually be designed by means of an algorithmic procedure. • An algorithm is a procedure that specifies a finite set of step that, if followed, give the solution to a problem. • The algorithm is a direct application of the procedure a person uses to perform a certain task. – example: comparator

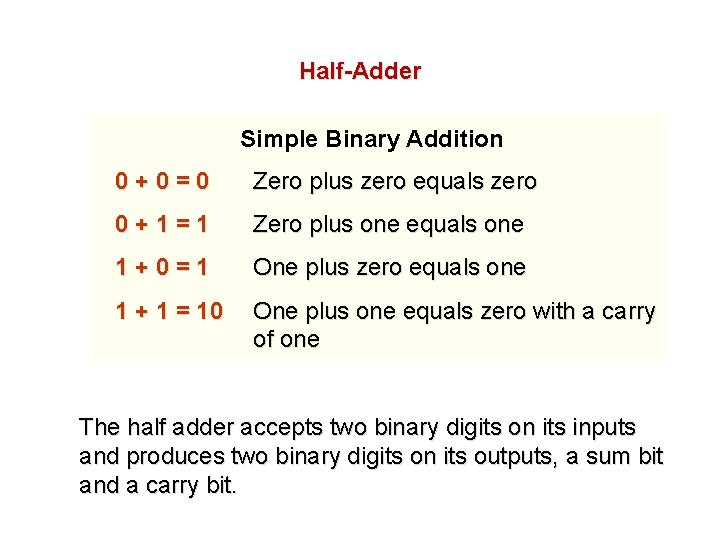

Half-Adder Simple Binary Addition 0+0=0 Zero plus zero equals zero 0+1=1 Zero plus one equals one 1+0=1 One plus zero equals one 1 + 1 = 10 One plus one equals zero with a carry of one The half adder accepts two binary digits on its inputs and produces two binary digits on its outputs, a sum bit and a carry bit.

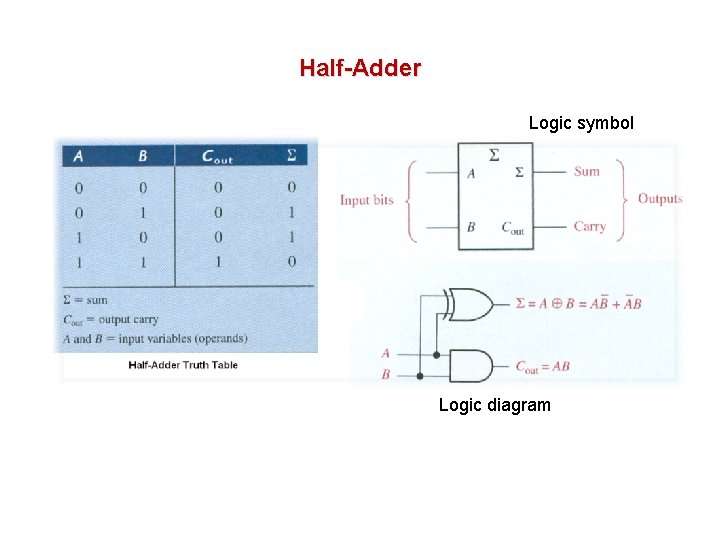

Half-Adder Logic symbol Logic diagram

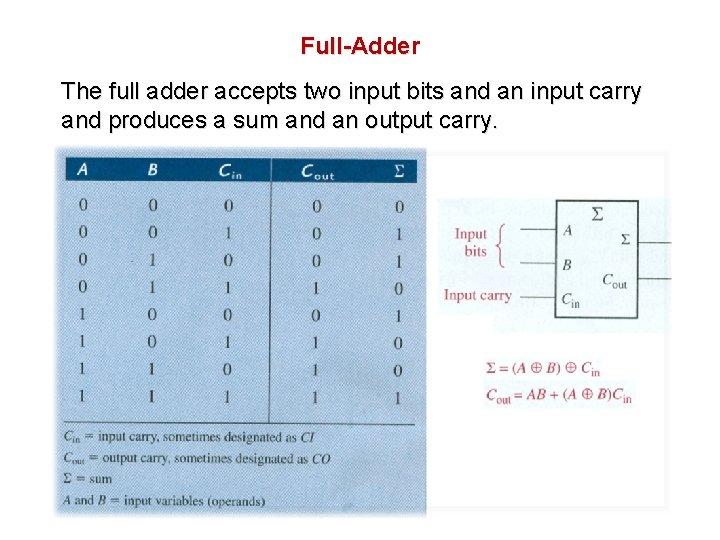

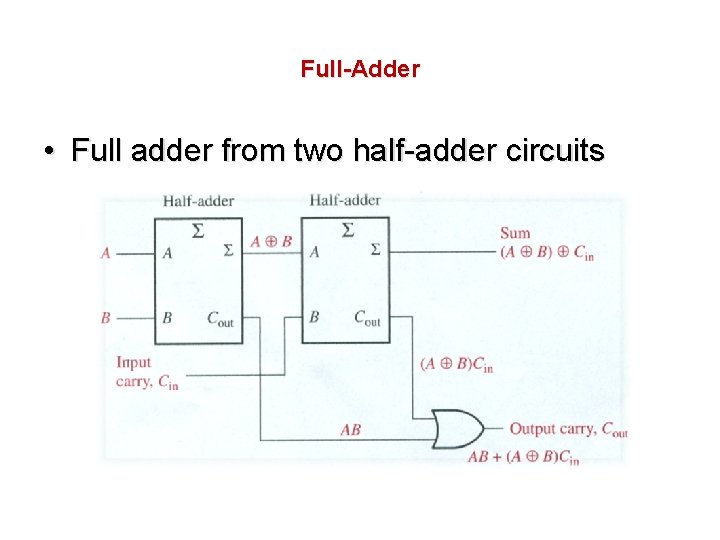

Full-Adder The full adder accepts two input bits and an input carry and produces a sum and an output carry.

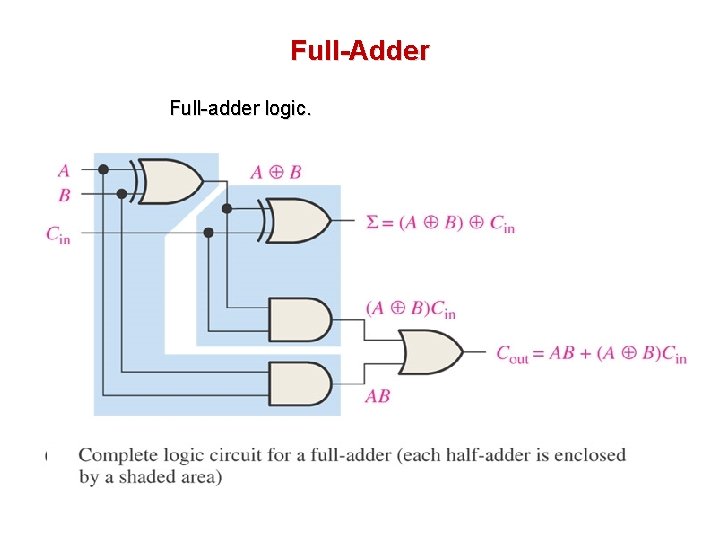

Full-Adder Full-adder logic.

Full-Adder • Full adder from two half-adder circuits

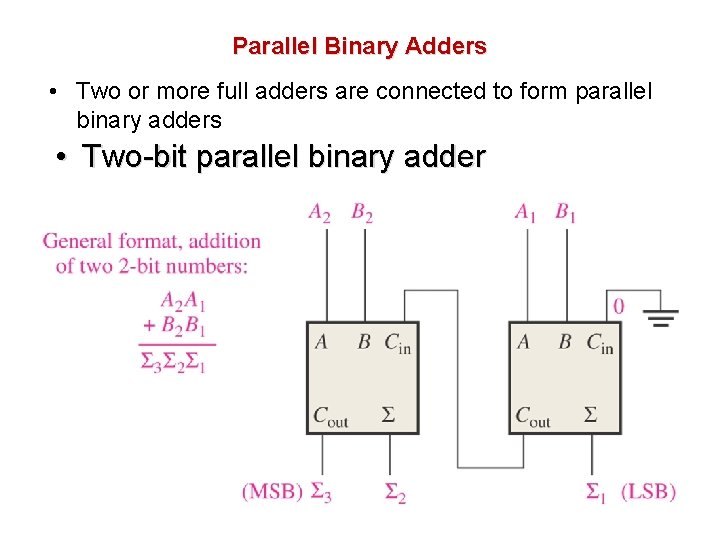

Parallel Binary Adders • Two or more full adders are connected to form parallel binary adders • Two-bit parallel binary adder

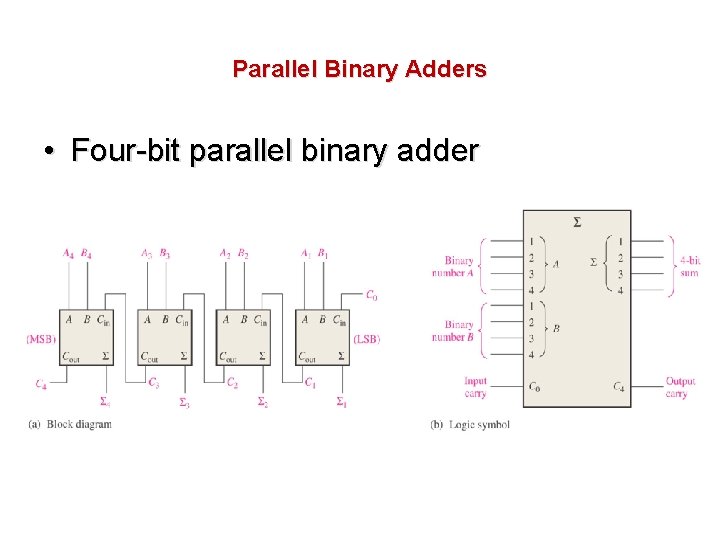

Parallel Binary Adders • Four-bit parallel binary adder

Application: a voting system using full adders and binary adders • Self study. See pages 281 and 282 in the textbook.

• • • Binary Subtractor The Subtraction A – B can be done by taking the 2’s complement (1’s complement + 1) of B and adding it to A. 1’s complement is implemented with inverters. The subtractor A – B is implemented by using adders and inverters. The input carry of Cin of the 1 st adder must be equal to 1. The operation becomes: A + 1’s complement of B + 1. Example: Design 2 bit subtractor.

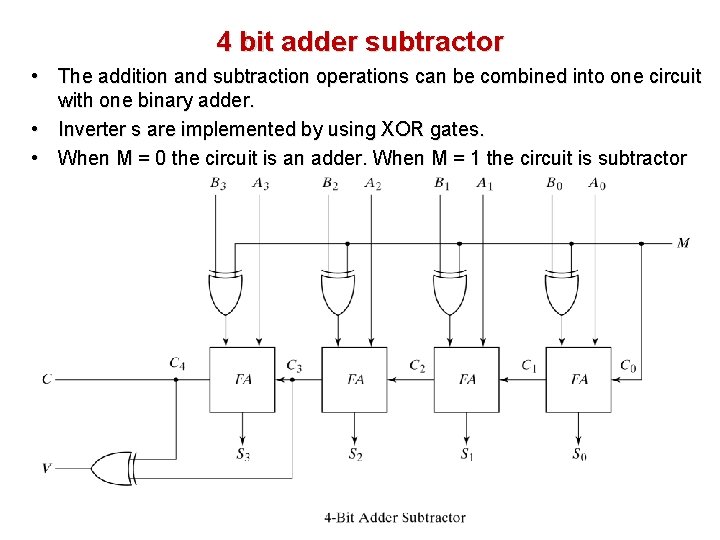

4 bit adder subtractor • The addition and subtraction operations can be combined into one circuit with one binary adder. • Inverter s are implemented by using XOR gates. • When M = 0 the circuit is an adder. When M = 1 the circuit is subtractor

Comparators • The basic function of a comparator is to compare the magnitudes of two binary quantities to determine the relationship of those quantities. – 1 -Bit Comparator – 2 -Bit Comparator – 4 -Bit Comparator

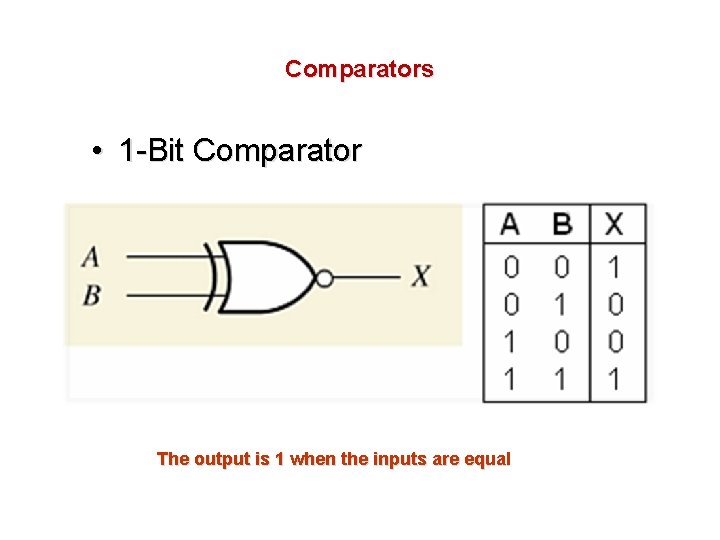

Comparators • 1 -Bit Comparator The output is 1 when the inputs are equal

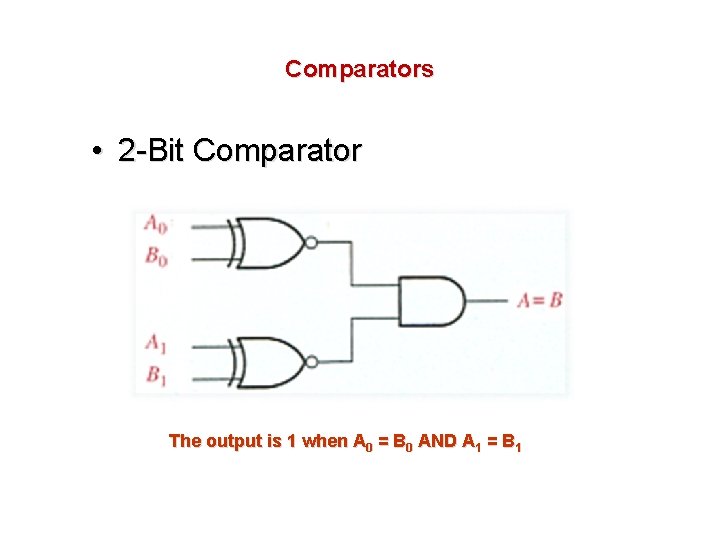

Comparators • 2 -Bit Comparator The output is 1 when A 0 = B 0 AND A 1 = B 1

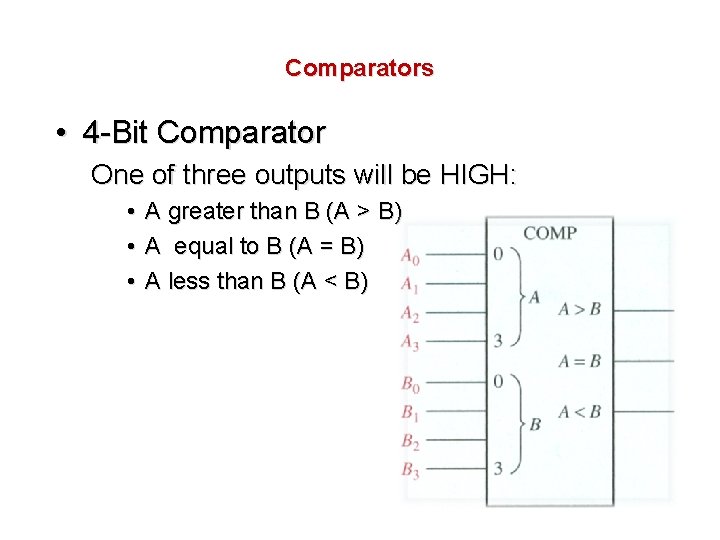

Comparators • 4 -Bit Comparator One of three outputs will be HIGH: • • • A greater than B (A > B) A equal to B (A = B) A less than B (A < B)

Designing the 4 -bit comparator

Decoders • • Binary decoder 4 -bit decoder BCD-to-decimal decoder BCD-to-7 -segement decoder

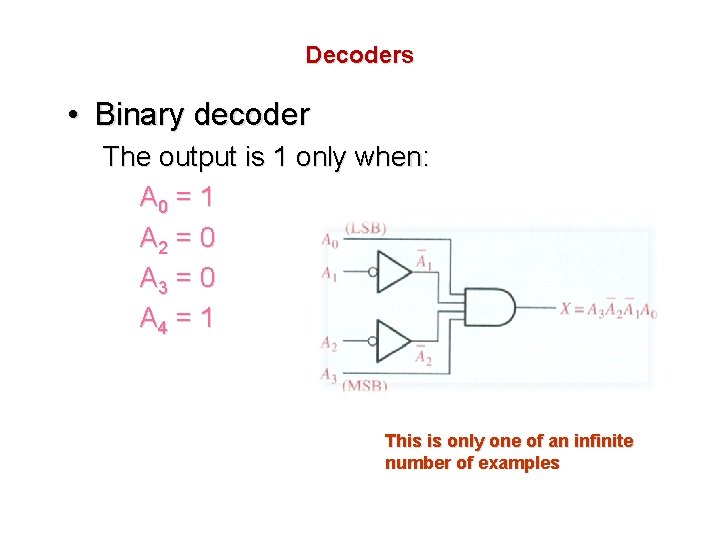

Decoders • Binary decoder The output is 1 only when: A 0 = 1 A 2 = 0 A 3 = 0 A 4 = 1 This is only one of an infinite number of examples

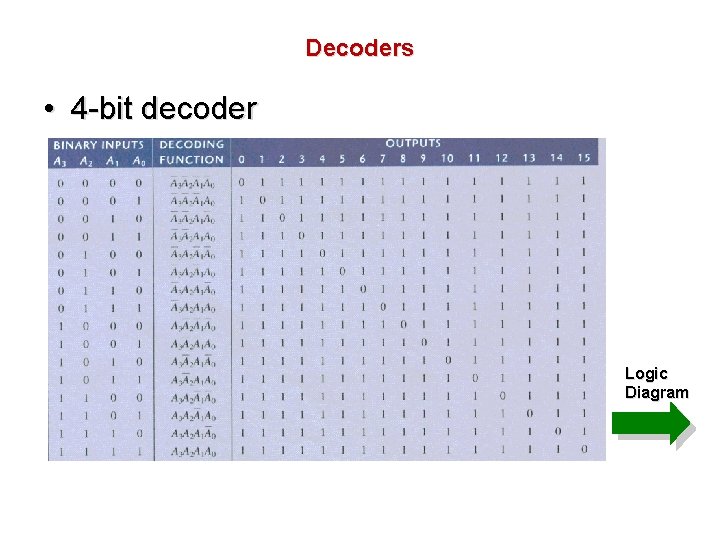

Decoders • 4 -bit decoder Logic Diagram

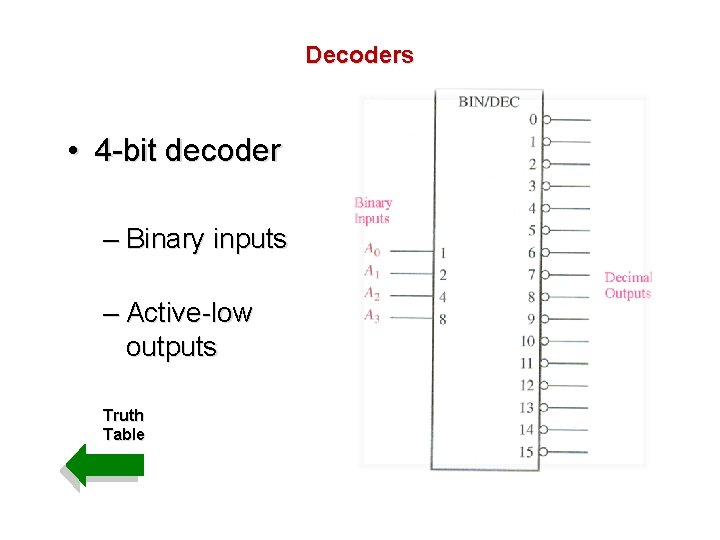

Decoders • 4 -bit decoder – Binary inputs – Active-low outputs Truth Table

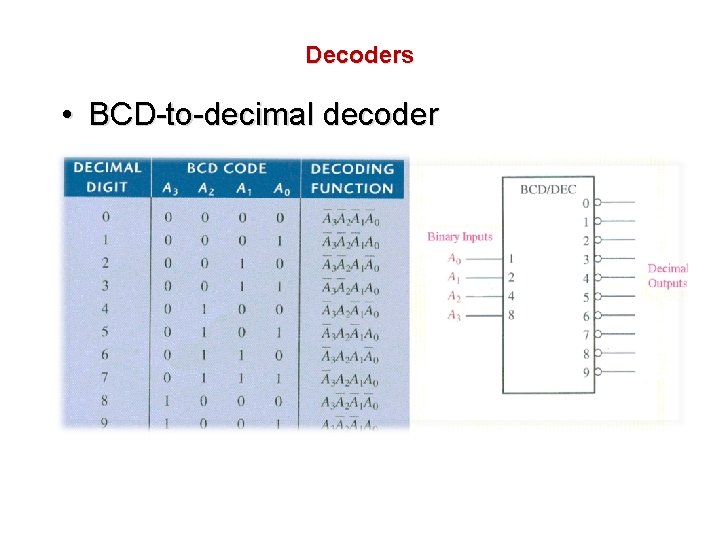

Decoders • BCD-to-decimal decoder

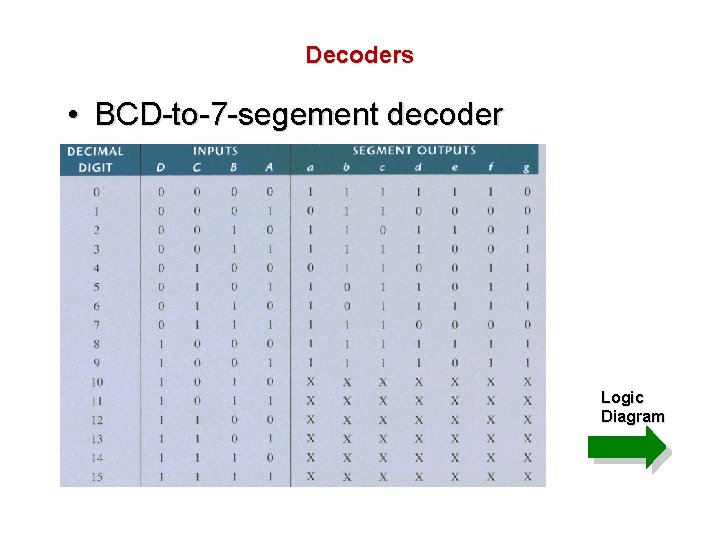

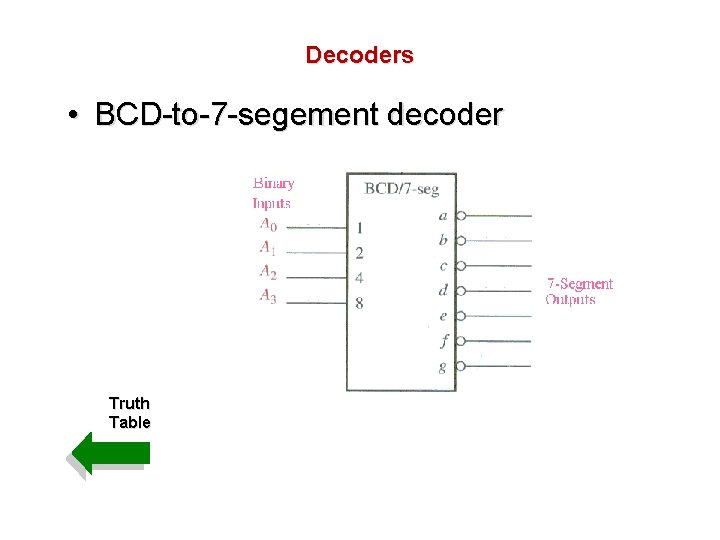

Decoders • BCD-to-7 -segement decoder Logic Diagram

Decoders • BCD-to-7 -segement decoder Truth Table

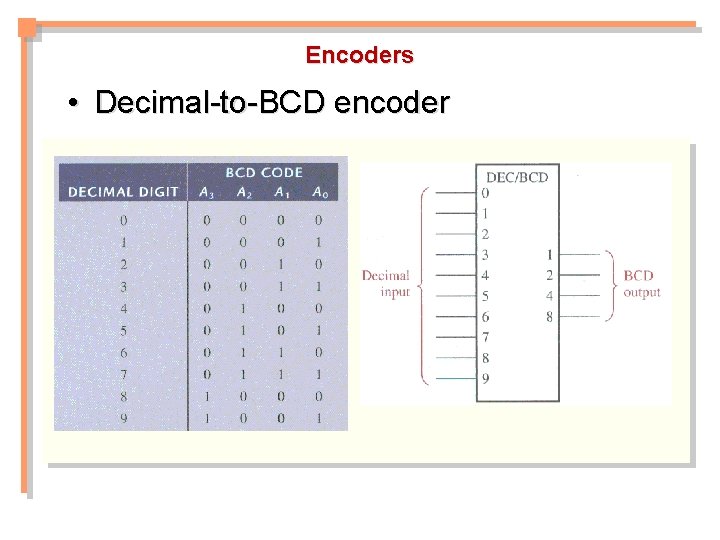

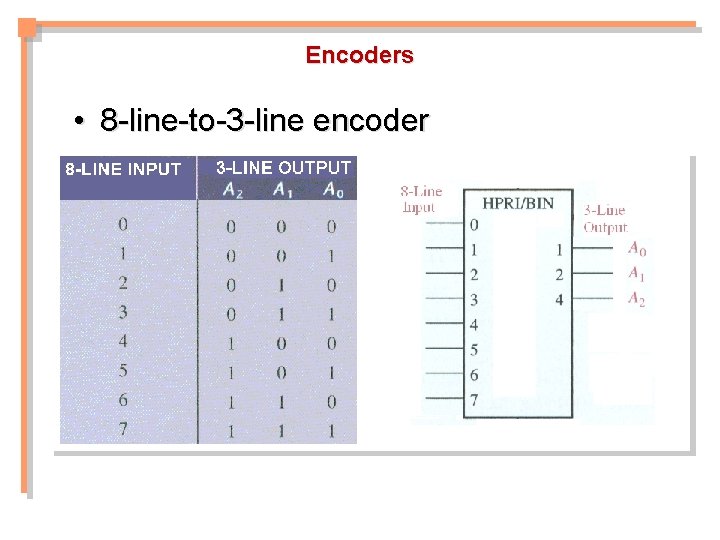

Encoders • Decimal-to-BCD encoder • 8 -line-to-3 -line encoder

Encoders • Decimal-to-BCD encoder

Encoders • 8 -line-to-3 -line encoder

Code Converters

Code Converters • BCD-to-binary conversion • Binary-Gray conversions

Code Converters • BCD-to-binary conversion

Code Converters • Binary-Gray conversions

Multiplexers (Data Selectors)

Multiplexers (Data Selectors) • 4 -input multiplexer • Expanded multiplexers

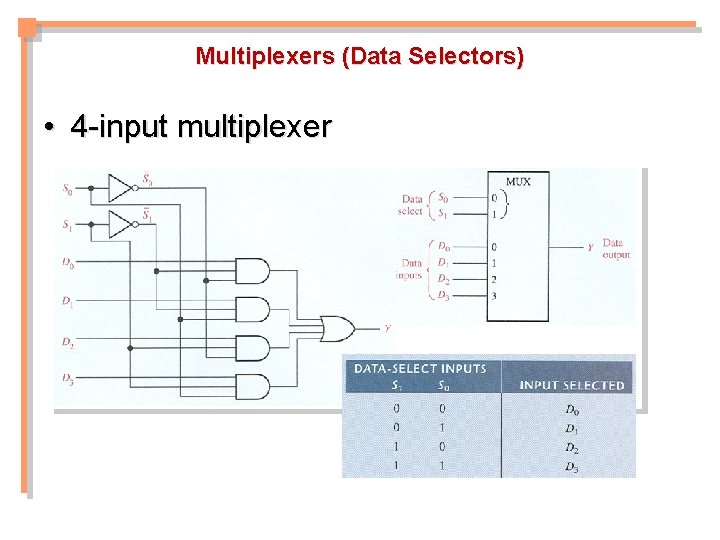

Multiplexers (Data Selectors) • 4 -input multiplexer

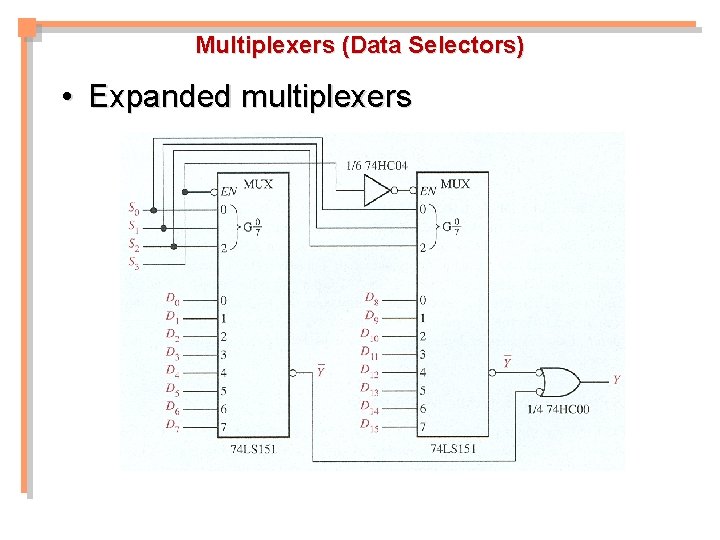

Multiplexers (Data Selectors) • Expanded multiplexers

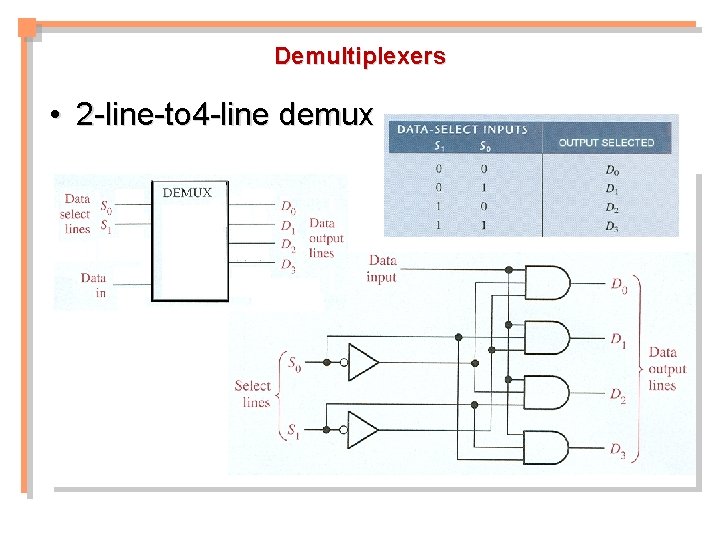

Demultiplexers

Demultiplexers • 2 -line-to 4 -line demux

Parity Generator/Checker

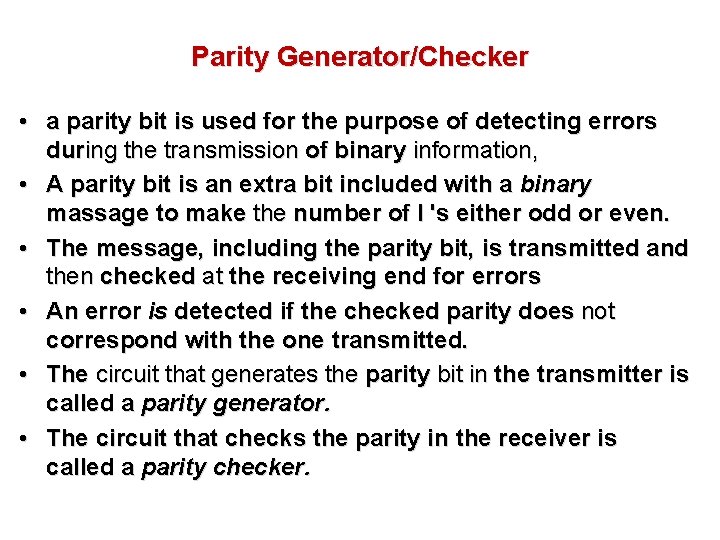

Parity Generator/Checker • a parity bit is used for the purpose of detecting errors during the transmission of binary information, • A parity bit is an extra bit included with a binary massage to make the number of I 's either odd or even. • The message, including the parity bit, is transmitted and then checked at the receiving end for errors • An error is detected if the checked parity does not correspond with the one transmitted. • The circuit that generates the parity bit in the transmitter is called a parity generator. • The circuit that checks the parity in the receiver is called a parity checker.

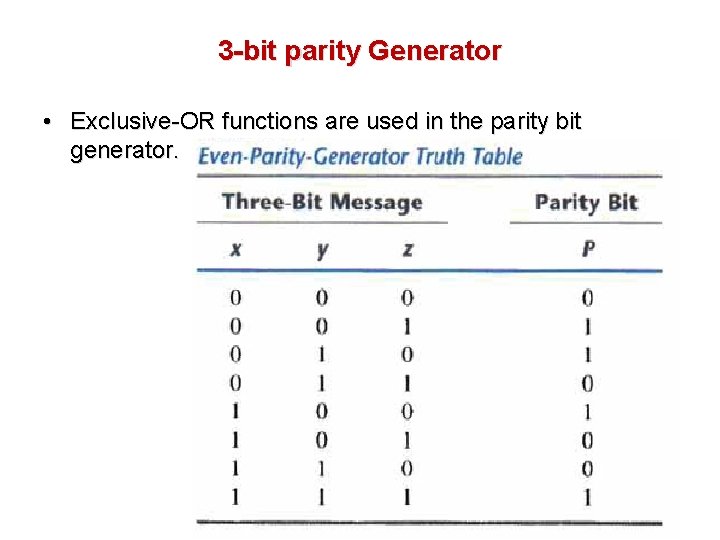

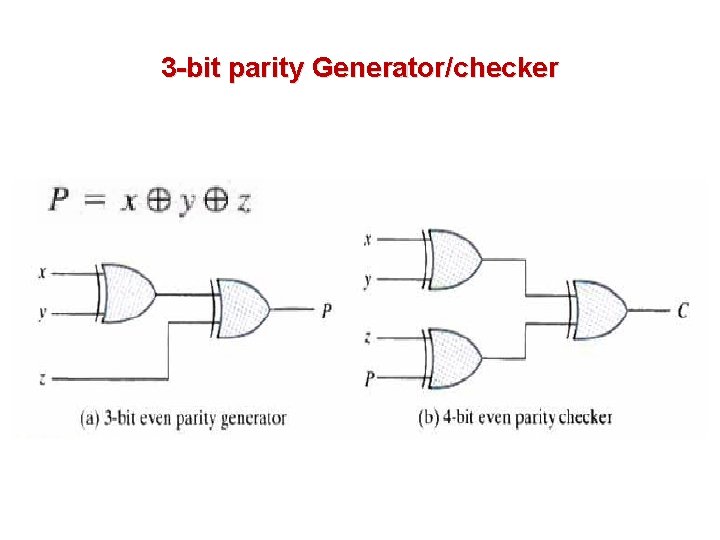

3 -bit parity Generator • Exclusive-OR functions are used in the parity bit generator.

3 -bit parity Generator/checker

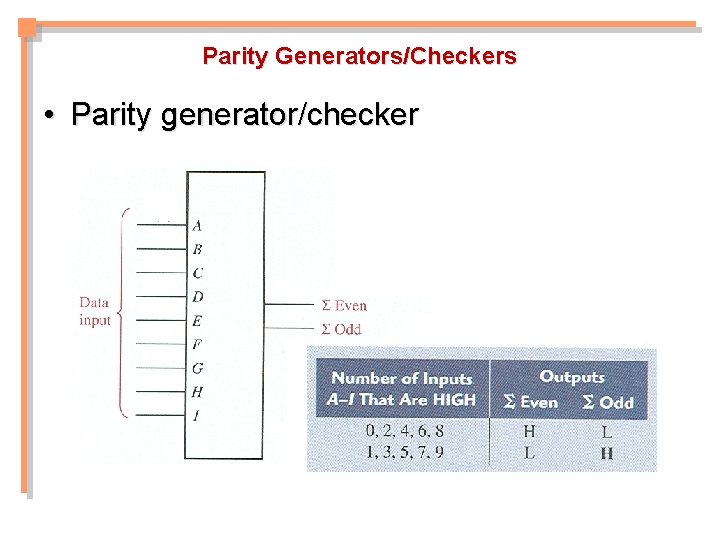

Parity Generators/Checkers • Parity generator/checker

These slides are based on Digital Fundamentals 9 th ed. By Thomas Floyd

- Slides: 45