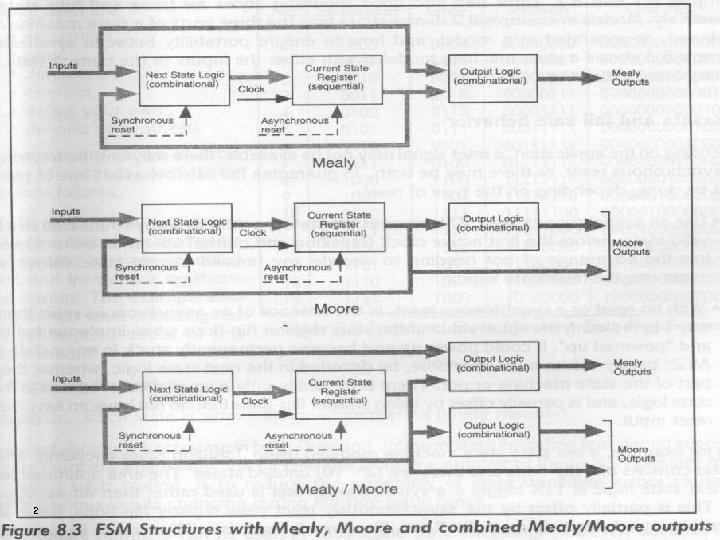

FSM Structures Mealy Moore and Combined MealyMoore outputs

FSM Structures • Mealy, Moore and Combined Mealy/Moore outputs • Figure 8. 3 1 EDA Lab. Dept. of Computer Engineering C. N. U.

2 EDA Lab. Dept. of Computer Engineering C. N. U.

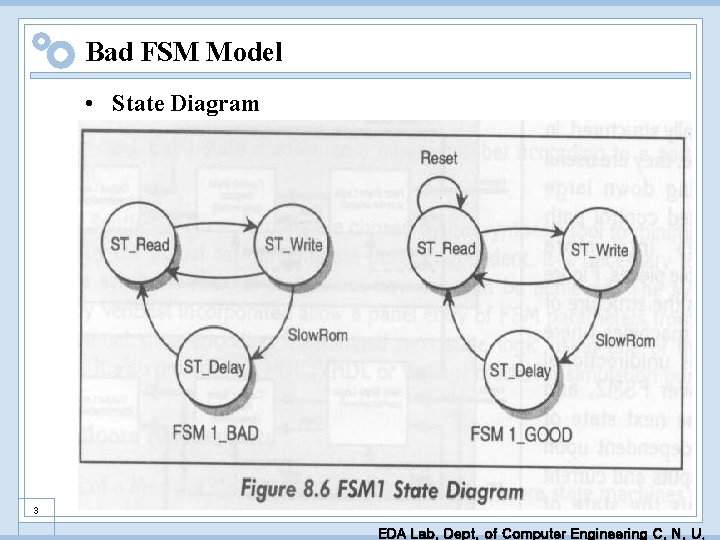

Bad FSM Model • State Diagram 3 EDA Lab. Dept. of Computer Engineering C. N. U.

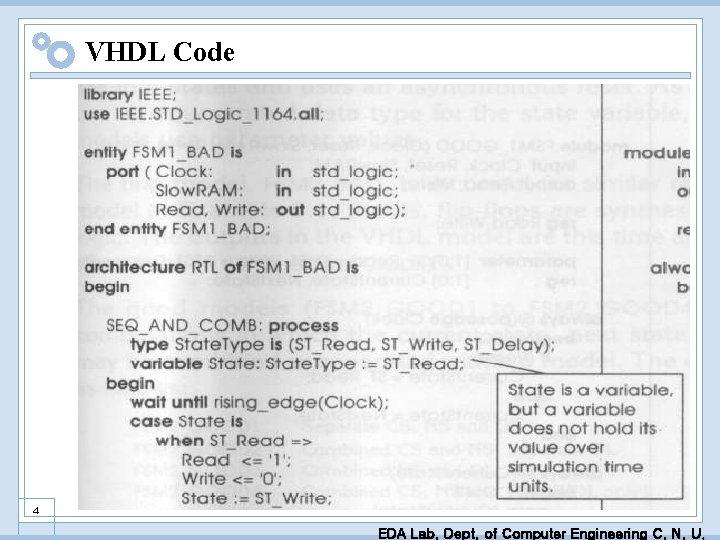

VHDL Code 4 EDA Lab. Dept. of Computer Engineering C. N. U.

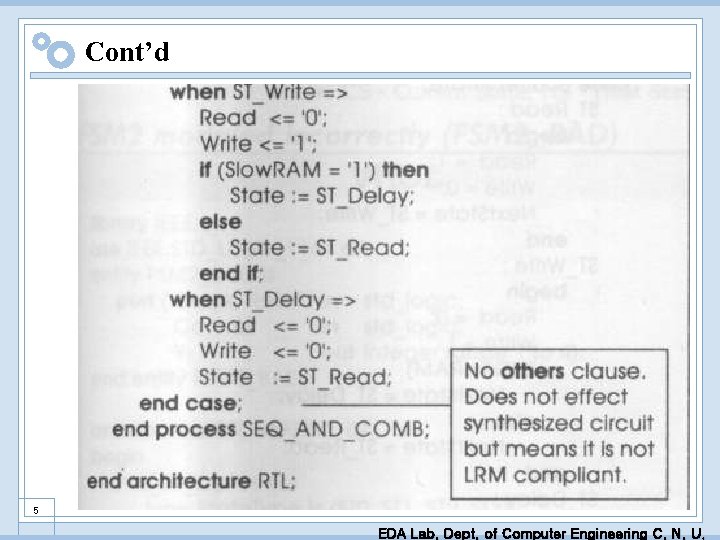

Cont’d 5 EDA Lab. Dept. of Computer Engineering C. N. U.

Problems of FSM 1 – BAD 1. no reset, no next state value defined for the unused state. – 2 bits FFs: 3 states used, one unused state. 2. Read and Write output assignment infer extra two FFs. – To avoid extra FFs, use separate combinational process. 3. variable initialization – Ignored by the synthesis tools. 6 EDA Lab. Dept. of Computer Engineering C. N. U.

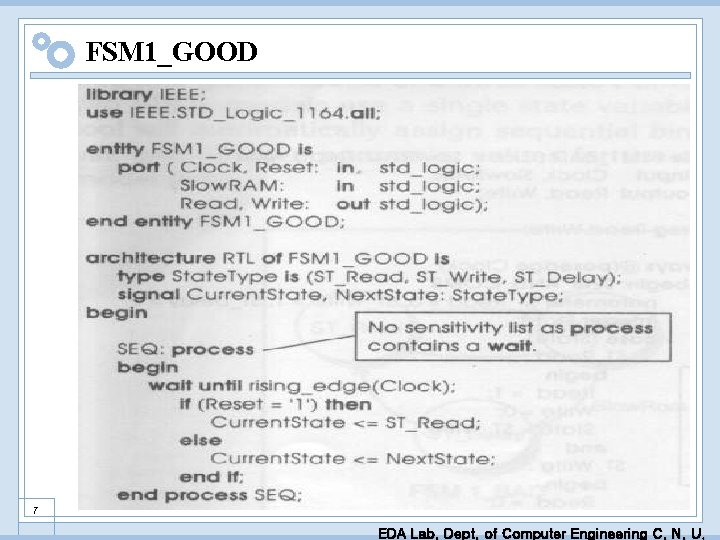

FSM 1_GOOD 7 EDA Lab. Dept. of Computer Engineering C. N. U.

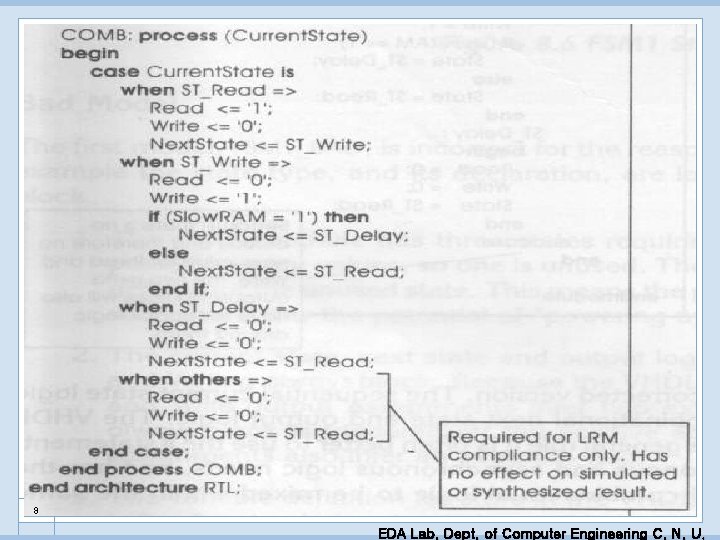

8 EDA Lab. Dept. of Computer Engineering C. N. U.

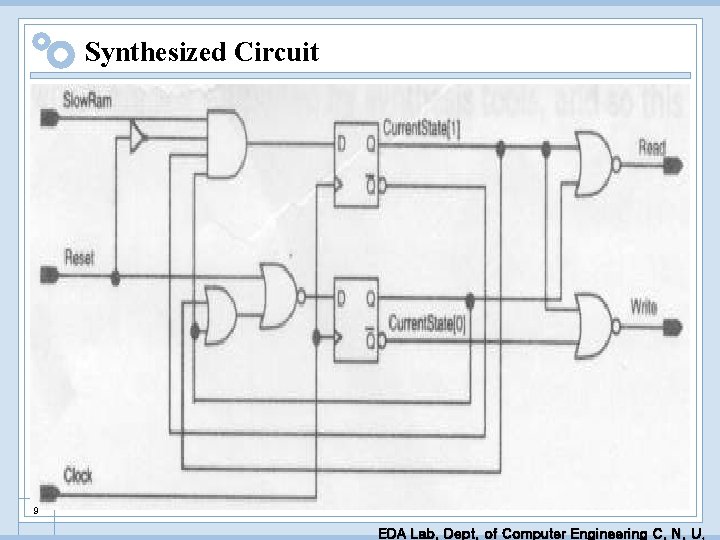

Synthesized Circuit 9 EDA Lab. Dept. of Computer Engineering C. N. U.

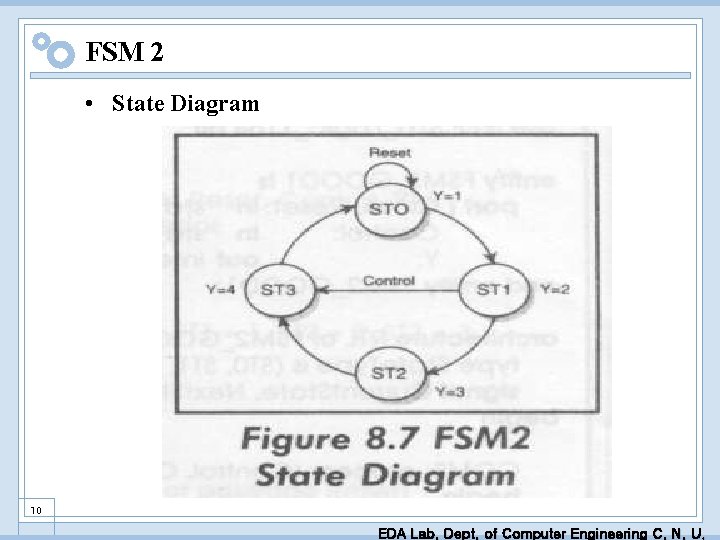

FSM 2 • State Diagram 10 EDA Lab. Dept. of Computer Engineering C. N. U.

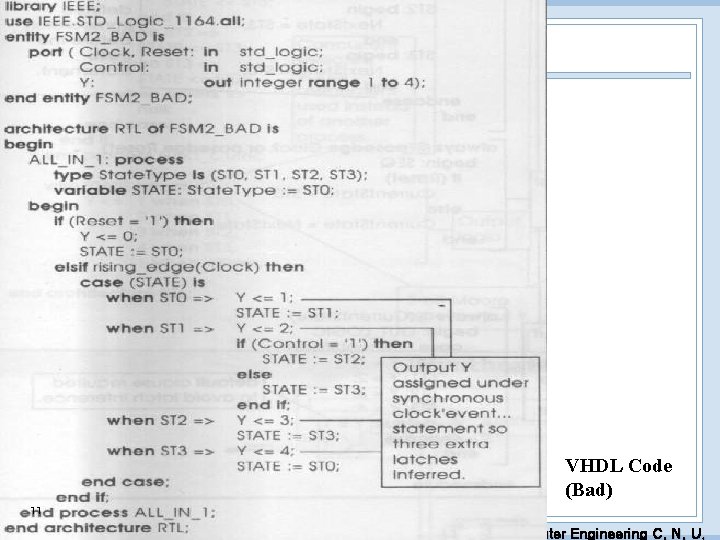

VHDL Code (Bad) 11 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d • Output Y – Assigned under clock’event … statement. – Extra FFs are inferred. 12 EDA Lab. Dept. of Computer Engineering C. N. U.

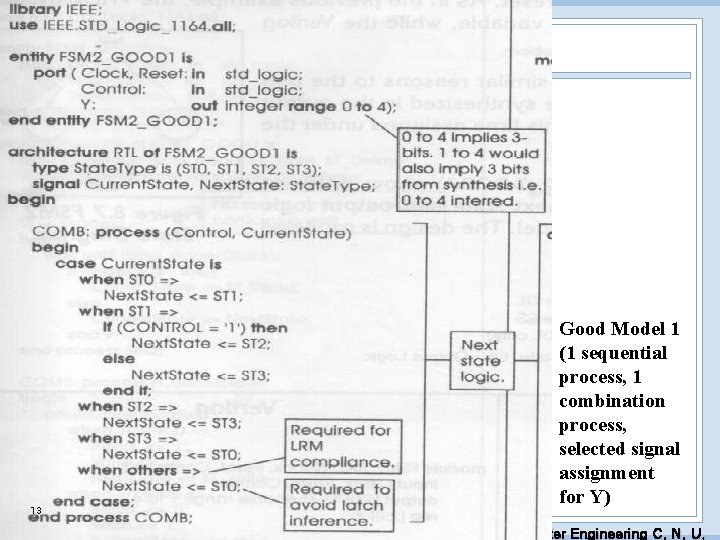

13 Good Model 1 (1 sequential process, 1 combination process, selected signal assignment for Y) EDA Lab. Dept. of Computer Engineering C. N. U.

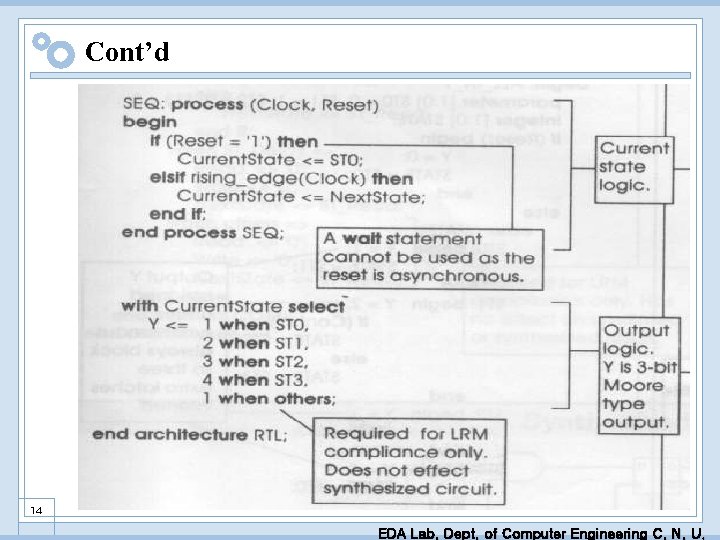

Cont’d 14 EDA Lab. Dept. of Computer Engineering C. N. U.

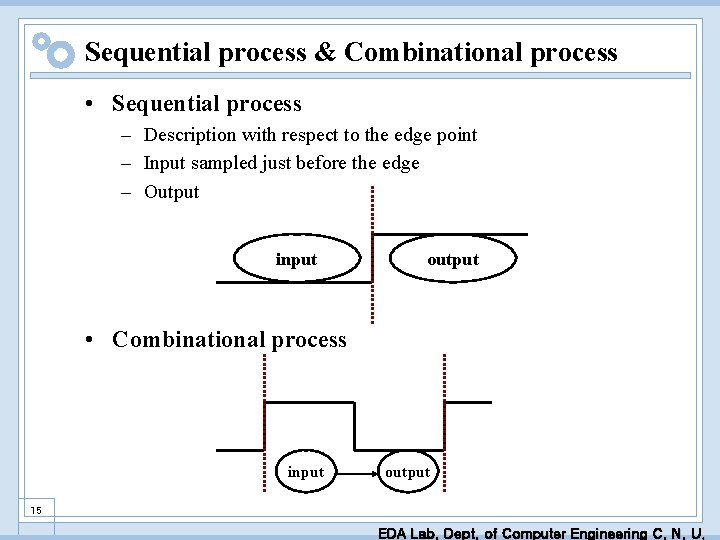

Sequential process & Combinational process • Sequential process – Description with respect to the edge point – Input sampled just before the edge – Output input output • Combinational process input output 15 EDA Lab. Dept. of Computer Engineering C. N. U.

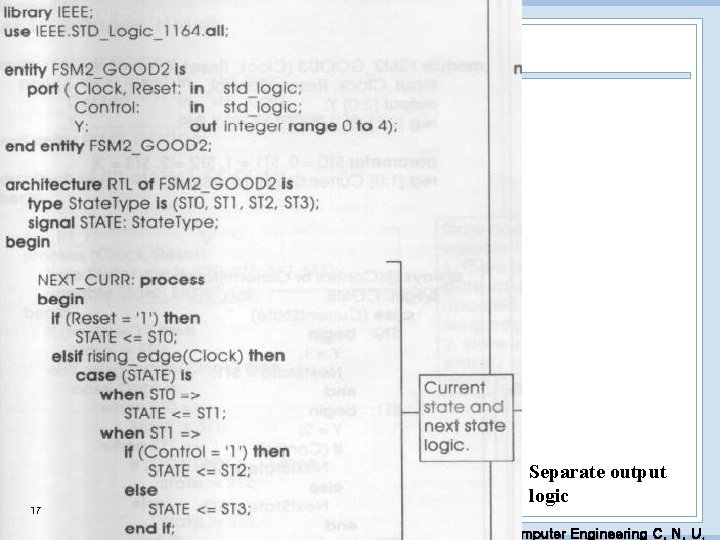

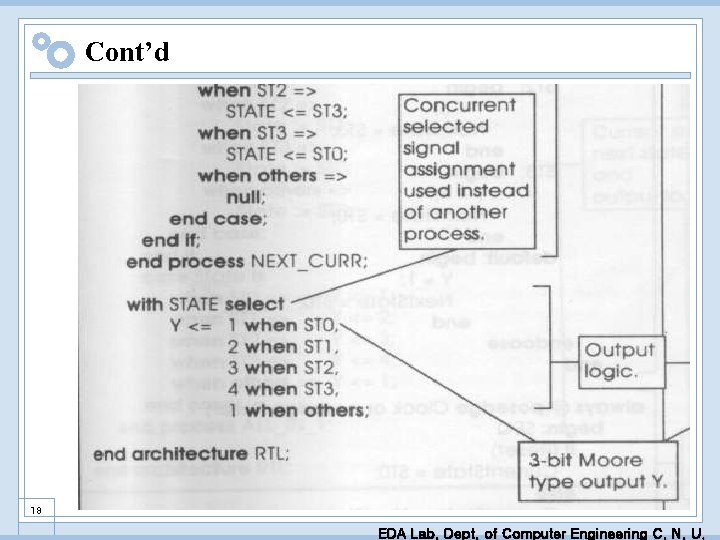

FSM 2_GOOD 2 • Combined current state and next state logic • Separate output logic 16 EDA Lab. Dept. of Computer Engineering C. N. U.

17 Separate output logic EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d 18 EDA Lab. Dept. of Computer Engineering C. N. U.

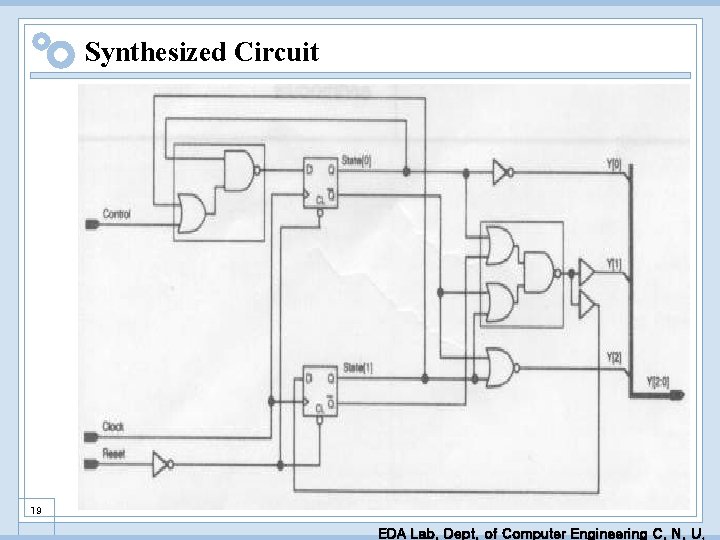

Synthesized Circuit 19 EDA Lab. Dept. of Computer Engineering C. N. U.

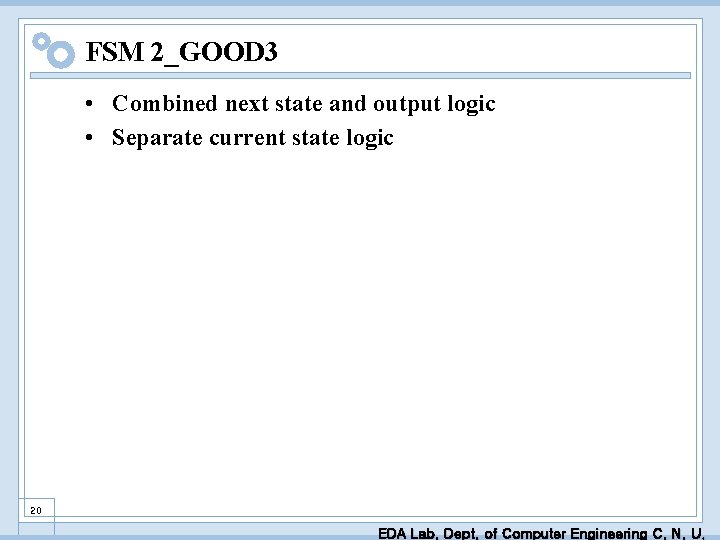

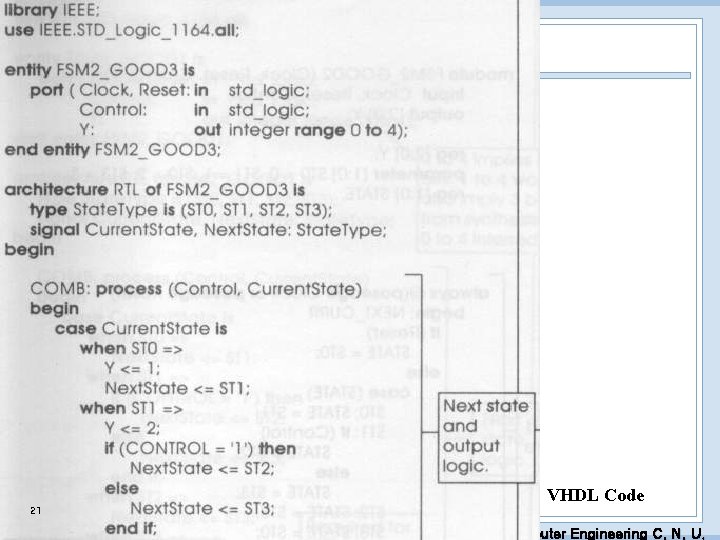

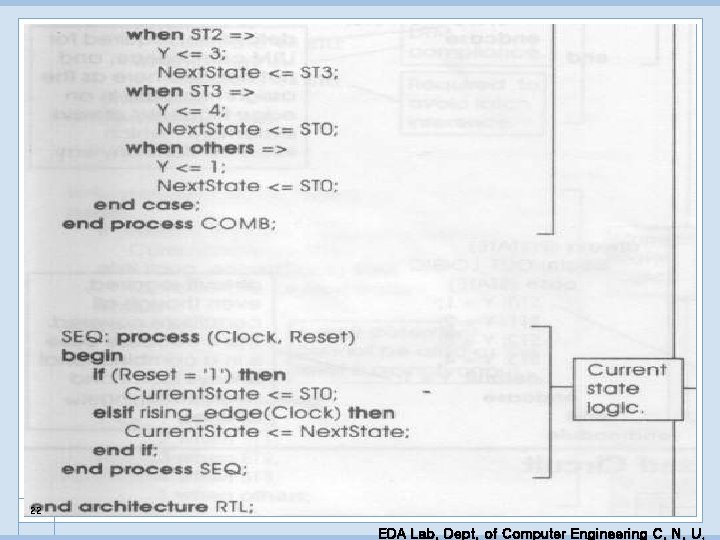

FSM 2_GOOD 3 • Combined next state and output logic • Separate current state logic 20 EDA Lab. Dept. of Computer Engineering C. N. U.

VHDL Code 21 EDA Lab. Dept. of Computer Engineering C. N. U.

22 EDA Lab. Dept. of Computer Engineering C. N. U.

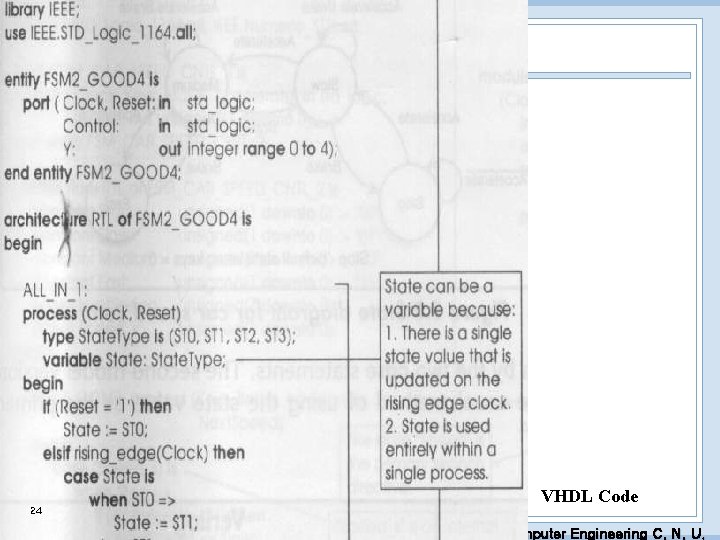

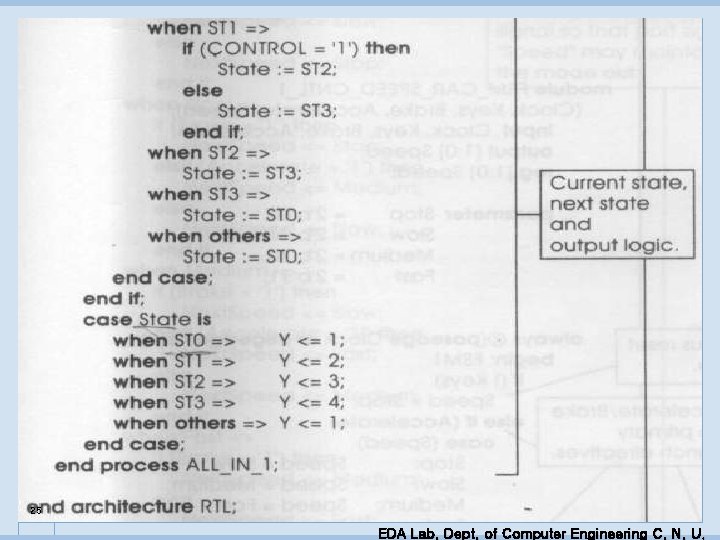

FSM 2_GOOD 4 • Combined current state, next state and output logic 23 EDA Lab. Dept. of Computer Engineering C. N. U.

24 VHDL Code EDA Lab. Dept. of Computer Engineering C. N. U.

25 EDA Lab. Dept. of Computer Engineering C. N. U.

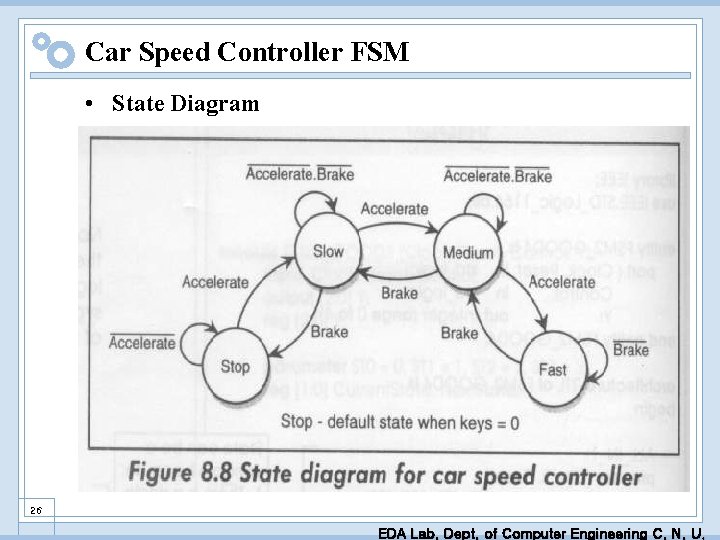

Car Speed Controller FSM • State Diagram 26 EDA Lab. Dept. of Computer Engineering C. N. U.

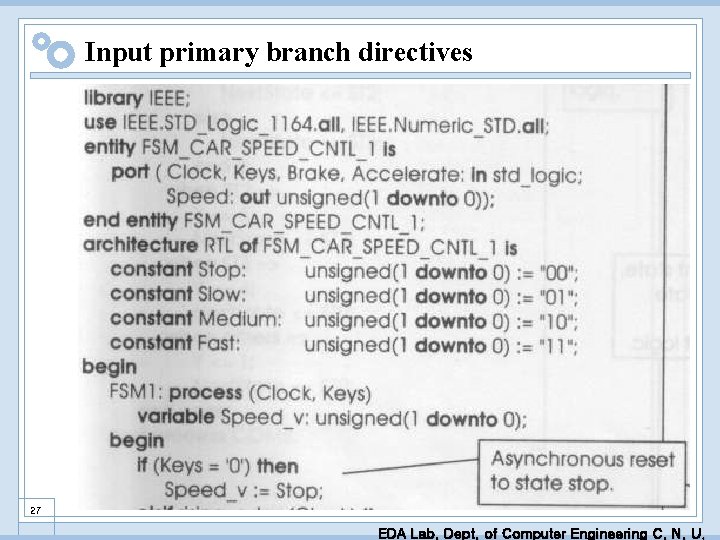

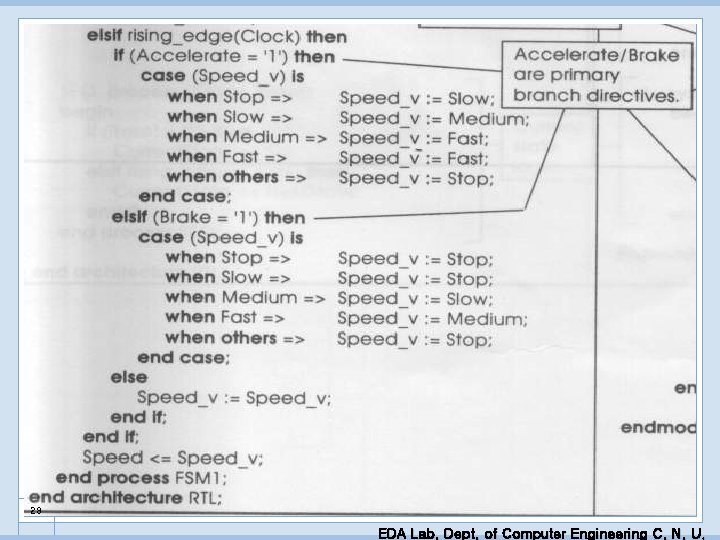

Input primary branch directives 27 EDA Lab. Dept. of Computer Engineering C. N. U.

28 EDA Lab. Dept. of Computer Engineering C. N. U.

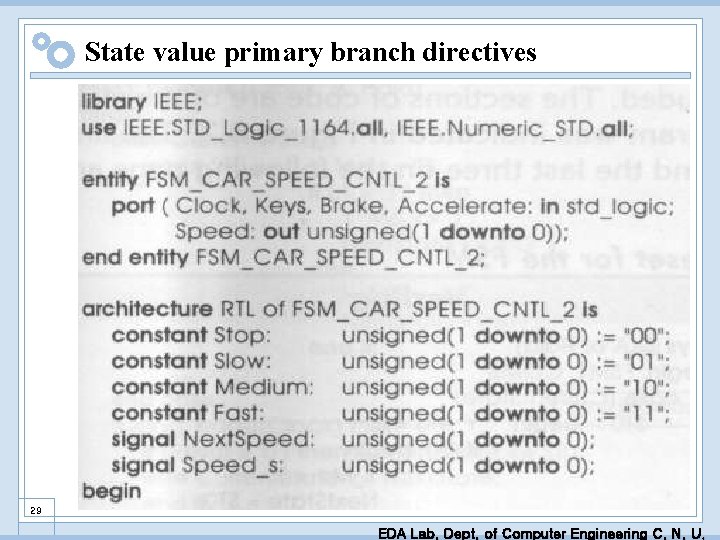

State value primary branch directives 29 EDA Lab. Dept. of Computer Engineering C. N. U.

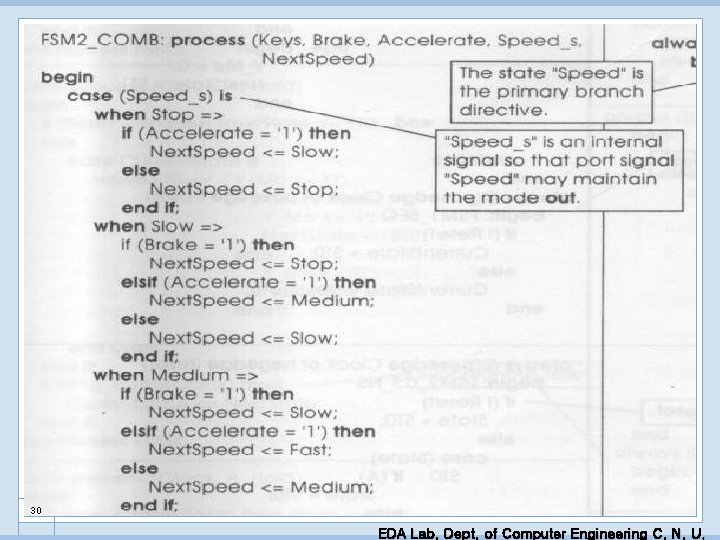

30 EDA Lab. Dept. of Computer Engineering C. N. U.

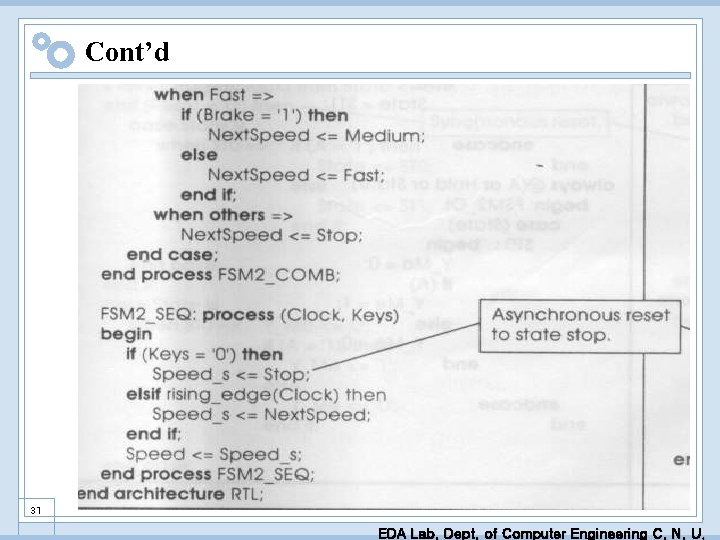

Cont’d 31 EDA Lab. Dept. of Computer Engineering C. N. U.

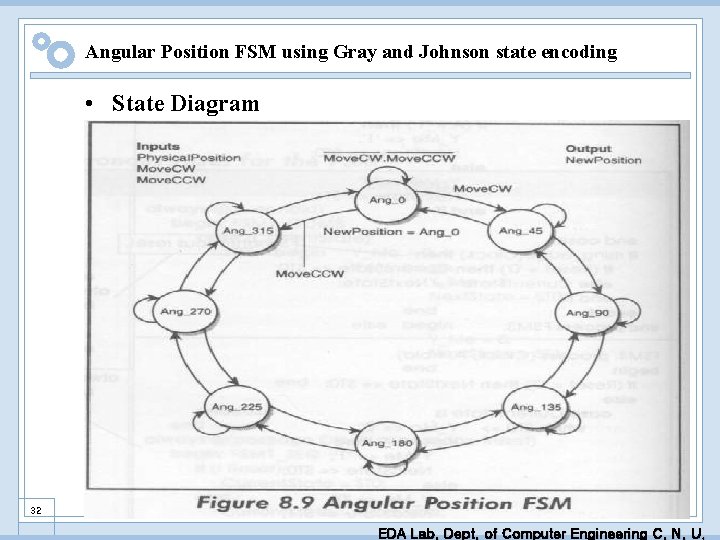

Angular Position FSM using Gray and Johnson state encoding • State Diagram 32 EDA Lab. Dept. of Computer Engineering C. N. U.

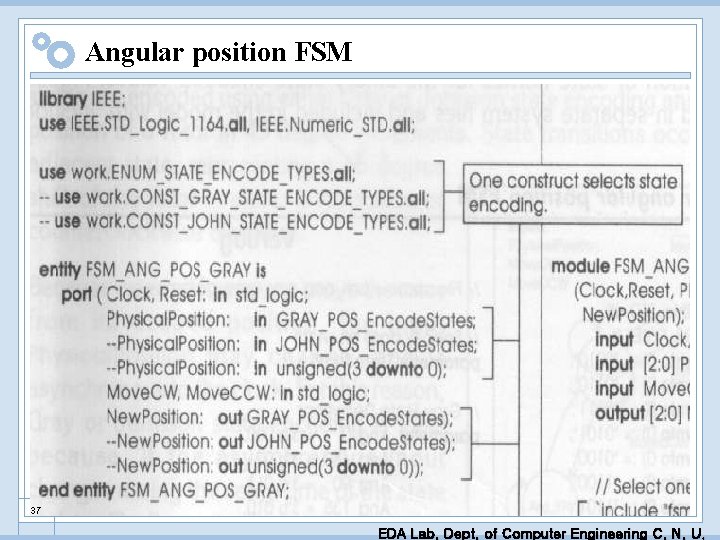

Cont’d • Input – Physical Position: asynchronous input(loaded when reset = ‘ 1’) – MOVE CW: 45˚ clock wise move – MOVE CCW: 45˚ counter clock wise move • Two ways of representing state encoding 1. Use a signal of an enumerated type for which a single synthesis specific “attribute” is applied. Attribute name is specific to the synthesis tool, not portable, needs to be changed. 33 EDA Lab. Dept. of Computer Engineering C. N. U.

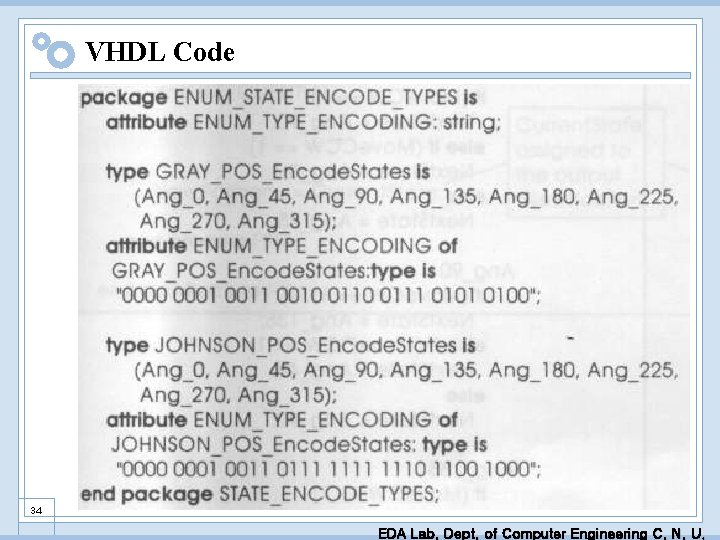

VHDL Code 34 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d 2. Use constants to represent the individual state values. It is directly portable to other synthesis tools. 35 EDA Lab. Dept. of Computer Engineering C. N. U.

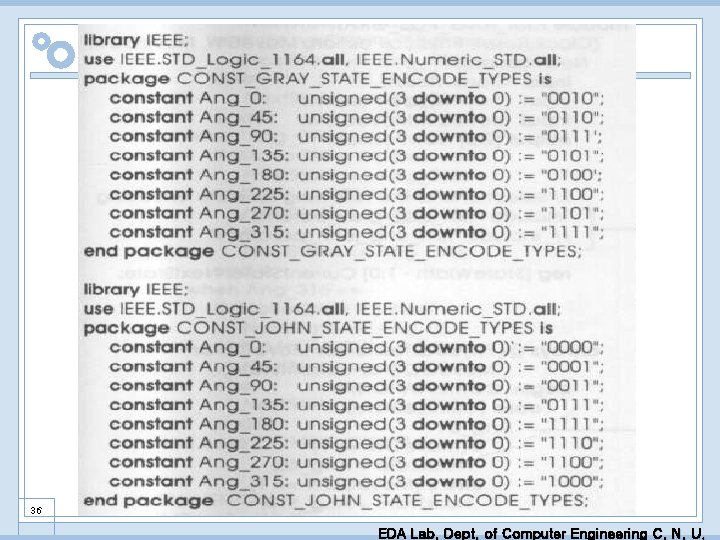

36 EDA Lab. Dept. of Computer Engineering C. N. U.

Angular position FSM 37 EDA Lab. Dept. of Computer Engineering C. N. U.

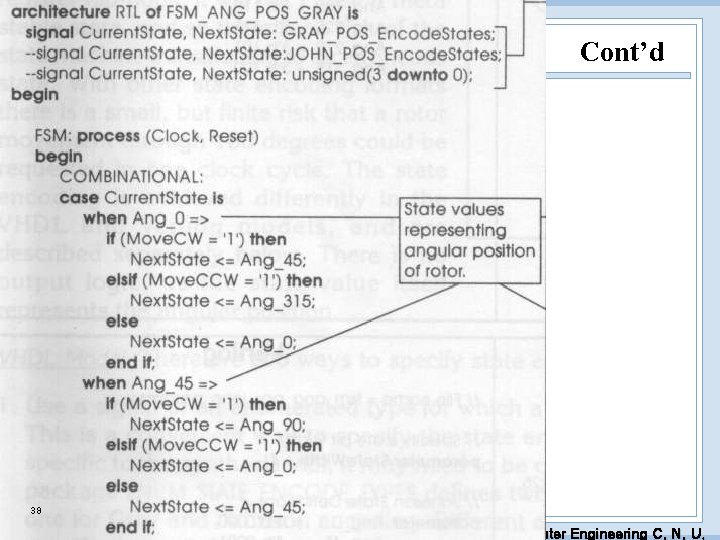

Cont’d 38 EDA Lab. Dept. of Computer Engineering C. N. U.

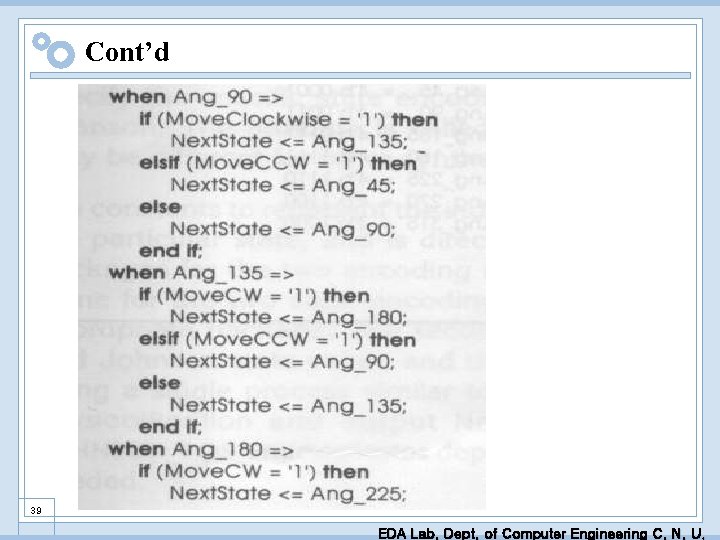

Cont’d 39 EDA Lab. Dept. of Computer Engineering C. N. U.

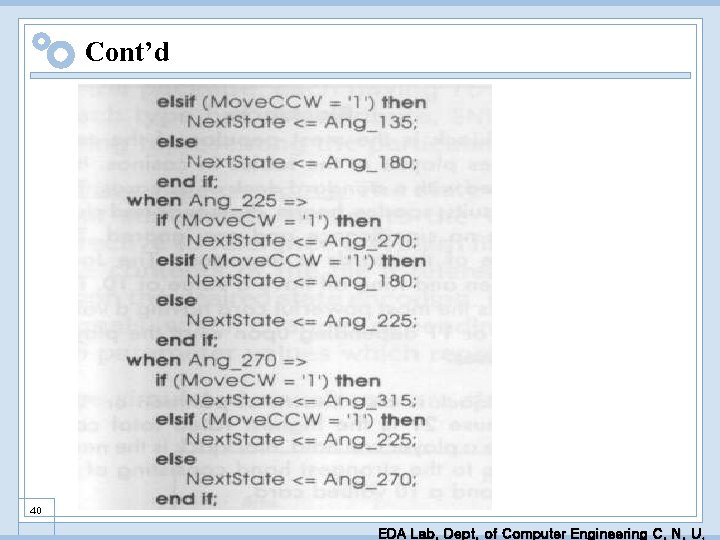

Cont’d 40 EDA Lab. Dept. of Computer Engineering C. N. U.

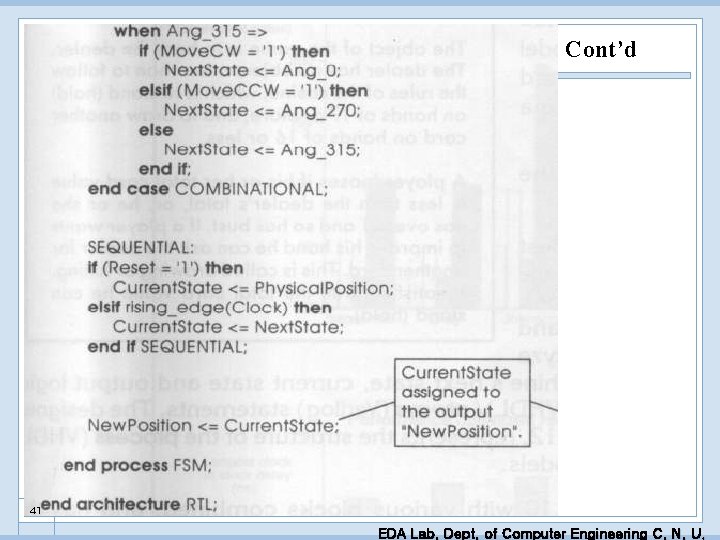

Cont’d 41 EDA Lab. Dept. of Computer Engineering C. N. U.

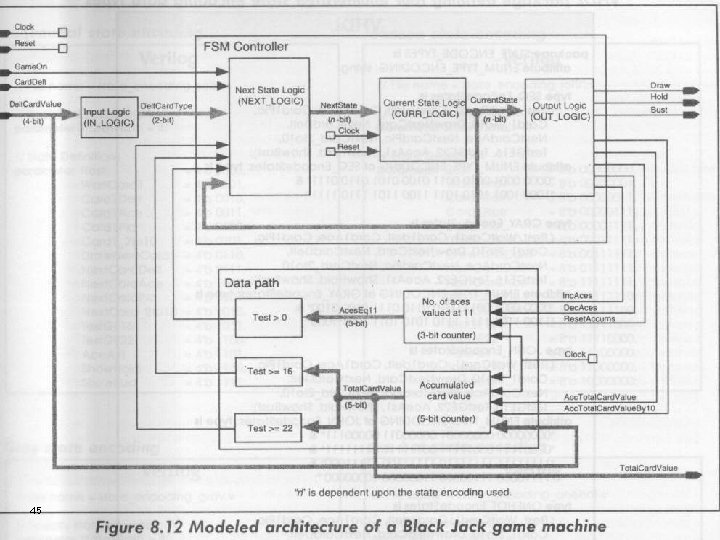

Black Jack Game Machine • Blackjack Game – Blackjack is the most popular of the card games played at the tables in casinos. It is played with a standard deck of 52 cards. The four suits; spades, hearts, diamonds and clubs have no significance and are ignored. The Jack, Queen and King all have a value of 10. The ace is the most powerful card having a value of 1 or 11 depending upon what the player chooses. – Blackjack is also known as pontoon or “ 21” because 21 is the highest rated total card value a player can hold. Blackjack is the name given to the strongest hand consisting of an ace and a 10 valued card. – The object of the game is to beat the dealer. The dealer has no object other than to follow the rules of the casino, which is to stand(hold) on hands of 17 or more, and to draw another card on hands of 16 or less. – A player looses if his or her total card value is less than the dealer’s total, or, he or she has over 21 and so has bust. If a player wants to improve his hand he can ask the dealer for another card. This is called drawing or hitting. If satisfied with the total card value he can stand(hold). 42 EDA Lab. Dept. of Computer Engineering C. N. U.

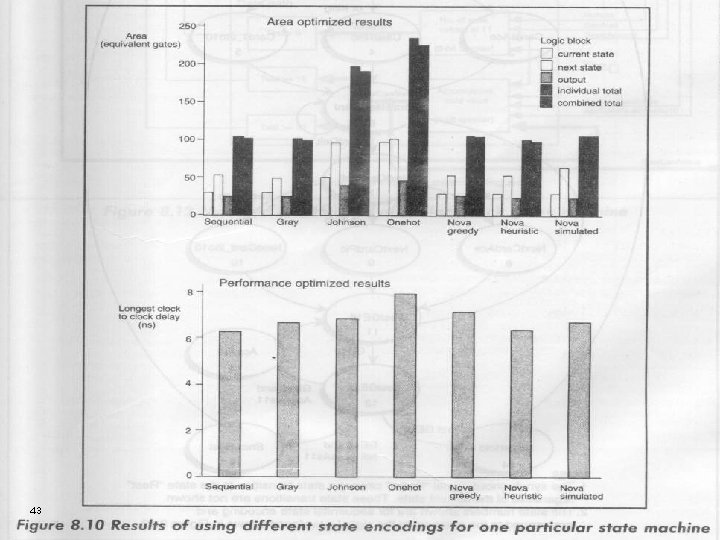

43 EDA Lab. Dept. of Computer Engineering C. N. U.

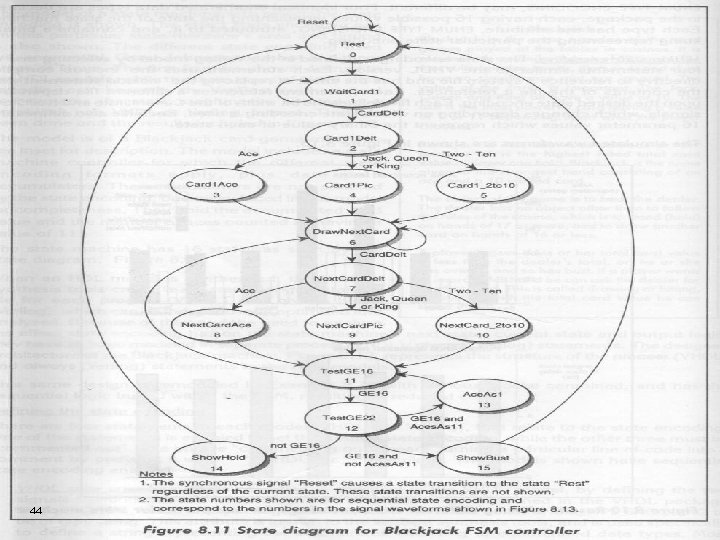

44 EDA Lab. Dept. of Computer Engineering C. N. U.

45 EDA Lab. Dept. of Computer Engineering C. N. U.

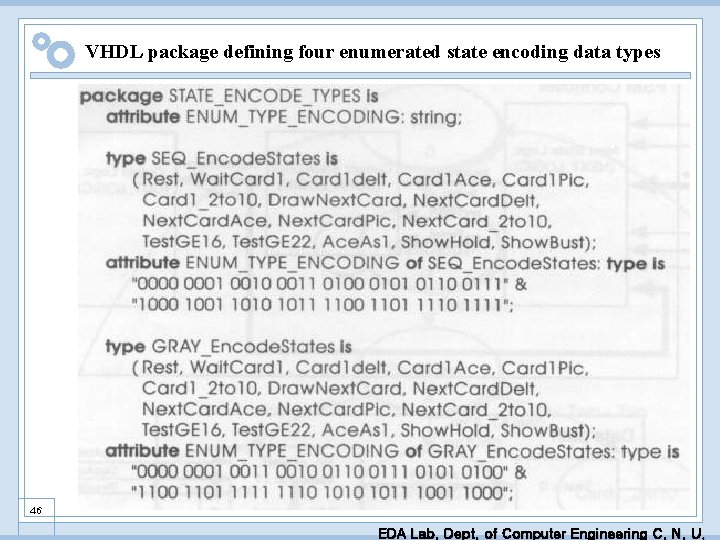

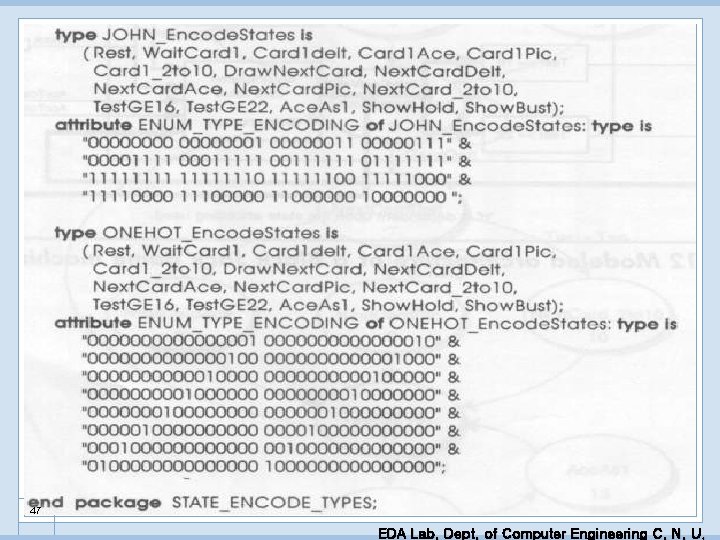

VHDL package defining four enumerated state encoding data types 46 EDA Lab. Dept. of Computer Engineering C. N. U.

47 EDA Lab. Dept. of Computer Engineering C. N. U.

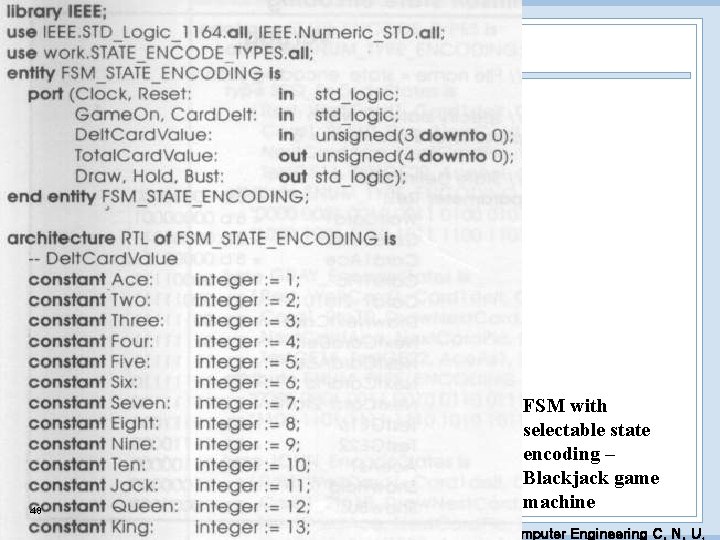

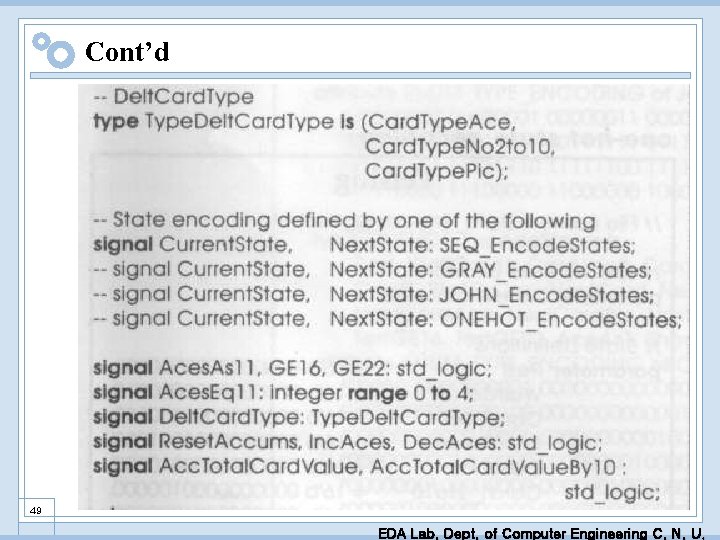

48 FSM with selectable state encoding – Blackjack game machine EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d 49 EDA Lab. Dept. of Computer Engineering C. N. U.

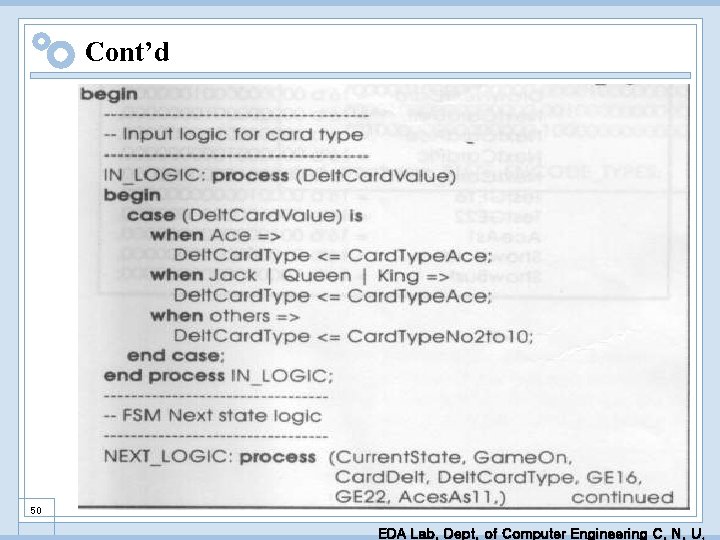

Cont’d 50 EDA Lab. Dept. of Computer Engineering C. N. U.

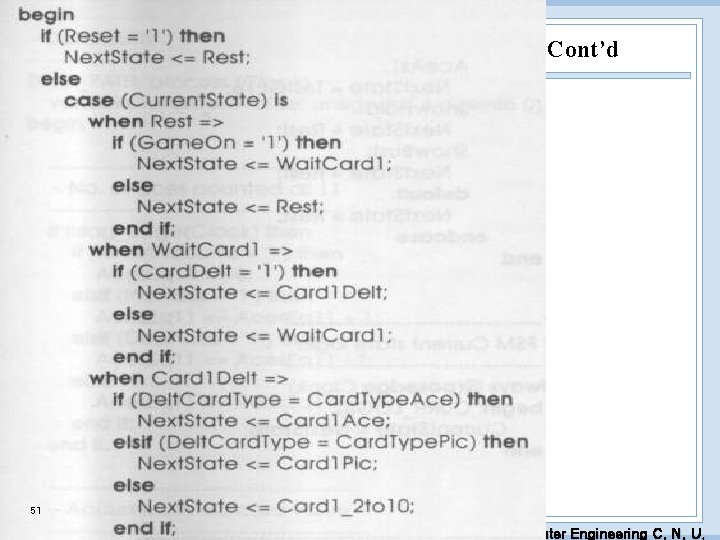

Cont’d 51 EDA Lab. Dept. of Computer Engineering C. N. U.

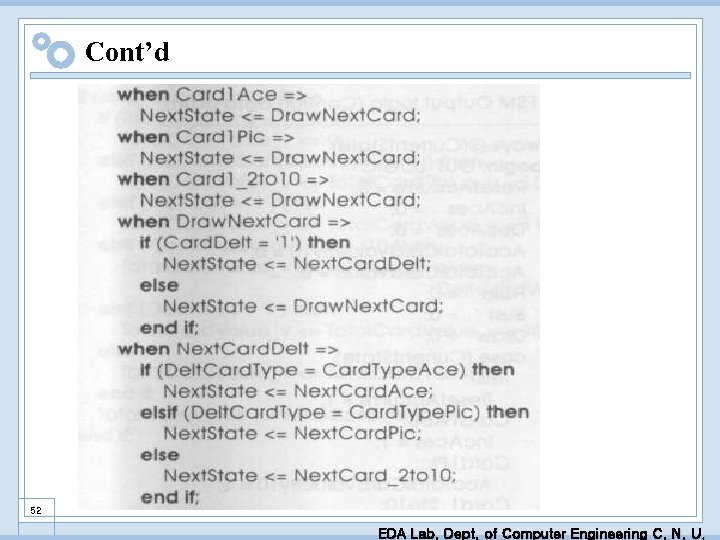

Cont’d 52 EDA Lab. Dept. of Computer Engineering C. N. U.

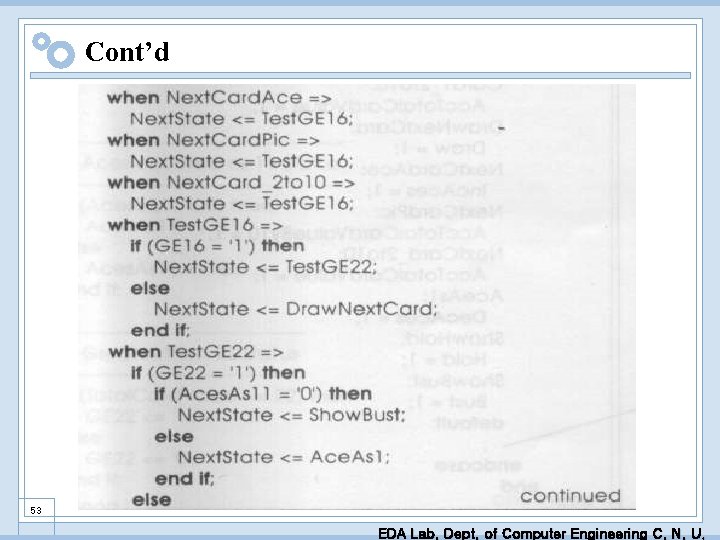

Cont’d 53 EDA Lab. Dept. of Computer Engineering C. N. U.

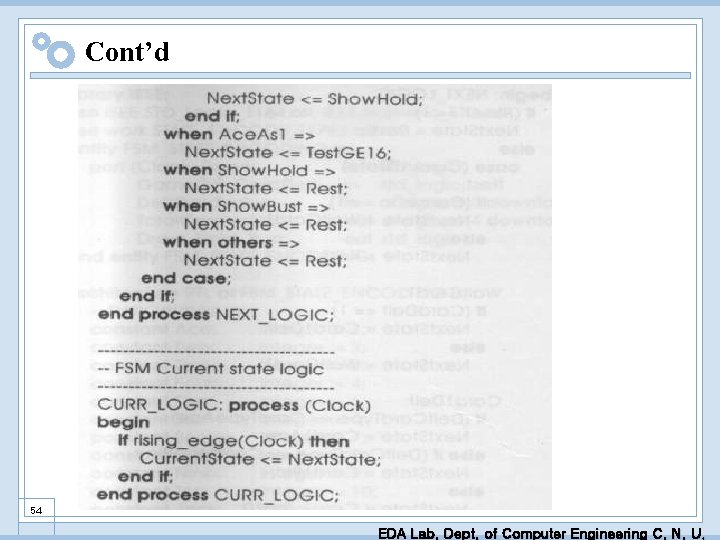

Cont’d 54 EDA Lab. Dept. of Computer Engineering C. N. U.

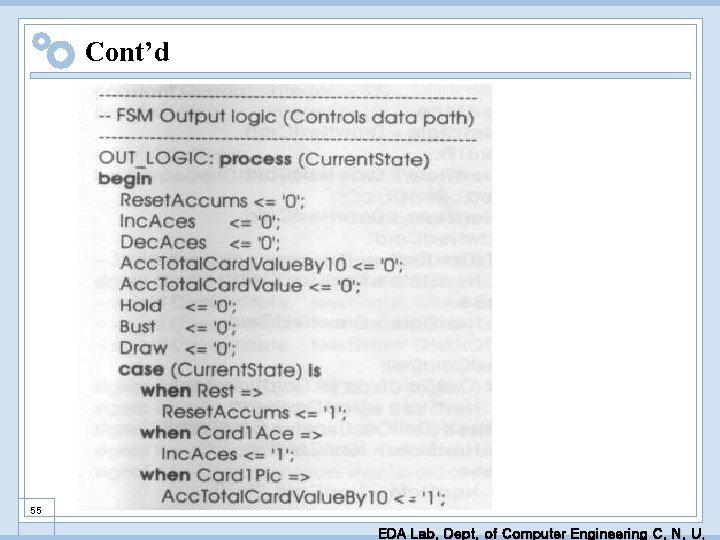

Cont’d 55 EDA Lab. Dept. of Computer Engineering C. N. U.

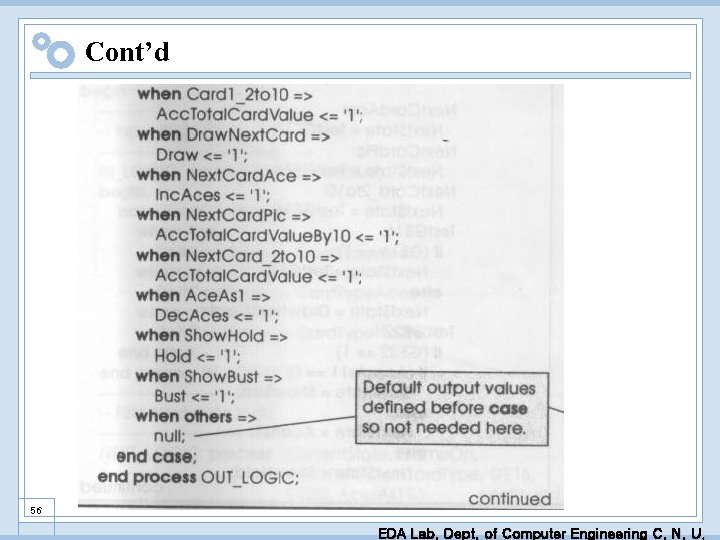

Cont’d 56 EDA Lab. Dept. of Computer Engineering C. N. U.

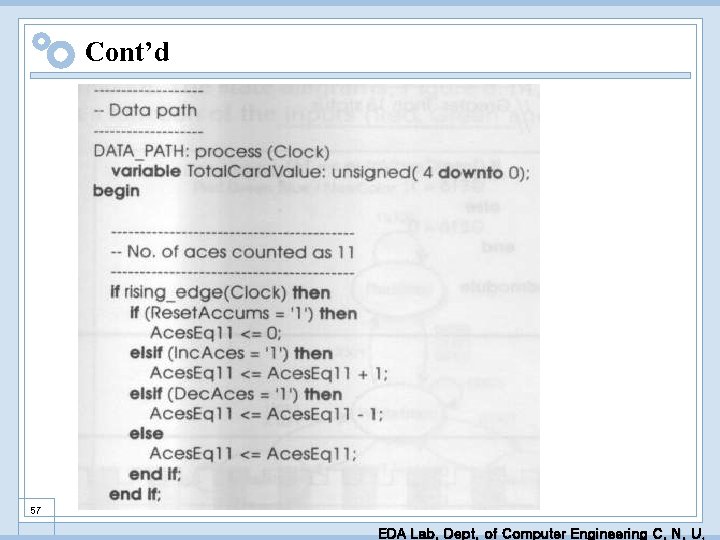

Cont’d 57 EDA Lab. Dept. of Computer Engineering C. N. U.

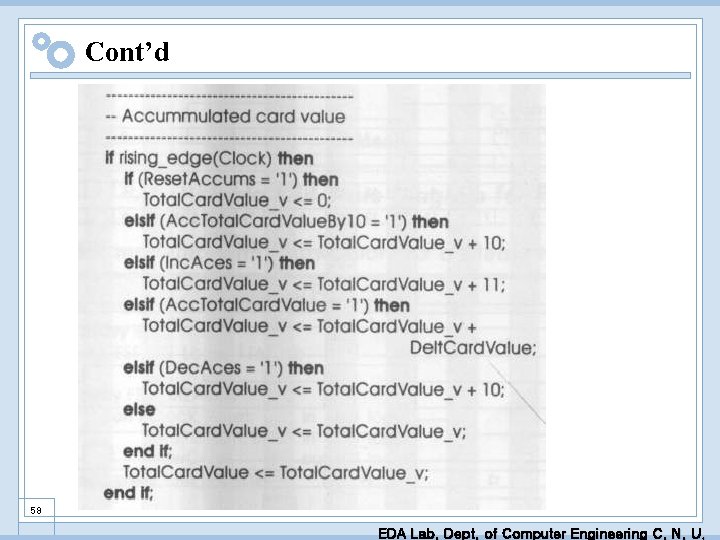

Cont’d 58 EDA Lab. Dept. of Computer Engineering C. N. U.

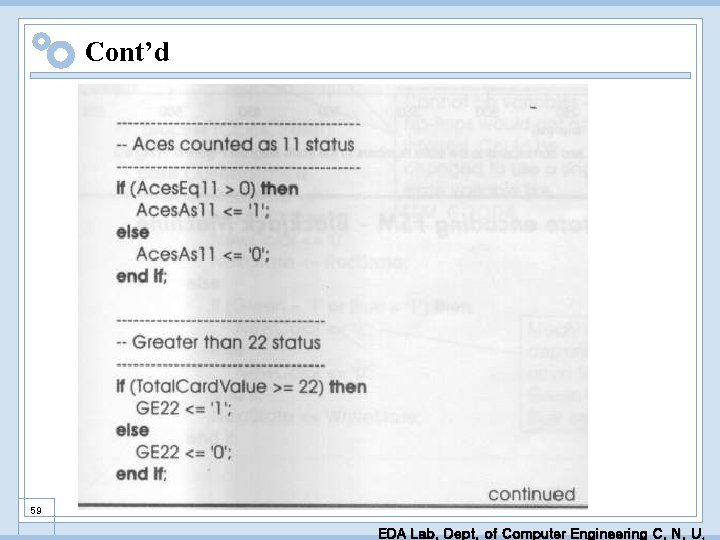

Cont’d 59 EDA Lab. Dept. of Computer Engineering C. N. U.

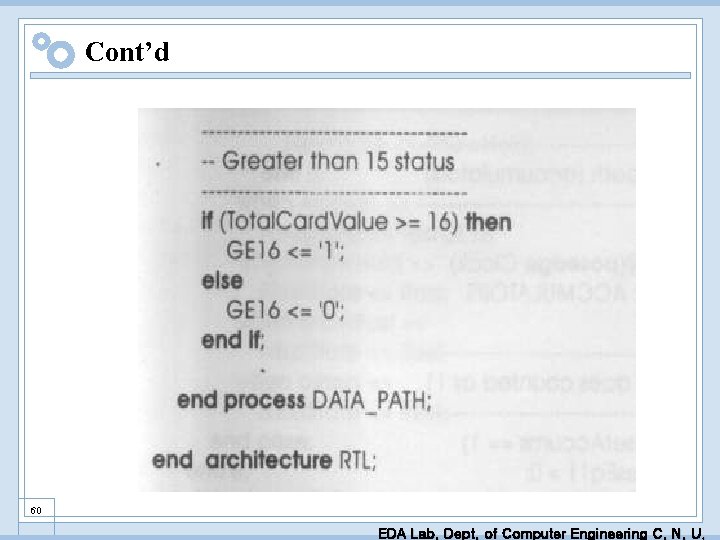

Cont’d 60 EDA Lab. Dept. of Computer Engineering C. N. U.

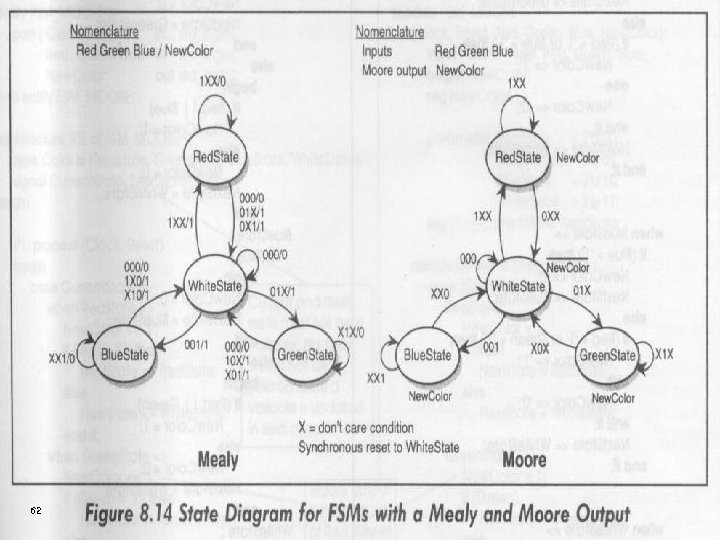

FSMs with a Mealy or Moore output • State Diagram for FSMs with a Mealy and Moore output 61 EDA Lab. Dept. of Computer Engineering C. N. U.

62 EDA Lab. Dept. of Computer Engineering C. N. U.

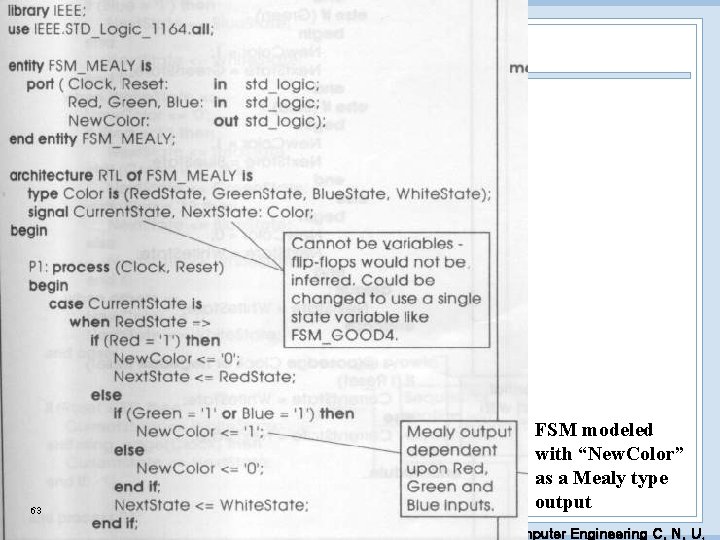

63 FSM modeled with “New. Color” as a Mealy type output EDA Lab. Dept. of Computer Engineering C. N. U.

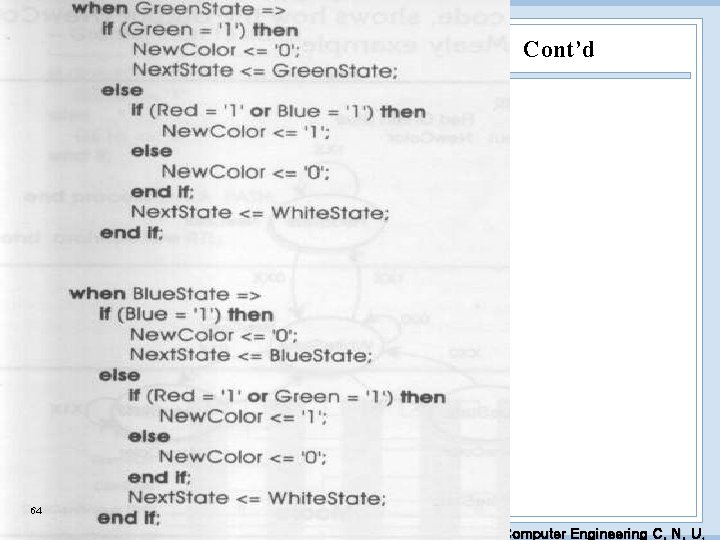

Cont’d 64 EDA Lab. Dept. of Computer Engineering C. N. U.

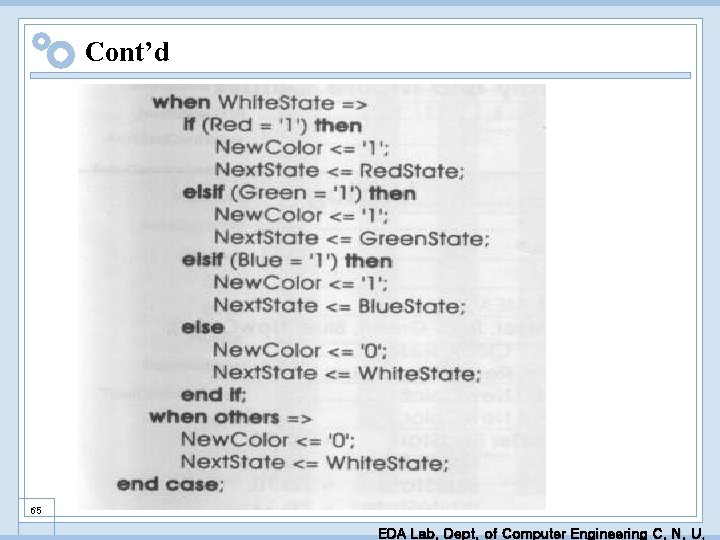

Cont’d 65 EDA Lab. Dept. of Computer Engineering C. N. U.

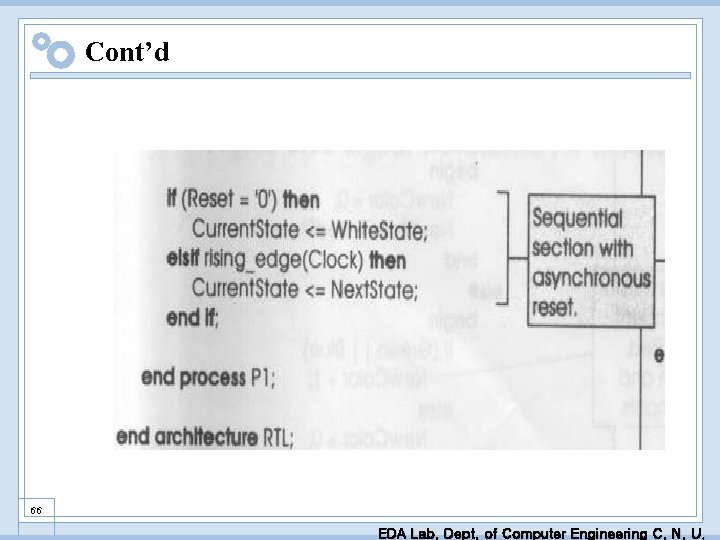

Cont’d 66 EDA Lab. Dept. of Computer Engineering C. N. U.

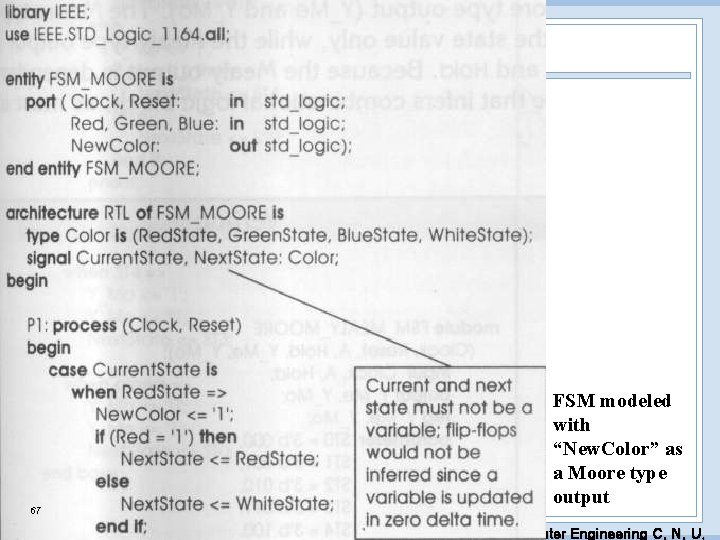

67 FSM modeled with “New. Color” as a Moore type output EDA Lab. Dept. of Computer Engineering C. N. U.

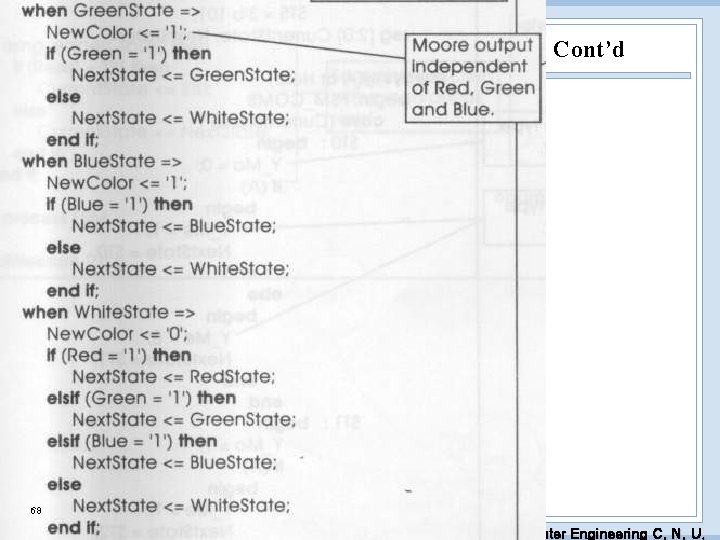

Cont’d 68 EDA Lab. Dept. of Computer Engineering C. N. U.

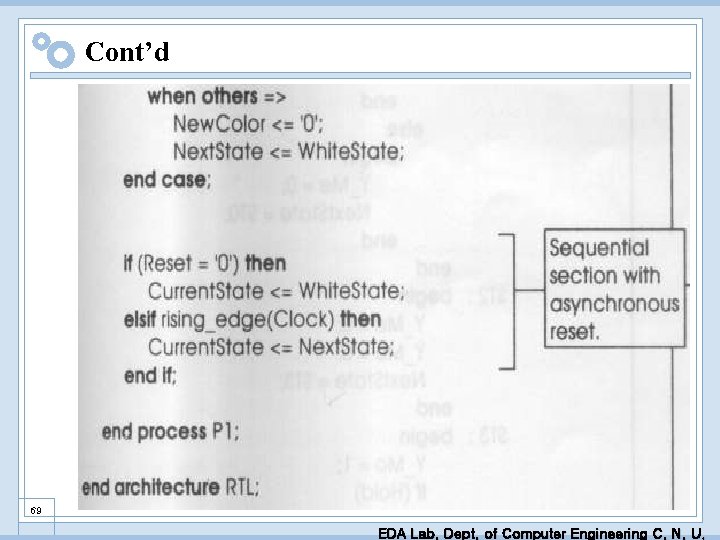

Cont’d 69 EDA Lab. Dept. of Computer Engineering C. N. U.

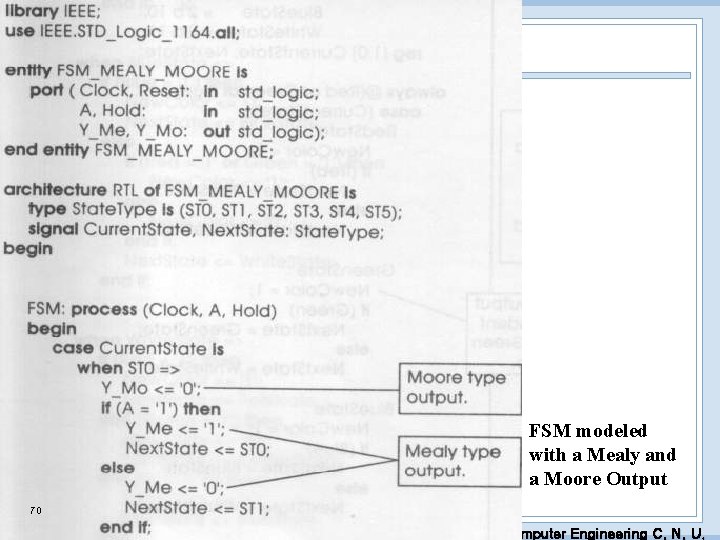

FSM modeled with a Mealy and a Moore Output 70 EDA Lab. Dept. of Computer Engineering C. N. U.

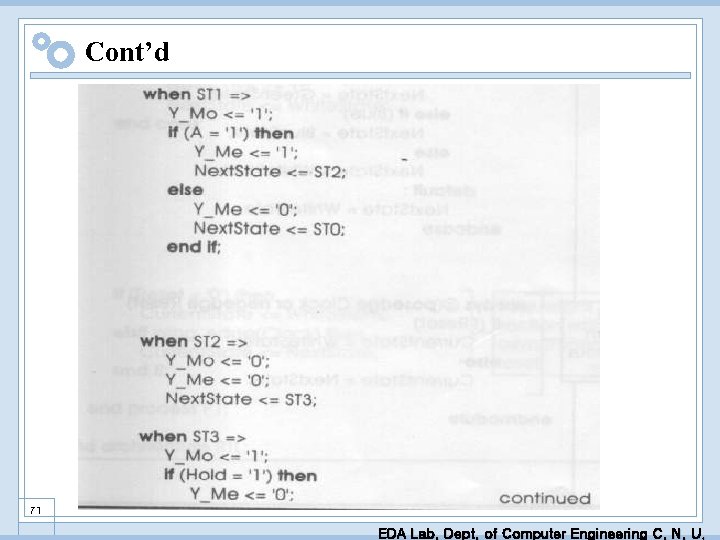

Cont’d 71 EDA Lab. Dept. of Computer Engineering C. N. U.

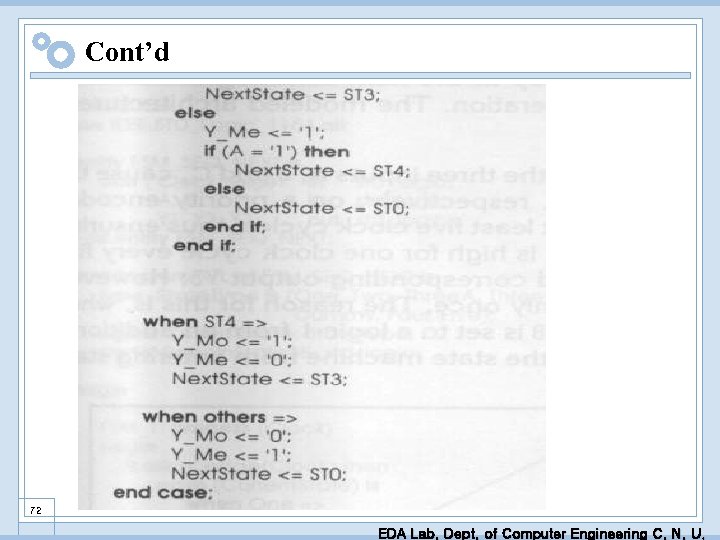

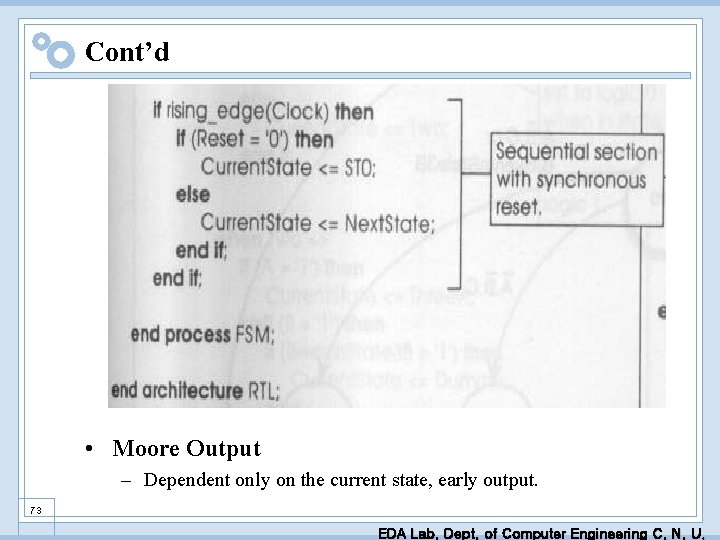

Cont’d 72 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d • Moore Output – Dependent only on the current state, early output. 73 EDA Lab. Dept. of Computer Engineering C. N. U.

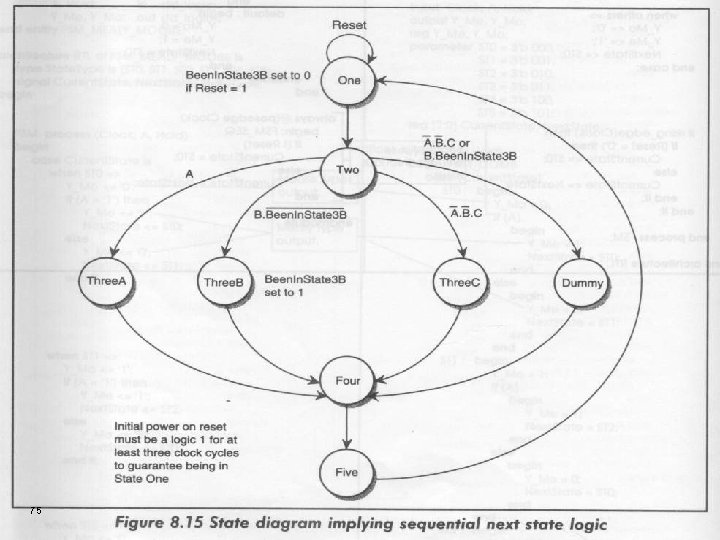

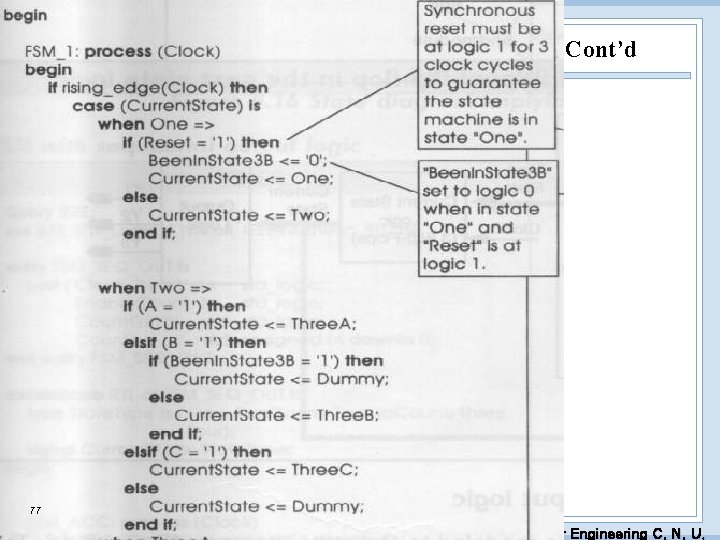

FSM with sequential next state logic • Extra FF in the next state logic. • State Diagram – Beenln. State 3 B (extra FF) 74 EDA Lab. Dept. of Computer Engineering C. N. U.

75 EDA Lab. Dept. of Computer Engineering C. N. U.

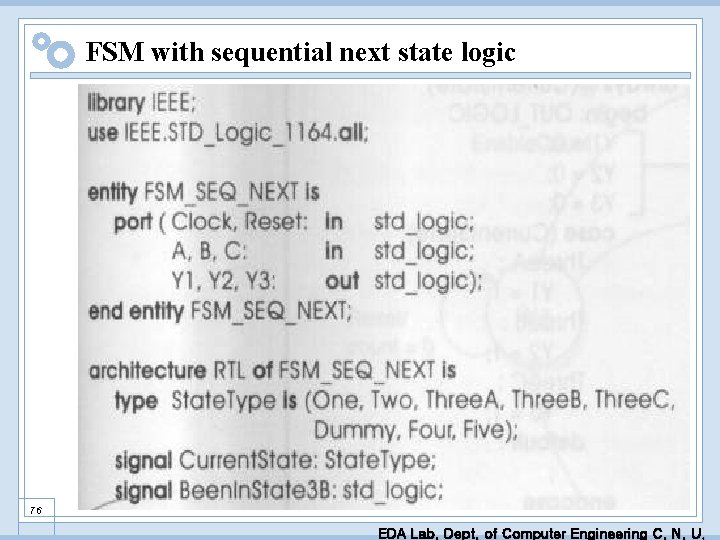

FSM with sequential next state logic 76 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d 77 EDA Lab. Dept. of Computer Engineering C. N. U.

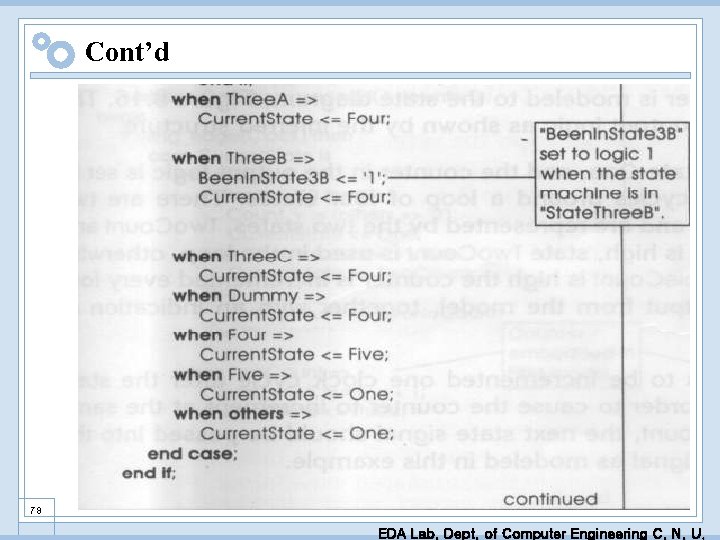

Cont’d 78 EDA Lab. Dept. of Computer Engineering C. N. U.

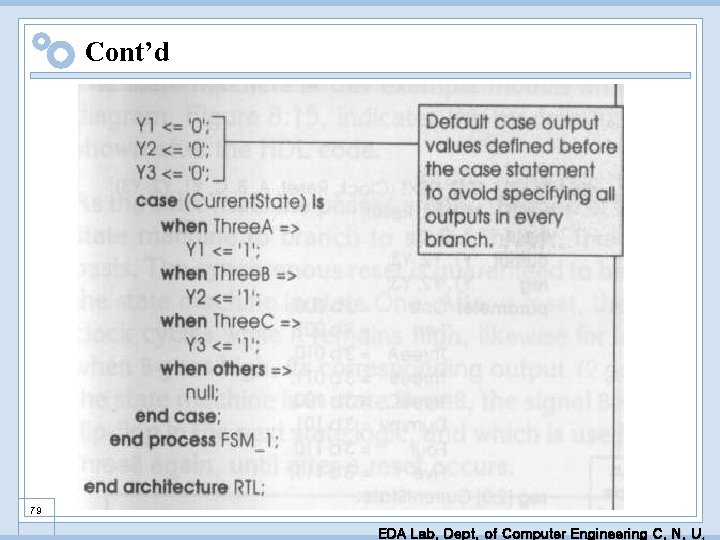

Cont’d 79 EDA Lab. Dept. of Computer Engineering C. N. U.

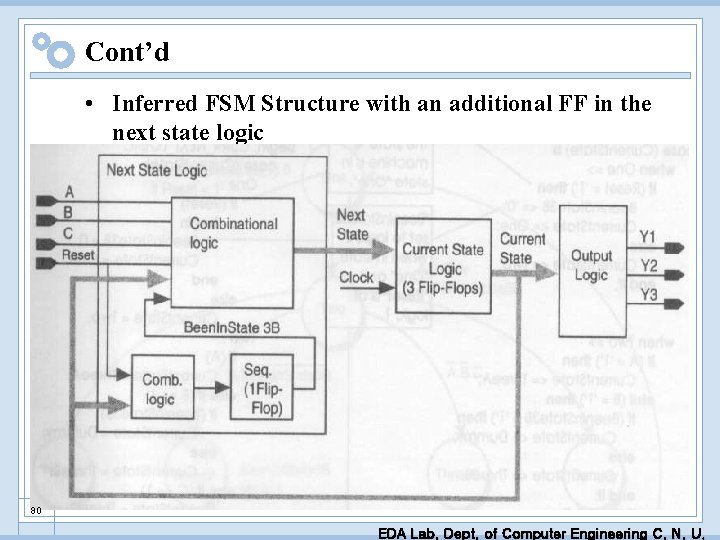

Cont’d • Inferred FSM Structure with an additional FF in the next state logic 80 EDA Lab. Dept. of Computer Engineering C. N. U.

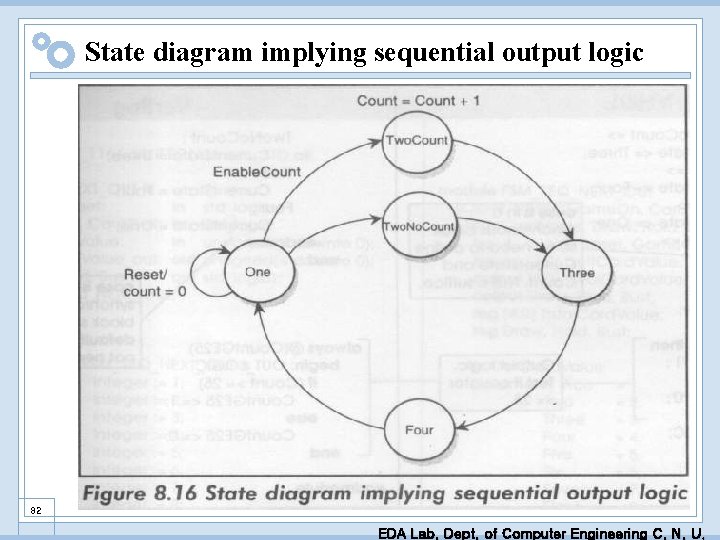

FSM with sequential output logic • FSM with sequential output logic – State machine with an embedded counter • Counter: parts of the state machine’s output logic. – State diagram implying sequential output logic 81 EDA Lab. Dept. of Computer Engineering C. N. U.

State diagram implying sequential output logic 82 EDA Lab. Dept. of Computer Engineering C. N. U.

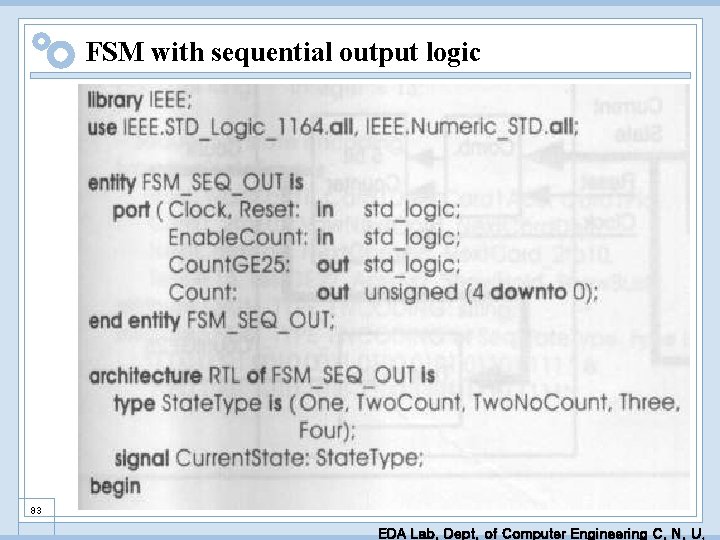

FSM with sequential output logic 83 EDA Lab. Dept. of Computer Engineering C. N. U.

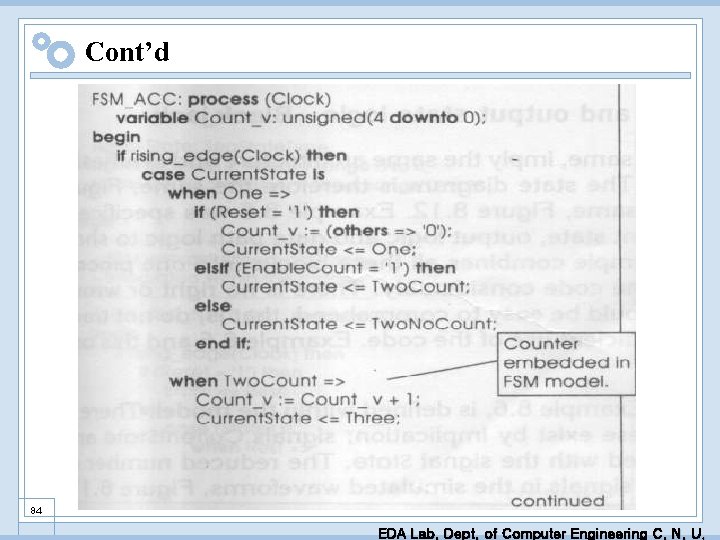

Cont’d 84 EDA Lab. Dept. of Computer Engineering C. N. U.

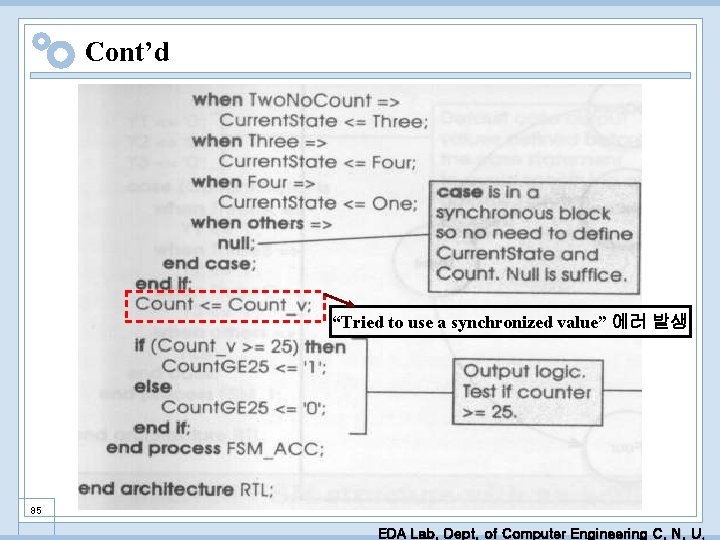

Cont’d “Tried to use a synchronized value” 에러 발생 85 EDA Lab. Dept. of Computer Engineering C. N. U.

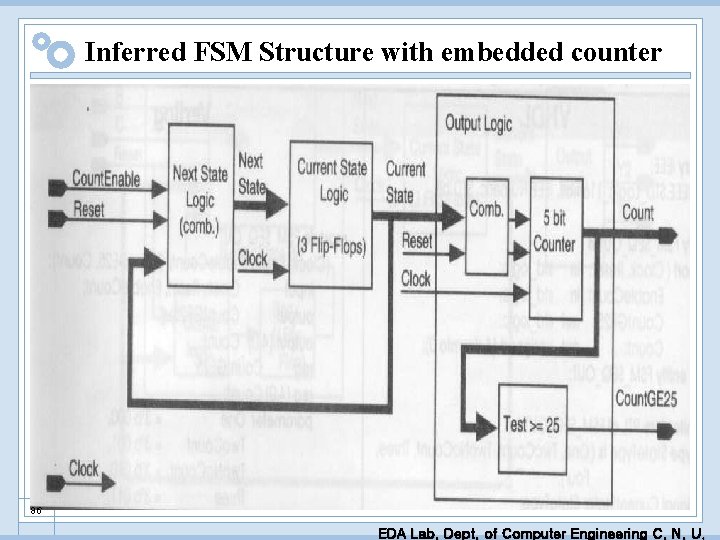

Inferred FSM Structure with embedded counter 86 EDA Lab. Dept. of Computer Engineering C. N. U.

FSM with sequential next state and output logic - Blackjack • Figure 8. 12 State Diagram – VHDL coded with one single process statement. 87 EDA Lab. Dept. of Computer Engineering C. N. U.

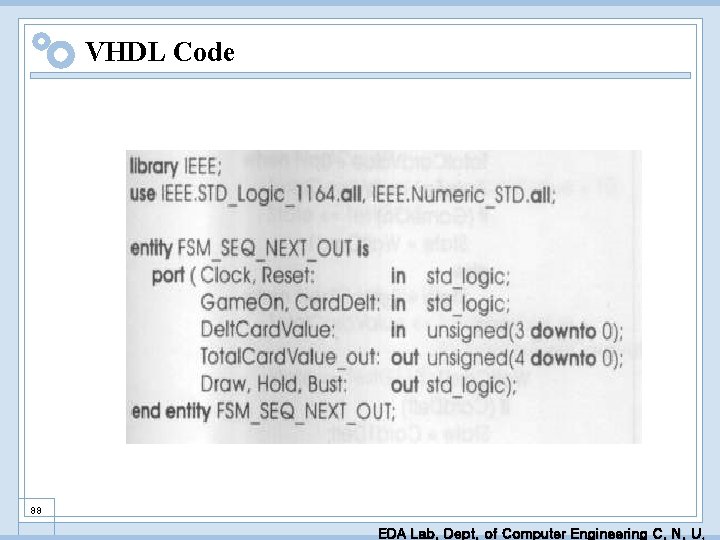

VHDL Code 88 EDA Lab. Dept. of Computer Engineering C. N. U.

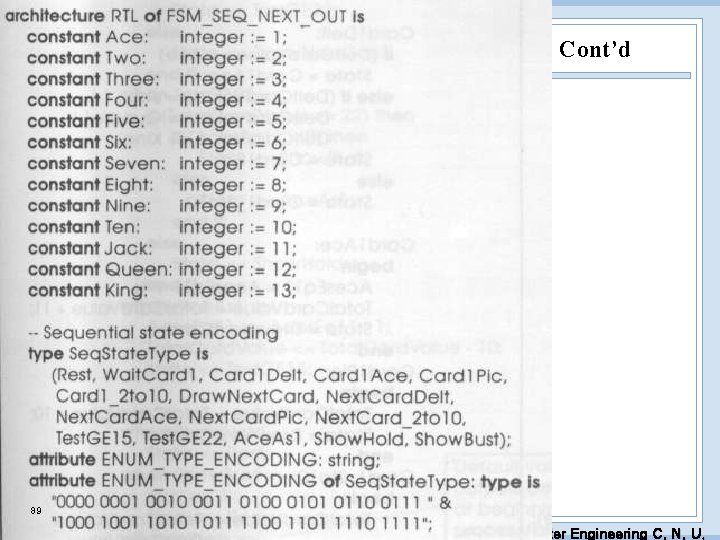

Cont’d 89 EDA Lab. Dept. of Computer Engineering C. N. U.

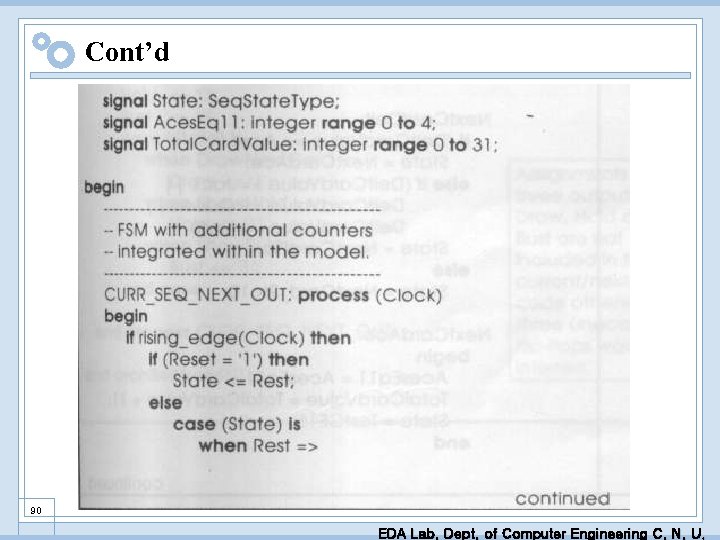

Cont’d 90 EDA Lab. Dept. of Computer Engineering C. N. U.

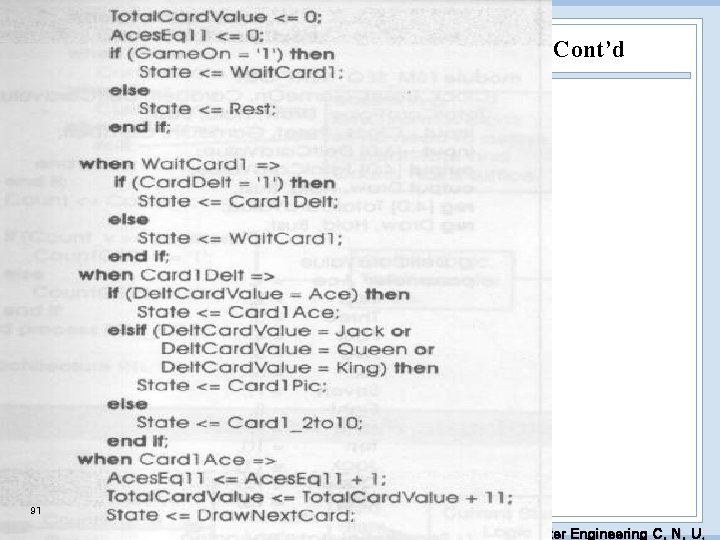

Cont’d 91 EDA Lab. Dept. of Computer Engineering C. N. U.

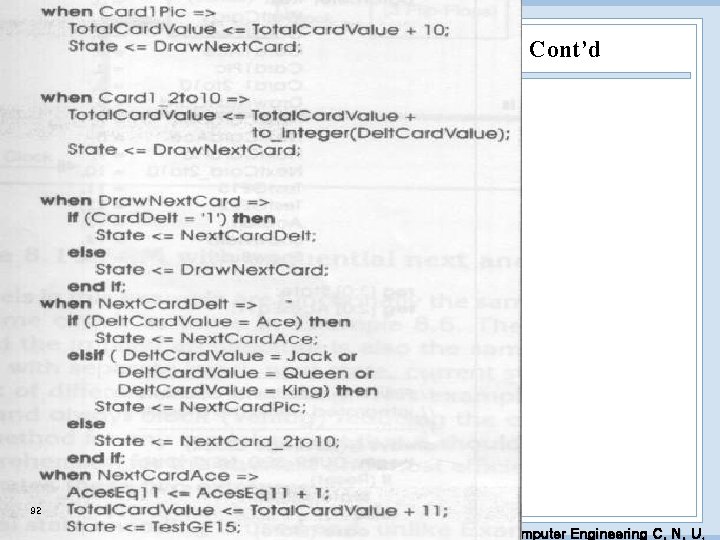

Cont’d 92 EDA Lab. Dept. of Computer Engineering C. N. U.

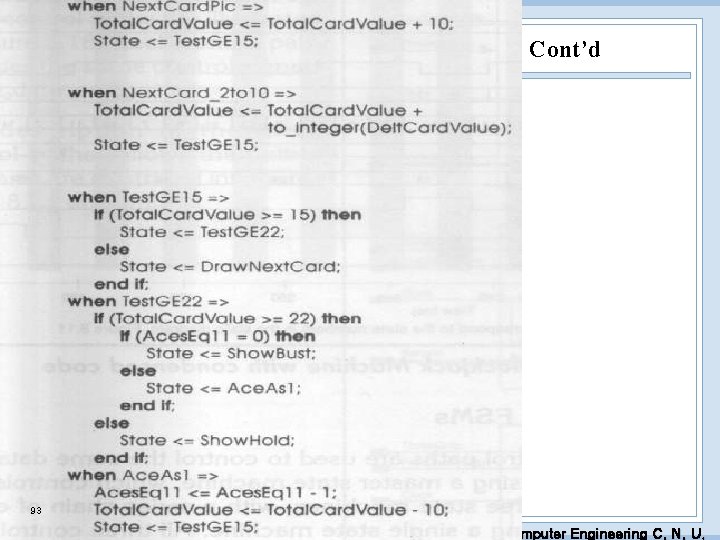

Cont’d 93 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d 94 EDA Lab. Dept. of Computer Engineering C. N. U.

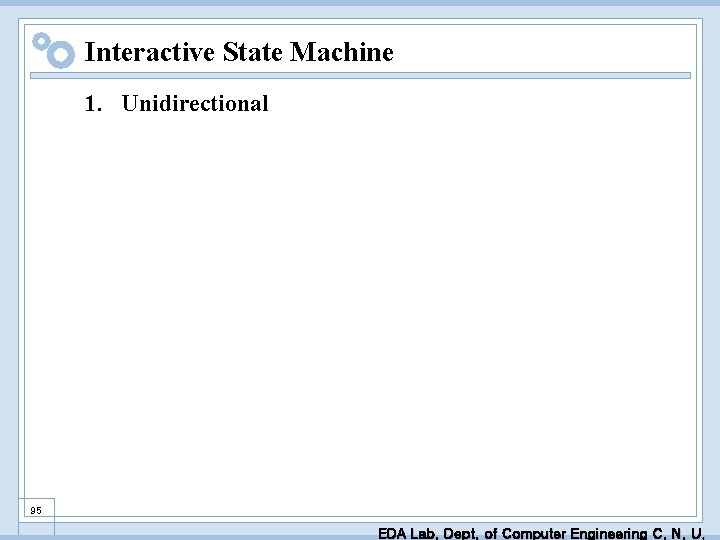

Interactive State Machine 1. Unidirectional 95 EDA Lab. Dept. of Computer Engineering C. N. U.

96 EDA Lab. Dept. of Computer Engineering C. N. U.

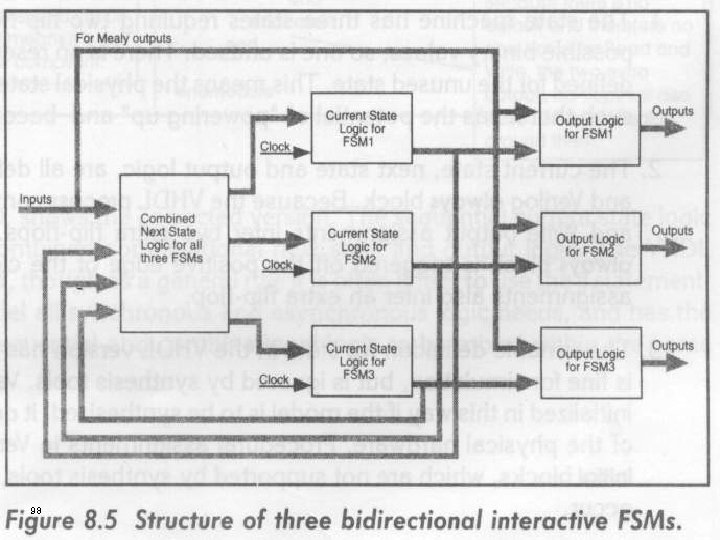

Interactive State Machine 2. Bidirectional 97 EDA Lab. Dept. of Computer Engineering C. N. U.

98 EDA Lab. Dept. of Computer Engineering C. N. U.

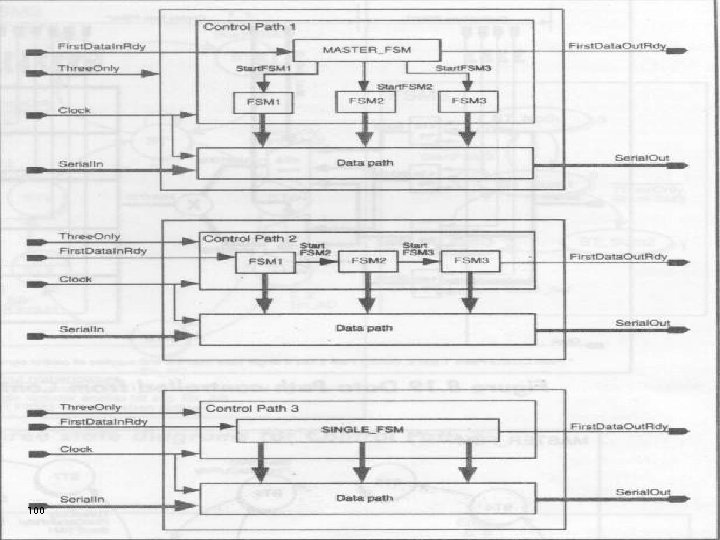

Unidirectional interactive FSMs • Three different ways of controlling data path with unidirectional interactive FSMs 99 EDA Lab. Dept. of Computer Engineering C. N. U.

100 EDA Lab. Dept. of Computer Engineering C. N. U.

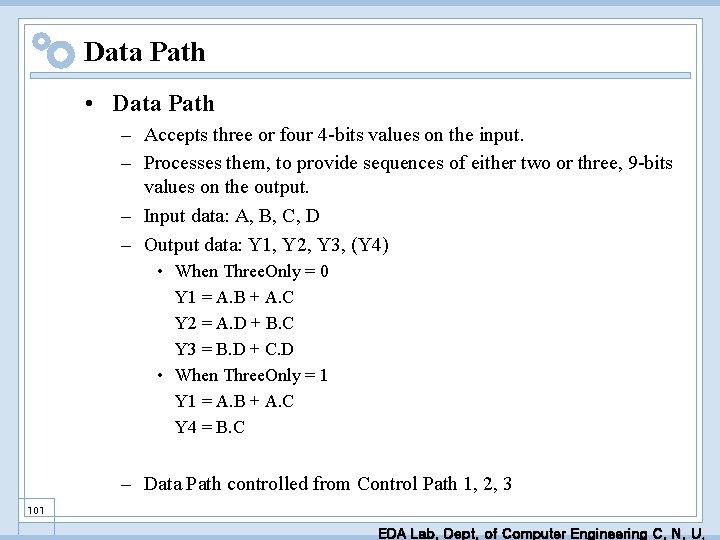

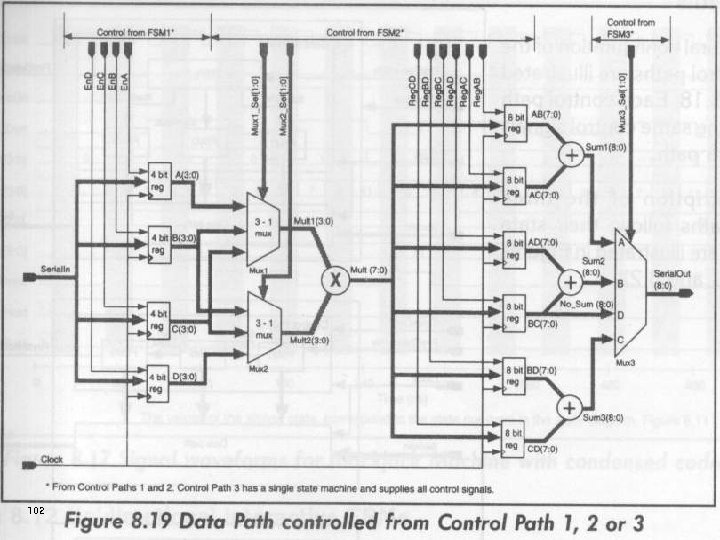

Data Path • Data Path – Accepts three or four 4 -bits values on the input. – Processes them, to provide sequences of either two or three, 9 -bits values on the output. – Input data: A, B, C, D – Output data: Y 1, Y 2, Y 3, (Y 4) • When Three. Only = 0 Y 1 = A. B + A. C Y 2 = A. D + B. C Y 3 = B. D + C. D • When Three. Only = 1 Y 1 = A. B + A. C Y 4 = B. C – Data Path controlled from Control Path 1, 2, 3 101 EDA Lab. Dept. of Computer Engineering C. N. U.

102 EDA Lab. Dept. of Computer Engineering C. N. U.

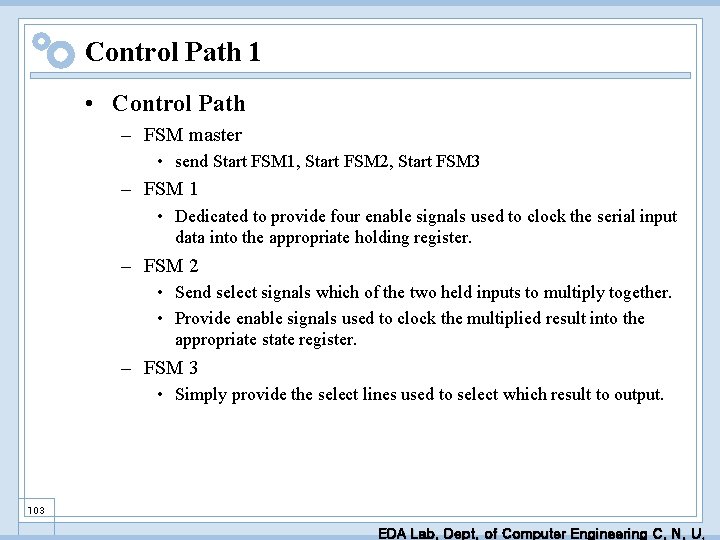

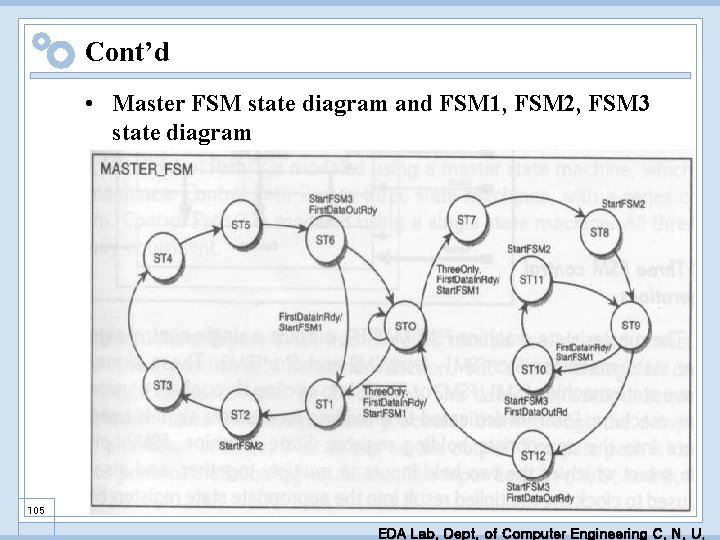

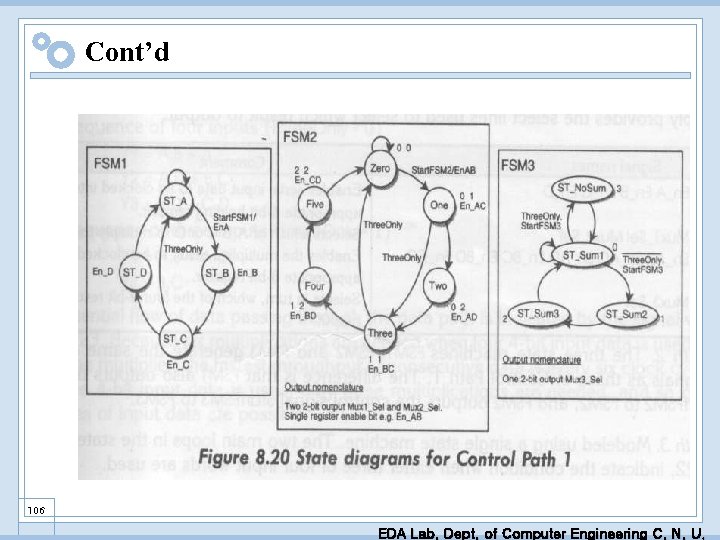

Control Path 1 • Control Path – FSM master • send Start FSM 1, Start FSM 2, Start FSM 3 – FSM 1 • Dedicated to provide four enable signals used to clock the serial input data into the appropriate holding register. – FSM 2 • Send select signals which of the two held inputs to multiply together. • Provide enable signals used to clock the multiplied result into the appropriate state register. – FSM 3 • Simply provide the select lines used to select which result to output. 103 EDA Lab. Dept. of Computer Engineering C. N. U.

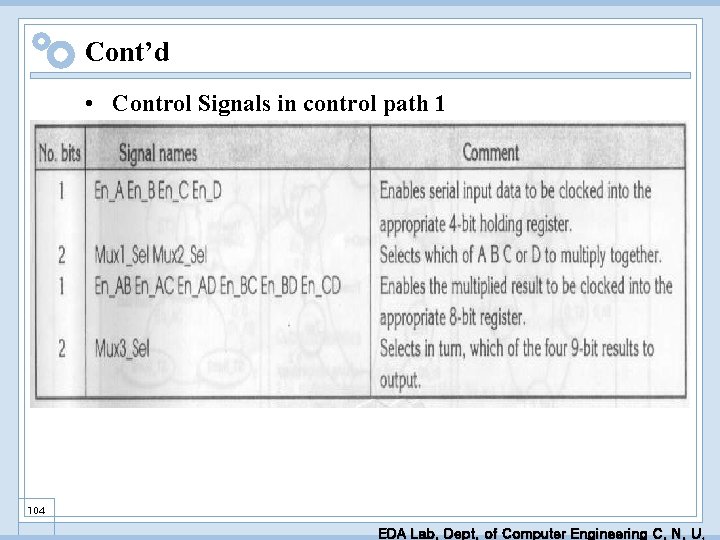

Cont’d • Control Signals in control path 1 104 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d • Master FSM state diagram and FSM 1, FSM 2, FSM 3 state diagram 105 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d 106 EDA Lab. Dept. of Computer Engineering C. N. U.

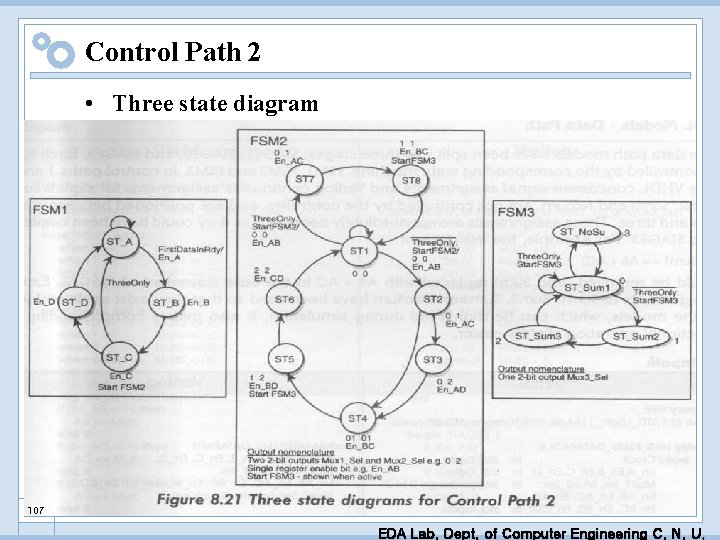

Control Path 2 • Three state diagram 107 EDA Lab. Dept. of Computer Engineering C. N. U.

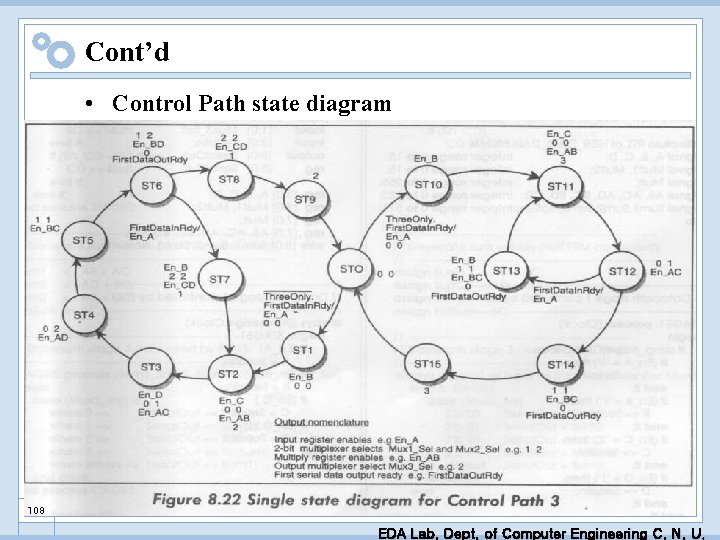

Cont’d • Control Path state diagram 108 EDA Lab. Dept. of Computer Engineering C. N. U.

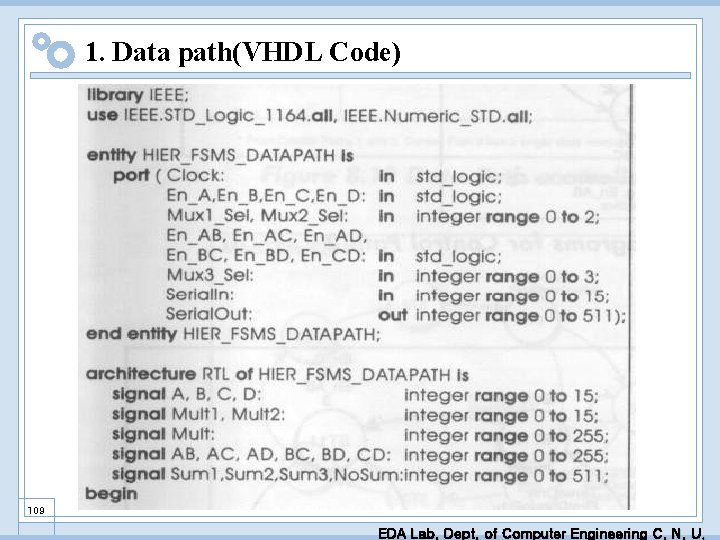

1. Data path(VHDL Code) 109 EDA Lab. Dept. of Computer Engineering C. N. U.

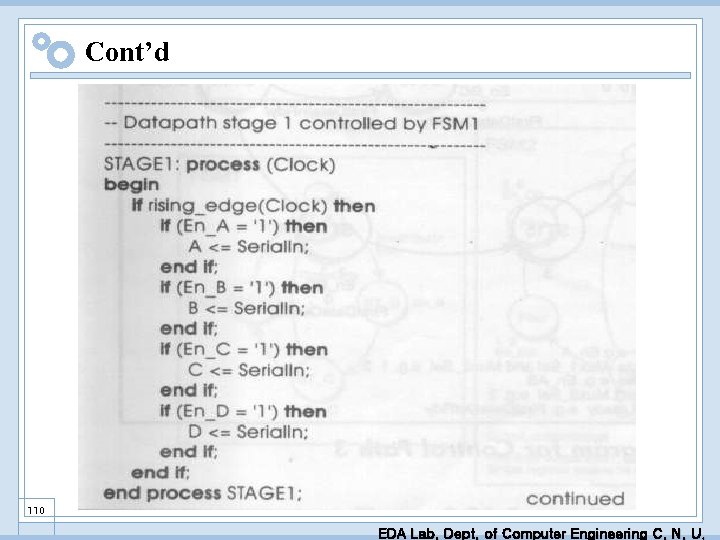

Cont’d 110 EDA Lab. Dept. of Computer Engineering C. N. U.

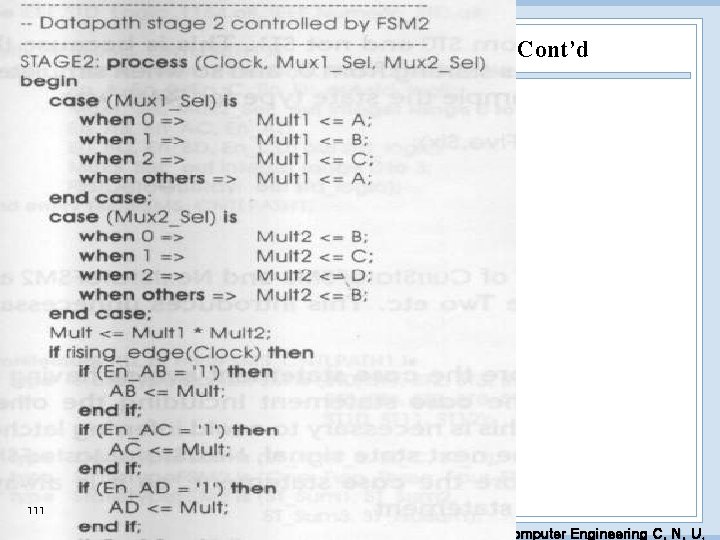

Cont’d 111 EDA Lab. Dept. of Computer Engineering C. N. U.

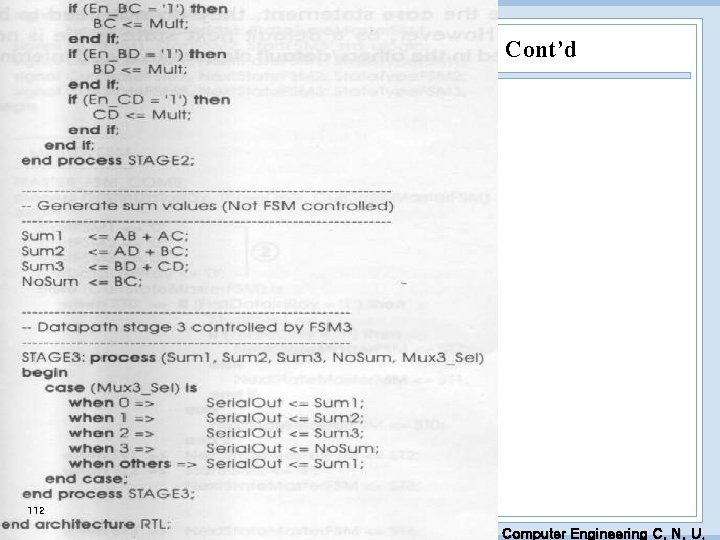

Cont’d 112 EDA Lab. Dept. of Computer Engineering C. N. U.

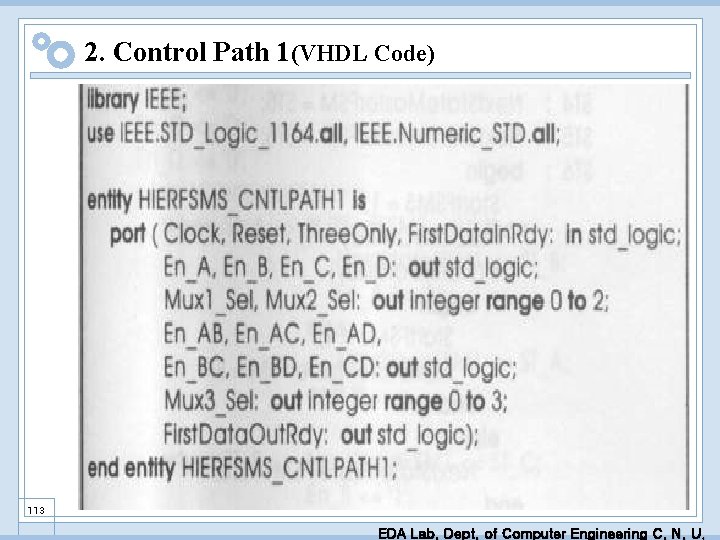

2. Control Path 1(VHDL Code) 113 EDA Lab. Dept. of Computer Engineering C. N. U.

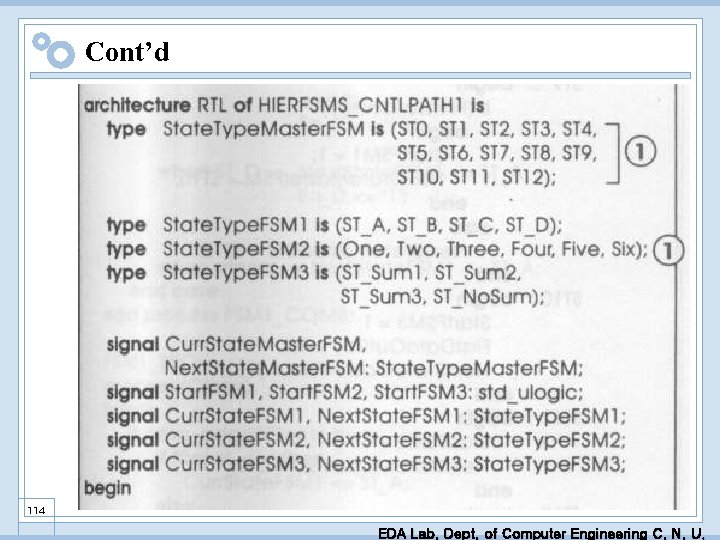

Cont’d 114 EDA Lab. Dept. of Computer Engineering C. N. U.

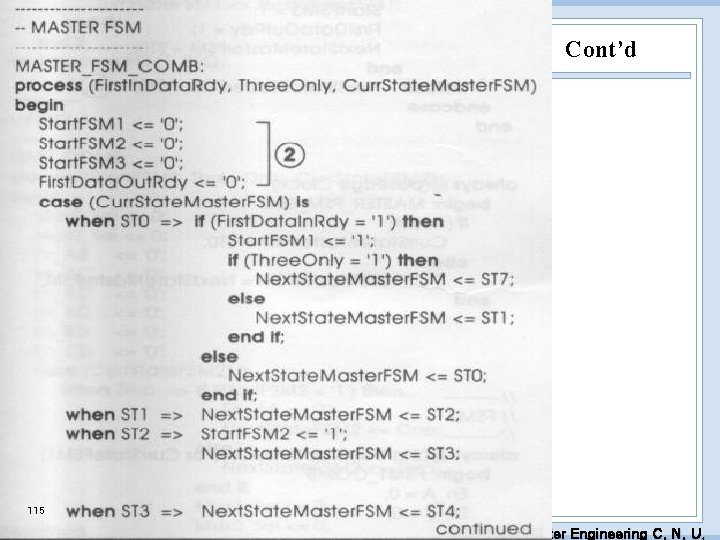

Cont’d 115 EDA Lab. Dept. of Computer Engineering C. N. U.

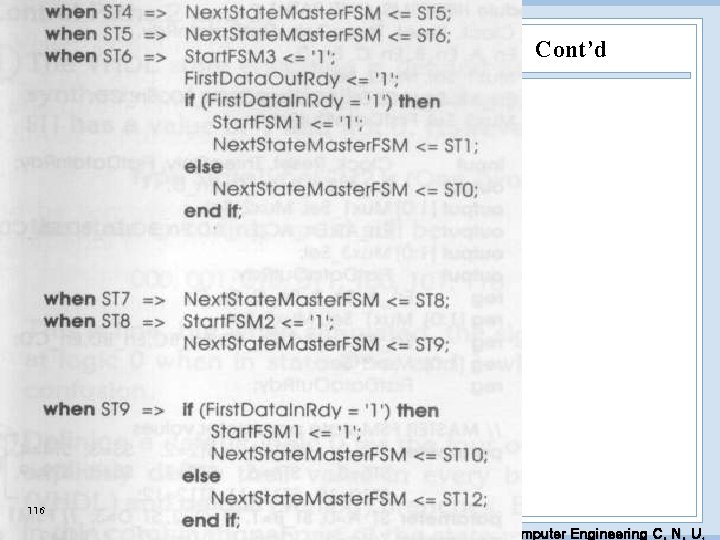

Cont’d 116 EDA Lab. Dept. of Computer Engineering C. N. U.

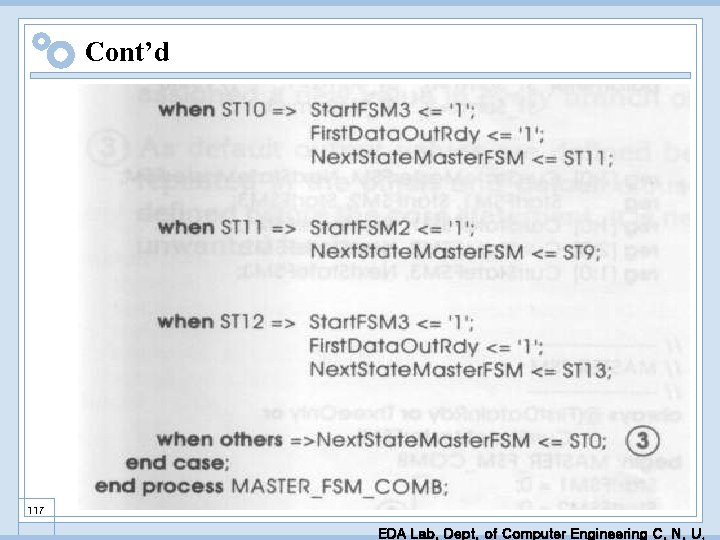

Cont’d 117 EDA Lab. Dept. of Computer Engineering C. N. U.

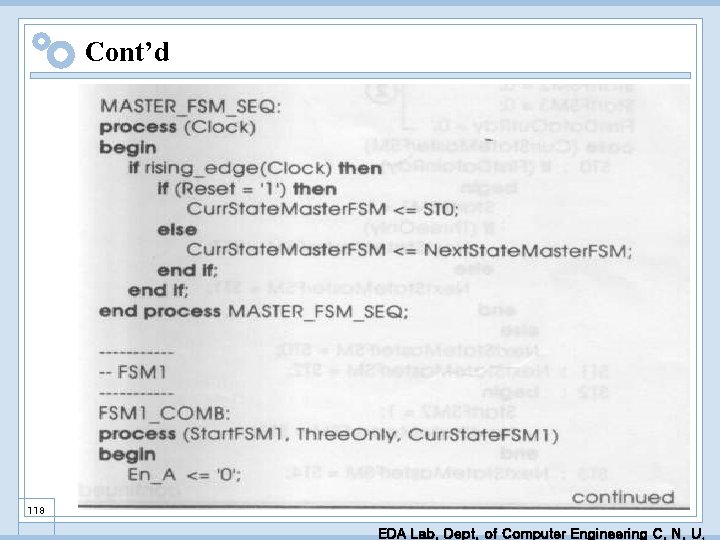

Cont’d 118 EDA Lab. Dept. of Computer Engineering C. N. U.

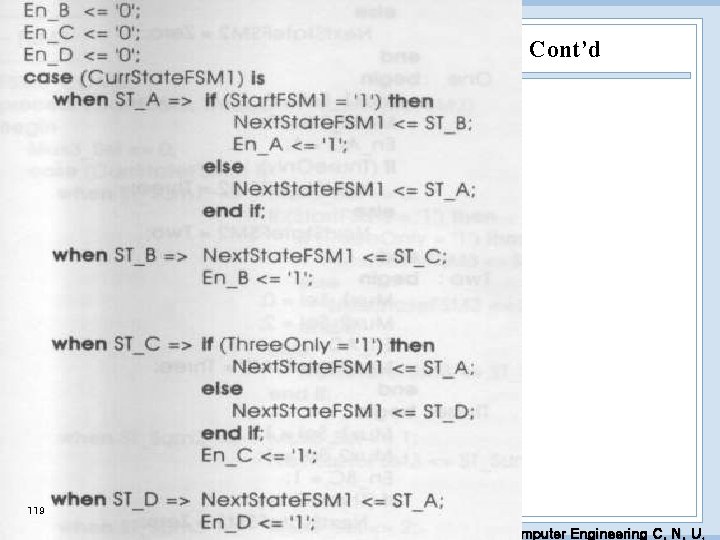

Cont’d 119 EDA Lab. Dept. of Computer Engineering C. N. U.

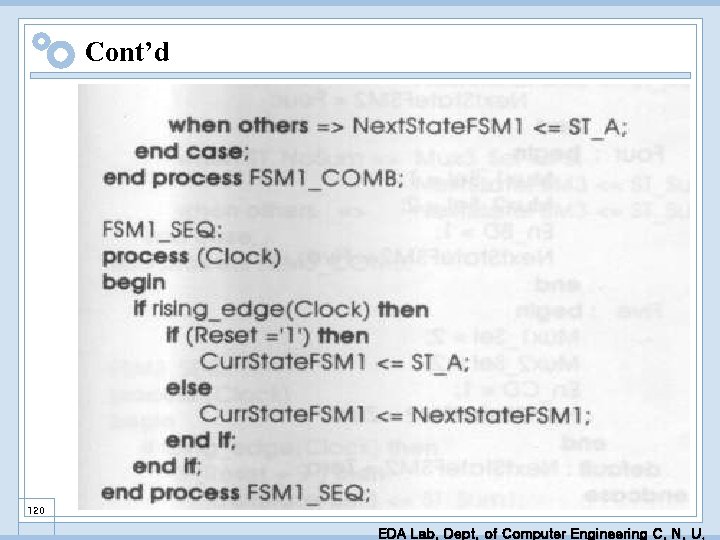

Cont’d 120 EDA Lab. Dept. of Computer Engineering C. N. U.

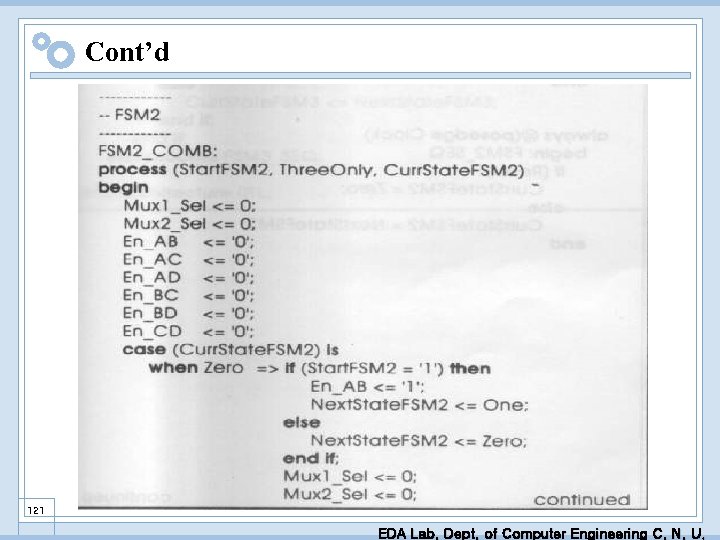

Cont’d 121 EDA Lab. Dept. of Computer Engineering C. N. U.

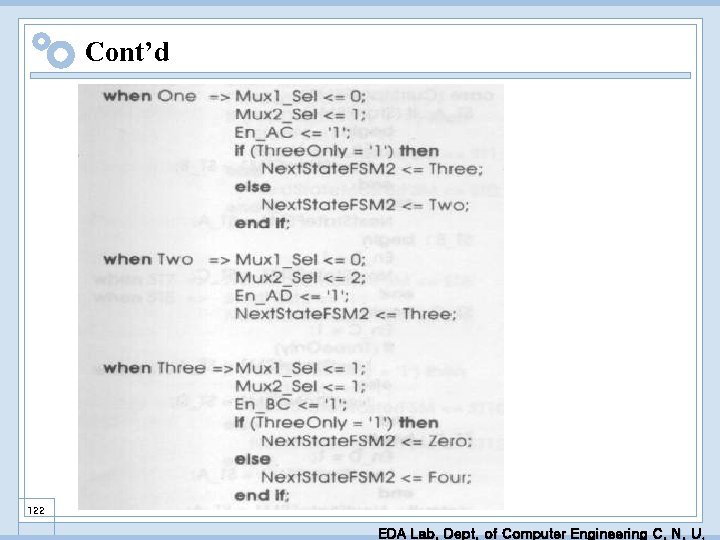

Cont’d 122 EDA Lab. Dept. of Computer Engineering C. N. U.

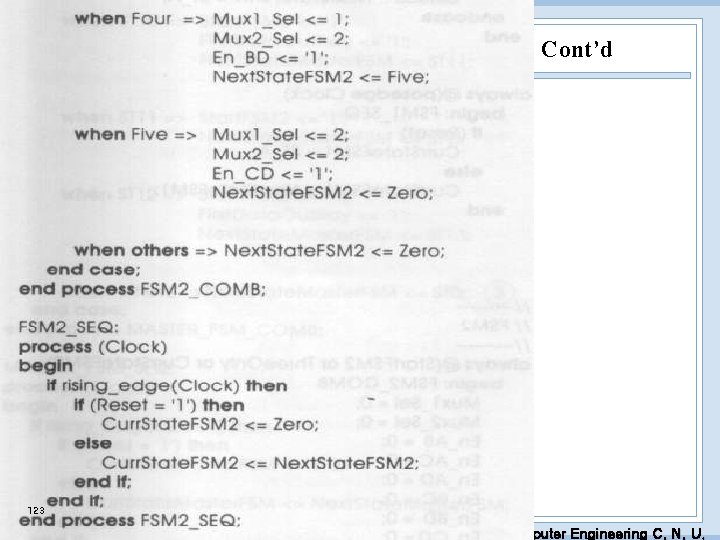

Cont’d 123 EDA Lab. Dept. of Computer Engineering C. N. U.

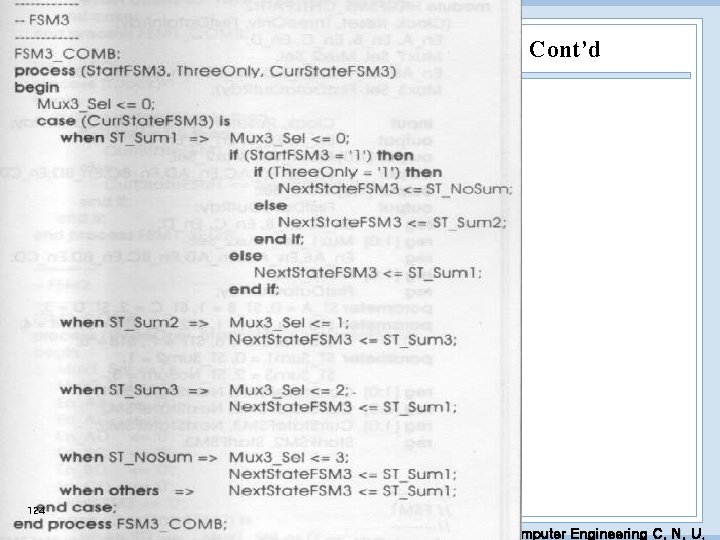

Cont’d 124 EDA Lab. Dept. of Computer Engineering C. N. U.

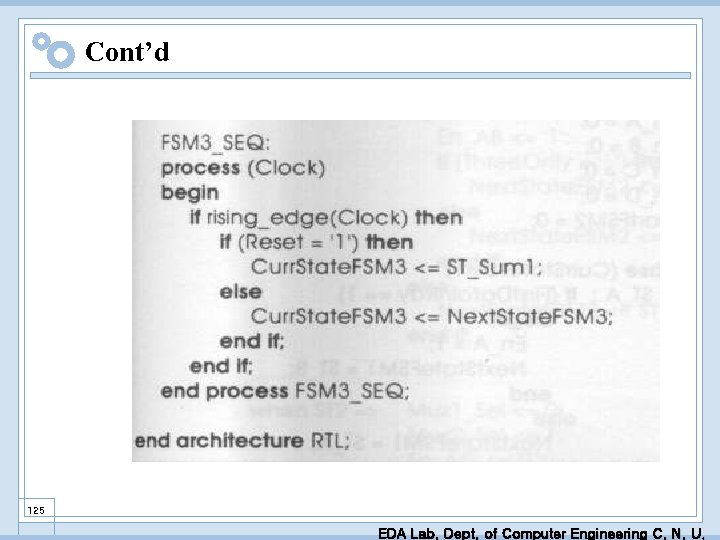

Cont’d 125 EDA Lab. Dept. of Computer Engineering C. N. U.

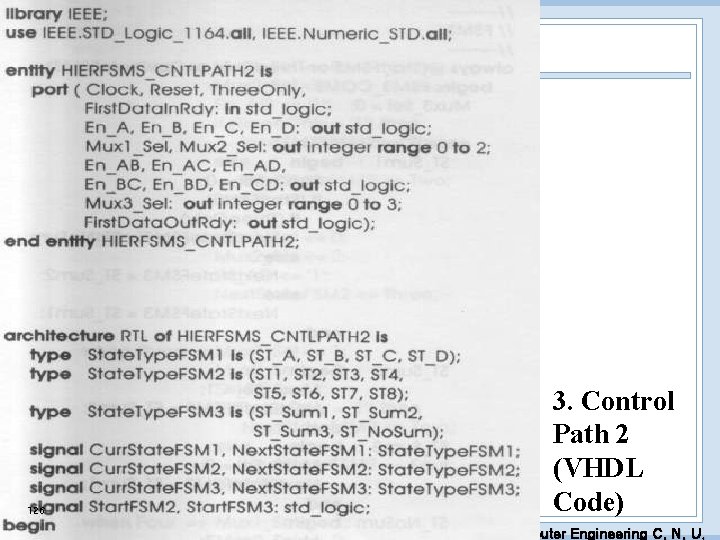

126 3. Control Path 2 (VHDL Code) EDA Lab. Dept. of Computer Engineering C. N. U.

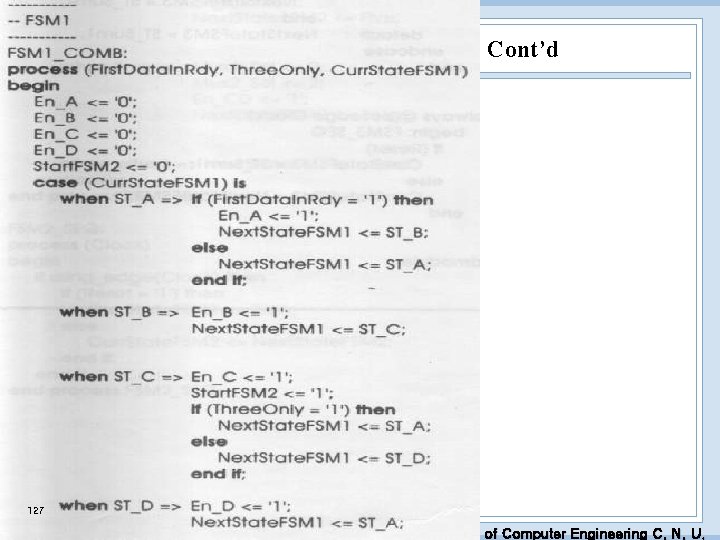

Cont’d 127 EDA Lab. Dept. of Computer Engineering C. N. U.

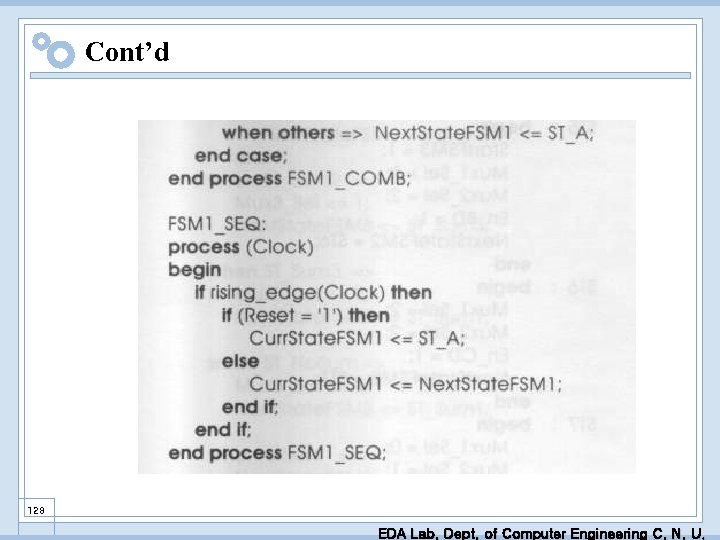

Cont’d 128 EDA Lab. Dept. of Computer Engineering C. N. U.

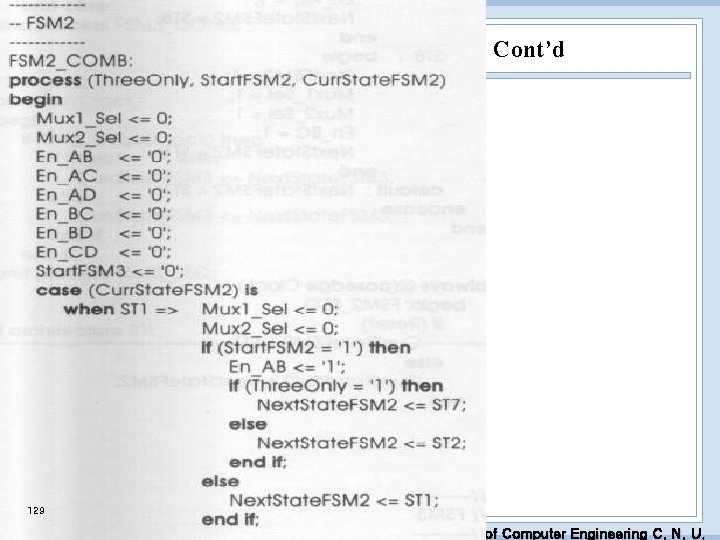

Cont’d 129 EDA Lab. Dept. of Computer Engineering C. N. U.

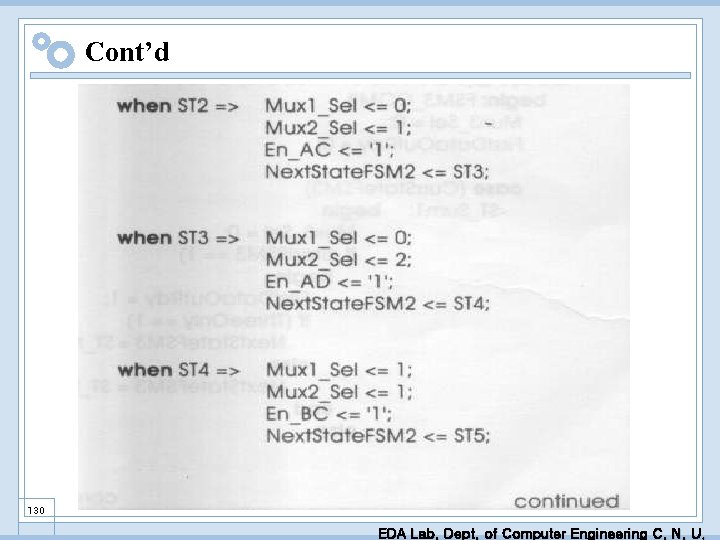

Cont’d 130 EDA Lab. Dept. of Computer Engineering C. N. U.

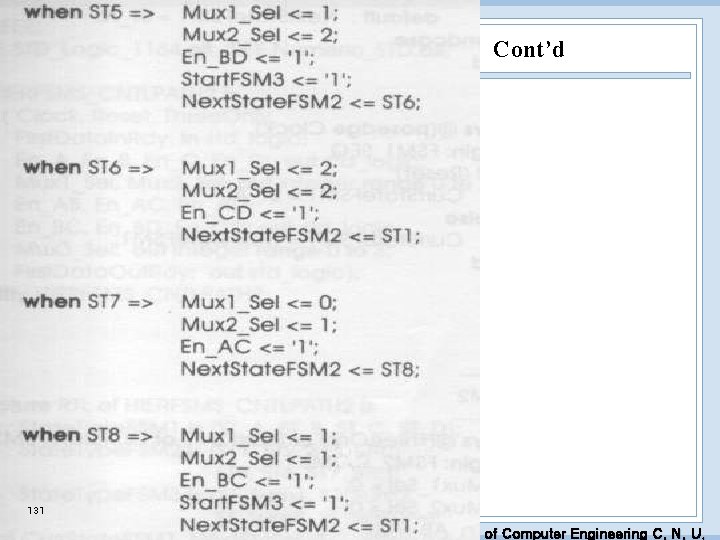

Cont’d 131 EDA Lab. Dept. of Computer Engineering C. N. U.

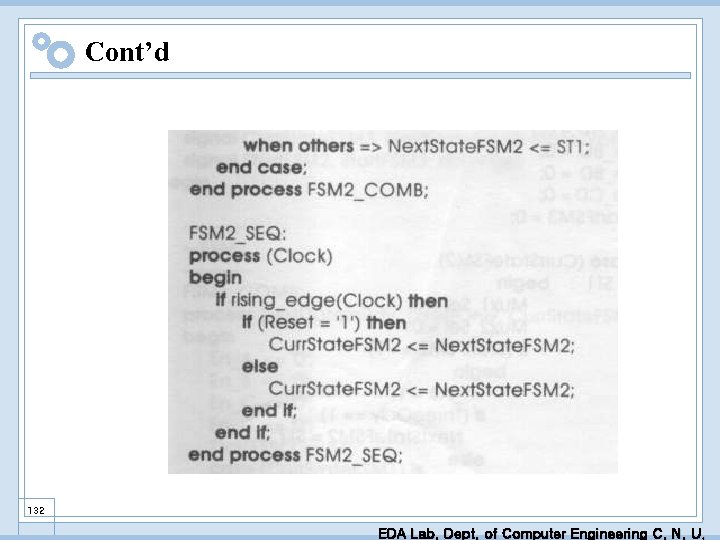

Cont’d 132 EDA Lab. Dept. of Computer Engineering C. N. U.

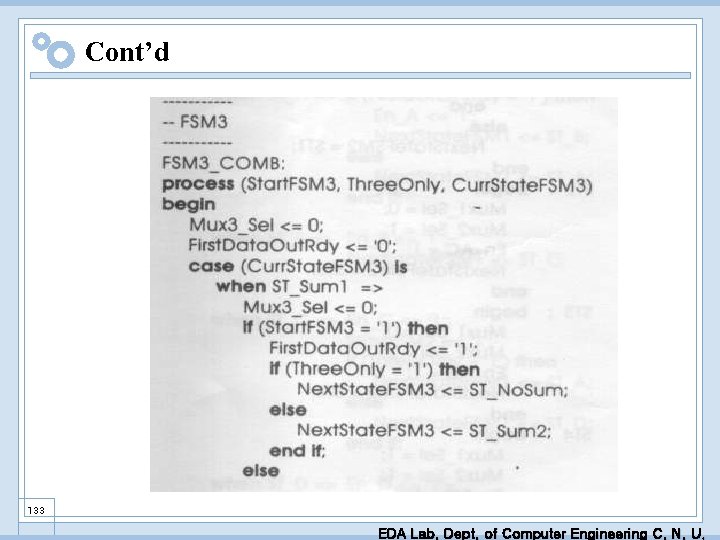

Cont’d 133 EDA Lab. Dept. of Computer Engineering C. N. U.

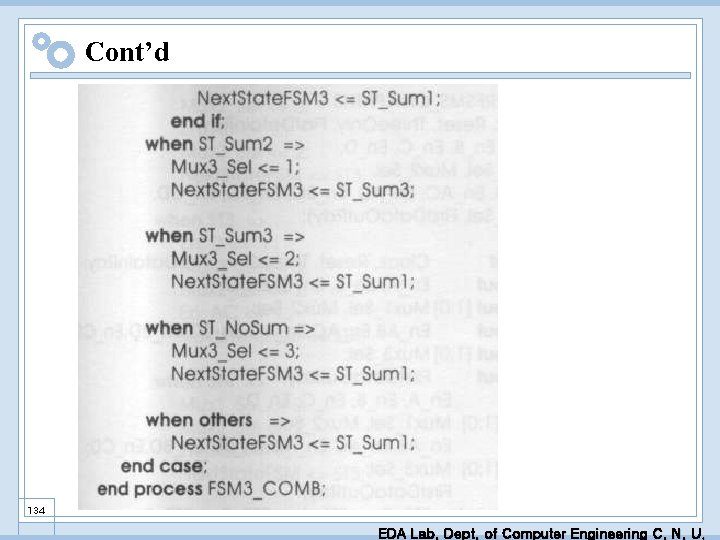

Cont’d 134 EDA Lab. Dept. of Computer Engineering C. N. U.

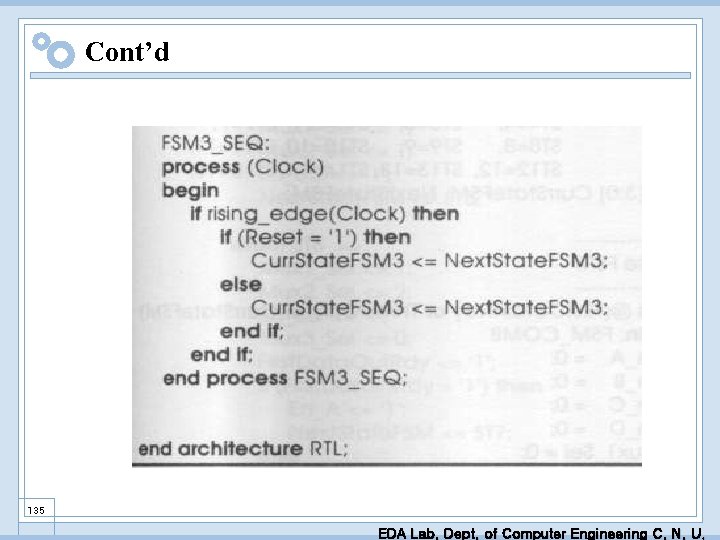

Cont’d 135 EDA Lab. Dept. of Computer Engineering C. N. U.

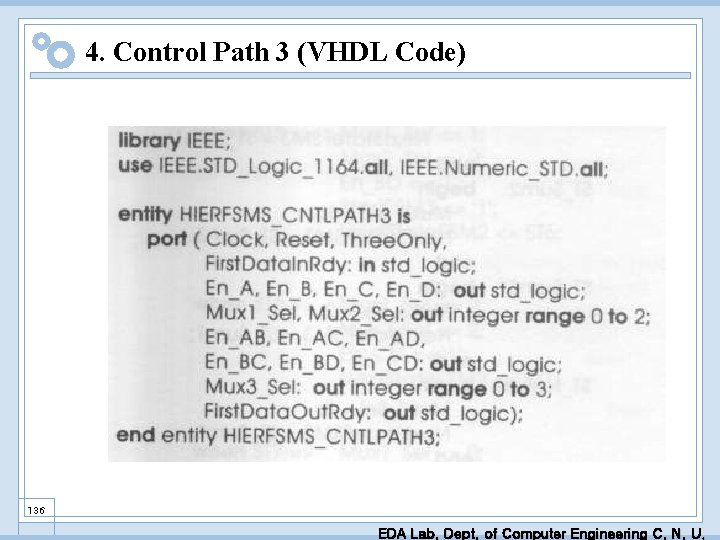

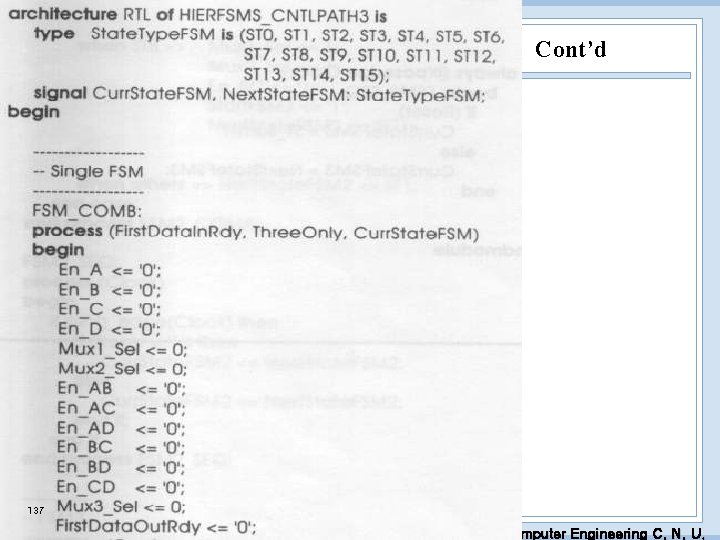

4. Control Path 3 (VHDL Code) 136 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d 137 EDA Lab. Dept. of Computer Engineering C. N. U.

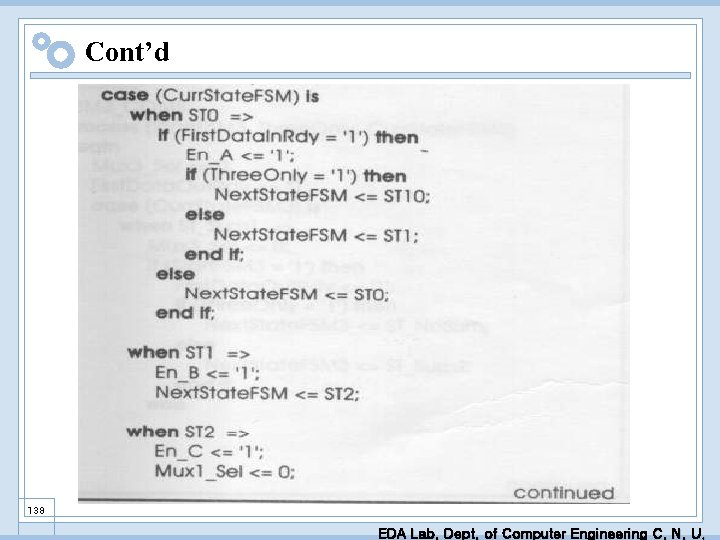

Cont’d 138 EDA Lab. Dept. of Computer Engineering C. N. U.

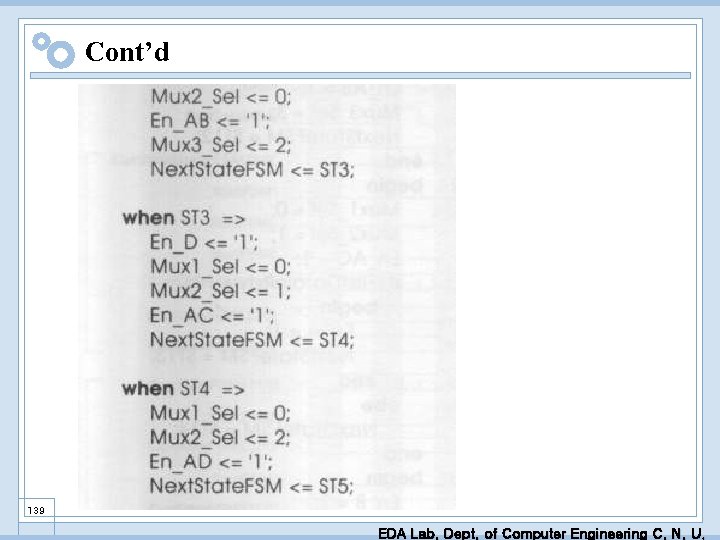

Cont’d 139 EDA Lab. Dept. of Computer Engineering C. N. U.

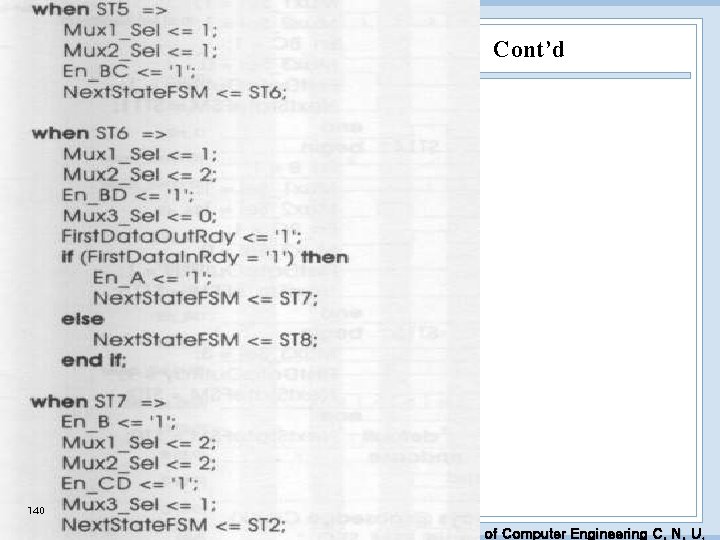

Cont’d 140 EDA Lab. Dept. of Computer Engineering C. N. U.

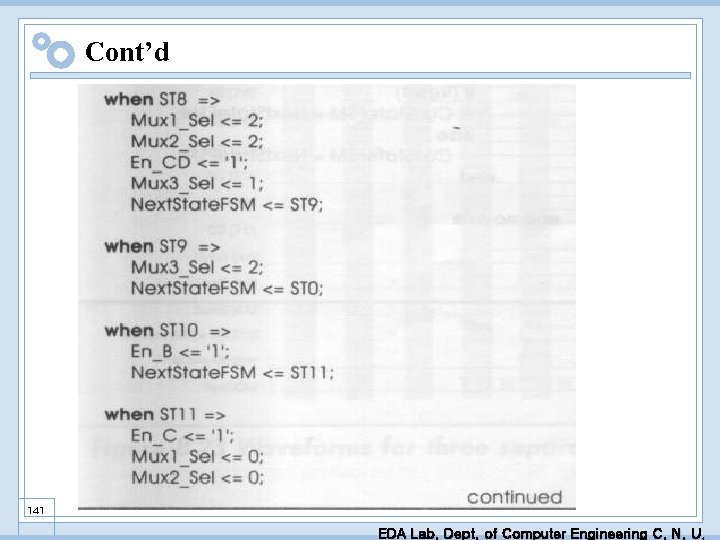

Cont’d 141 EDA Lab. Dept. of Computer Engineering C. N. U.

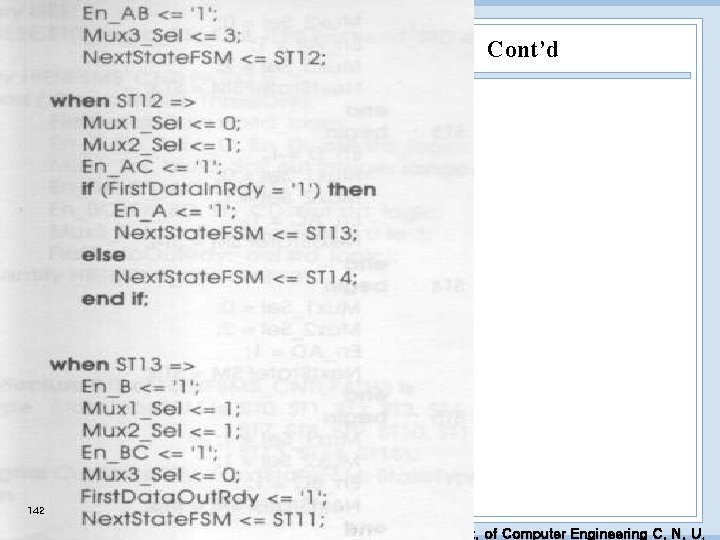

Cont’d 142 EDA Lab. Dept. of Computer Engineering C. N. U.

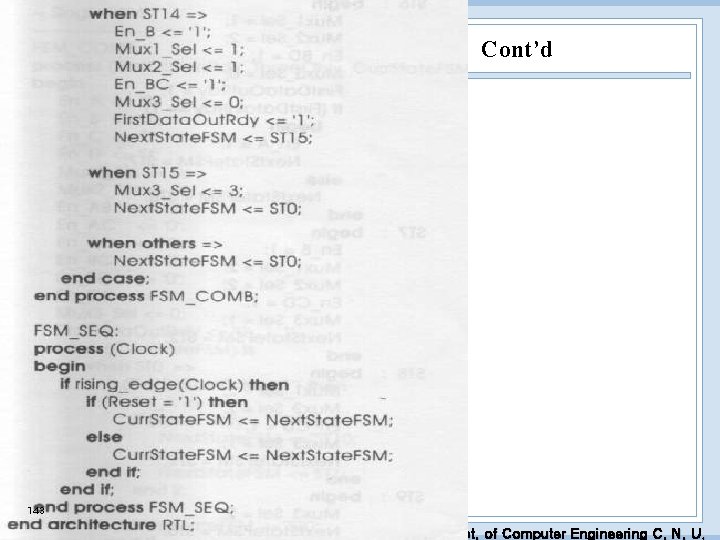

Cont’d 143 EDA Lab. Dept. of Computer Engineering C. N. U.

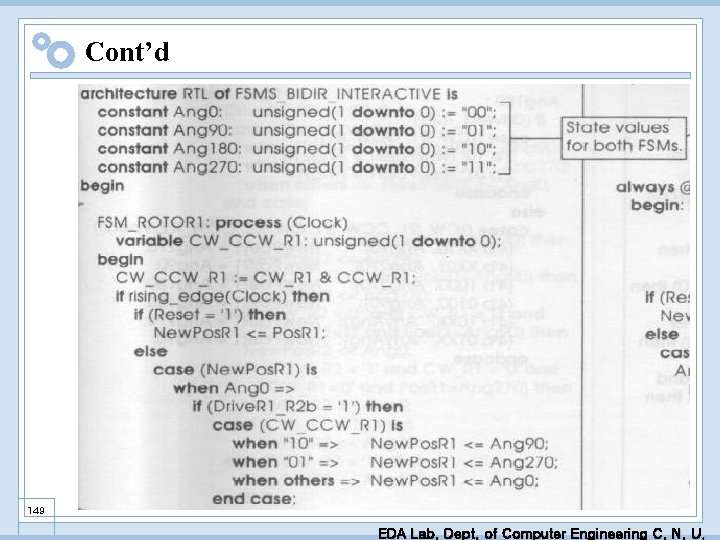

Two Interactive FSM Controlling rotors • Two Interactive FSM Controlling rotors – To control two mechanical interlocking rotors, which rotate in 90˚ increments in a clockwise or counter clockwise. 144 EDA Lab. Dept. of Computer Engineering C. N. U.

145 EDA Lab. Dept. of Computer Engineering C. N. U.

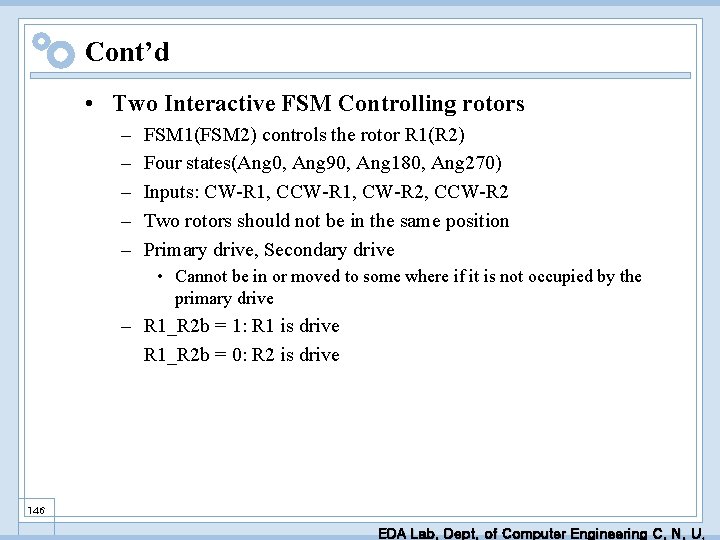

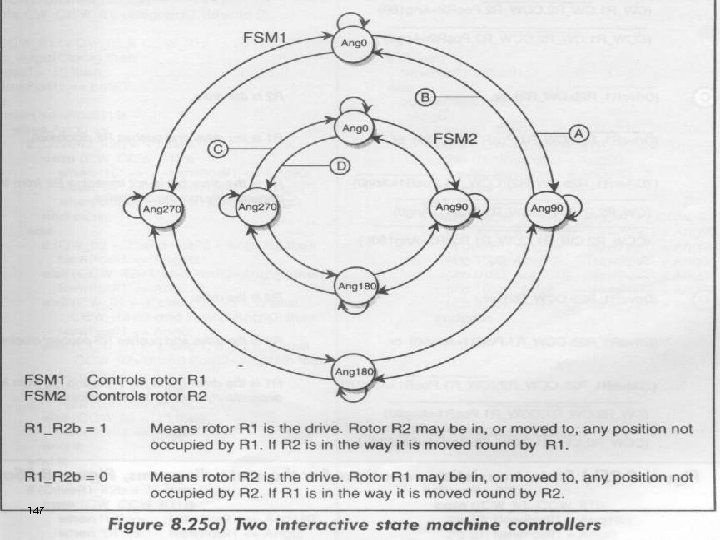

Cont’d • Two Interactive FSM Controlling rotors – – – FSM 1(FSM 2) controls the rotor R 1(R 2) Four states(Ang 0, Ang 90, Ang 180, Ang 270) Inputs: CW-R 1, CW-R 2, CCW-R 2 Two rotors should not be in the same position Primary drive, Secondary drive • Cannot be in or moved to some where if it is not occupied by the primary drive – R 1_R 2 b = 1: R 1 is drive R 1_R 2 b = 0: R 2 is drive 146 EDA Lab. Dept. of Computer Engineering C. N. U.

147 EDA Lab. Dept. of Computer Engineering C. N. U.

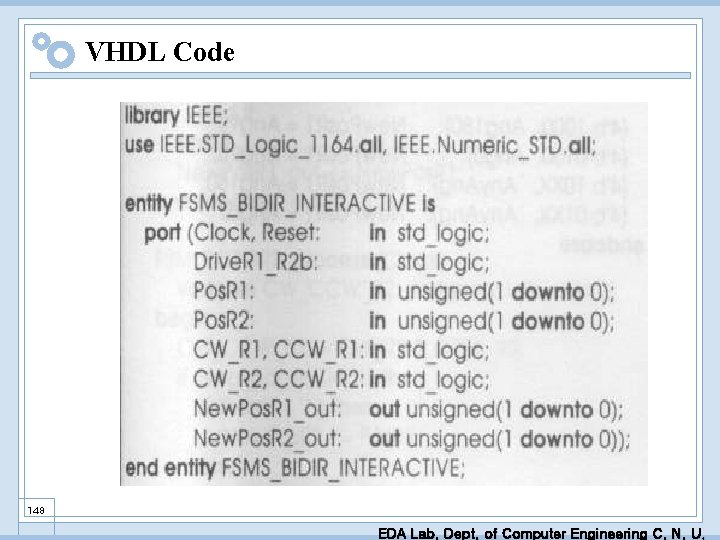

VHDL Code 148 EDA Lab. Dept. of Computer Engineering C. N. U.

Cont’d 149 EDA Lab. Dept. of Computer Engineering C. N. U.

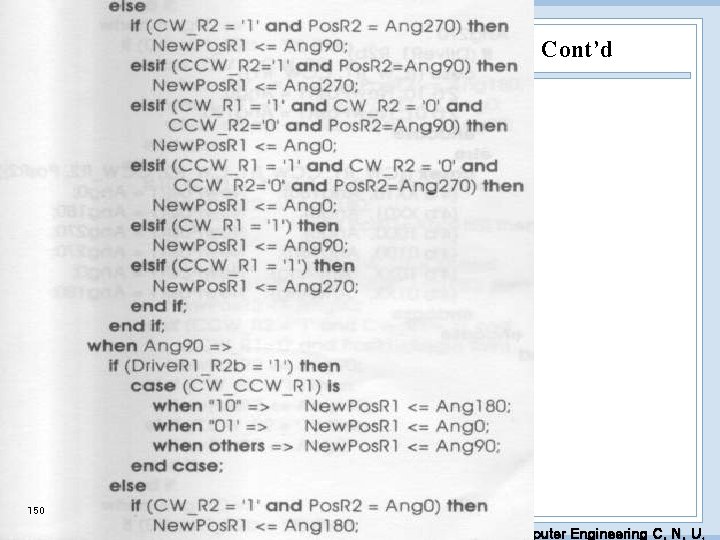

Cont’d 150 EDA Lab. Dept. of Computer Engineering C. N. U.

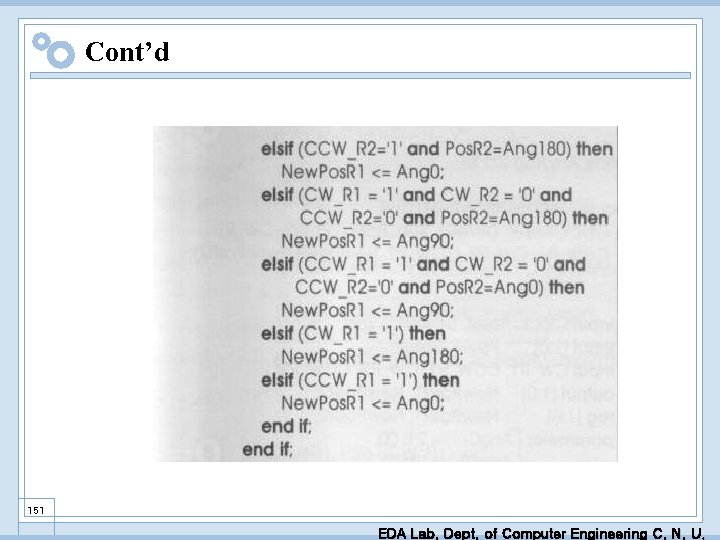

Cont’d 151 EDA Lab. Dept. of Computer Engineering C. N. U.

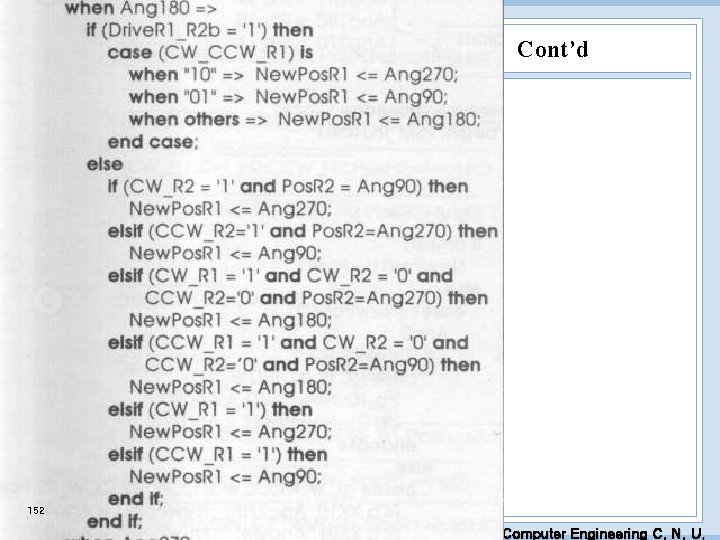

Cont’d 152 EDA Lab. Dept. of Computer Engineering C. N. U.

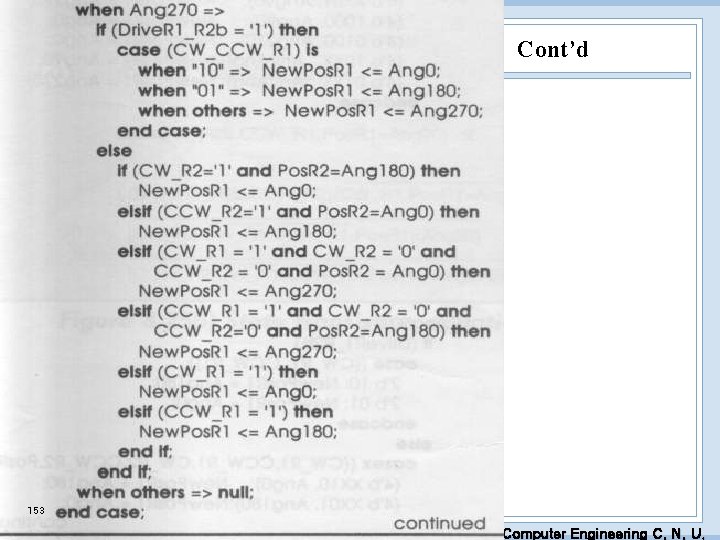

Cont’d 153 EDA Lab. Dept. of Computer Engineering C. N. U.

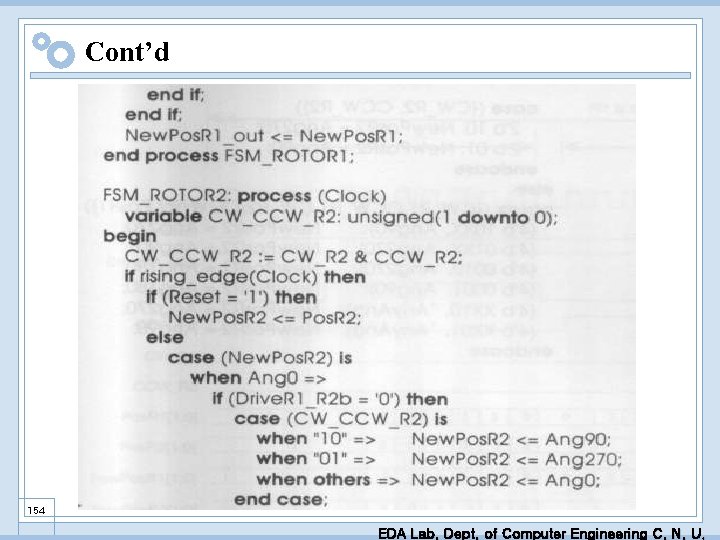

Cont’d 154 EDA Lab. Dept. of Computer Engineering C. N. U.

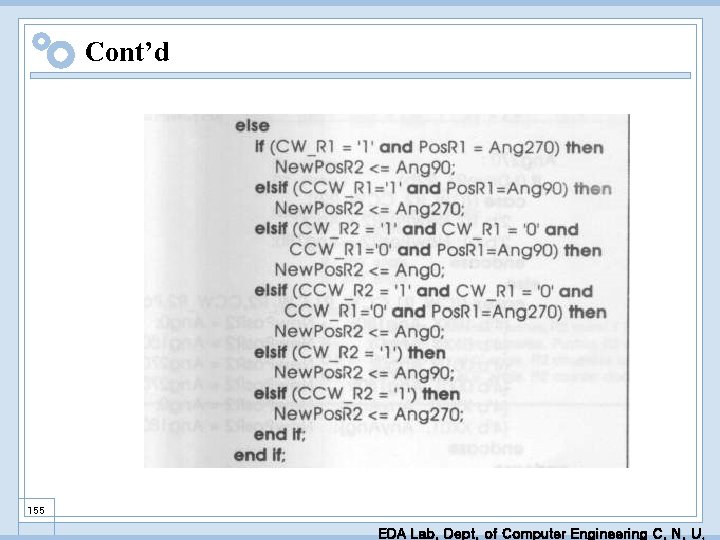

Cont’d 155 EDA Lab. Dept. of Computer Engineering C. N. U.

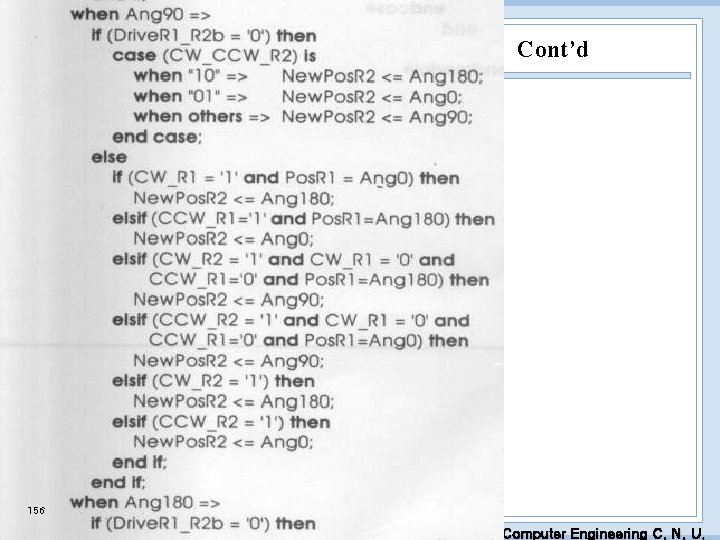

Cont’d 156 EDA Lab. Dept. of Computer Engineering C. N. U.

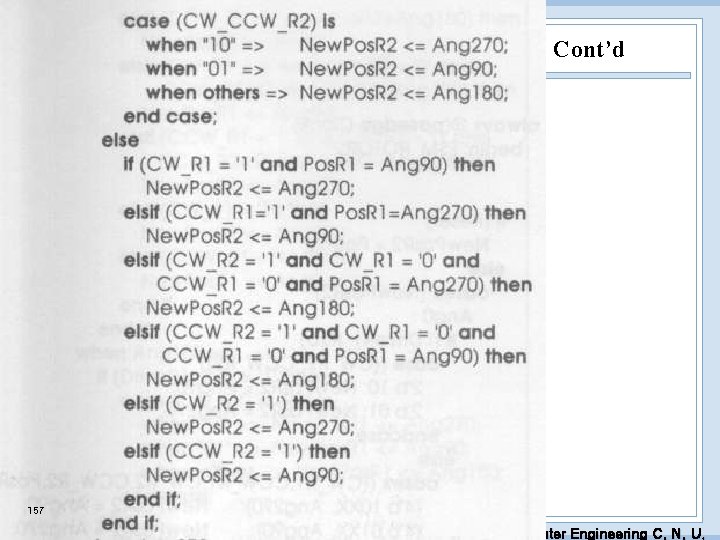

Cont’d 157 EDA Lab. Dept. of Computer Engineering C. N. U.

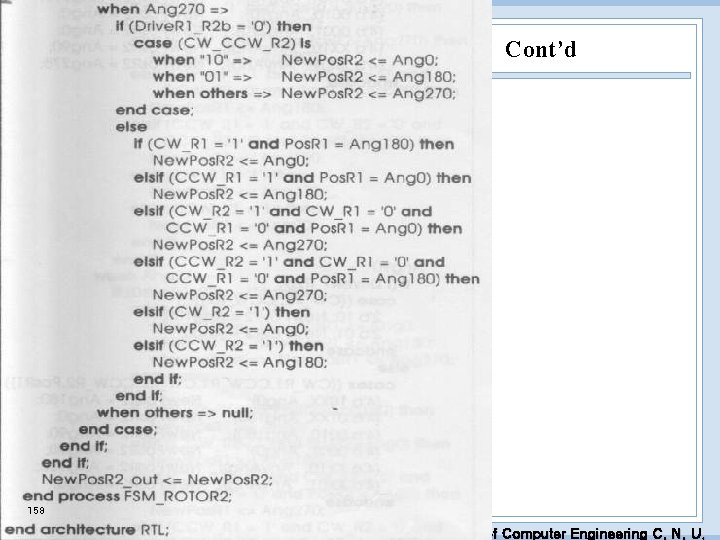

Cont’d 158 EDA Lab. Dept. of Computer Engineering C. N. U.

- Slides: 158