Front end Electronic Scott 0 KM 3 Ne

- Slides: 12

Front end Electronic Scott 0 KM 3 Ne. T WPs meeting in Paris, 23 -24 February Fabrice Guilloux on behalf Saclay’s group DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr 24/02/2009

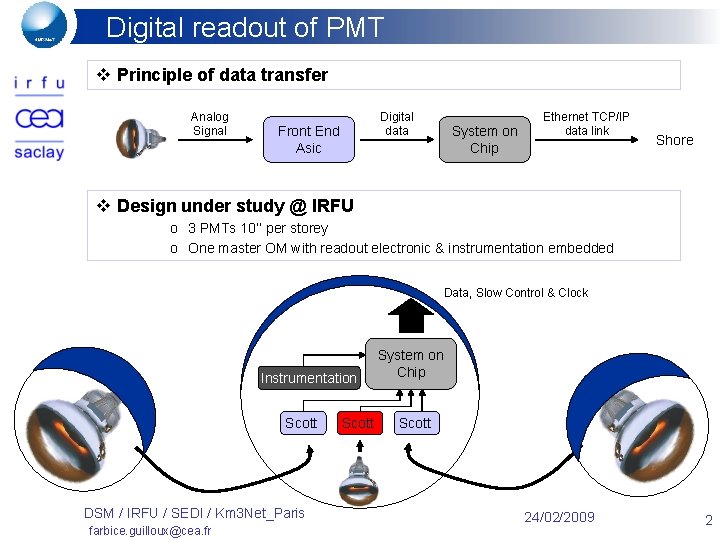

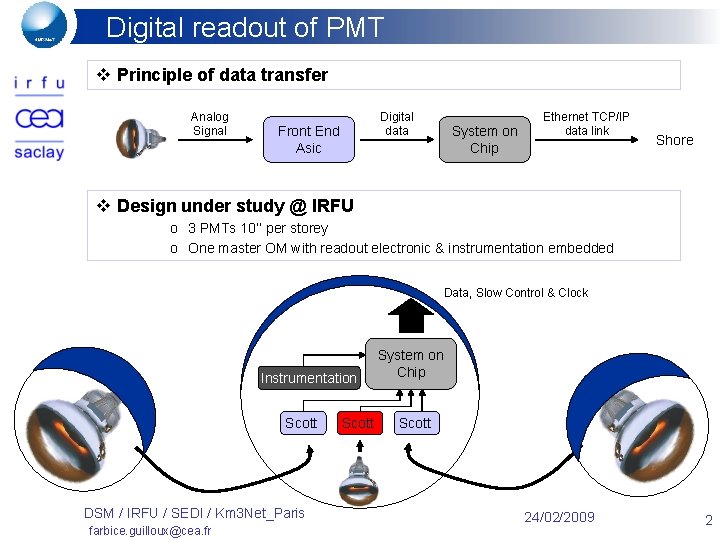

Digital readout of PMT v Principle of data transfer Analog Signal Digital data Front End Asic System on Chip Ethernet TCP/IP data link Shore v Design under study @ IRFU o 3 PMTs 10’’ per storey o One master OM with readout electronic & instrumentation embedded Data, Slow Control & Clock Instrumentation Scott DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr Scott System on Chip Scott 24/02/2009 2

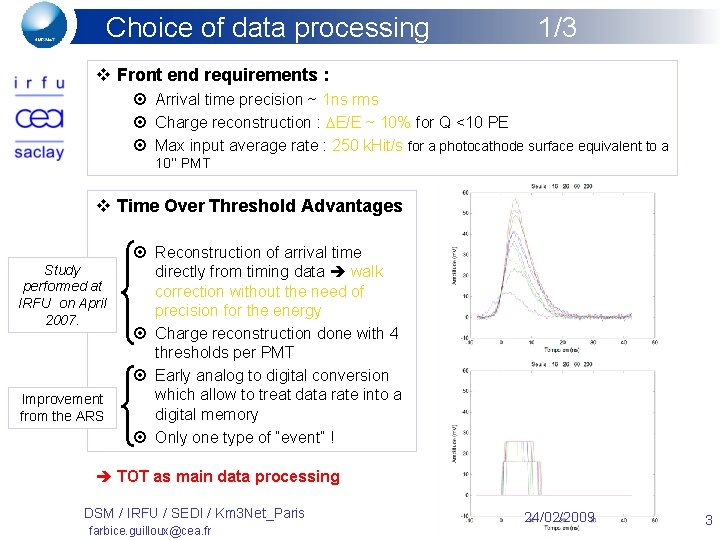

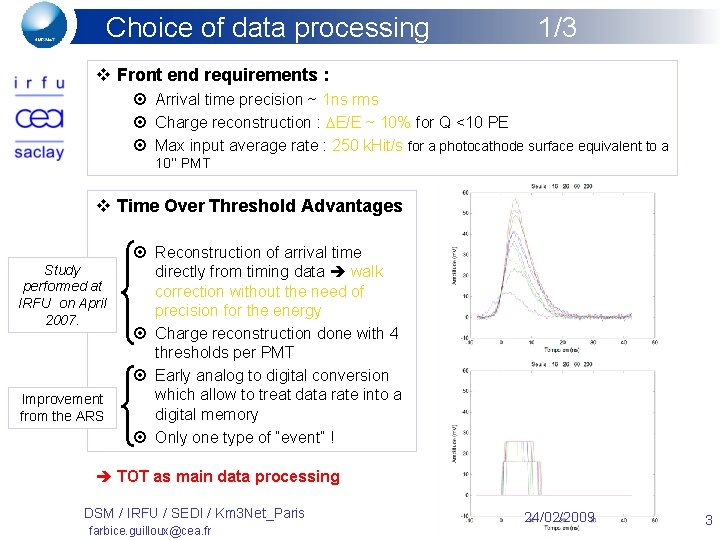

Choice of data processing 1/3 v Front end requirements : ¤ Arrival time precision ~ 1 ns rms ¤ Charge reconstruction : DE/E ~ 10% for Q <10 PE ¤ Max input average rate : 250 k. Hit/s for a photocathode surface equivalent to a 10’’ PMT v Time Over Threshold Advantages Study performed at IRFU on April 2007. Improvement from the ARS ¤ Reconstruction of arrival time directly from timing data walk correction without the need of precision for the energy ¤ Charge reconstruction done with 4 thresholds per PMT ¤ Early analog to digital conversion which allow to treat data rate into a digital memory ¤ Only one type of “event” ! TOT as main data processing DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr 24/02/2009 3

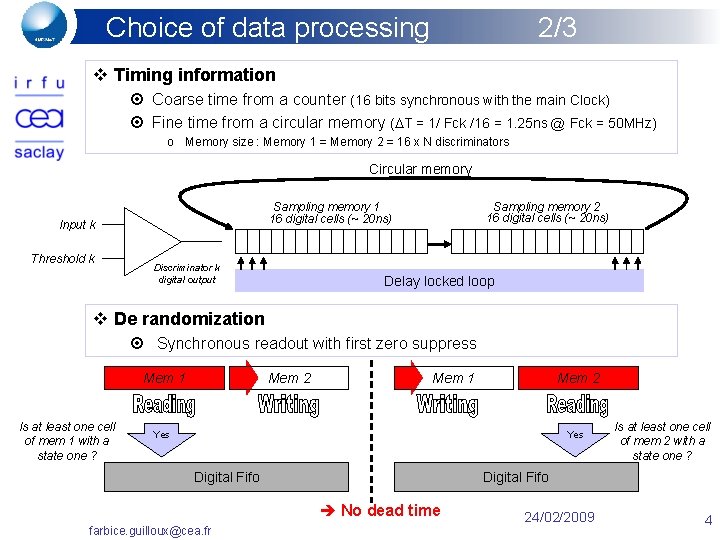

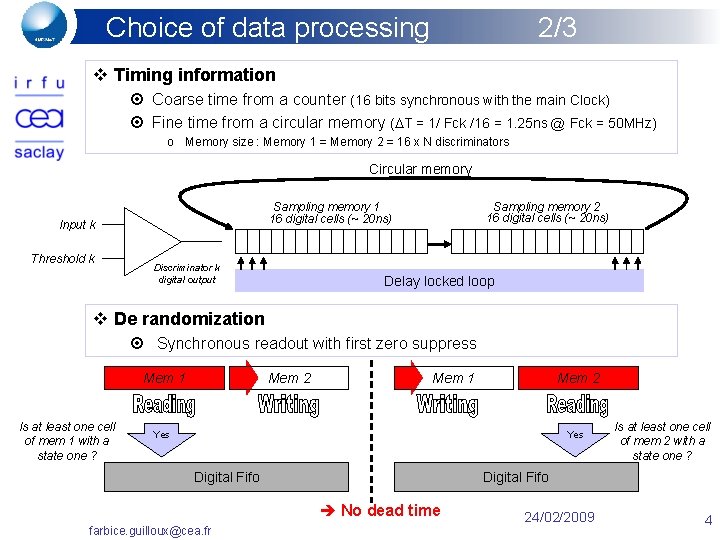

Choice of data processing 2/3 v Timing information ¤ Coarse time from a counter (16 bits synchronous with the main Clock) ¤ Fine time from a circular memory (DT = 1/ Fck /16 = 1. 25 ns @ Fck = 50 MHz) o Memory size : Memory 1 = Memory 2 = 16 x N discriminators Circular memory Sampling memory 1 16 digital cells (~ 20 ns) Input k Threshold k Discriminator k digital output Sampling memory 2 16 digital cells (~ 20 ns) Delay locked loop v De randomization ¤ Synchronous readout with first zero suppress Mem 1 Is at least one cell of mem 1 with a state one ? Mem 2 Mem 1 Mem 2 Yes Digital Fifo DSM / IRFU / SEDI / Km 3 Net_Paris No dead time farbice. guilloux@cea. fr Is at least one cell of mem 2 with a state one ? Digital Fifo 24/02/2009 4

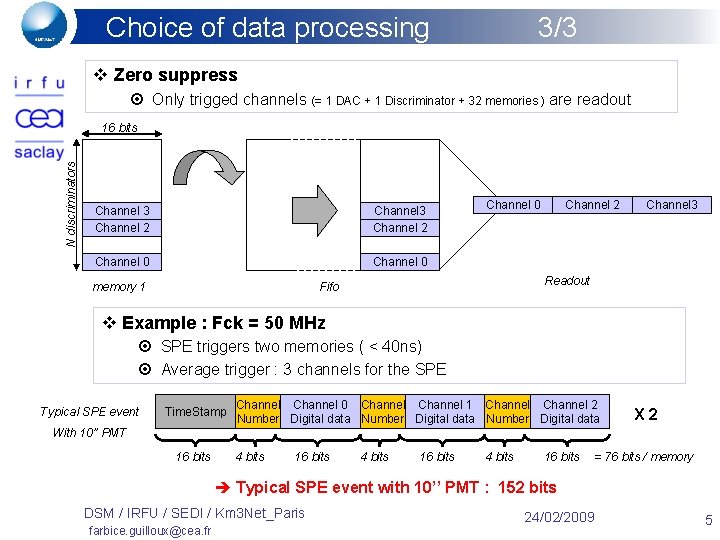

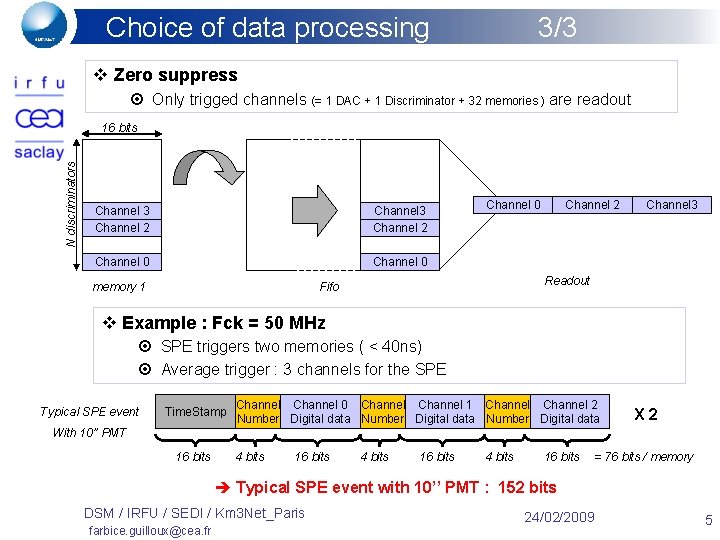

Choice of data processing 3/3 v Zero suppress ¤ Only trigged channels (= 1 DAC + 1 Discriminator + 32 memories ) are readout N discriminators 16 bits Channel 3 Channel 2 Channel 0 memory 1 Channel 0 Channel 2 Channel 3 Readout Fifo v Example : Fck = 50 MHz ¤ SPE triggers two memories ( < 40 ns) ¤ Average trigger : 3 channels for the SPE Typical SPE event Time. Stamp Channel 0 Channel 1 Channel 2 Number Digital data X 2 With 10’’ PMT 16 bits 4 bits 16 bits = 76 bits / memory Typical SPE event with 10’’ PMT : 152 bits DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr 24/02/2009 5

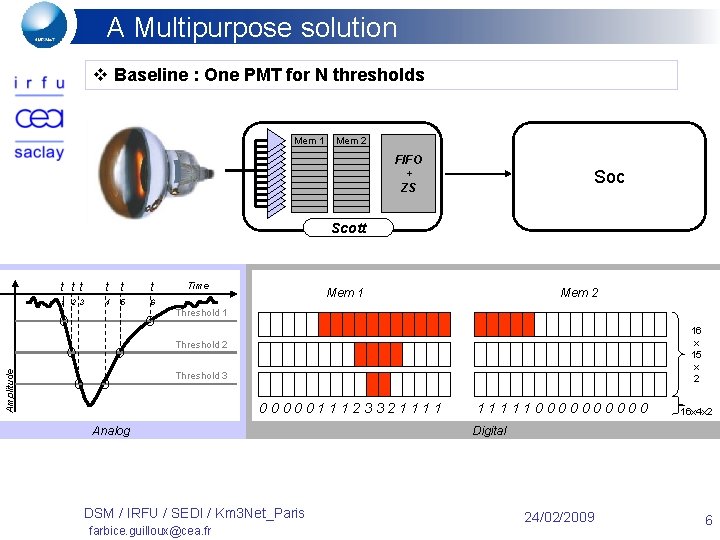

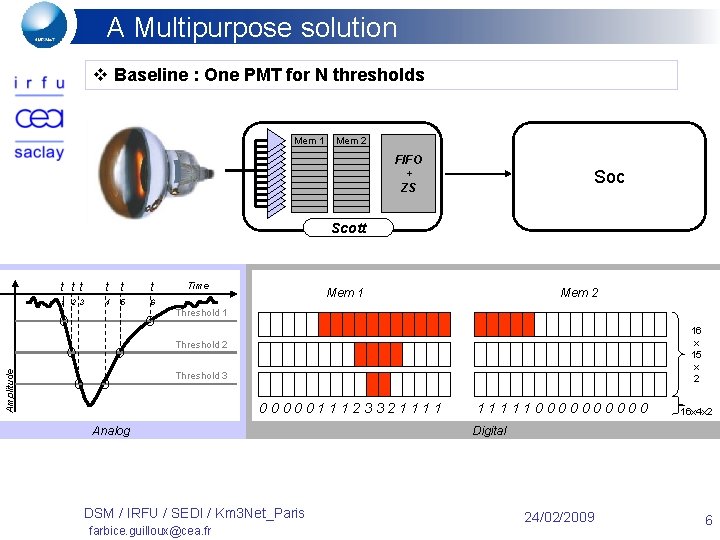

A Multipurpose solution v Baseline : One PMT for N thresholds Mem 1 Mem 2 FIFO + ZS Soc Scott t t t 1 23 4 6 5 Time Mem 1 Mem 2 Threshold 1 16 x 15 x 2 Amplitude Threshold 2 Threshold 3 0000011123321111 Analog DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr 1111100000 16 x 4 x 2 Digital 24/02/2009 6

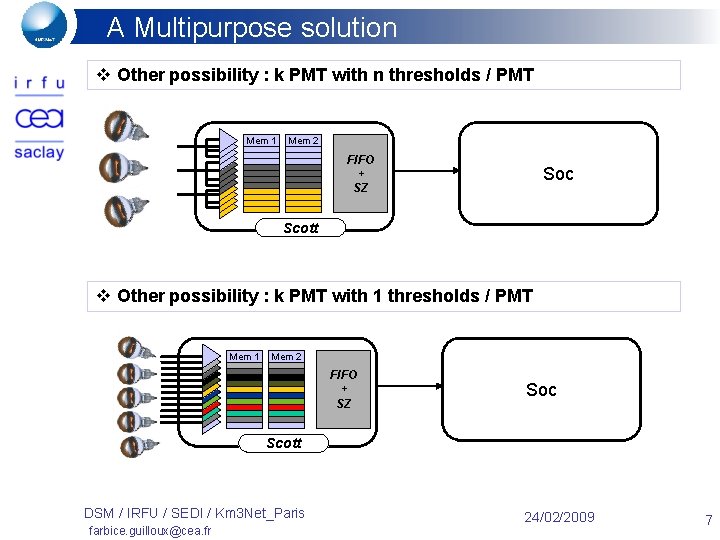

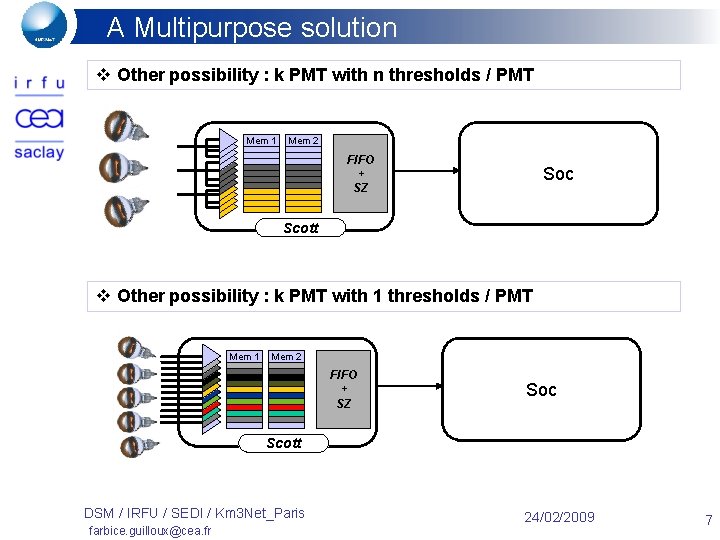

A Multipurpose solution v Other possibility : k PMT with n thresholds / PMT Mem 1 Mem 2 FIFO + SZ Soc Scott v Other possibility : k PMT with 1 thresholds / PMT Mem 1 Mem 2 FIFO + SZ Soc Scott DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr 24/02/2009 7

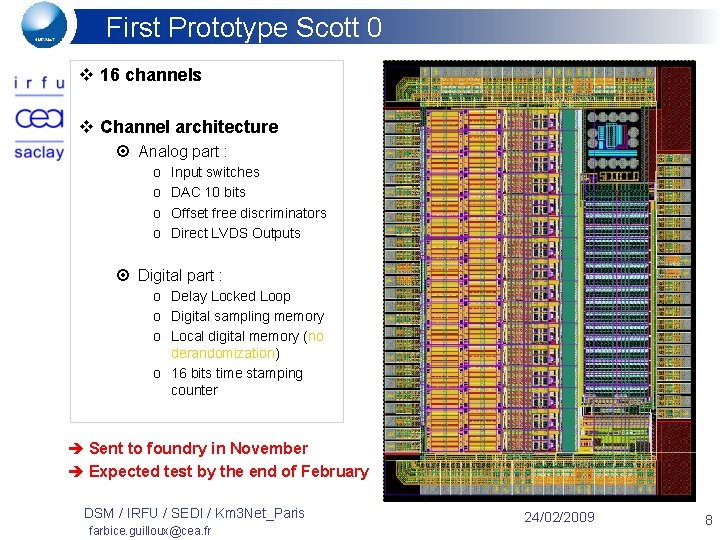

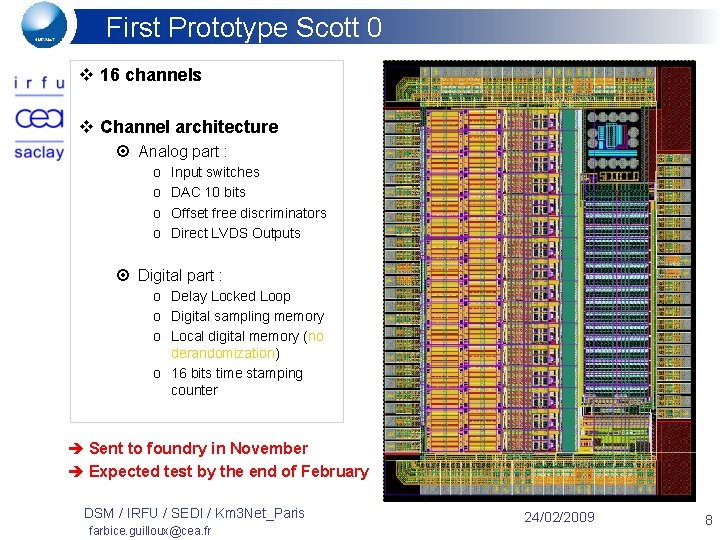

First Prototype Scott 0 v 16 channels v Channel architecture ¤ Analog part : o o Input switches DAC 10 bits Offset free discriminators Direct LVDS Outputs ¤ Digital part : o Delay Locked Loop o Digital sampling memory o Local digital memory (no derandomization) o 16 bits time stamping counter Sent to foundry in November Expected test by the end of February DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr 24/02/2009 8

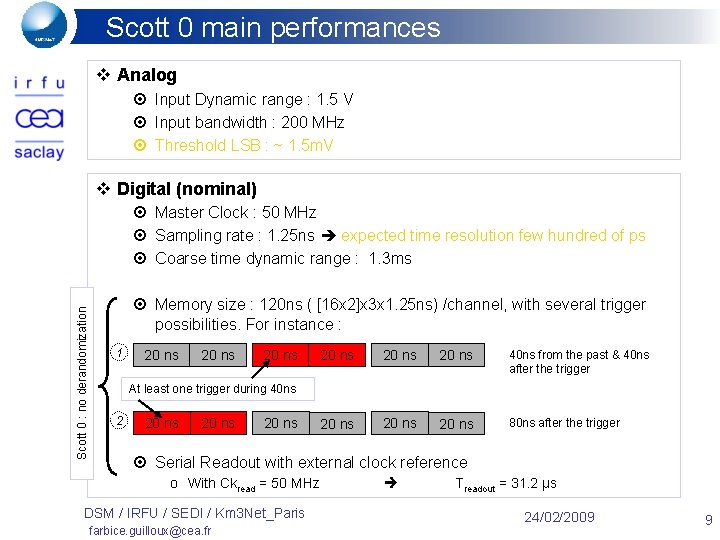

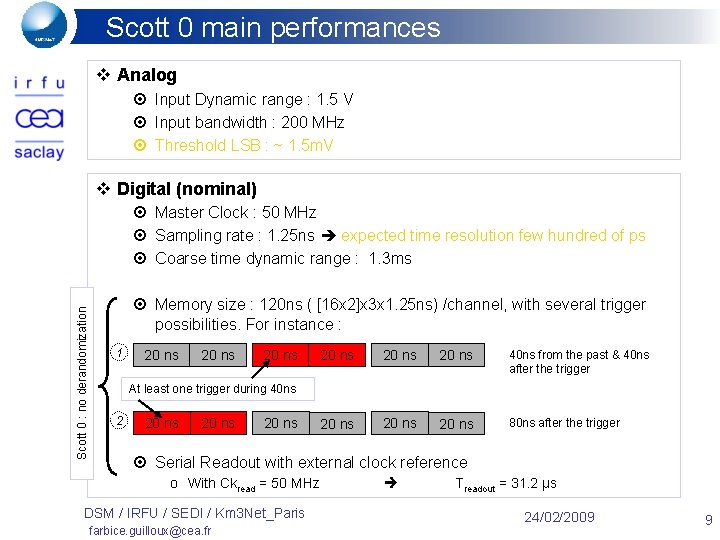

Scott 0 main performances v Analog ¤ Input Dynamic range : 1. 5 V ¤ Input bandwidth : 200 MHz ¤ Threshold LSB : ~ 1. 5 m. V v Digital (nominal) Scott 0 : no derandomization ¤ Master Clock : 50 MHz ¤ Sampling rate : 1. 25 ns expected time resolution few hundred of ps ¤ Coarse time dynamic range : 1. 3 ms ¤ Memory size : 120 ns ( [16 x 2]x 3 x 1. 25 ns) /channel, with several trigger possibilities. For instance : 1 20 ns 20 ns 40 ns from the past & 40 ns after the trigger 20 ns 80 ns after the trigger At least one trigger during 40 ns 2 20 ns ¤ Serial Readout with external clock reference o With Ckread = 50 MHz DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr Treadout = 31. 2 µs 24/02/2009 9

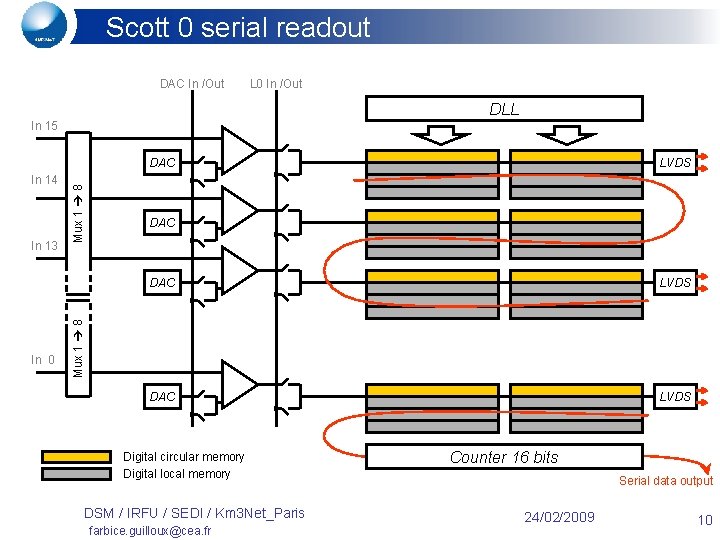

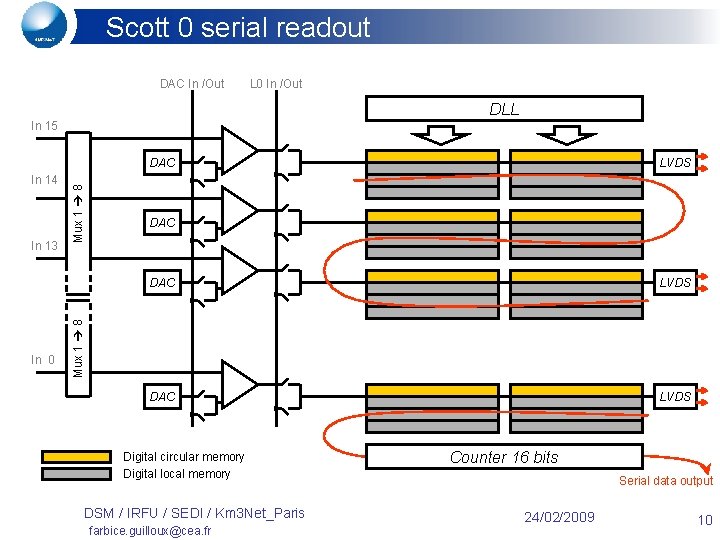

Scott 0 serial readout DAC In /Out L 0 In /Out DLL In 15 In 13 In 0 LVDS DAC LVDS Mux 1 8 In 14 Mux 1 8 DAC Digital circular memory Digital local memory DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr Counter 16 bits Serial data output 24/02/2009 10

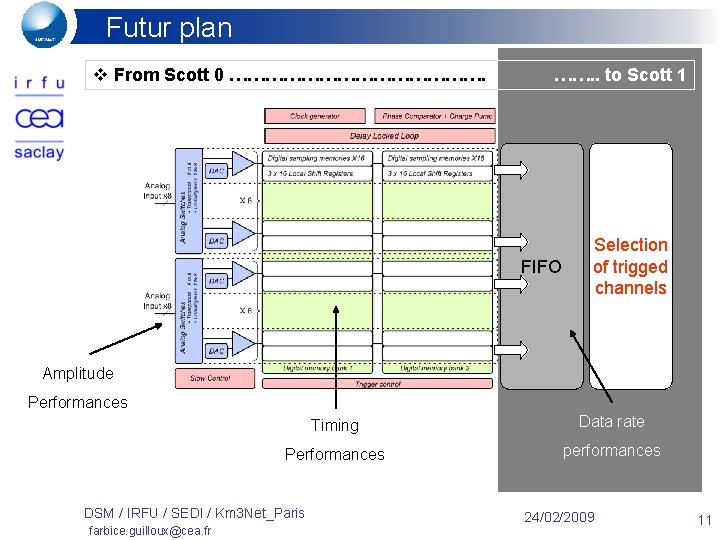

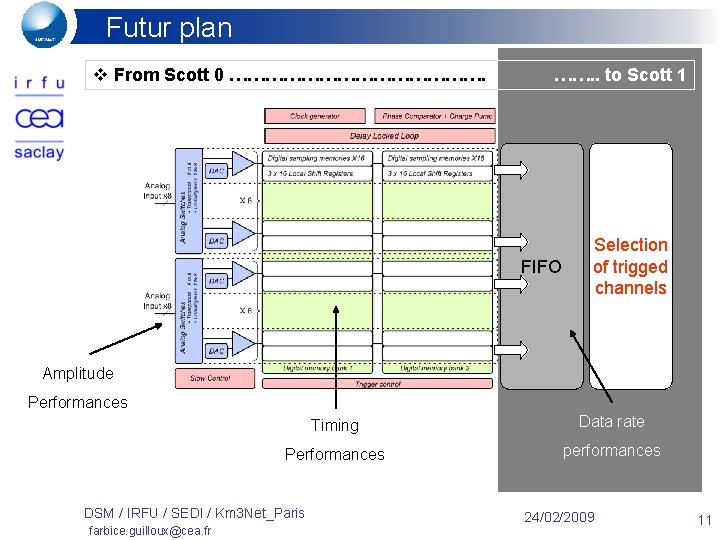

Futur plan v From Scott 0 …………………. . to Scott 1 FIFO Selection of trigged channels Amplitude Performances Timing Data rate Performances performances DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr 24/02/2009 11

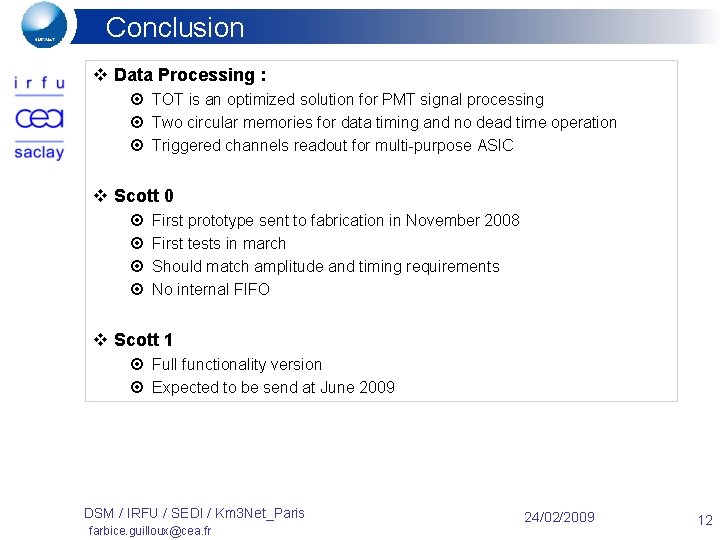

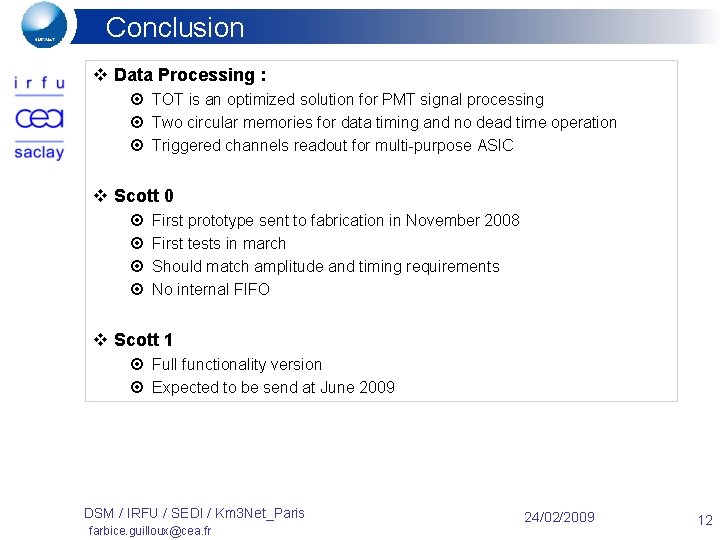

Conclusion v Data Processing : ¤ TOT is an optimized solution for PMT signal processing ¤ Two circular memories for data timing and no dead time operation ¤ Triggered channels readout for multi-purpose ASIC v Scott 0 ¤ ¤ First prototype sent to fabrication in November 2008 First tests in march Should match amplitude and timing requirements No internal FIFO v Scott 1 ¤ Full functionality version ¤ Expected to be send at June 2009 DSM / IRFU / SEDI / Km 3 Net_Paris farbice. guilloux@cea. fr 24/02/2009 12