From Algorithms to SystemsonaChip in a Semester E

![RAKE Receiver Student: Tufan Karalar I 8 Q S[n] Z-1 S[n-1] S[n-2] 1 st RAKE Receiver Student: Tufan Karalar I 8 Q S[n] Z-1 S[n-1] S[n-2] 1 st](https://slidetodoc.com/presentation_image_h2/b7cfd0361c4d3af0c0c3570f5b9294b6/image-10.jpg)

- Slides: 24

From Algorithms to Systems-on-a-Chip in a Semester E 225 C - 2000 Borivoje Nikolić

Fall 2000 - EE 225 C • Course topics: – Communication systems oriented – Building blocks • Datapaths, arithmetic (adders, multipliers, MACs, dividers, CORDICs) • Parallelization, pipelining, unrolling, etc. • Transformations: FIR filters, Viterbi decoders – Systems • Finite wordlengths, ADCs, AGC, adaptive equalizers, sequence detection • Applied to x. DSL, Gigabit ethernet, wireless, disk drives

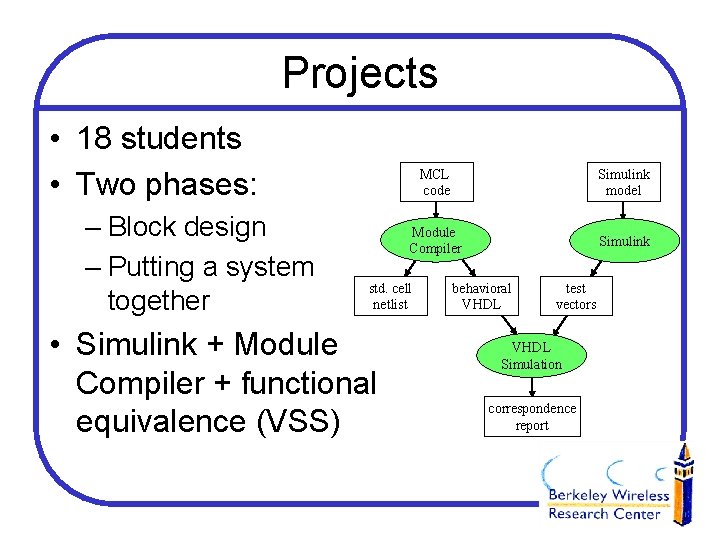

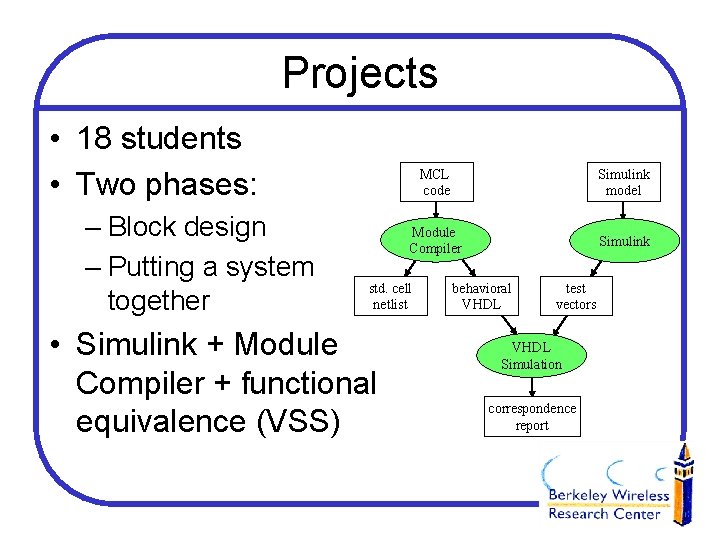

Projects • 18 students • Two phases: – Block design – Putting a system together MCL code Simulink model Module Compiler Simulink std. cell netlist • Simulink + Module Compiler + functional equivalence (VSS) behavioral VHDL test vectors VHDL Simulation correspondence report

Design Projects – Timing recovery for CDMA – OFDM receiver with multi-antenna support – 3 G Turbo decoder – LDPC iterative decoder – Polyphase filter bank – RAKE receiver – Adaptive image-reject mixer – Decoder for maskless lithography

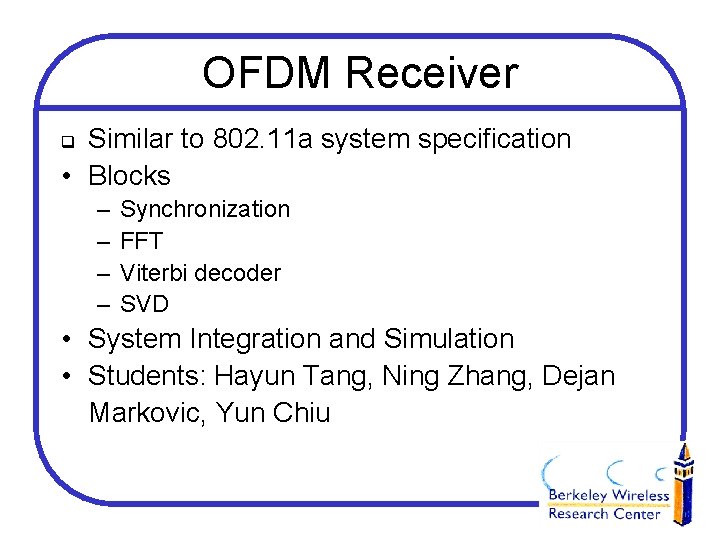

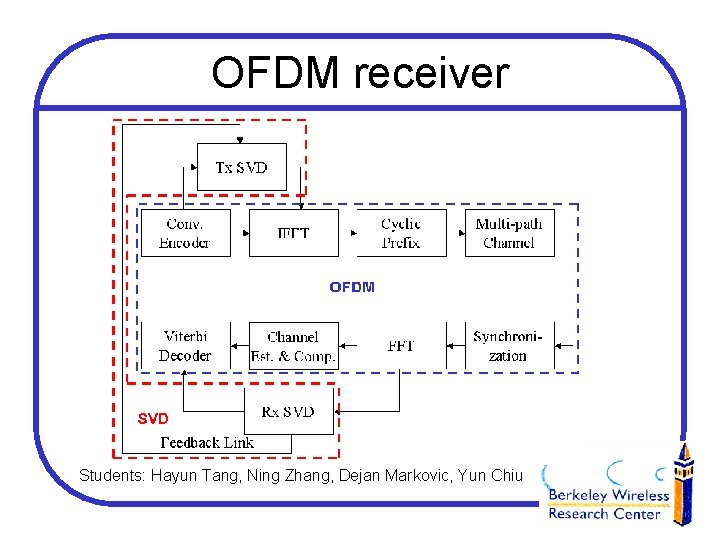

OFDM Receiver Similar to 802. 11 a system specification • Blocks q – – Synchronization FFT Viterbi decoder SVD • System Integration and Simulation • Students: Hayun Tang, Ning Zhang, Dejan Markovic, Yun Chiu

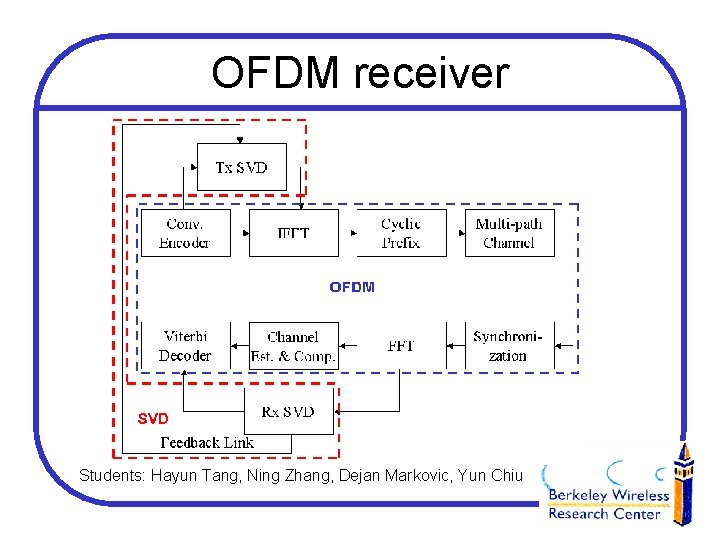

OFDM receiver Students: Hayun Tang, Ning Zhang, Dejan Markovic, Yun Chiu

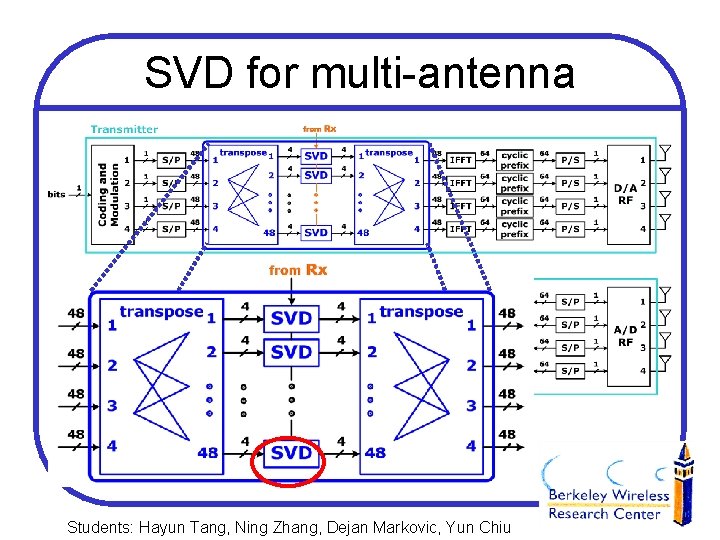

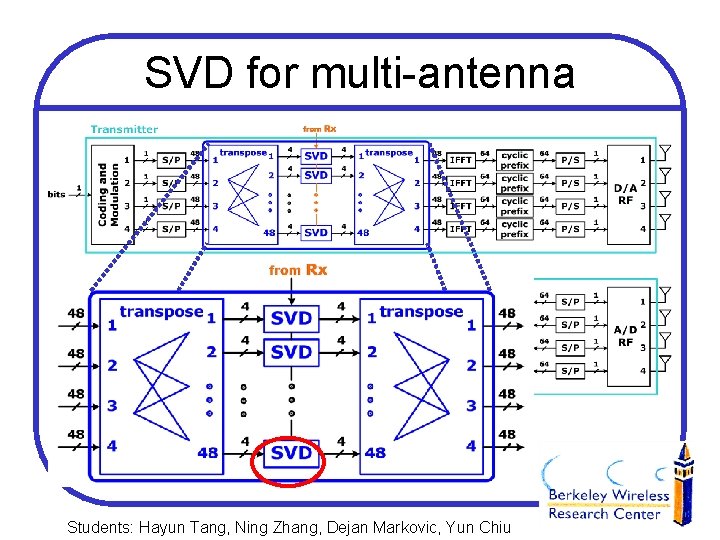

SVD for multi-antenna Students: Hayun Tang, Ning Zhang, Dejan Markovic, Yun Chiu

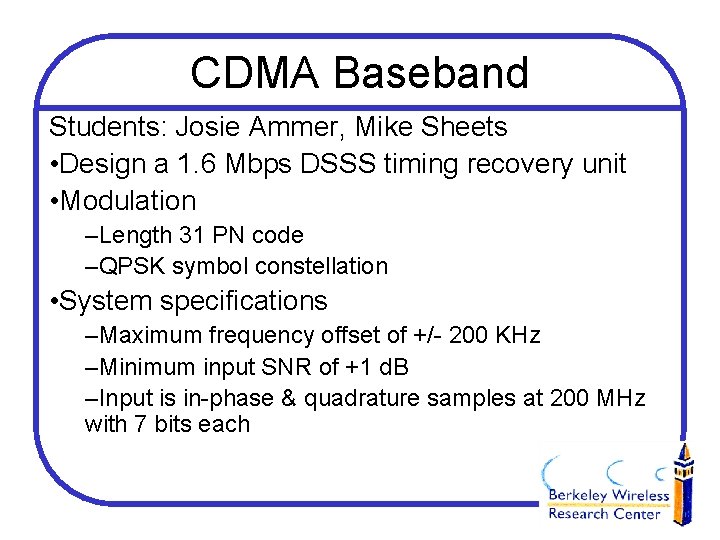

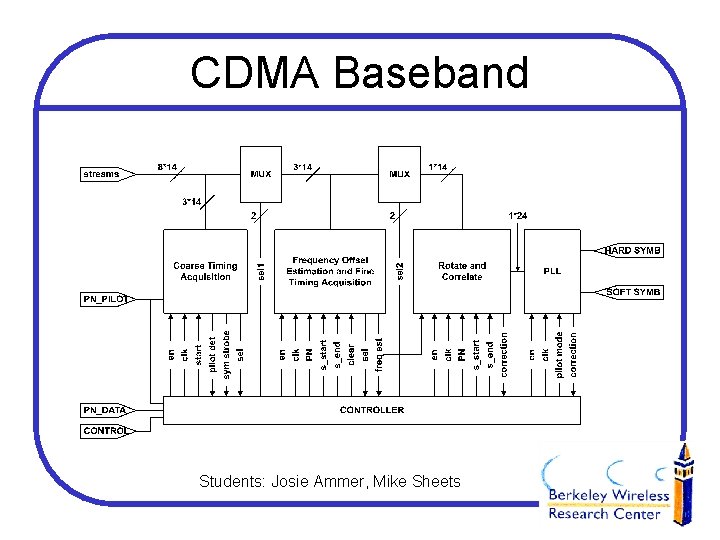

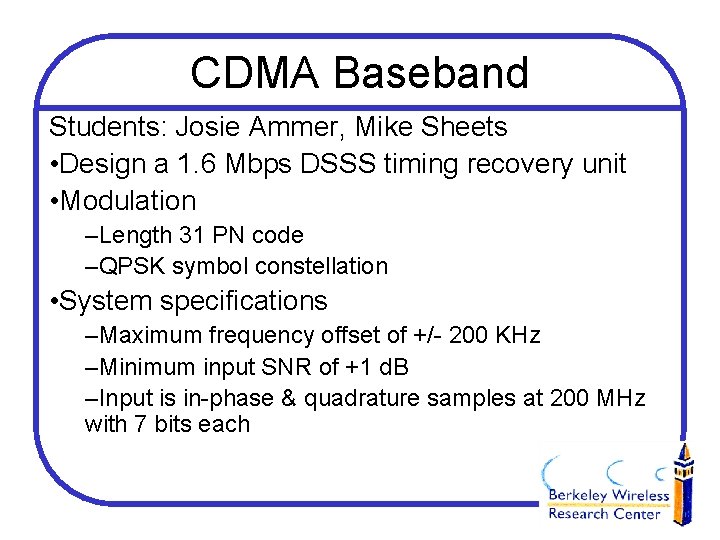

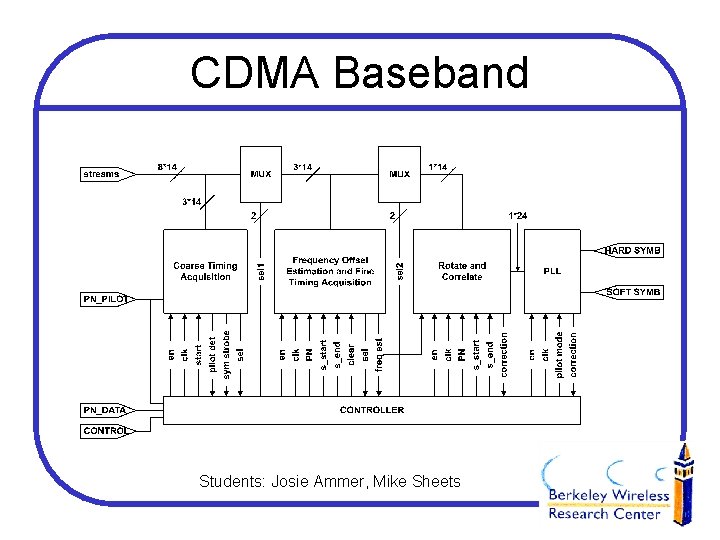

CDMA Baseband Students: Josie Ammer, Mike Sheets • Design a 1. 6 Mbps DSSS timing recovery unit • Modulation –Length 31 PN code –QPSK symbol constellation • System specifications –Maximum frequency offset of +/- 200 KHz –Minimum input SNR of +1 d. B –Input is in-phase & quadrature samples at 200 MHz with 7 bits each

CDMA Baseband Students: Josie Ammer, Mike Sheets

![RAKE Receiver Student Tufan Karalar I 8 Q Sn Z1 Sn1 Sn2 1 st RAKE Receiver Student: Tufan Karalar I 8 Q S[n] Z-1 S[n-1] S[n-2] 1 st](https://slidetodoc.com/presentation_image_h2/b7cfd0361c4d3af0c0c3570f5b9294b6/image-10.jpg)

RAKE Receiver Student: Tufan Karalar I 8 Q S[n] Z-1 S[n-1] S[n-2] 1 st 0 th R[n] Z-1 S[n-3] Z-1 2 nd R[n] 3 rd R[n] Third multipath component can be observed in here Correlator Σ Σ C*0 Σ C*1 22 C*2 22 C*3 22 One finger 24 Σ 22 Ul I Q Dissipates 4 m. W power, runs at 25 MHz has an areaof. 4 mm 2

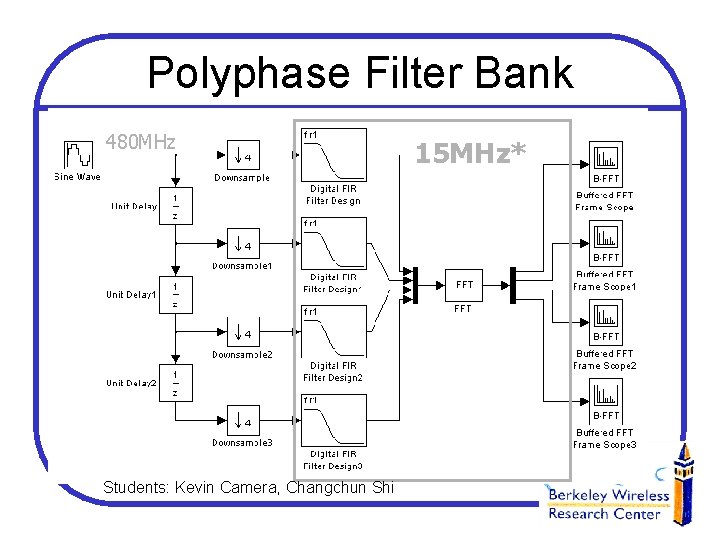

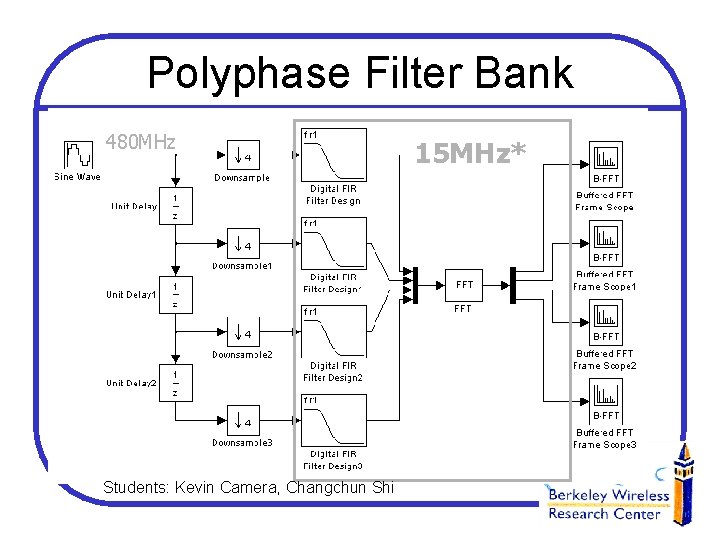

Polyphase Filter Bank 480 MHz Students: Kevin Camera, Changchun Shi 15 MHz*

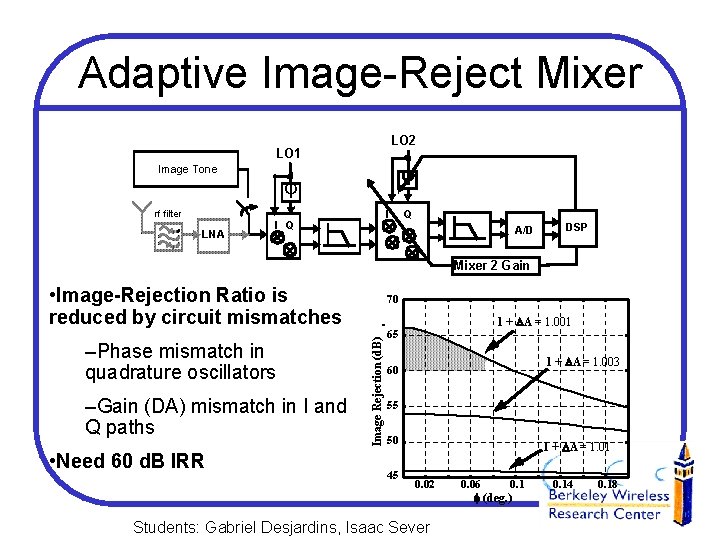

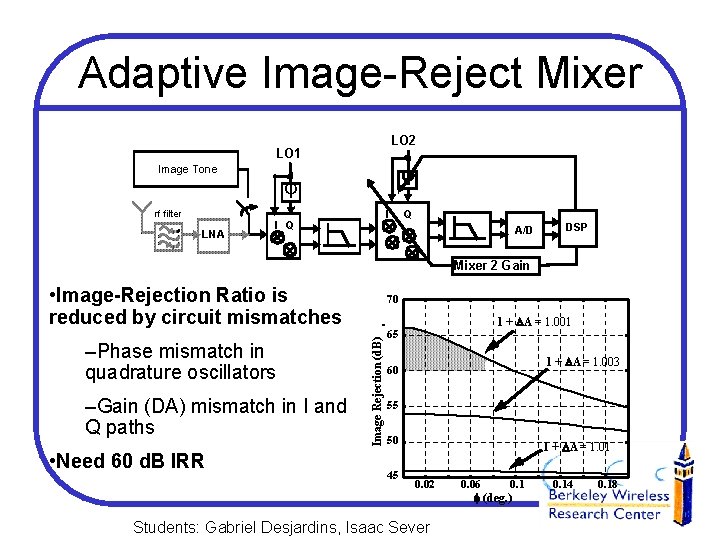

Adaptive Image-Reject Mixer LO 2 LO 1 Image Tone rf filter LNA j j I I Q Q A/D DSP Mixer 2 Gain • Image-Rejection Ratio is reduced by circuit mismatches –Gain (DA) mismatch in I and Q paths • Need 60 d. B IRR Image Rejection (d. B) –Phase mismatch in quadrature oscillators 70 1 + DA = 1. 001 65 1 + DA = 1. 003 60 55 50 45 1 + DA = 1. 01 0. 02 Students: Gabriel Desjardins, Isaac Sever 0. 06 0. 1 f (deg. ) 0. 14 0. 18

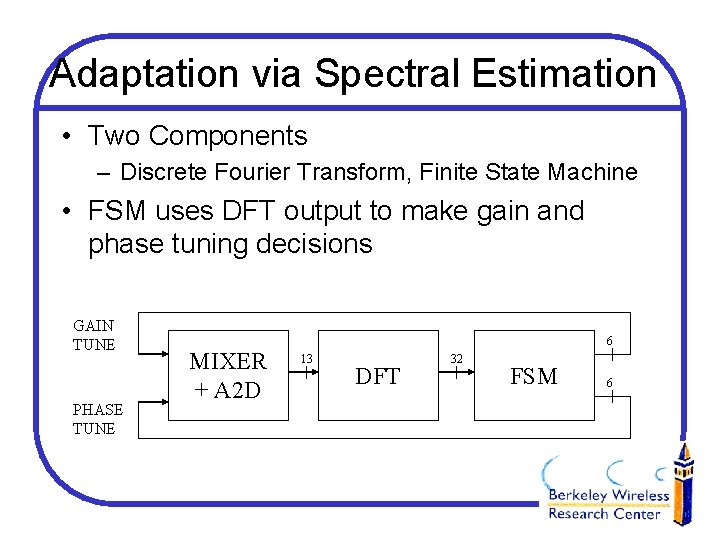

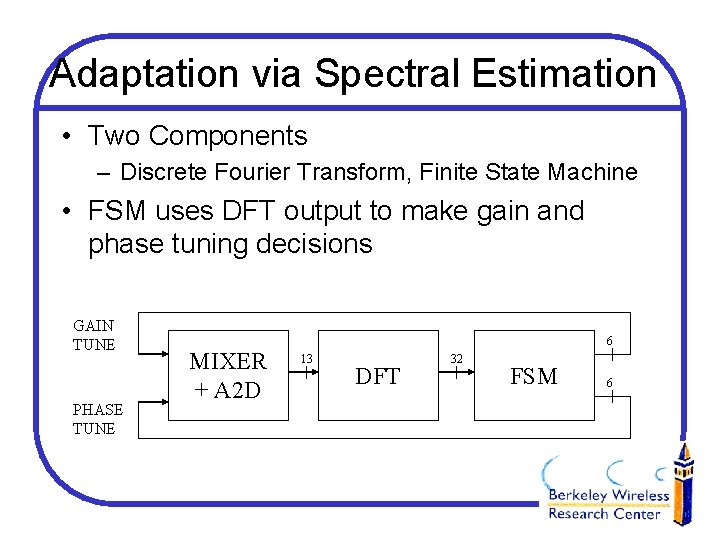

Adaptation via Spectral Estimation • Two Components – Discrete Fourier Transform, Finite State Machine • FSM uses DFT output to make gain and phase tuning decisions GAIN TUNE PHASE TUNE 6 MIXER + A 2 D 13 DFT 32 FSM 6

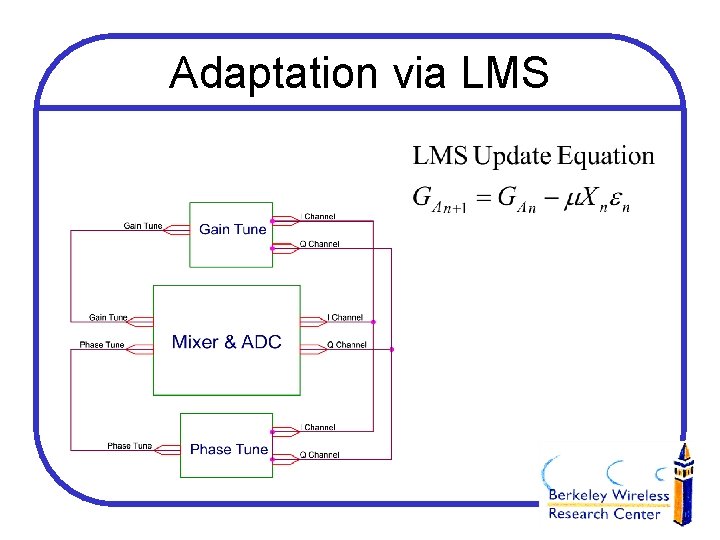

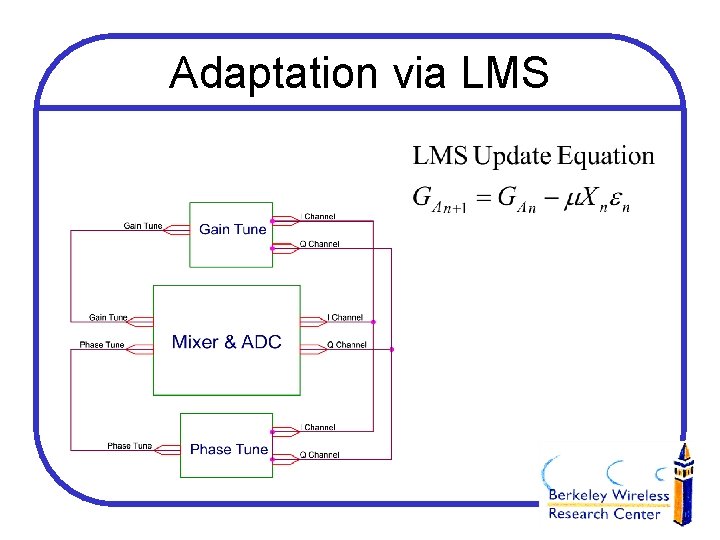

Adaptation via LMS

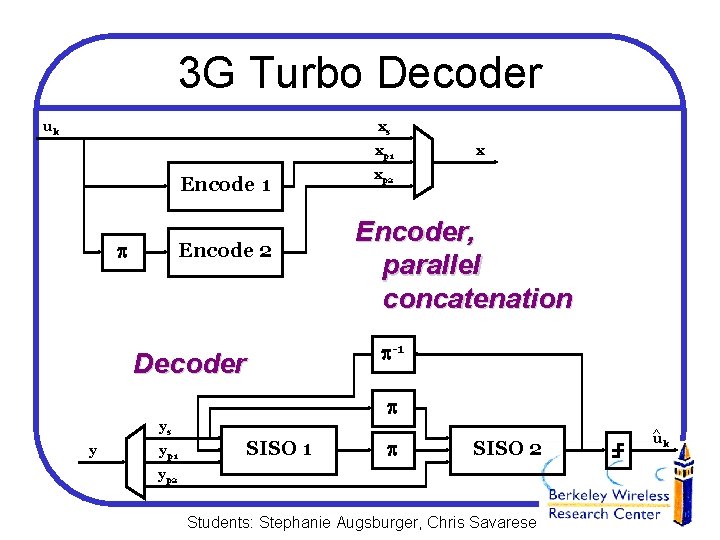

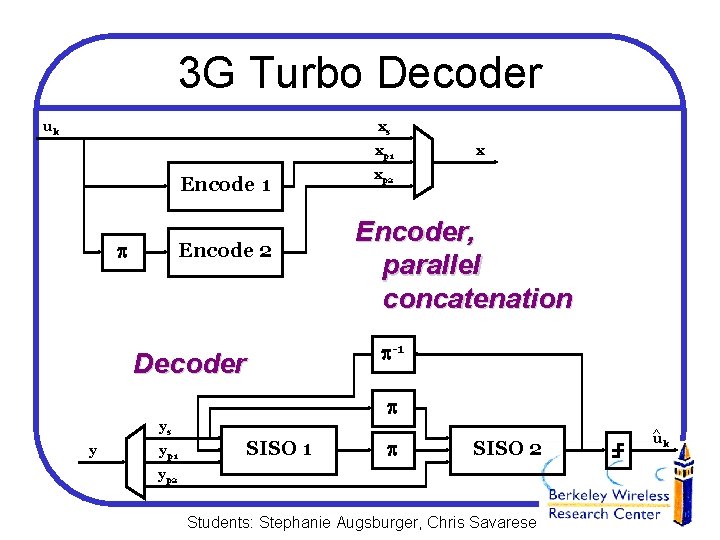

3 G Turbo Decoder uk xs xp 1 Encode 1 Encode 2 Decoder x xp 2 Encoder, parallel concatenation -1 ys y yp 1 SISO 2 yp 2 Students: Stephanie Augsburger, Chris Savarese ^ uk

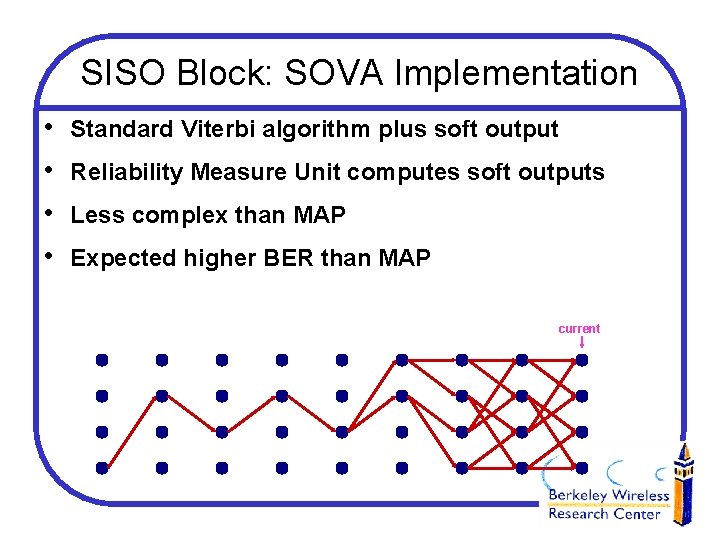

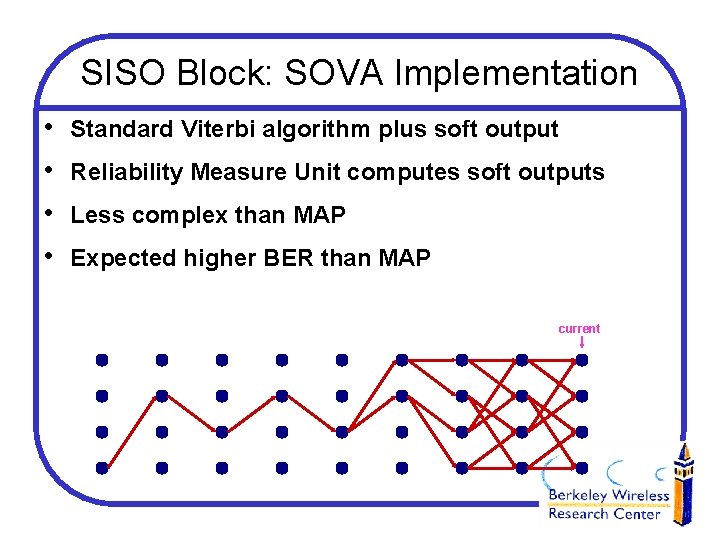

SISO Block: SOVA Implementation • • Standard Viterbi algorithm plus soft output Reliability Measure Unit computes soft outputs Less complex than MAP Expected higher BER than MAP current

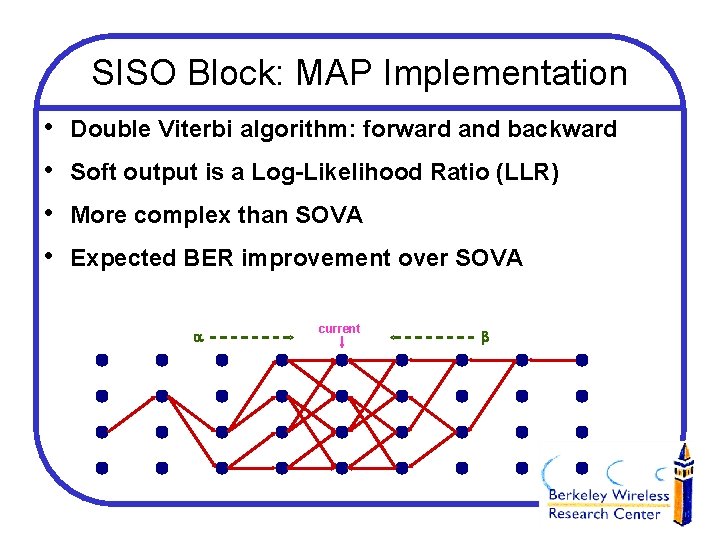

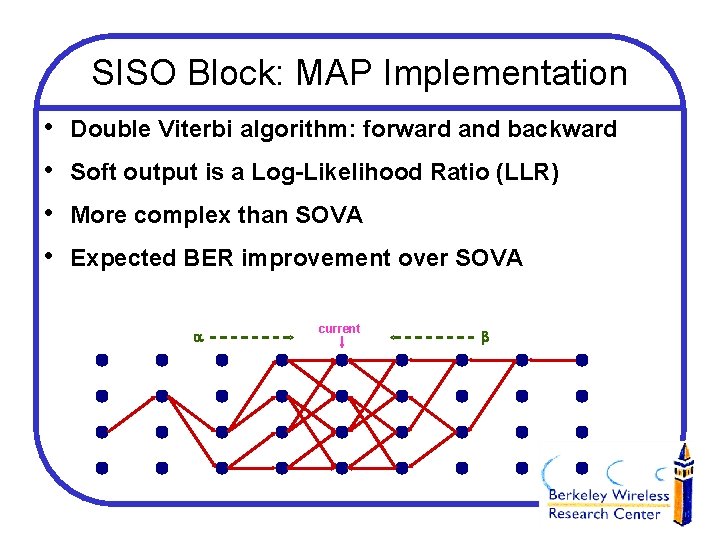

SISO Block: MAP Implementation • • Double Viterbi algorithm: forward and backward Soft output is a Log-Likelihood Ratio (LLR) More complex than SOVA Expected BER improvement over SOVA current

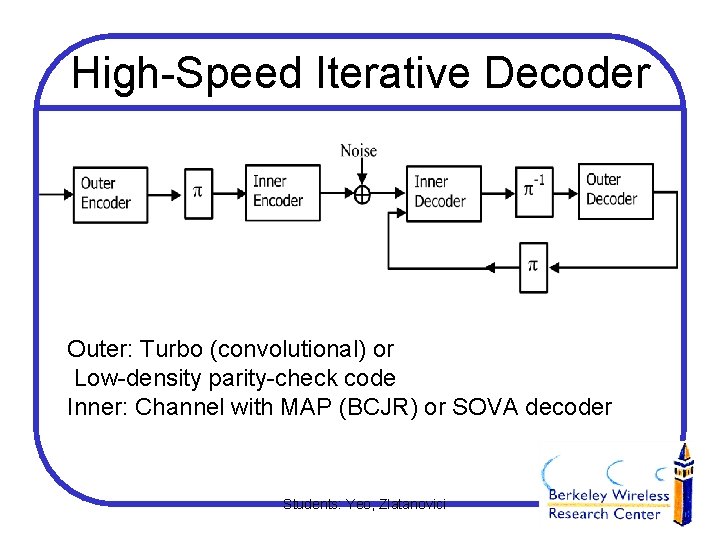

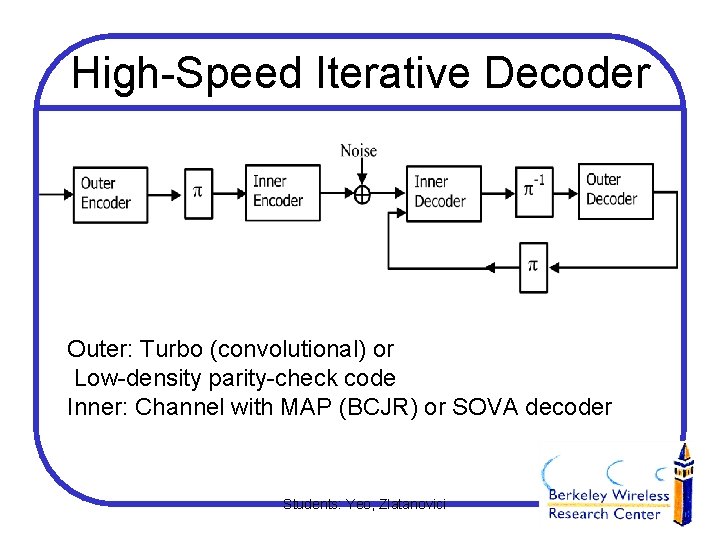

High-Speed Iterative Decoder Outer: Turbo (convolutional) or Low-density parity-check code Inner: Channel with MAP (BCJR) or SOVA decoder Students: Yeo, Zlatanovici

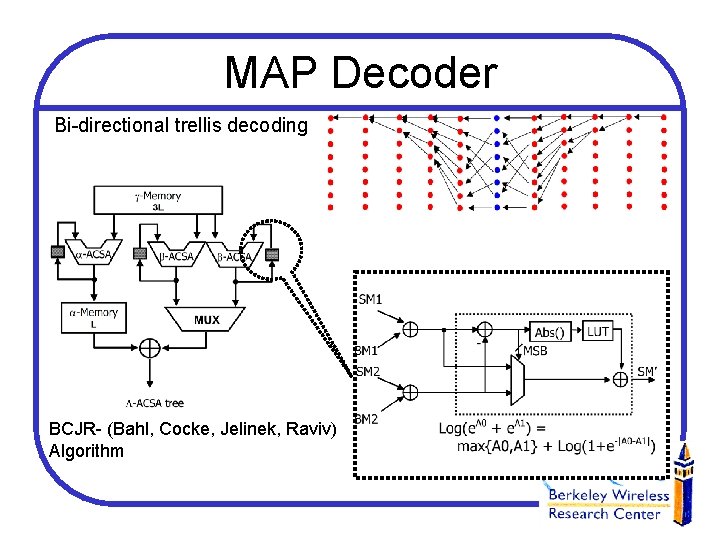

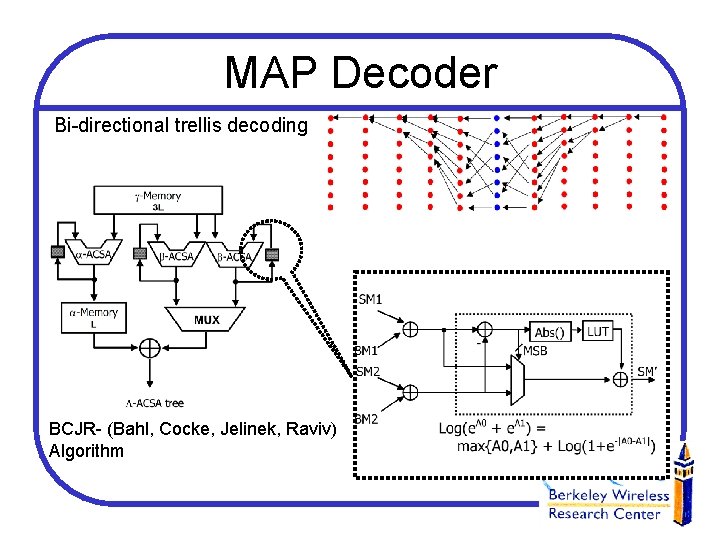

MAP Decoder Bi-directional trellis decoding BCJR- (Bahl, Cocke, Jelinek, Raviv) Algorithm

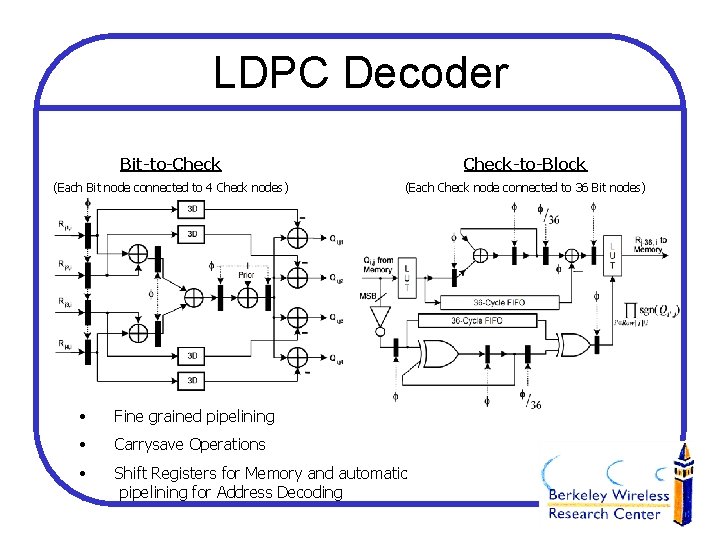

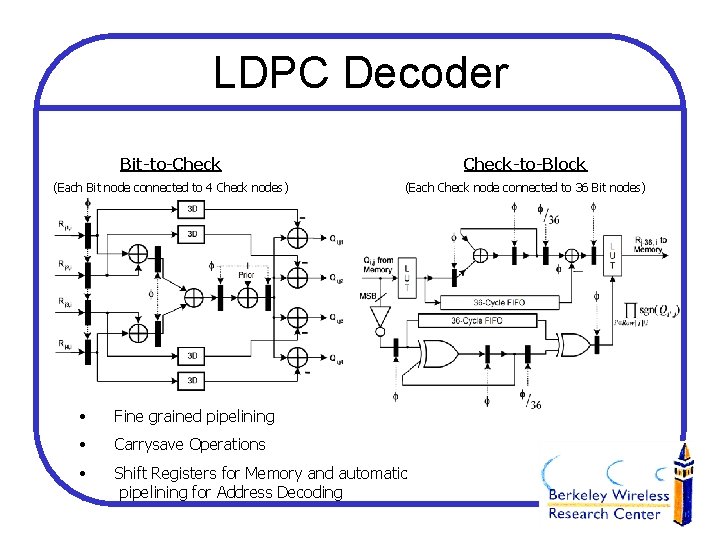

LDPC Decoder Bit-to-Check-to-Block (Each Bit node connected to 4 Check nodes) (Each Check node connected to 36 Bit nodes) • Fine grained pipelining • Carrysave Operations • Shift Registers for Memory and automatic pipelining for Address Decoding

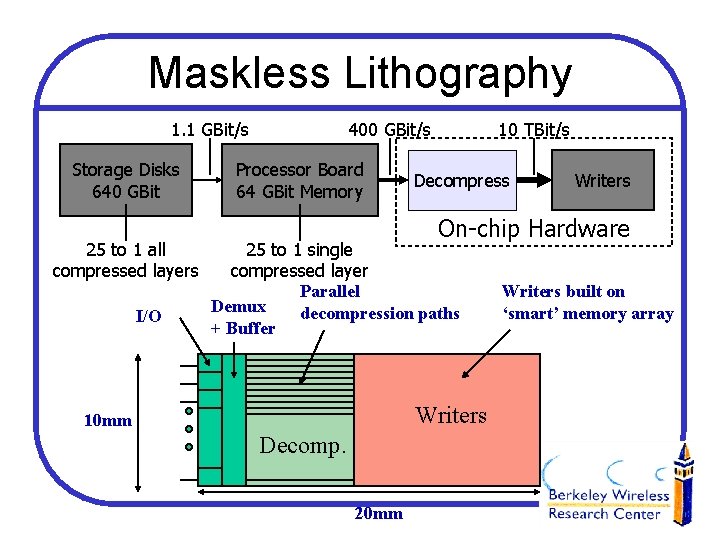

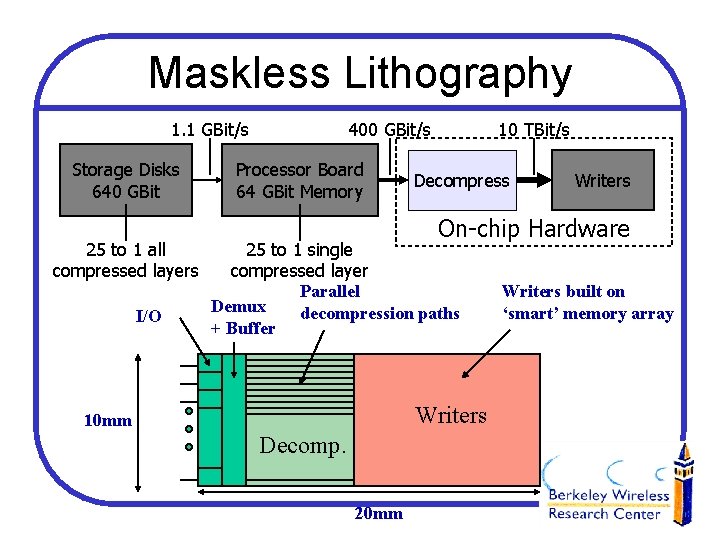

Maskless Lithography 1. 1 GBit/s Storage Disks 640 GBit 25 to 1 all compressed layers I/O 400 GBit/s Processor Board 64 GBit Memory 10 TBit/s Decompress Writers On-chip Hardware 25 to 1 single compressed layer Parallel Demux decompression paths + Buffer Writers 10 mm Decomp. 20 mm Writers built on ‘smart’ memory array

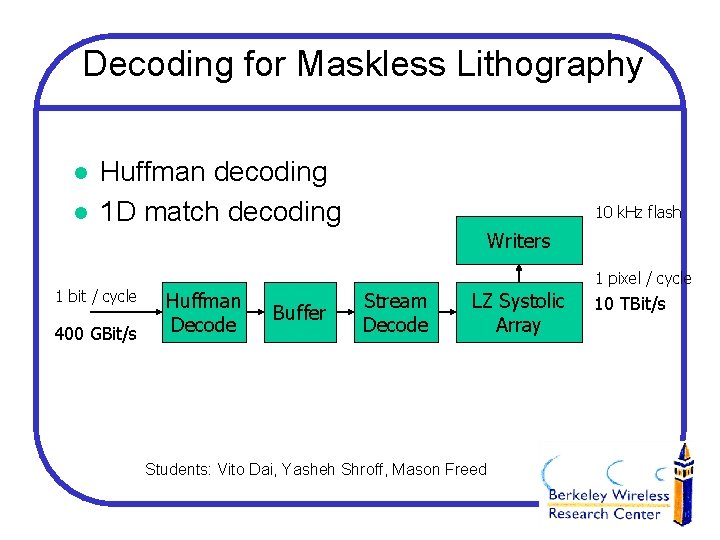

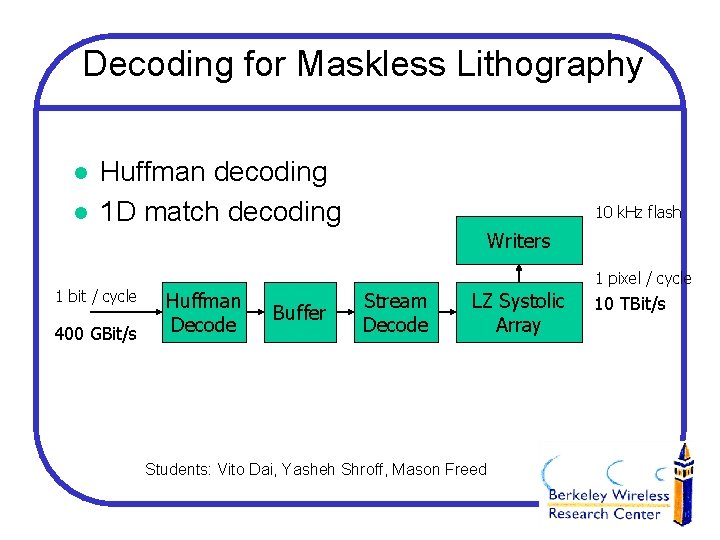

Decoding for Maskless Lithography l l Huffman decoding 1 D match decoding 10 k. Hz flash Writers 1 bit / cycle 400 GBit/s 1 pixel / cycle Huffman Decode Buffer Stream Decode LZ Systolic Array Students: Vito Dai, Yasheh Shroff, Mason Freed 10 TBit/s

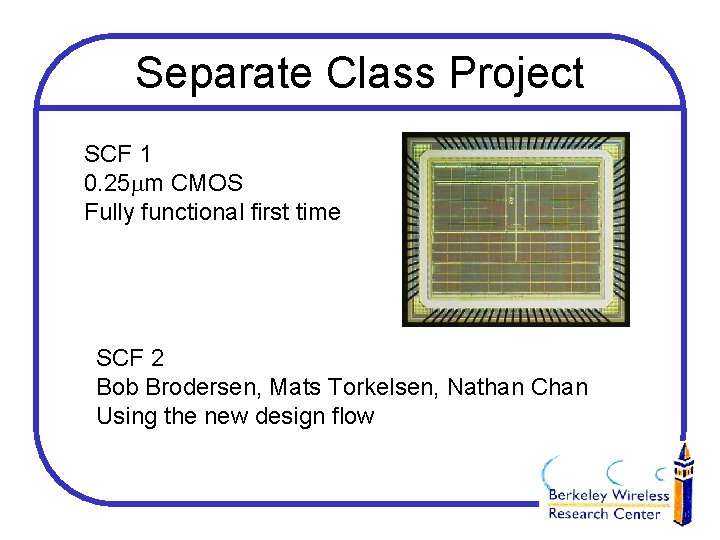

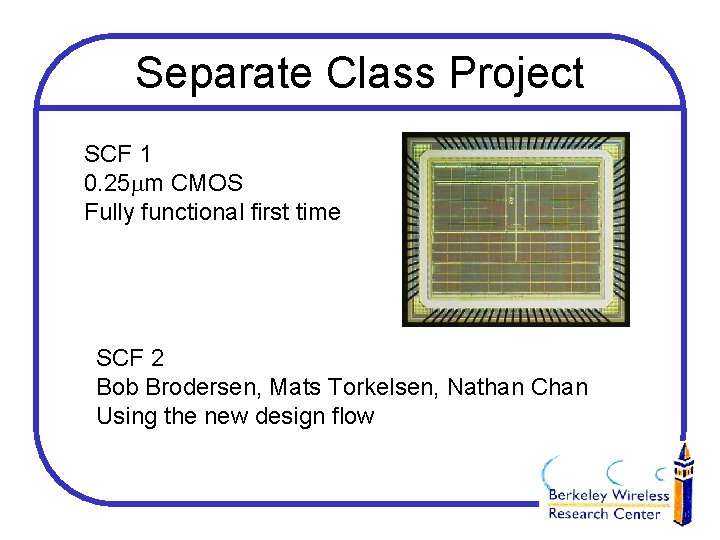

Separate Class Project SCF 1 0. 25 m CMOS Fully functional first time SCF 2 Bob Brodersen, Mats Torkelsen, Nathan Chan Using the new design flow

What did we learn? • • • Flow works surprisingly well Easy to learn Still fragile Need to add support for SRAM Need block-level timing analysis For faster designs will need regular placement