FPGA Implementation of the 3 D FDTD Algorithm

- Slides: 1

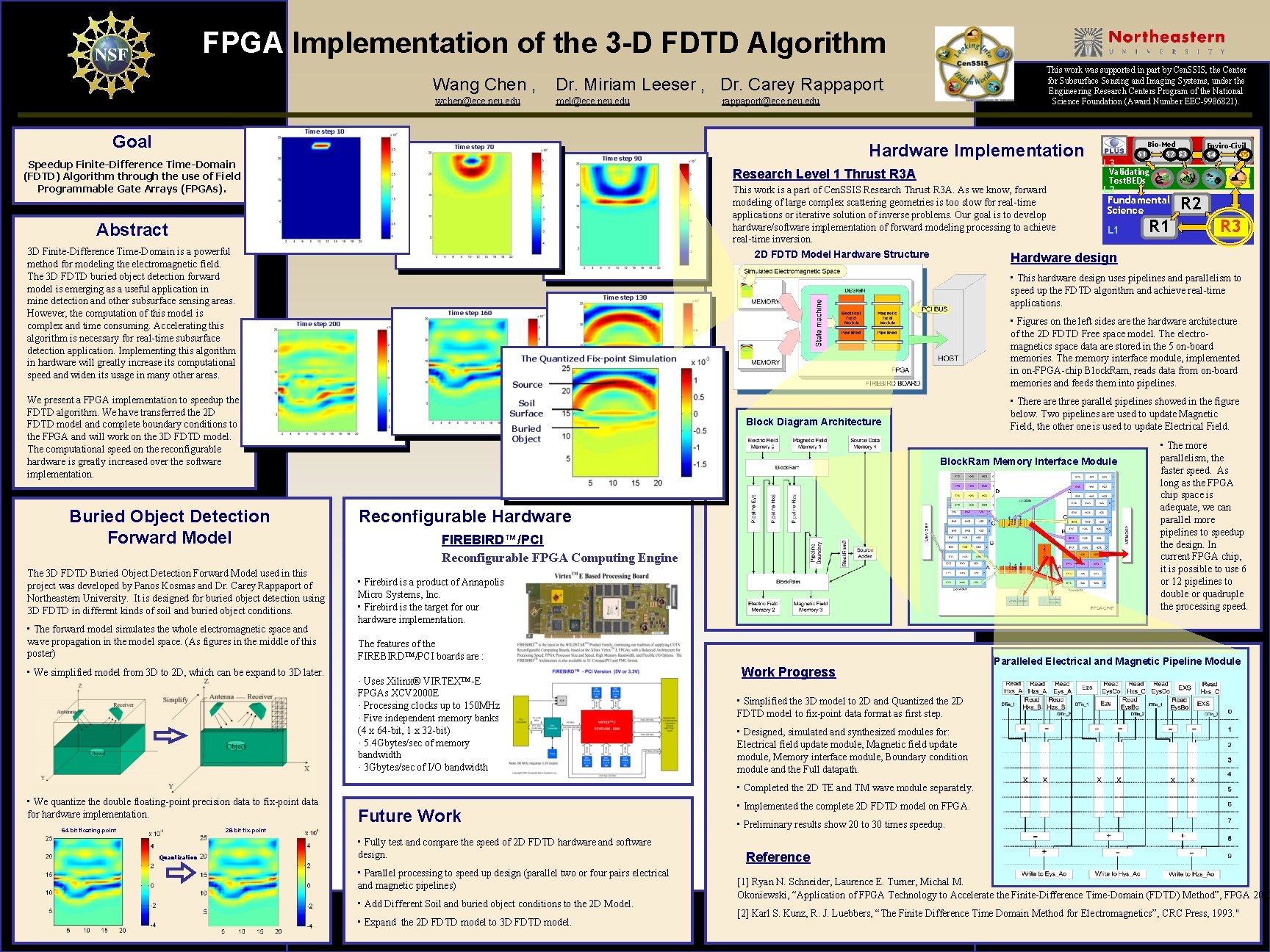

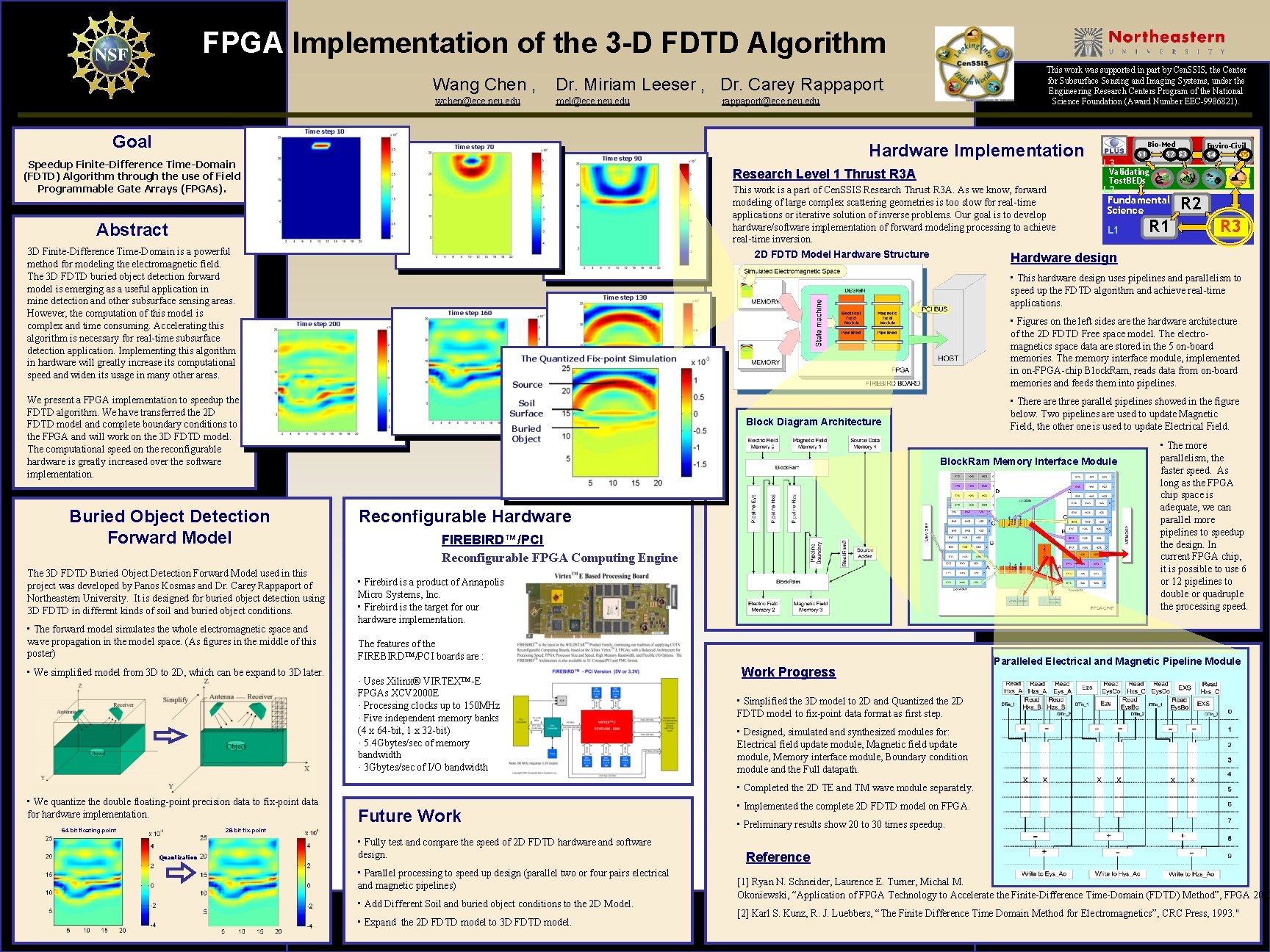

FPGA Implementation of the 3 -D FDTD Algorithm Wang Chen , Dr. Miriam Leeser , Dr. Carey Rappaport wchen@ece. neu. edu mel@ece. neu. edu rappaport@ece. neu. edu Goal Hardware Implementation Speedup Finite-Difference Time-Domain (FDTD) Algorithm through the use of Field Programmable Gate Arrays (FPGAs). Research Level 1 Thrust R 3 A This work is a part of Cen. SSIS Research Thrust R 3 A. As we know, forward modeling of large complex scattering geometries is too slow for real-time applications or iterative solution of inverse problems. Our goal is to develop hardware/software implementation of forward modeling processing to achieve real-time inversion. 2 D FDTD Model Hardware Structure Hardware Abstract 3 D Finite-Difference Time-Domain is a powerful method for modeling the electromagnetic field. The 3 D FDTD buried object detection forward model is emerging as a useful application in mine detection and other subsurface sensing areas. However, the computation of this model is complex and time consuming. Accelerating this algorithm is necessary for real-time subsurface detection application. Implementing this algorithm in hardware will greatly increase its computational speed and widen its usage in many other areas. The 3 D FDTD Buried Object Detection Forward Model used in this project was developed by Panos Kosmas and Dr. Carey Rappaport of Northeastern University. It is designed for buried object detection using 3 D FDTD in different kinds of soil and buried object conditions. • The forward model simulates the whole electromagnetic space and wave propagation in the model space. (As figures in the middle of this poster) • We simplified model from 3 D to 2 D, which can be expand to 3 D later. L 3 S 1 Bio-Med S 2 S 3 Enviro-Civil S 4 S 5 Validating Test. BEDs L 2 Fundamental Science L 1 R 2 R 3 design • This hardware design uses pipelines and parallelism to speed up the FDTD algorithm and achieve real-time applications. • Figures on the left sides are the hardware architecture of the 2 D FDTD Free space model. The electromagnetics space data are stored in the 5 on-board memories. The memory interface module, implemented in on-FPGA-chip Block. Ram, reads data from on-board memories and feeds them into pipelines. We present a FPGA implementation to speedup the FDTD algorithm. We have transferred the 2 D FDTD model and complete boundary conditions to the FPGA and will work on the 3 D FDTD model. The computational speed on the reconfigurable hardware is greatly increased over the software implementation. Buried Object Detection Forward Model This work was supported in part by Cen. SSIS, the Center for Subsurface Sensing and Imaging Systems, under the Engineering Research Centers Program of the National Science Foundation (Award Number EEC-9986821). • There are three parallel pipelines showed in the figure below. Two pipelines are used to update Magnetic Field, the other one is used to update Electrical Field. Block Diagram Architecture Block. Ram Memory Interface Module Reconfigurable Hardware FIREBIRD™/PCI Reconfigurable FPGA Computing Engine • Firebird is a product of Annapolis Micro Systems, Inc. • Firebird is the target for our hardware implementation. The features of the FIREBIRD™/PCI boards are : · Uses Xilinx® VIRTEX™-E FPGAs XCV 2000 E · Processing clocks up to 150 MHz · Five independent memory banks (4 x 64 -bit, 1 x 32 -bit) · 5. 4 Gbytes/sec of memory bandwidth · 3 Gbytes/sec of I/O bandwidth Work Progress • The more parallelism, the faster speed. As long as the FPGA chip space is adequate, we can parallel more pipelines to speedup the design. In current FPGA chip, it is possible to use 6 or 12 pipelines to double or quadruple the processing speed. Paralleled Electrical and Magnetic Pipeline Module • Simplified the 3 D model to 2 D and Quantized the 2 D FDTD model to fix-point data format as first step. • Designed, simulated and synthesized modules for: Electrical field update module, Magnetic field update module, Memory interface module, Boundary condition module and the Full datapath. • Completed the 2 D TE and TM wave module separately. • We quantize the double floating-point precision data to fix-point data for hardware implementation. 64 -bit floating-point Future Work 28 -bit fix-point Quantization • Fully test and compare the speed of 2 D FDTD hardware and software design. • Parallel processing to speed up design (parallel two or four pairs electrical and magnetic pipelines) • Add Different Soil and buried object conditions to the 2 D Model. • Expand the 2 D FDTD model to 3 D FDTD model. • Implemented the complete 2 D FDTD model on FPGA. • Preliminary results show 20 to 30 times speedup. Reference [1] Ryan N. Schneider, Laurence E. Turner, Michal M. Okoniewski, “Application of FPGA Technology to Accelerate the Finite-Difference Time-Domain (FDTD) Method”, FPGA 2002 [2] Karl S. Kunz, R. J. Luebbers, “The Finite Difference Time Domain Method for Electromagnetics”, CRC Press, 1993. "