FPGA Based System Design Tahir Muhammad tm uettaxilayahoo

FPGA Based System Design Tahir Muhammad tm. uettaxila@yahoo. com Spring 2013 Lecture 1 FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Course Organization n § § n Course material: All the course material can be found at the course webpage http: //web. uettaxila. edu. pk/CMS/SP 2013/ect. FPBbs/index. a sp Instructor: Tahir Muhammad Office: ASIC Lab, UET Taxila Email: tm. uettaxila@yahoo. com Office Hours: Wednesday n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Course Objectives After taking this course, you will: – Learn how to design digital circuits with HDL – Have an understanding » » » » VLSI: Fabrication, circuits, interconnects FPGA based design techniques FPGA fabrics FPGA optimization for size, speed, and power consumption Verilog HDL The structure of large digital circuits Large scale platform and multi-FPGA systems – Understand some of the important ideas for designing more complex systems. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Course Organization n Lectures – n Labs – n Wednesday 5 -7 Wednesday 1 -3 Textbook – FPGA-Based System Design by Wayne Wolf We will mark which section in the book corresponds to the material covered in each lecture Lecture notes are often enough to do the homeworks and the exams, but reading the book is highly recommended FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Course Outline n n n n Chapter 1: FPGA Based Systems Chapter 2: VLSI Technology Chapter 3: FPGA Fabrics Chapter 4: Combinational Logic Chapter 5: Sequential Machines Chapter 6: Architectures Chapter 7: Large Scale Systems FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Overview Why VLSI? n Moore’s Law. n Why FPGAs? n The VLSI and system design process. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Why VLSI? n Integration improves the design: – lower parasitics = higher speed; – lower power; – physically smaller. n Integration reduces manufacturing cost(almost) no manual assembly. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

VLSI and you n Microprocessors: – personal computers; – microcontrollers. DRAM/SRAM/flash. n Audio/video and other consumer systems. n Telecommunications. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Moore’s Law Gordon Moore: co-founder of Intel. n Predicted that number of transistors per chip would grow exponentially (double every 18 months). n Exponential improvement in technology is a natural trend: steam engines, dynamos, automobiles. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

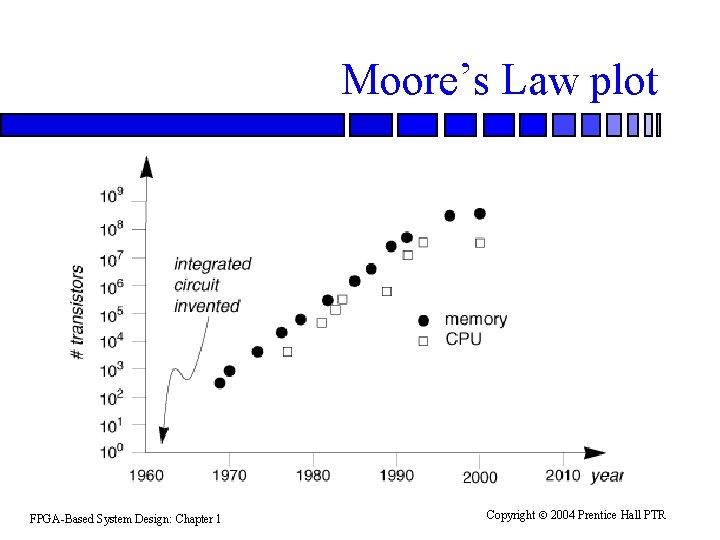

Moore’s Law plot FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

The cost of fabrication Current cost: $2 -3 billion. n Typical fab line occupies about 1 city block, employs a few hundred people. n New fabrication processes require 6 -8 month turnaround. n Most profitable period is first 18 months-2 years. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Cost factors in ICs n For large-volume ICs: – packaging is largest cost; – testing is second-largest cost. n For low-volume ICs, design costs may swamp all manufacturing costs. – $10 million-$20 million. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

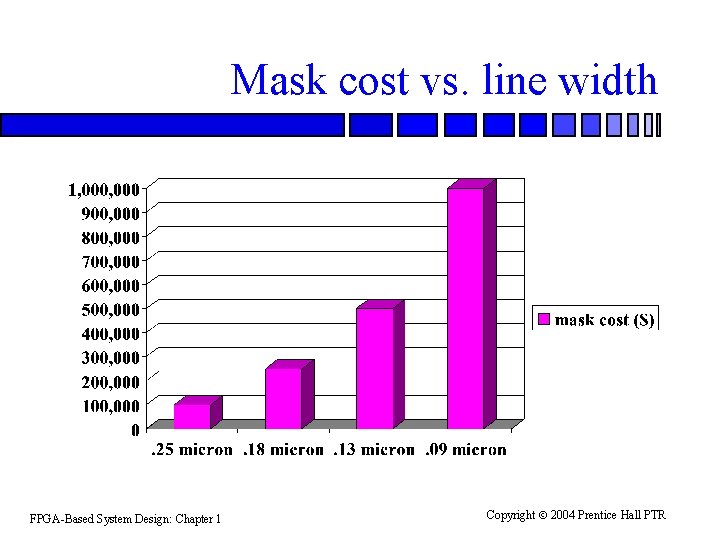

Mask cost vs. line width FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

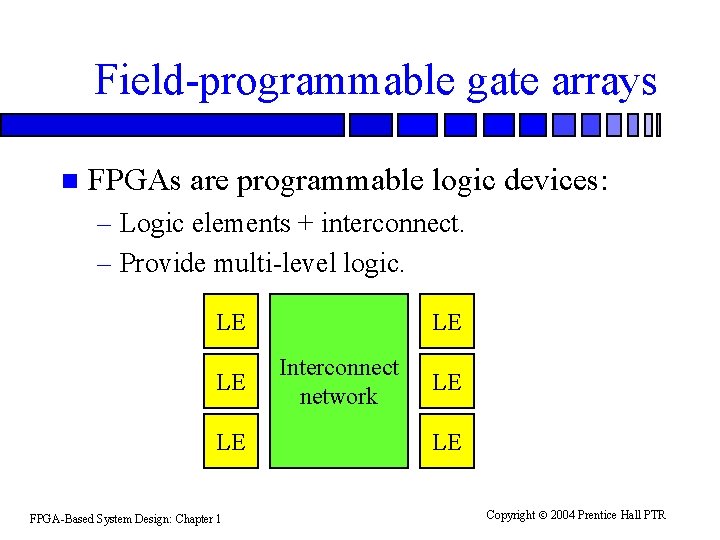

Field-programmable gate arrays n FPGAs are programmable logic devices: – Logic elements + interconnect. – Provide multi-level logic. LE LE LE FPGA-Based System Design: Chapter 1 LE Interconnect network LE LE Copyright 2004 Prentice Hall PTR

FPGAs and VLSI n FPGAs are standard parts: – Pre-manufactured. – Don’t worry (much) about physical design. n Custom silicon: – Tailored to your application. – Generally lower power consumption. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Standard parts vs. custom n Do you build your system with an FPGA or with custom silicon? – FPGAs have shorter design cycle. – FPGAs have no manufacturing delay. – FPGAs reduce inventory. – FPGAs are slower, larger, more power-hungry. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Challenges in system design Multiple levels of abstraction: logic to CPUs. n Multiple and conflicting constraints: low cost and high performance are often at odds. n Short design time: Late products are often irrelevant. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

The system design process May be part of larger product design. n Major levels of abstraction: n – specification; – architecture; – logic design; – circuit design; – layout. FPGA-Based System Design: Chapter 1 FPGA-based system design Copyright 2004 Prentice Hall PTR

Dealing with complexity Divide-and-conquer: limit the number of components you deal with at any one time. n Group several components into larger components: n – transistors form gates; – gates form functional units; – functional units form processing elements; – etc. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

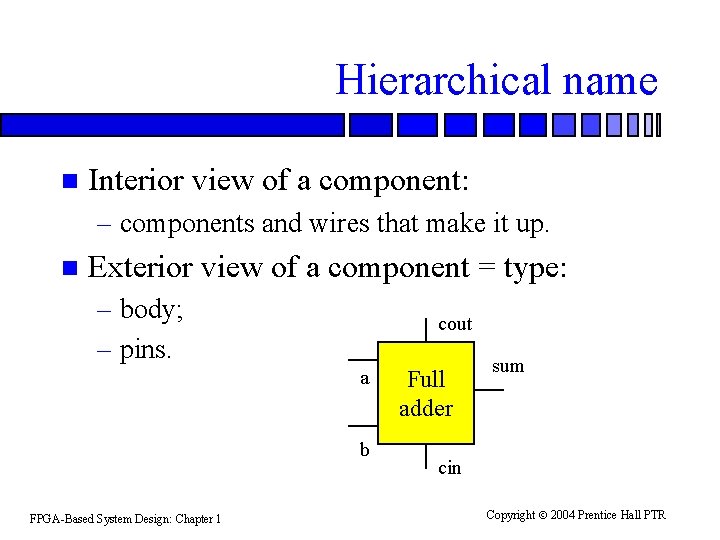

Hierarchical name n Interior view of a component: – components and wires that make it up. n Exterior view of a component = type: – body; – pins. cout a b FPGA-Based System Design: Chapter 1 Full adder sum cin Copyright 2004 Prentice Hall PTR

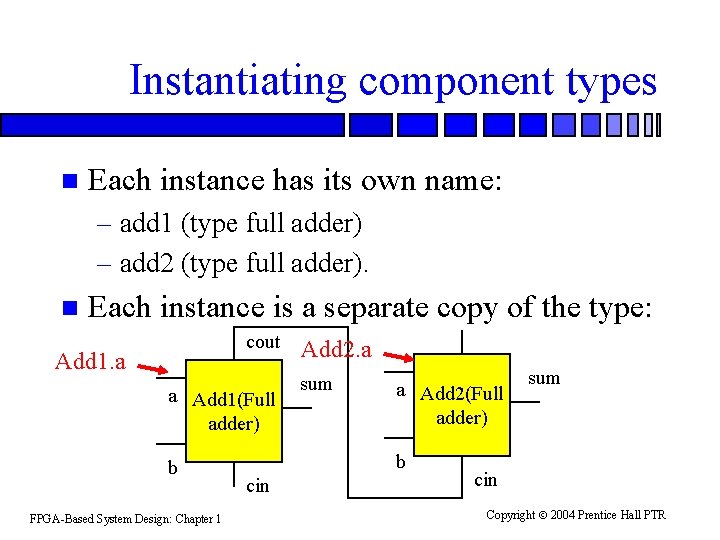

Instantiating component types n Each instance has its own name: – add 1 (type full adder) – add 2 (type full adder). n Each instance is a separate copy of the type: cout Add 1. a a Add 1(Full adder) b FPGA-Based System Design: Chapter 1 Add 2. a sum a Add 2(Full adder) b cin sum cin Copyright 2004 Prentice Hall PTR

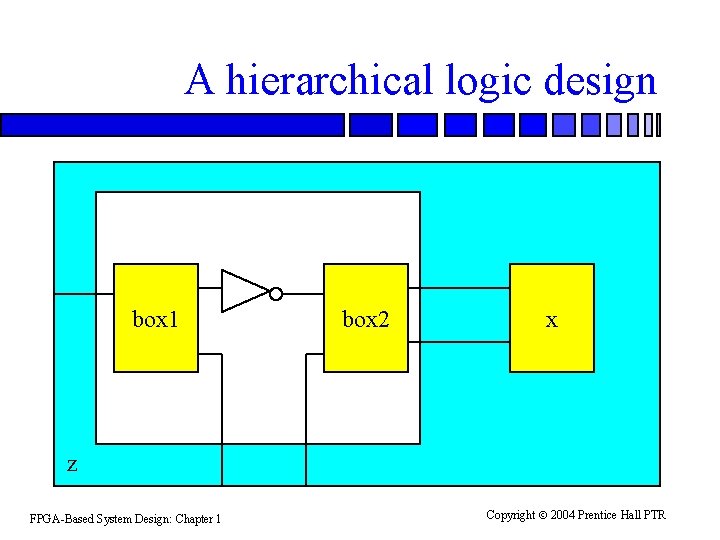

A hierarchical logic design box 1 box 2 x z FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

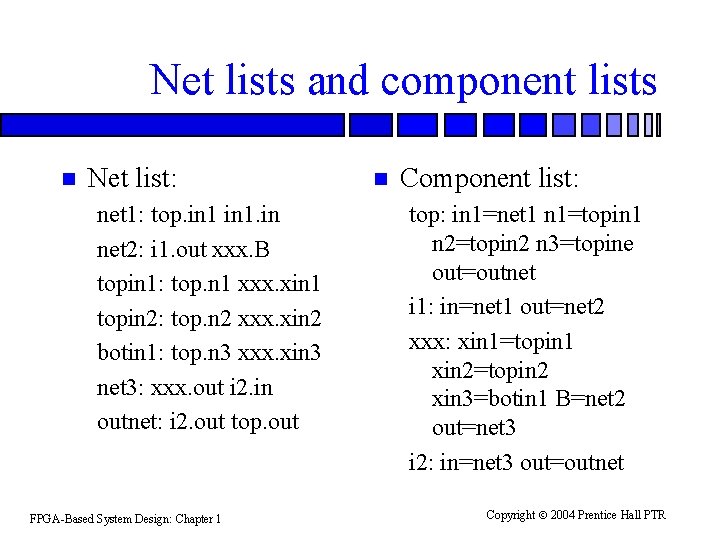

Net lists and component lists n Net list: net 1: top. in 1. in net 2: i 1. out xxx. B topin 1: top. n 1 xxx. xin 1 topin 2: top. n 2 xxx. xin 2 botin 1: top. n 3 xxx. xin 3 net 3: xxx. out i 2. in outnet: i 2. out top. out FPGA-Based System Design: Chapter 1 n Component list: top: in 1=net 1 n 1=topin 1 n 2=topin 2 n 3=topine out=outnet i 1: in=net 1 out=net 2 xxx: xin 1=topin 1 xin 2=topin 2 xin 3=botin 1 B=net 2 out=net 3 i 2: in=net 3 out=outnet Copyright 2004 Prentice Hall PTR

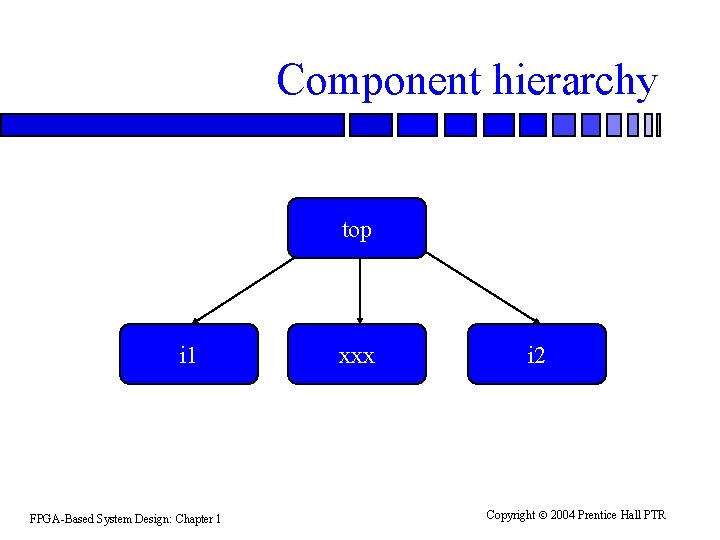

Component hierarchy top i 1 FPGA-Based System Design: Chapter 1 xxx i 2 Copyright 2004 Prentice Hall PTR

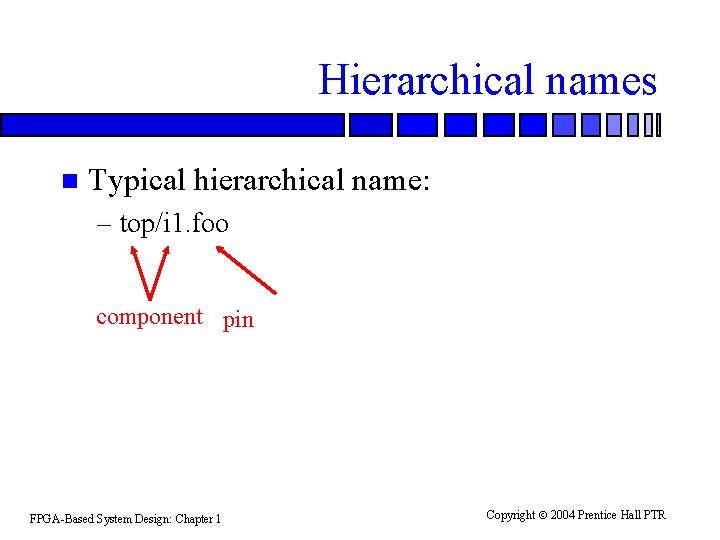

Hierarchical names n Typical hierarchical name: – top/i 1. foo component pin FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

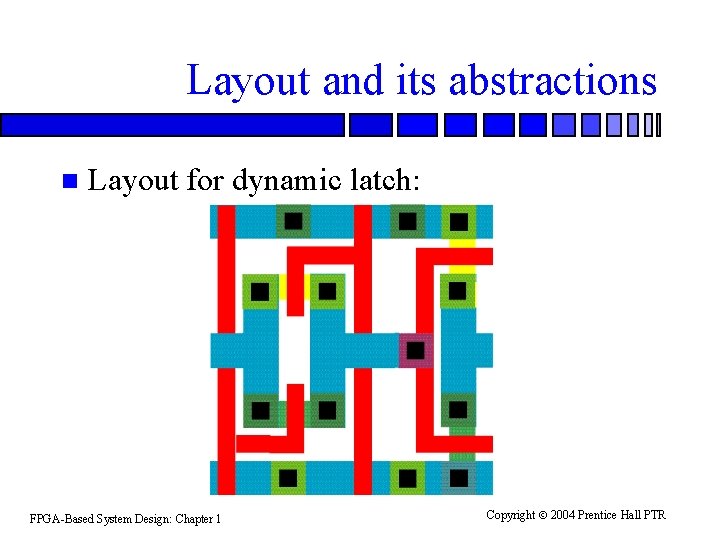

Layout and its abstractions n Layout for dynamic latch: FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

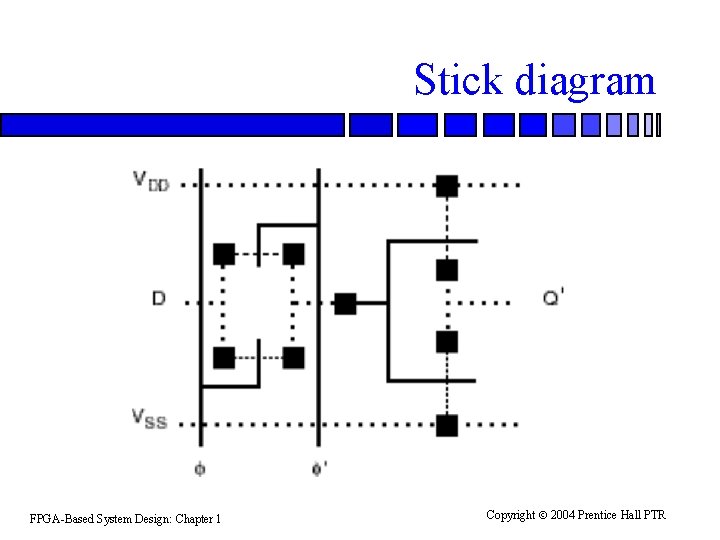

Stick diagram FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

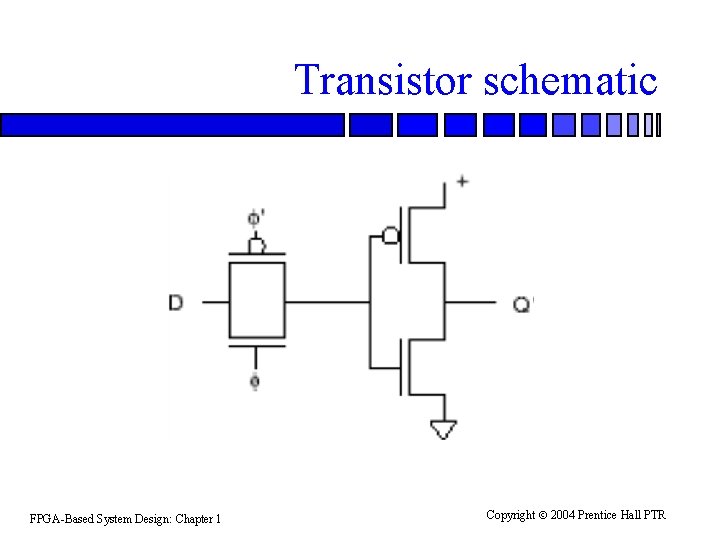

Transistor schematic FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

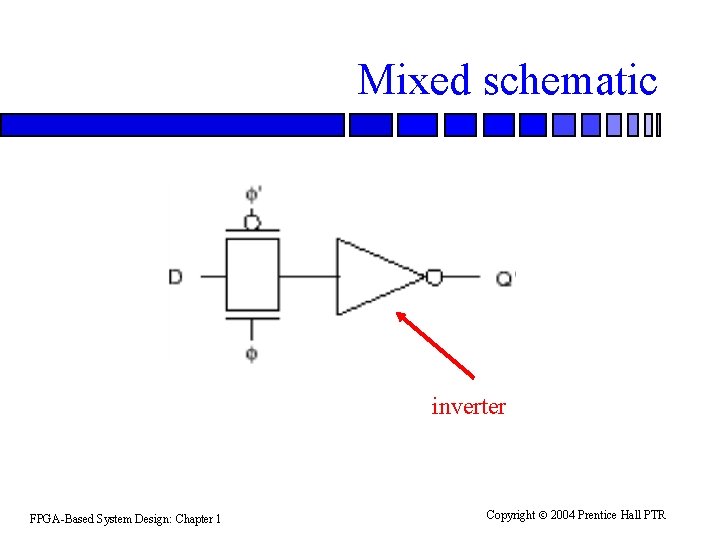

Mixed schematic inverter FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Levels of abstraction Specification: function, cost, etc. n Architecture: large blocks. n Logic: gates + registers. n Circuits: transistor sizes for speed, power. n Layout: determines parasitics. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

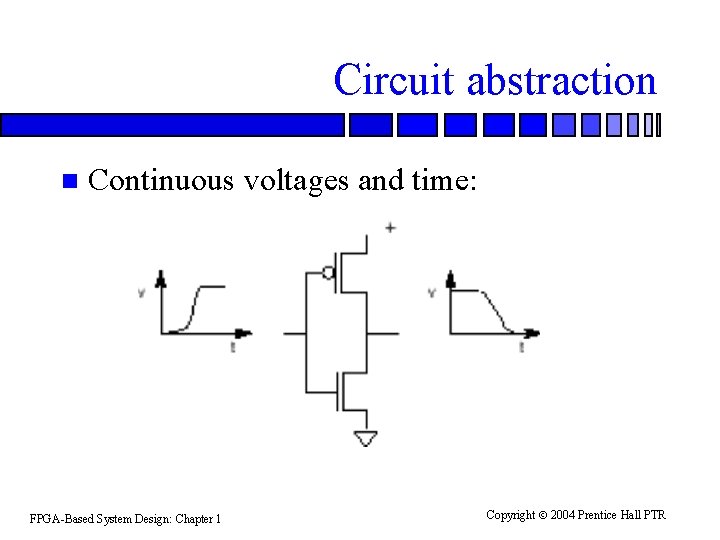

Circuit abstraction n Continuous voltages and time: FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

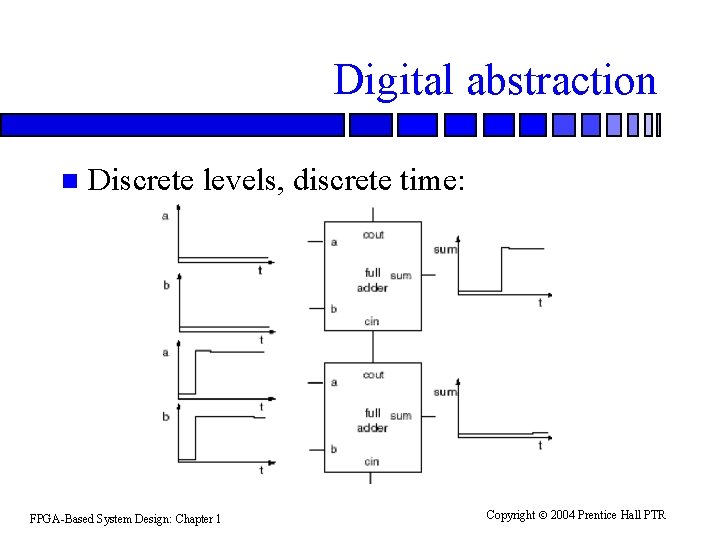

Digital abstraction n Discrete levels, discrete time: FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

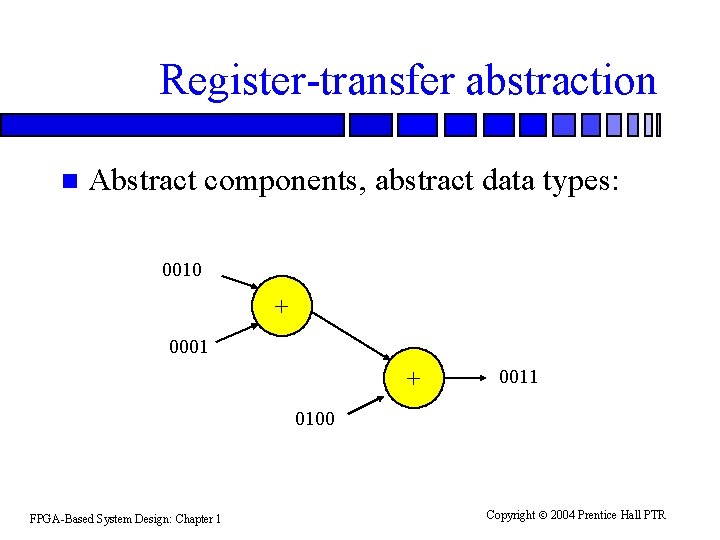

Register-transfer abstraction n Abstract components, abstract data types: 0010 + 0001 + 0011 0100 FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Top-down vs. bottom-up design n Top-down design adds functional detail. – Create lower levels of abstraction from upper levels. Bottom-up design creates abstractions from low-level behavior. n Good design needs both top-down and bottom-up efforts. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

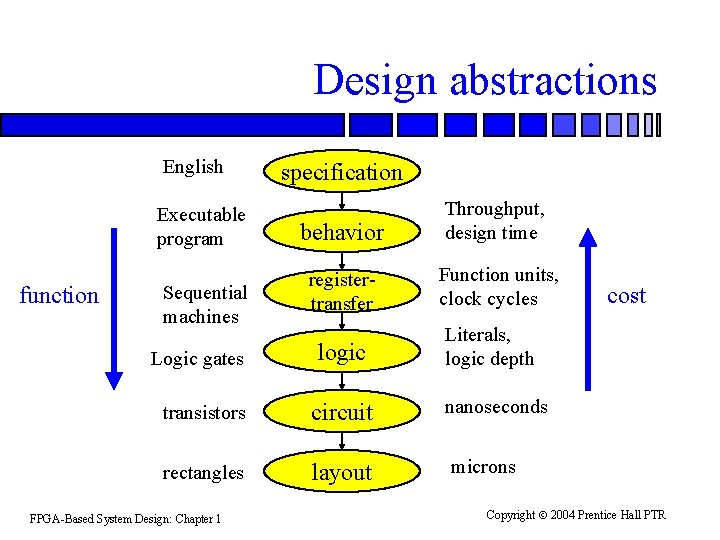

Design abstractions English Executable program function Sequential machines Logic gates specification behavior Throughput, design time registertransfer Function units, clock cycles logic Literals, logic depth transistors circuit nanoseconds rectangles layout microns FPGA-Based System Design: Chapter 1 cost Copyright 2004 Prentice Hall PTR

FPGA design FPGA manufacturer creates an FPGA fabric; system designer uses the fabric. n FPGA fabric design issues: n – Study sample user designs. – Select interconnect topology. – Create logic element structures. – Design circuits, layout. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Why do we care about layout? We won’t design layout. n Layout determines: n – Logic delay. – Interconnect delay. – Energy consumption. n We want to understand sources of FPGA characteristics. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Design validation Must check at every step that errors haven’t been introduced-the longer an error remains, the more expensive it becomes to remove it. n Forward checking: compare results of lessand more-abstract stages. n Back annotation: copy performance numbers to earlier stages. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

- Slides: 38