FPGA Based EEPROM Programmer By Jeremy Cooke With

FPGA Based E/EPROM Programmer By: Jeremy Cooke With Advisor: Dr. Izadi 1

Presentation Overview l l l l 2 Definitions Project Goals Technologies Used Hardware Design Software Design Problems and Solutions Conclusions

Definitions l E/EPROM Programmer – l FPGA – 3 A device that can read and write the contents of a variety of non-volatile memory chips Field Programmable Gate Array, a programmable logic device

Project Goals l l Design and develop an E/EPROM programmer Explore advanced digital logic techniques – l l Mix analog and digital circuitry Interface hardware with Windows based software – – 4 Learn modern FPGA design techniques Parallel port interfacing techniques Communications protocol development and implementation

Technologies Used l Field Programmable Gate Array – l Analog Circuitry – l Power Subsystem Windows Based Software – 5 Digital core Programming in Visual C++ 6. 0

Hardware Design l l Hardware broken into separate analog and digital sections Digital hardware – – – l Analog Hardware (Internal Power Supply) – – – 6 Based around an FPGA core Handles control and coordination of all other components Controlled by Personal Computer over parallel port Used for voltage regulation and control Based around DC-DC converter and adjustable voltage regulators Controlled by FPGA

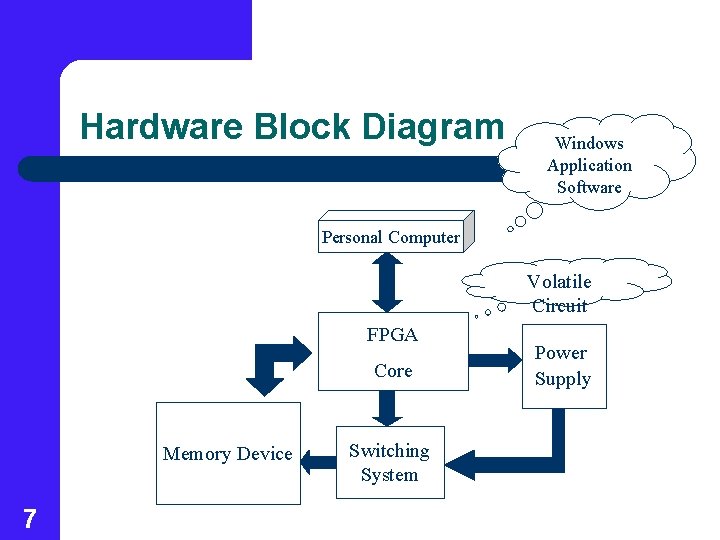

Hardware Block Diagram Windows Application Software Personal Computer Volatile Circuit FPGA Core Memory Device 7 Switching System Power Supply

Xilinx FPGA l l Excellent for complex digital systems PROM required for non-volatile operation XC 4010 XL Field Programmable Gate Array 8 Logic Cells 950 System Gates 7 -20 K Max RAM Bits 12, 800

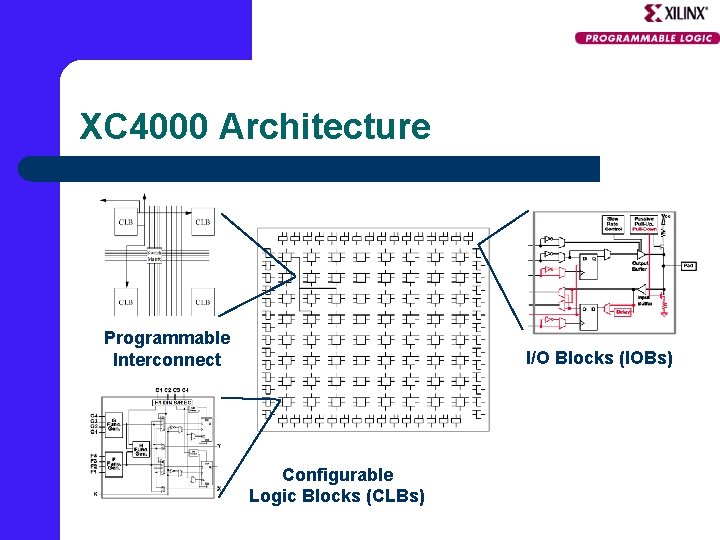

XC 4000 Architecture Programmable Interconnect I/O Blocks (IOBs) Configurable Logic Blocks (CLBs)

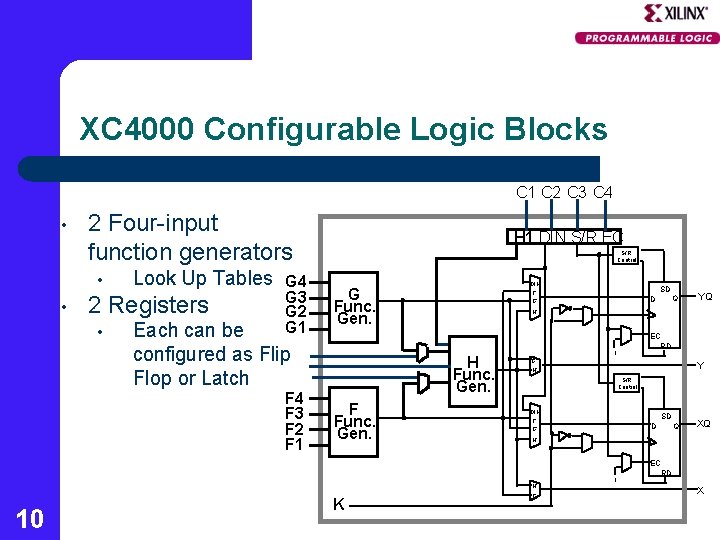

XC 4000 Configurable Logic Blocks C 1 C 2 C 3 C 4 • 2 Four-input function generators • • Look Up Tables 2 Registers • G 4 G 3 G 2 G 1 Each can be configured as Flip Flop or Latch F 4 F 3 F 2 F 1 H 1 DIN S/R EC S/R Control DIN F' G' G Func. Gen. 10 YQ EC RD 1 G' H' Y S/R Control DIN F' G' SD D Q XQ H' H' K Q H' H Func. Gen. F Func. Gen. SD D F' 1 EC RD X

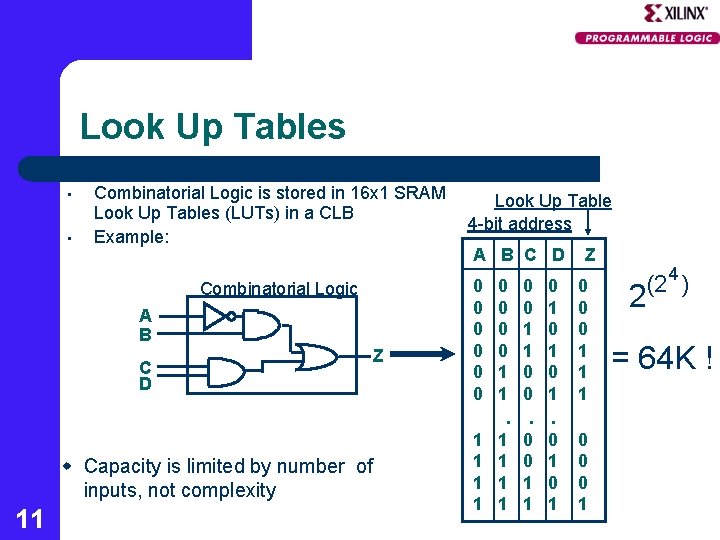

Look Up Tables • • Combinatorial Logic is stored in 16 x 1 SRAM Look Up Tables (LUTs) in a CLB Example: Combinatorial Logic A B C D Z Look Up Table 4 -bit address A B C D 0 0 0 0 0 1 1 0 0 0 1 0 1 Z 0 0 0 1 1 1 . . . w Capacity is limited by number of inputs, not complexity 11 1 1 1 1 0 0 1 1 0 1 0 0 0 1 2 4 (2 ) = 64 K !

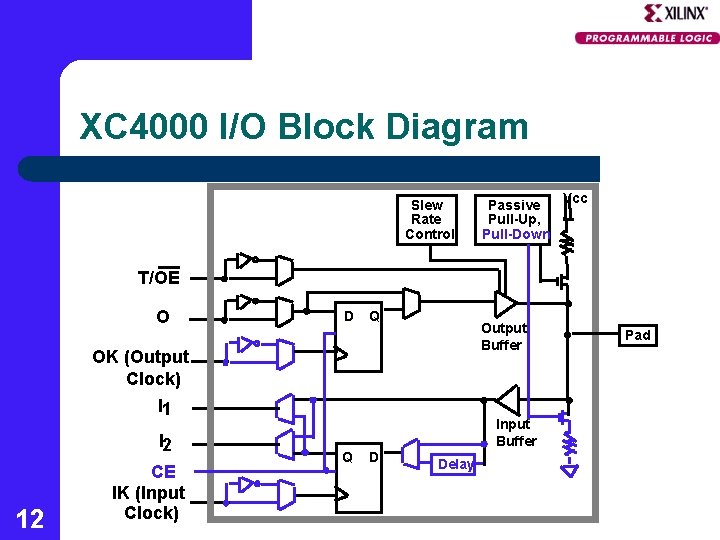

XC 4000 I/O Block Diagram Slew Rate Control Passive Pull-Up, Pull-Down Vcc T/OE O D Q Output Buffer OK (Output Clock) I 1 I 2 12 CE IK (Input Clock) Input Buffer Q D Delay Pad

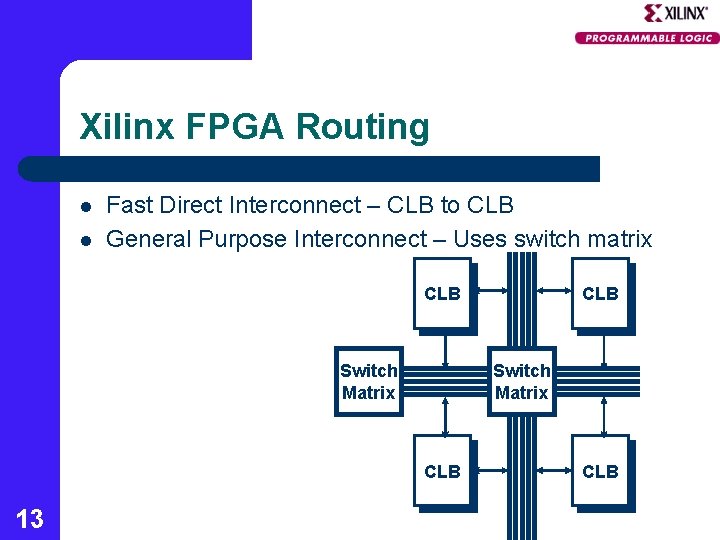

Xilinx FPGA Routing l l Fast Direct Interconnect – CLB to CLB General Purpose Interconnect – Uses switch matrix CLB Switch Matrix CLB 13 CLB

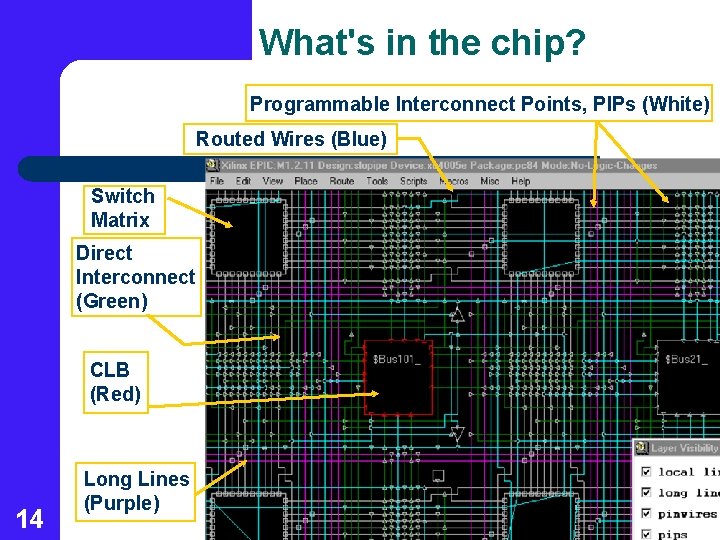

What's in the chip? Programmable Interconnect Points, PIPs (White) Routed Wires (Blue) Switch Matrix Direct Interconnect (Green) CLB (Red) 14 Long Lines (Purple)

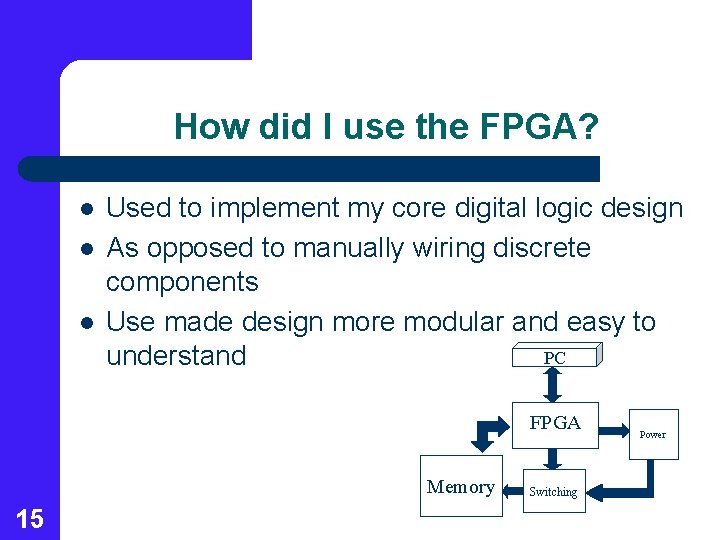

How did I use the FPGA? l l l Used to implement my core digital logic design As opposed to manually wiring discrete components Use made design more modular and easy to PC understand FPGA Memory 15 Switching Power

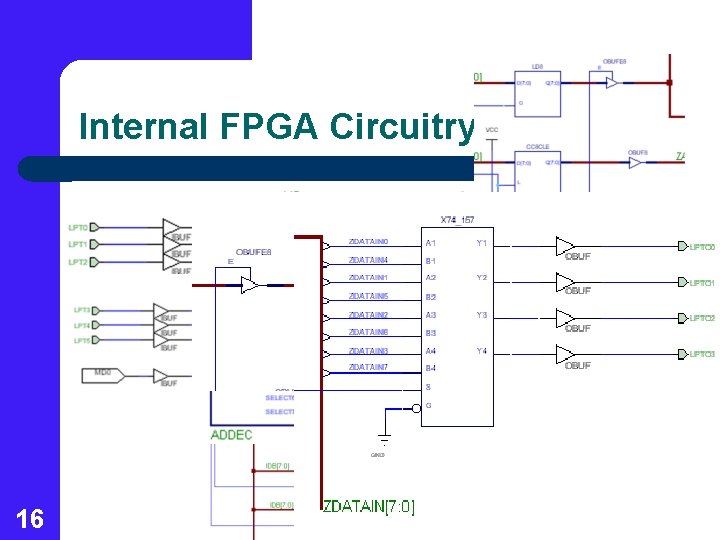

Internal FPGA Circuitry 16

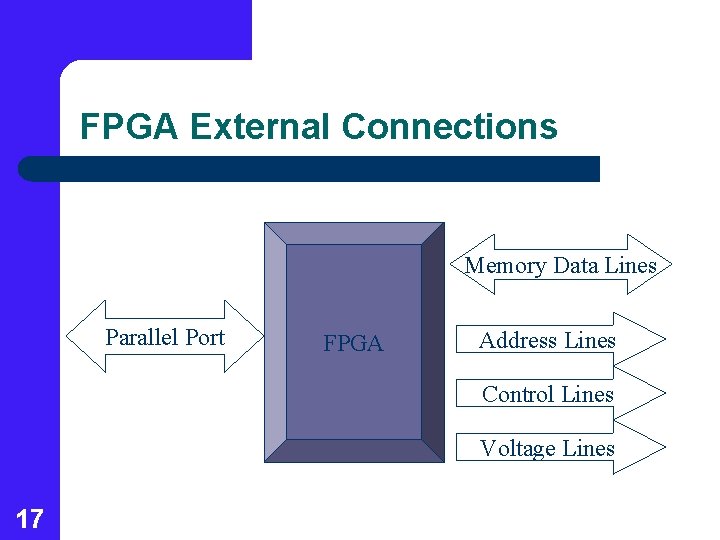

FPGA External Connections Memory Data Lines Parallel Port FPGA Address Lines Control Lines Voltage Lines 17

E/EPROM Considerations l l 18 For most EPROM types there are corresponding EEPROMs of the same size, density, and compatible chip configuration Allows for easier support for both technologies

E/EPROM Considerations l EPROM – Usually require 2 voltage levels : Vcc and Vpp l – Special erasing procedures l l UV Light for example EEPROM – – 19 Vpp usually 12 volts or higher Usually require only 1 voltage level : Vcc Erase/Write procedure often as simple as a static RAM device

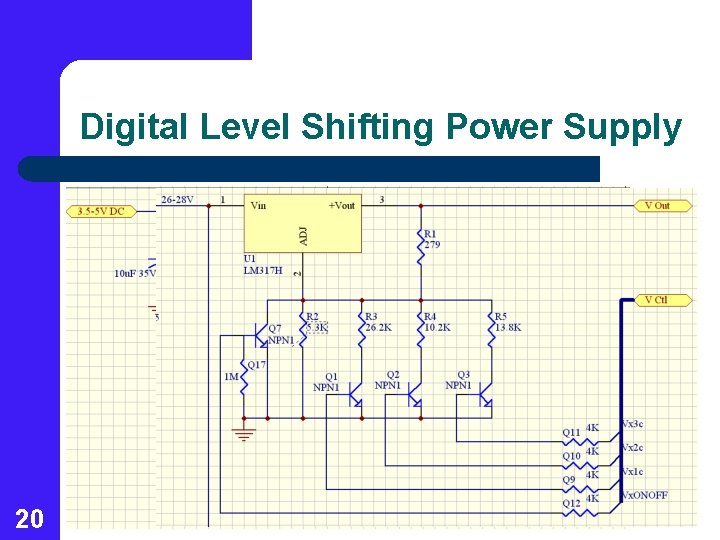

Digital Level Shifting Power Supply Vpp Out 5 V In DC-DC Converter 5 V to 28 V Vpp Level Selector Control Lines Vcc Out Vcc Level Selector 20 Control Lines

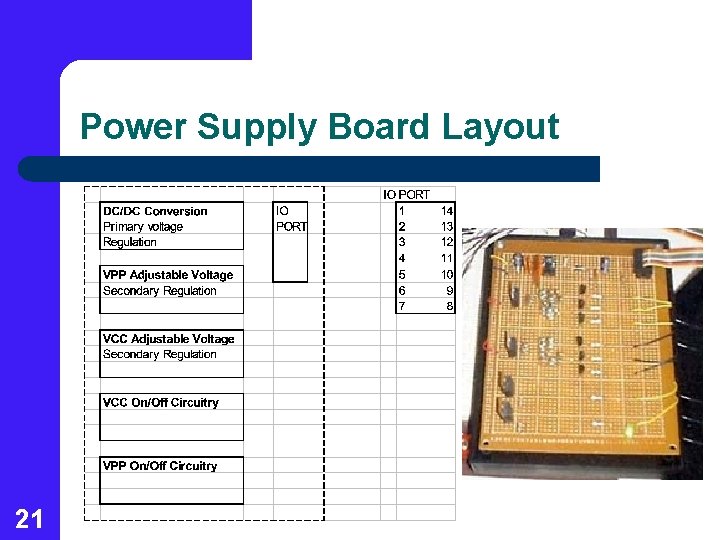

Power Supply Board Layout 21

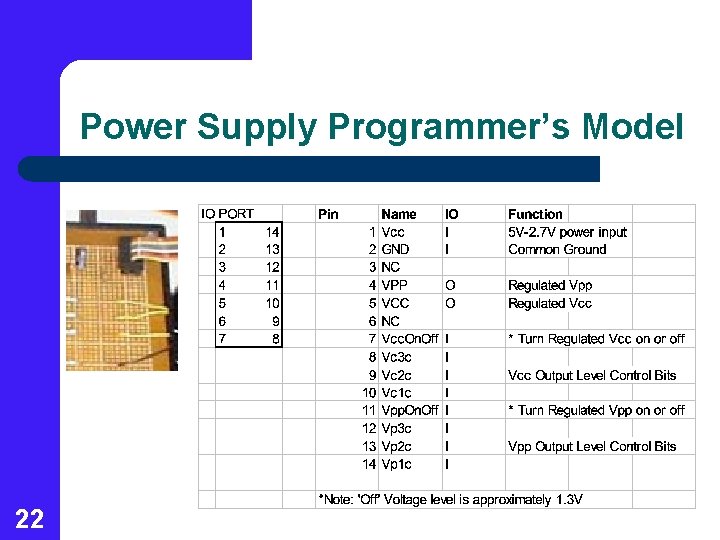

Power Supply Programmer’s Model 22

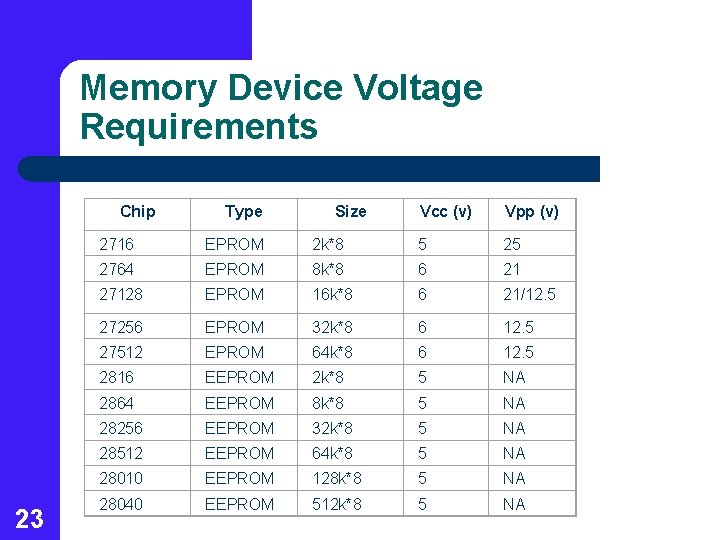

Memory Device Voltage Requirements Chip 23 Type Size Vcc (v) Vpp (v) 2716 EPROM 2 k*8 5 25 2764 EPROM 8 k*8 6 21 27128 EPROM 16 k*8 6 21/12. 5 27256 EPROM 32 k*8 6 12. 5 27512 EPROM 64 k*8 6 12. 5 2816 EEPROM 2 k*8 5 NA 2864 EEPROM 8 k*8 5 NA 28256 EEPROM 32 k*8 5 NA 28512 EEPROM 64 k*8 5 NA 28010 EEPROM 128 k*8 5 NA 28040 EEPROM 512 k*8 5 NA

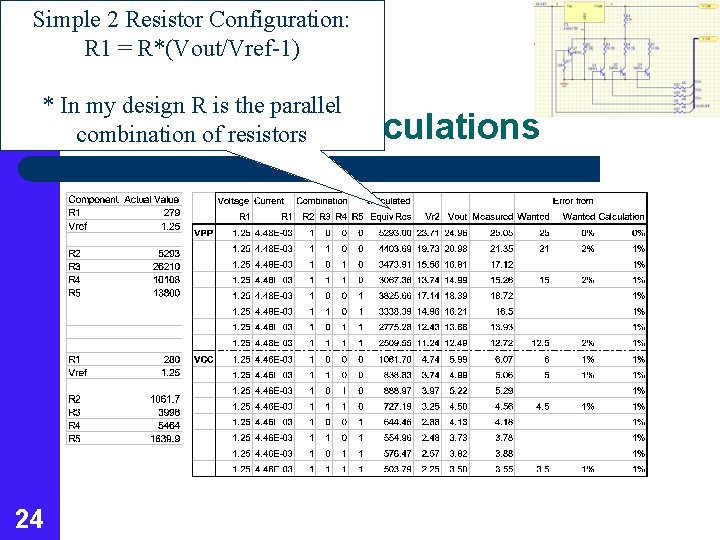

Simple 2 Resistor Configuration: R 1 = R*(Vout/Vref-1) * In my design R is the parallel Power Supply combination of resistors Calculations 24

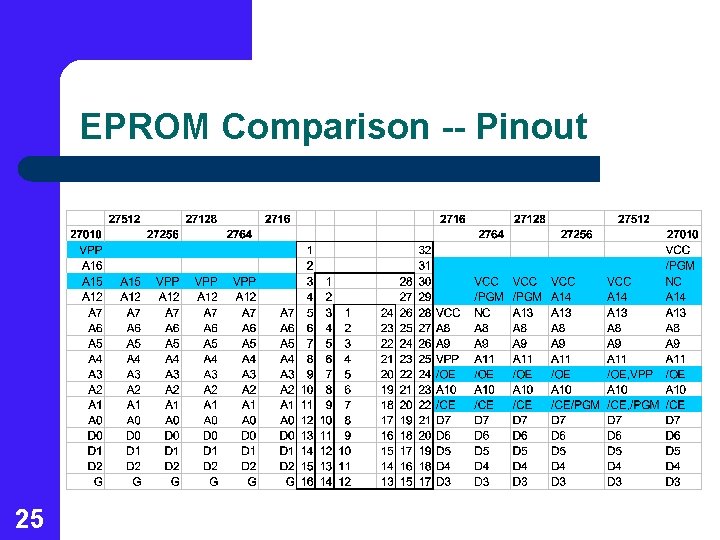

EPROM Comparison -- Pinout 25

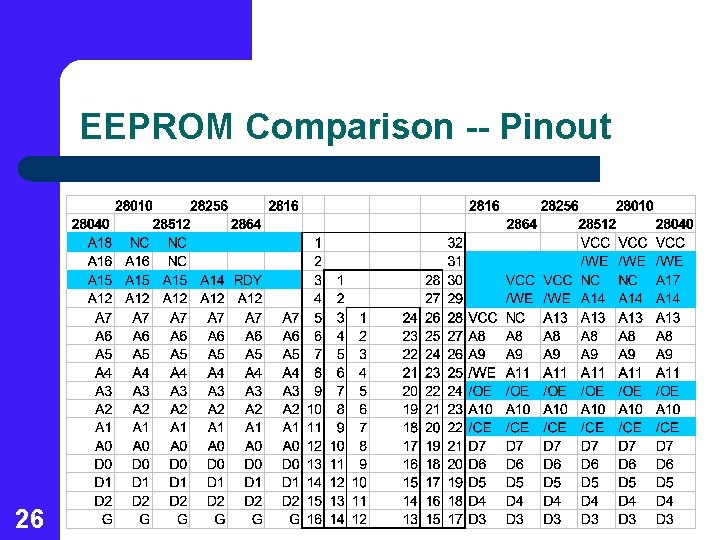

EEPROM Comparison -- Pinout 26

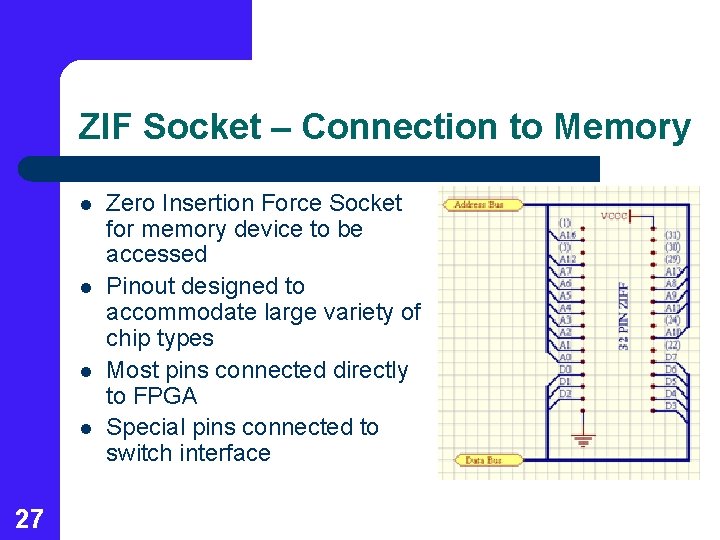

ZIF Socket – Connection to Memory l l 27 Zero Insertion Force Socket for memory device to be accessed Pinout designed to accommodate large variety of chip types Most pins connected directly to FPGA Special pins connected to switch interface

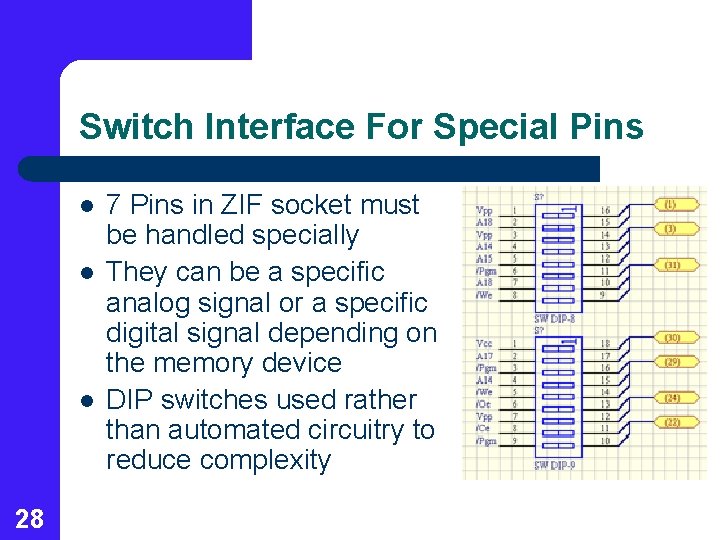

Switch Interface For Special Pins l l l 28 7 Pins in ZIF socket must be handled specially They can be a specific analog signal or a specific digital signal depending on the memory device DIP switches used rather than automated circuitry to reduce complexity

Software Design l Software was created using Visual C++ – l This development environment allowed me to create: – – – 29 Program structure in terms of objects, not just C under C++ software in an object oriented manner an easy to user interface a professional looking final product in minimal time

Software Design l Bottom up design process – Encapsulate hardware interface routines l – Create software API l – Middle level of abstraction Create Application Software l 30 lowest level Top level

Software Design l l l 31 This design process enabled me to test and debug the hardware on its lowest level first. Then I built upon working routines while creating the application software. Hardware interfacing was less of a concern at this point because all routines have already been created and debugged.

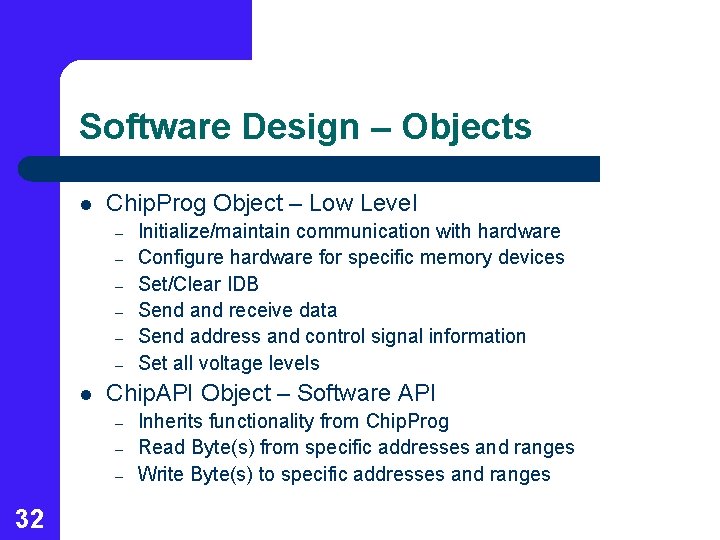

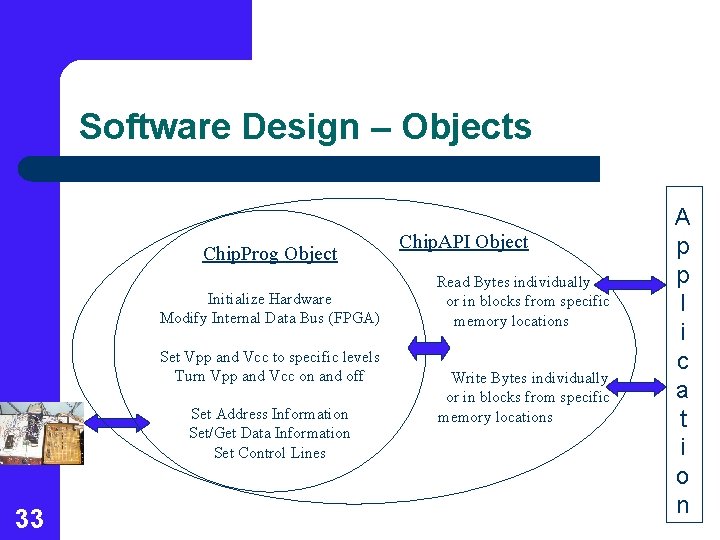

Software Design – Objects l Chip. Prog Object – Low Level – – – l Chip. API Object – Software API – – – 32 Initialize/maintain communication with hardware Configure hardware for specific memory devices Set/Clear IDB Send and receive data Send address and control signal information Set all voltage levels Inherits functionality from Chip. Prog Read Byte(s) from specific addresses and ranges Write Byte(s) to specific addresses and ranges

Software Design – Objects Chip. Prog Object Initialize Hardware Modify Internal Data Bus (FPGA) Set Vpp and Vcc to specific levels Turn Vpp and Vcc on and off Set Address Information Set/Get Data Information Set Control Lines 33 Chip. API Object Read Bytes individually or in blocks from specific memory locations Write Bytes individually or in blocks from specific memory locations A p p l i c a t i o n

Software Design – Hardware Testing 34 l Using the Chip. Prog object as interface to the hardware, I created a simple application to test features of the hardware: l Then I wrote the final application software after all of the basic hardware functions seemed to work properly under software control

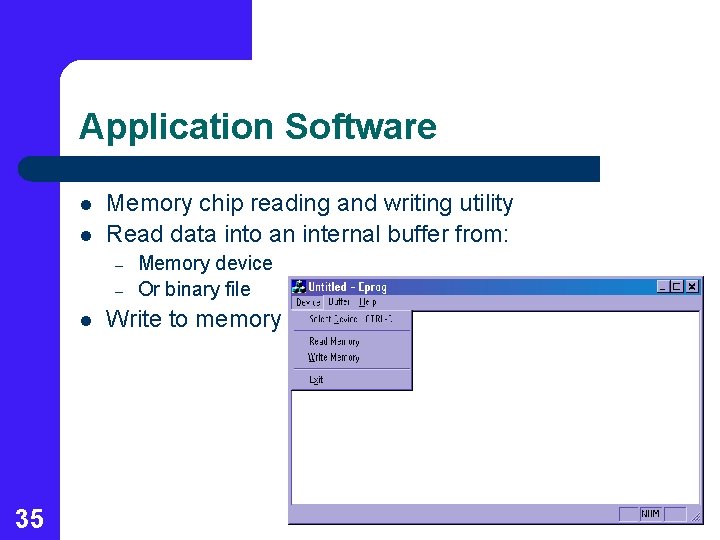

Application Software l l Memory chip reading and writing utility Read data into an internal buffer from: – – l 35 Memory device Or binary file Write to memory

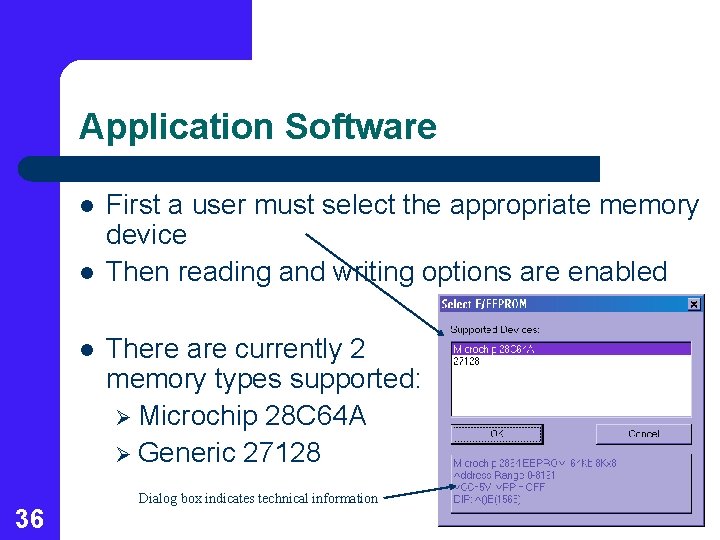

Application Software l l l 36 First a user must select the appropriate memory device Then reading and writing options are enabled There are currently 2 memory types supported: Ø Microchip 28 C 64 A Ø Generic 27128 Dialog box indicates technical information

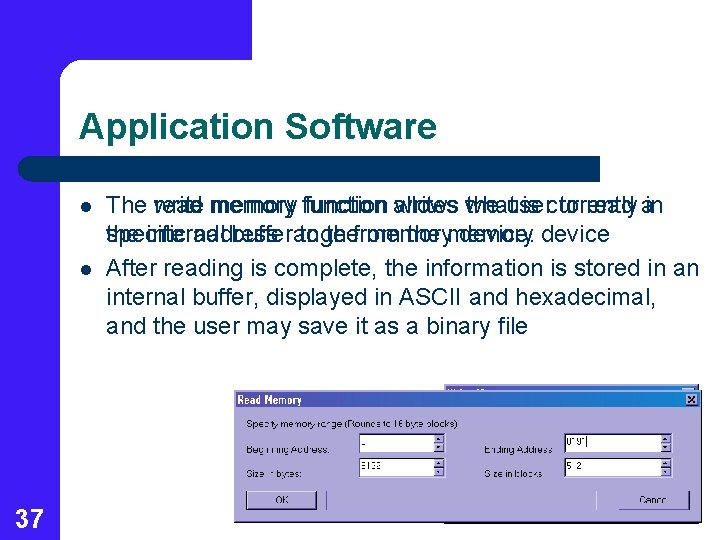

Application Software l l 37 The read write memory function allows writes what the user is currently to read ain the internal specific address bufferrange to thefrom memory the memory device After reading is complete, the information is stored in an internal buffer, displayed in ASCII and hexadecimal, and the user may save it as a binary file

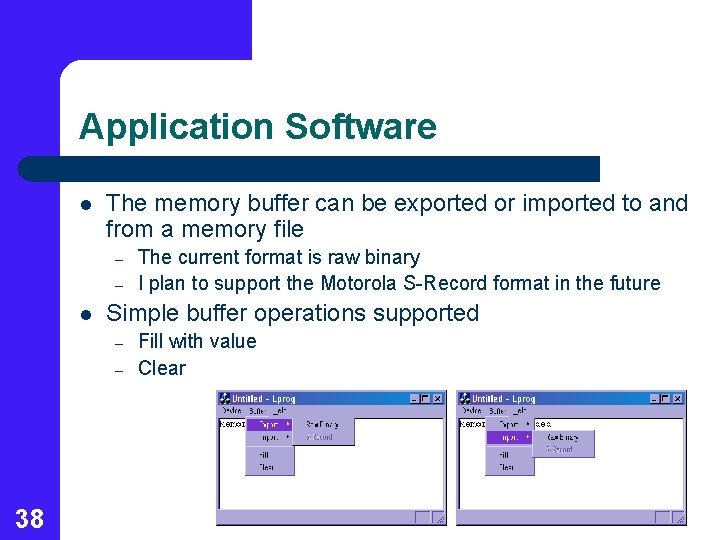

Application Software l The memory buffer can be exported or imported to and from a memory file – – l Simple buffer operations supported – – 38 The current format is raw binary I plan to support the Motorola S-Record format in the future Fill with value Clear

Problems l Insufficient pins on FPGA for all functions – l l Interference from FPGA evaluation board Timing to ms resolution difficult on PC – l Hard to coordinate control signal timing correctly Control related feedback not available – 39 Forced manual solution for switching section Sometimes results in errors during block writes

Possible Improvements l l Use FPGA without evaluation board and more pins Design FPGA logic solely with VHDL – l Abandon limiting idea to use discrete logic chips Utilize a microcontroller – – Accurate timing Better communication with PC l l – l 40 USB More information Intelligent device Remove DIP switches and use automated analog switching solution – Analog MUX

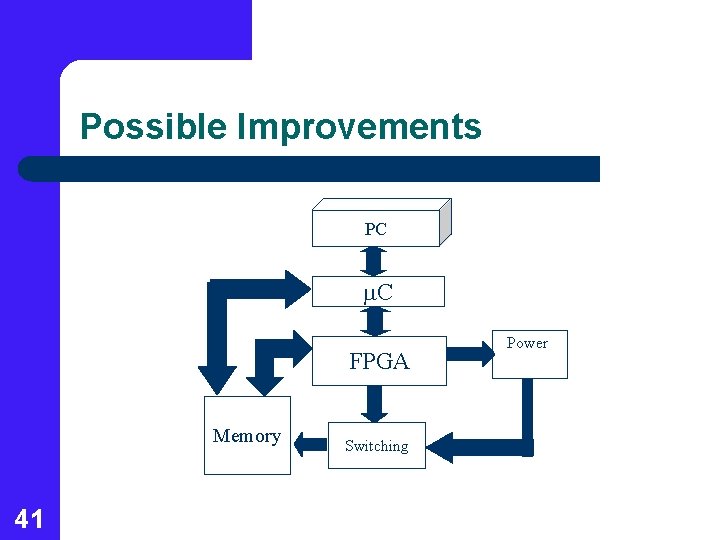

Possible Improvements PC m. C FPGA Memory 41 Switching Power

Conclusions l This project utilized advanced digital logic techniques – – l Implementation of a mixed voltage level system – l 42 Design and debug of FPGA based systems Current industry practice Common requirement in transition to low power systems As well as a mixed analog/digital system

Idea Conclusions l Design process for the hardware was a topdown approach – – 43 System Began with vague requirements and an idea of an end product Gradually broke ideas down into manageable components Implemented/debugged each component separately Combined to create the final hardware system

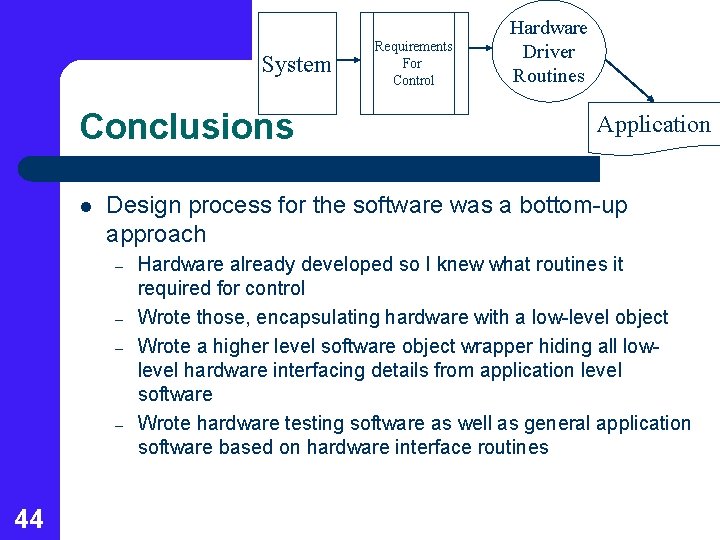

System Conclusions l Application Design process for the software was a bottom-up approach – – 44 Requirements For Control Hardware Driver Routines Hardware already developed so I knew what routines it required for control Wrote those, encapsulating hardware with a low-level object Wrote a higher level software object wrapper hiding all lowlevel hardware interfacing details from application level software Wrote hardware testing software as well as general application software based on hardware interface routines

Special Thanks l Dr. Izadi - Senior Project Advisor – – – l Professor Otis – – 45 Information and help regarding all aspects of FPGA based system design General hardware/software design advice Continued support through all phases of my project Support and advice on microprocessor and microcontroller based system design and interfacing details As well as gave general advice throughout the life of my project

- Slides: 45