Formalne metode u oblikovanju sustava Sveuilite u Zagrebu

Formalne metode u oblikovanju sustava Sveučilište u Zagrebu Fakultet elektrotehnike i računarstva Prof. dr. sc. Nikola Bogunović 1

Što su formalne metode (FM)? n n To su matematički zasnovane tehnike za specificiranje zahtjeva i arhitekture u oblikovanju i razvoju, te za verifikaciju sklopovskih i programskih sustava. Budući da matematički modeli daju preciznu semantiku, uporaba FM je motivirana istim argumentima kao i u drugim inženjerskim disciplinama: matematički zasnovana analiza doprinosi pouzdanosti i robusnosti konačnog proizvoda. n Postoje dokazi da uporaba FM smanjuje cijenu i skraćuje vrijeme stavljanja proizvoda na tržište (engl. time-to-market) n FM nisu zamjena za ispitivanje (testiranje) već su to dva međusobno komplementarna skupa tehnika. 2

Što su formalne metode (FM)? n n U FM usredotočenost je na statičko (simboličko) rasuđivanje o sustavima. Npr. programski produkt se ispituje bez stvarnog izvođenja, a analiza se provodi na izvornom kodu ili na nekom modelu (apstrakciji) izvornog koda. Analiza koja se provodi stvarnim izvođenjem programa naziva se dinamička analiza. To je područje ispitivanja (testiranja) sustava. FM nisu ezoterične metode. U programskom inženjerstvu prevođenje (kompilacija) izvornog koda je također FM, jer se viša razina opisa (apstrakcije) preslikava u nižu razinu. FM koriste alate za rasuđivanje o sustavima (npr. programi su formalni entiteti u alatima). 3

Formalne metode n Pružaju radno okruženje u fazama oblikovanja sustava: n n n specifikaciju sustava (i uvode pojam ispravnosti, korektnosti). oblikovanje (modeliranje) i razvoj sustava verifikaciju ispravnosti: n n n implementacije u odnosu na specifikaciju ekvivalencije različitih implementacija Rasuđivanje je zasnovano na (matematičkoj) logici koja: n n je podložna strojnoj analizi i manipulaciji. omogućuje verifikaciju različitih značajki sustava (uz pretpostavke: dovoljno raspoloživog vremena, posjedovanje vještima i strpljivosti). 4

“Lagane” (engl. Light weight) formalne metode n To je djelomična primjena formalnih metoda n n Pažnja samo na neke značajke sustava n n n Specificiraju se i analiziraju samo dijelovi sustava. Sigurnost, životnost, nepristranost, odsutnost zastoja (engl. dead-lock) i sl. Automatizirano izvođenje (minimizira se interakcije s alatom). Najuspješnija “lagana” tehnika u okviru formalnih metoda: provjera modela (engl. model checking). 5

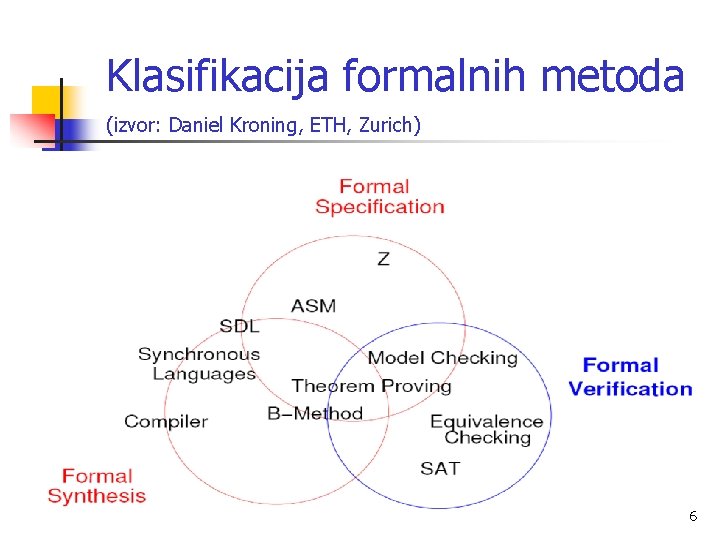

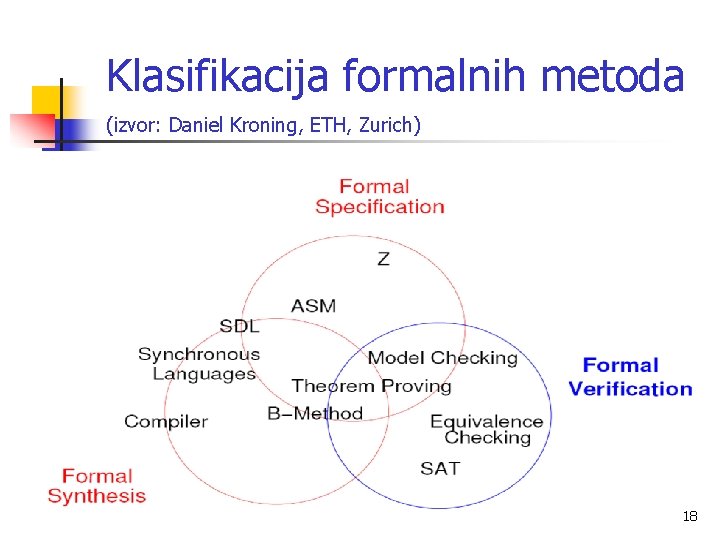

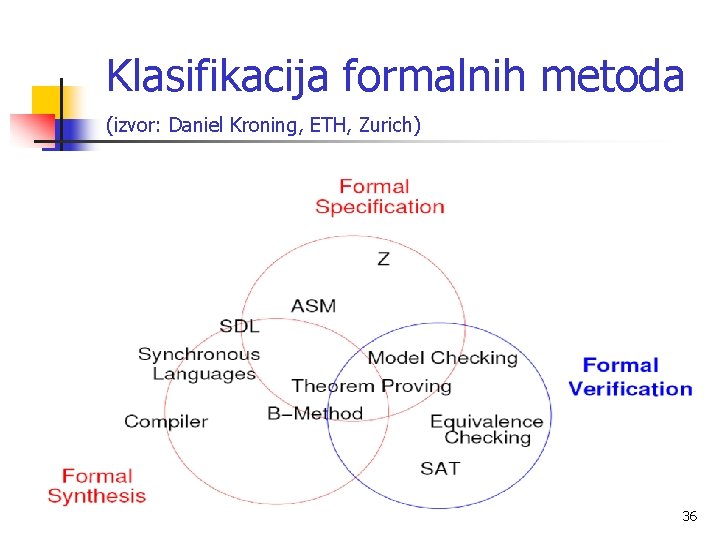

Klasifikacija formalnih metoda (izvor: Daniel Kroning, ETH, Zurich) 6

Formalna specifikacija n Apstrahira nepotrebne implementacijske detalje. n To je matematički model visoke apstrakcijske razine. n Vrlo koristan pristup u početnom oblikovanju. n n Pokazuje nekonzistentne i dvosmislene specifikacije (koje izviru iz analize zahtjeva). Nema dodatnih alata (formalna specifikacija je sama za sebe tehnika). 7

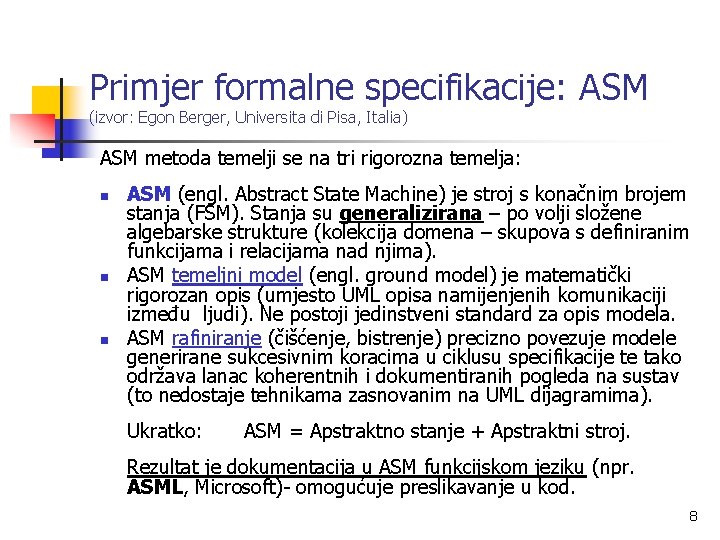

Primjer formalne specifikacije: ASM (izvor: Egon Berger, Universita di Pisa, Italia) ASM metoda temelji se na tri rigorozna temelja: n n n ASM (engl. Abstract State Machine) je stroj s konačnim brojem stanja (FSM). Stanja su generalizirana – po volji složene algebarske strukture (kolekcija domena – skupova s definiranim funkcijama i relacijama nad njima). ASM temeljni model (engl. ground model) je matematički rigorozan opis (umjesto UML opisa namijenjenih komunikaciji između ljudi). Ne postoji jedinstveni standard za opis modela. ASM rafiniranje (čišćenje, bistrenje) precizno povezuje modele generirane sukcesivnim koracima u ciklusu specifikacije te tako održava lanac koherentnih i dokumentiranih pogleda na sustav (to nedostaje tehnikama zasnovanim na UML dijagramima). Ukratko: ASM = Apstraktno stanje + Apstraktni stroj. Rezultat je dokumentacija u ASM funkcijskom jeziku (npr. ASML, Microsoft)- omogućuje preslikavanje u kod. 8

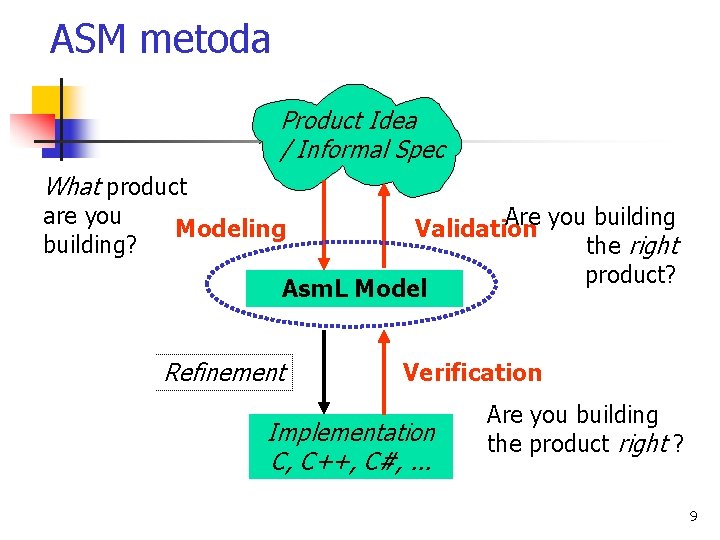

ASM metoda Product Idea / Informal Spec What product are you building? Are you building Validation the right product? Asm. L Modeling Refinement Verification Implementation C, C++, C#, . . . Are you building the product right ? 9

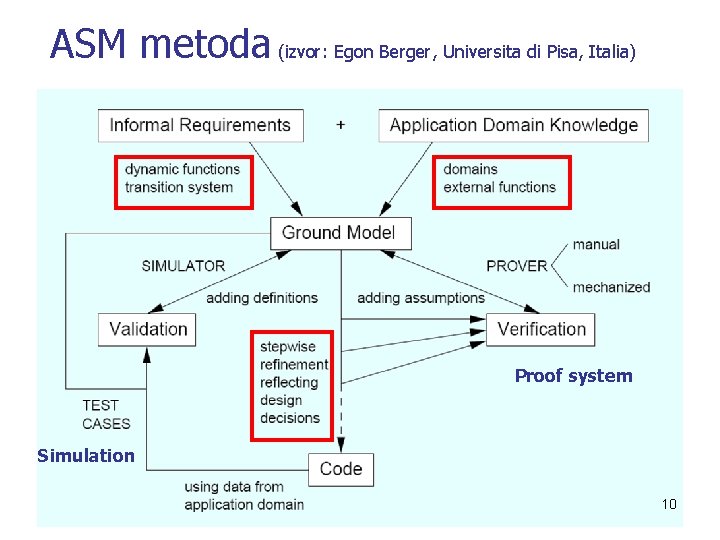

ASM metoda (izvor: Egon Berger, Universita di Pisa, Italia) Proof system Simulation 10

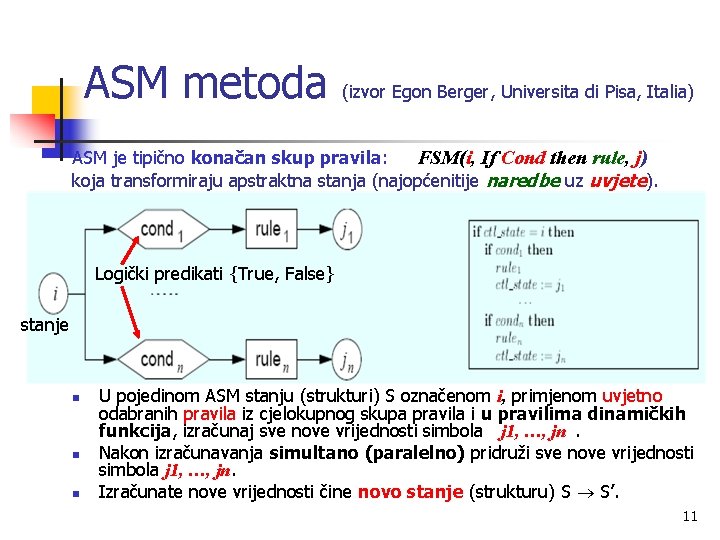

ASM metoda (izvor Egon Berger, Universita di Pisa, Italia) ASM je tipično konačan skup pravila: FSM(i, If Cond then rule, j) koja transformiraju apstraktna stanja (najopćenitije naredbe uz uvjete). Logički predikati {True, False} stanje n n n U pojedinom ASM stanju (strukturi) S označenom i, primjenom uvjetno odabranih pravila iz cjelokupnog skupa pravila i u pravilima dinamičkih funkcija, izračunaj sve nove vrijednosti simbola j 1, …, jn. Nakon izračunavanja simultano (paralelno) pridruži sve nove vrijednosti simbola j 1, …, jn. Izračunate nove vrijednosti čine novo stanje (strukturu) S S’. 11

Primjer formalne specifikacije: Z metoda (čita se “zed”) n n n n Metoda je razvijena na University of Oxford. Temeljena na logici predikata. Z dokument se sastoji iz matematičkih definicija isprepletenih s engleskim tekstom. Z tekst je pisan kao skup struktura - Schema. Započinje osnovnim definicijama i ograničenjima sustava. Nastavlja se opisom akcija sustava. Završava dokazivanjem različitih teorema koji garantiraju konzistentnost definicija. U deklarativni dio Scheme mogu se uključiti imena drugih postojećih Schema (nasljeđivanje). 12

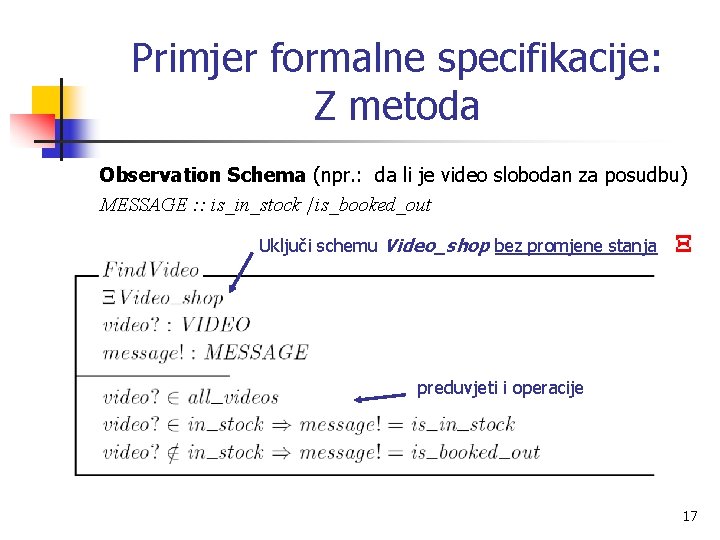

Primjer formalne specifikacije: Z metoda n Tipovi schema: n n State schema – globalne izjave o sustavu. Operation schema - opisuje efekt određenih operacija koje mijenjaju stanje podataka u sustavu. Observation schema – opisuje dohvat informacija (podaci u sustavu se ne mijenjaju). Dozvoljene su sve logičke operacije između schema kao i kvantifikacija (egzistencijska i univerzalna). 13

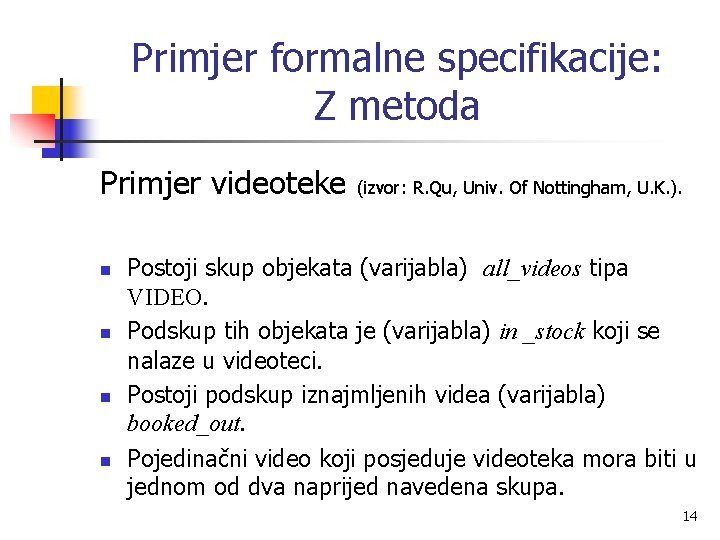

Primjer formalne specifikacije: Z metoda Primjer videoteke n n (izvor: R. Qu, Univ. Of Nottingham, U. K. ). Postoji skup objekata (varijabla) all_videos tipa VIDEO. Podskup tih objekata je (varijabla) in _stock koji se nalaze u videoteci. Postoji podskup iznajmljenih videa (varijabla) booked_out. Pojedinačni video koji posjeduje videoteka mora biti u jednom od dva naprijed navedena skupa. 14

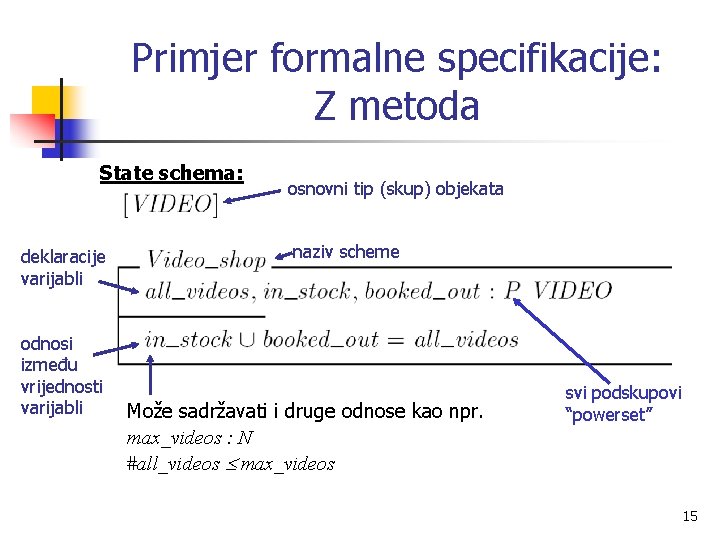

Primjer formalne specifikacije: Z metoda State schema: deklaracije varijabli odnosi između vrijednosti varijabli osnovni tip (skup) objekata naziv scheme Može sadržavati i druge odnose kao npr. max_videos : N #all_videos max_videos svi podskupovi “powerset” 15

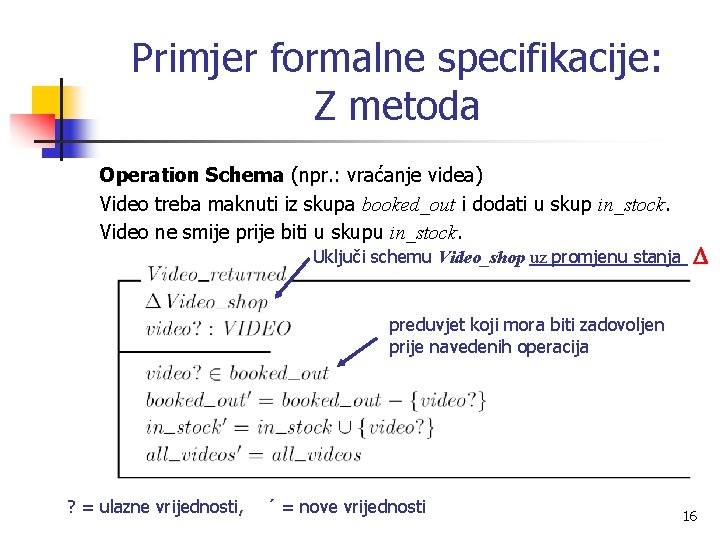

Primjer formalne specifikacije: Z metoda Operation Schema (npr. : vraćanje videa) Video treba maknuti iz skupa booked_out i dodati u skup in_stock. Video ne smije prije biti u skupu in_stock. Uključi schemu Video_shop uz promjenu stanja preduvjet koji mora biti zadovoljen prije navedenih operacija ? = ulazne vrijednosti, ´ = nove vrijednosti 16

Primjer formalne specifikacije: Z metoda Observation Schema (npr. : da li je video slobodan za posudbu) MESSAGE : : is_in_stock is_booked_out Uključi schemu Video_shop bez promjene stanja preduvjeti i operacije 17

Klasifikacija formalnih metoda (izvor: Daniel Kroning, ETH, Zurich) 18

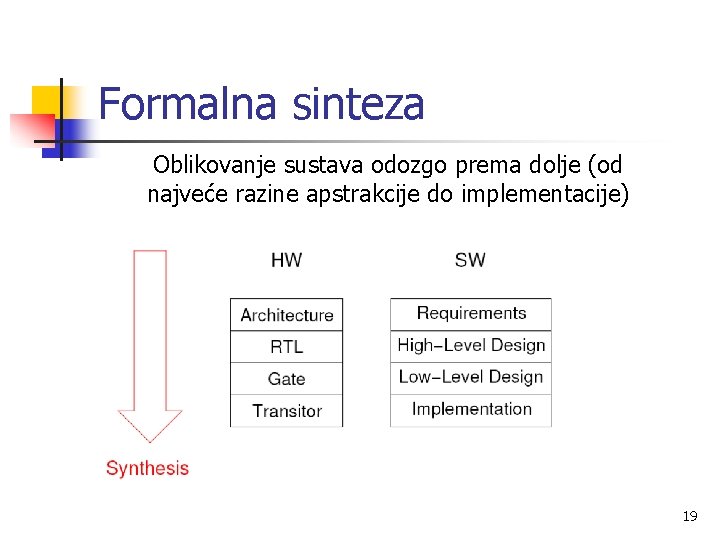

Formalna sinteza Oblikovanje sustava odozgo prema dolje (od najveće razine apstrakcije do implementacije) 19

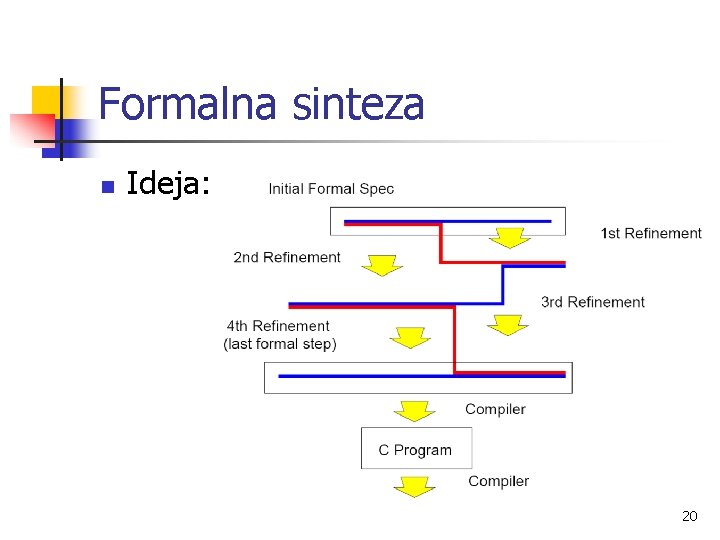

Formalna sinteza n Ideja: 20

Formalna sinteza n Integrira verifikaciju tijekom procesa razvoja produkta. n Najčešće u uporabi pristup oblikovanju odozgo prema dolje uz korake koji detaljiziraju (rafiniraju) proizvod. n Raspodjeljuje verifikacijski posao na male zadatke (princip oblikovanja podijeli pa vladaj). n Unosi promjenu u tradicijski proces oblikovanja uz povećanje cijene razvoja. n Svakom koraku detaljiziranja (rafiniranja) pridružena je određena formalna metoda verifikacije. Napredni verifikacijski algoritmi omogućuju velikim dijelom automatizaciju procesa. 21

Primjer formalne sinteze – SDL (Specification and Description Language) n n Objektno usmjeren formalan jezik definiran od International Telecommunications Union, ITU-T. Primjeren za specifikaciju i sintezu interaktivnih primjenskih sustava za rad u stvarnom vremenu i arhitekturi programskih produkata temeljenoj na implicitnom pozivanju (događajno usmjerena, engl. Event based). Pruža osnovicu za analizu specifikacija s aspekta potpunosti (engl. completeness), ispravnosti (engl. correctness) i konzistencije. Verifikacija je podržana dodatnim alatima. Generiranje primjenskih sustava temeljenih na SDL-u velikim je dijelom računalno potpomognuto (intenzivna uporaba alata). 22

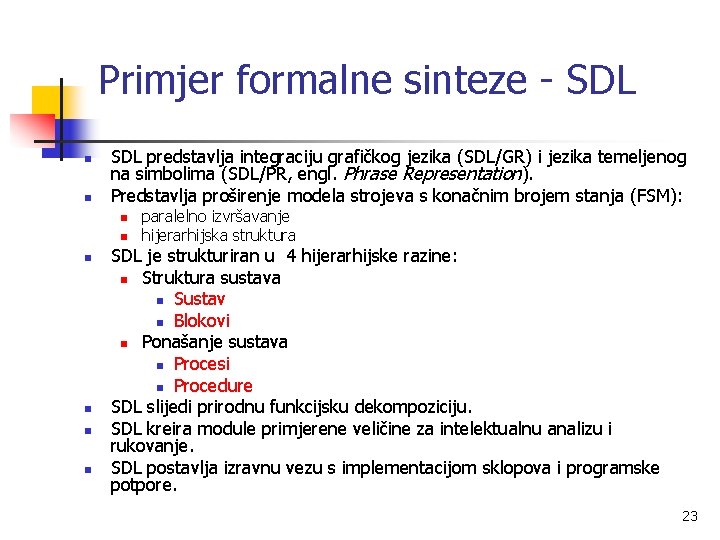

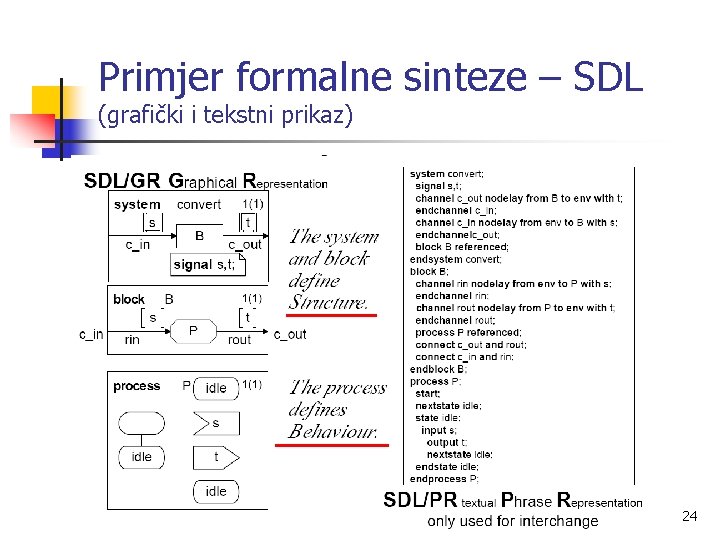

Primjer formalne sinteze - SDL n n SDL predstavlja integraciju grafičkog jezika (SDL/GR) i jezika temeljenog na simbolima (SDL/PR, engl. Phrase Representation). Predstavlja proširenje modela strojeva s konačnim brojem stanja (FSM): n n n paralelno izvršavanje hijerarhijska struktura SDL je strukturiran u 4 hijerarhijske razine: n Struktura sustava n Sustav n Blokovi n Ponašanje sustava n Procesi n Procedure SDL slijedi prirodnu funkcijsku dekompoziciju. SDL kreira module primjerene veličine za intelektualnu analizu i rukovanje. SDL postavlja izravnu vezu s implementacijom sklopova i programske potpore. 23

Primjer formalne sinteze – SDL (grafički i tekstni prikaz) 24

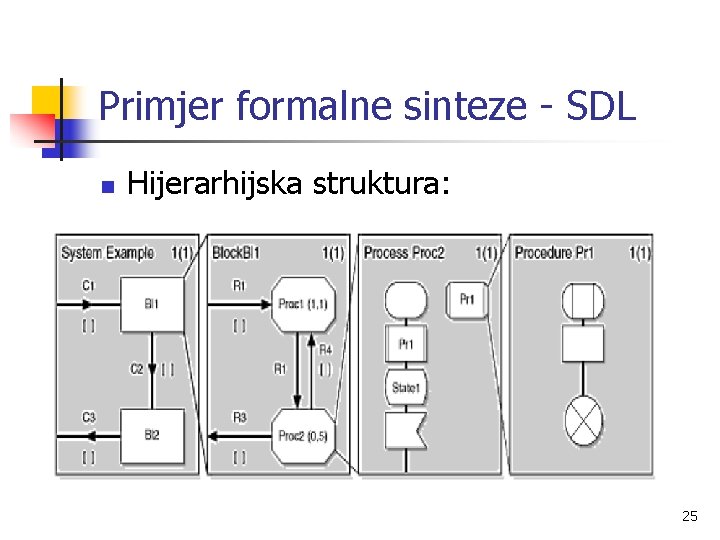

Primjer formalne sinteze - SDL n Hijerarhijska struktura: 25

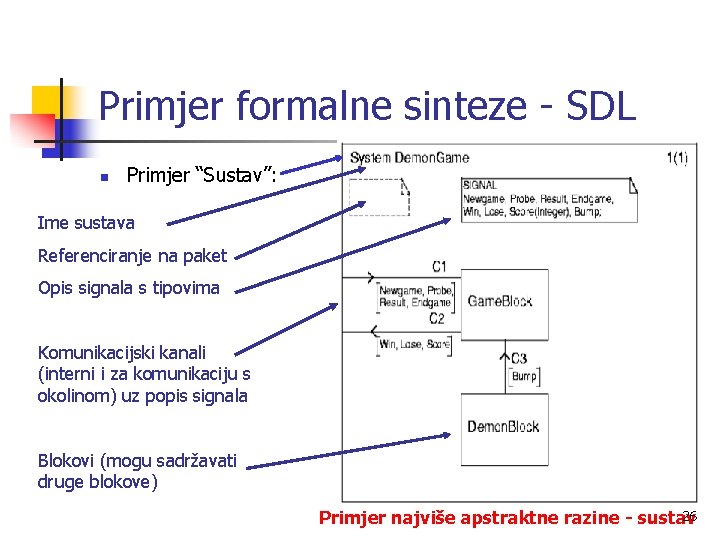

Primjer formalne sinteze - SDL n Primjer “Sustav”: Ime sustava Referenciranje na paket Opis signala s tipovima Komunikacijski kanali (interni i za komunikaciju s okolinom) uz popis signala Blokovi (mogu sadržavati druge blokove) 26 Primjer najviše apstraktne razine - sustav

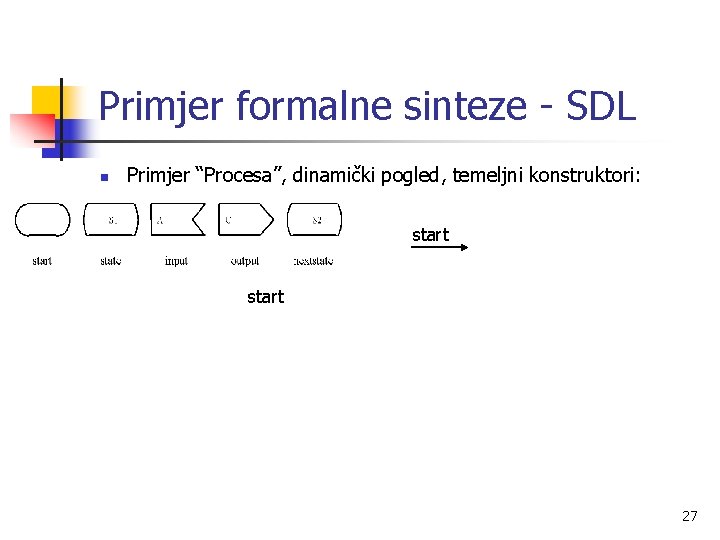

Primjer formalne sinteze - SDL n Primjer “Procesa”, dinamički pogled, temeljni konstruktori: start 27

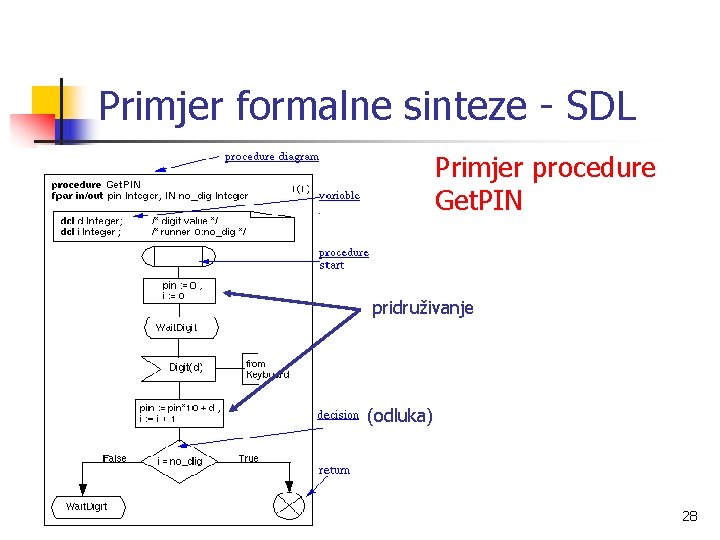

Primjer formalne sinteze - SDL Primjer procedure Get. PIN pridruživanje (odluka) 28

Primjer formalne sinteze – Prevoditelj (engl. compiler), Izvor: A. Artale, Univ. of Bolzano n n n Prevoditelji preslikavaju programe iz jednog jezika (izvorni jezik) u drugi jezik (ciljni jezik). Dodatno, prevoditelju su nužni drugi programi za generiranje strojno izvršnog koda. Interpreteri izvode program bez prethodnog prevođenja. Sekvencijski proces prevođenja: Izvorni program (engl. source code) -> Prevoditelj (engl. Compiler) -> Ciljni asemblerski program -> Asembler -> Relokatibilni strojni kod -> Punjenje/povezivanje (engl. Loader/Linker) -> Apsolutni strojni kod 29

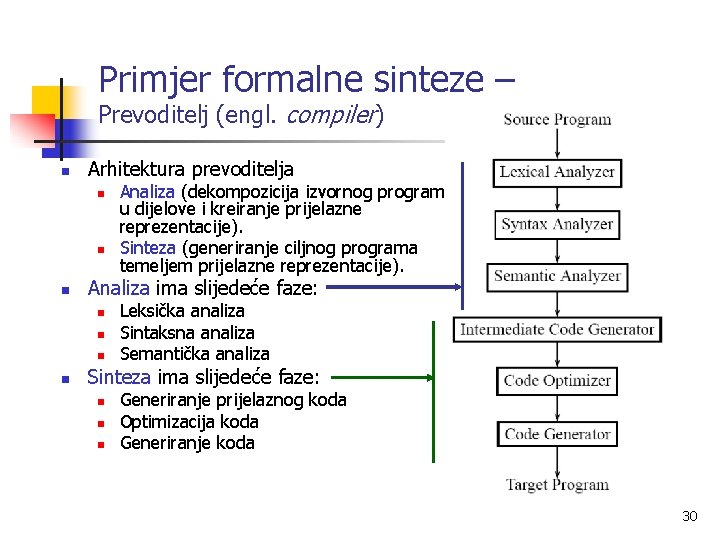

Primjer formalne sinteze – Prevoditelj (engl. compiler) n Arhitektura prevoditelja n n n Analiza ima slijedeće faze: n n Analiza (dekompozicija izvornog programa u dijelove i kreiranje prijelazne reprezentacije). Sinteza (generiranje ciljnog programa temeljem prijelazne reprezentacije). Leksička analiza Sintaksna analiza Semantička analiza Sinteza ima slijedeće faze: n n n Generiranje prijelaznog koda Optimizacija koda Generiranje koda 30

Primjer formalne sinteze – Prevoditelj (engl. compiler) n Leksička analiza i izgradnja tablice simbola n Izdvajanje sekvenci karaktera (leksema) i grupiranje u leksičke značke. (engl. tokens) određenog tipa. Npr: position = initial + rate * 60 ID - Identifier 31

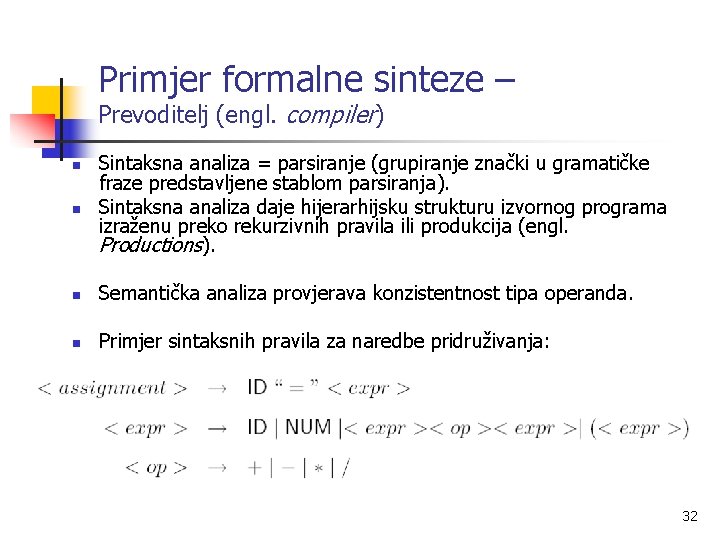

Primjer formalne sinteze – Prevoditelj (engl. compiler) n Sintaksna analiza = parsiranje (grupiranje znački u gramatičke fraze predstavljene stablom parsiranja). Sintaksna analiza daje hijerarhijsku strukturu izvornog programa izraženu preko rekurzivnih pravila ili produkcija (engl. Productions). n Semantička analiza provjerava konzistentnost tipa operanda. n Primjer sintaksnih pravila za naredbe pridruživanja: n 32

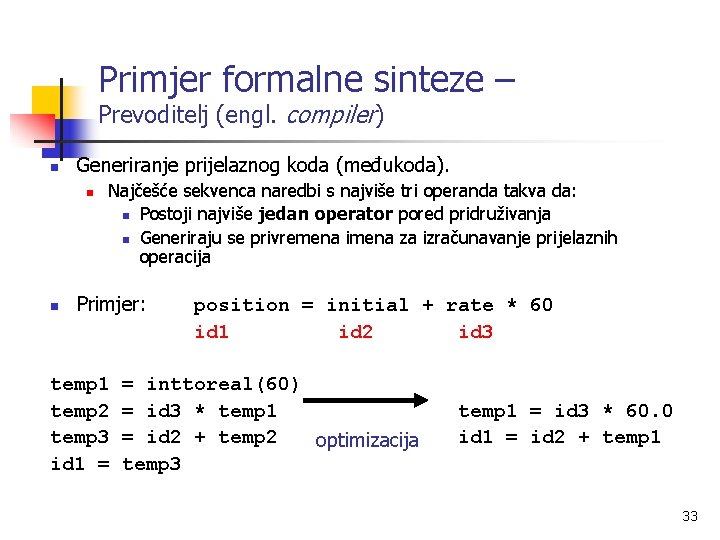

Primjer formalne sinteze – Prevoditelj (engl. compiler) n Generiranje prijelaznog koda (međukoda). n n Najčešće sekvenca naredbi s najviše tri operanda takva da: n Postoji najviše jedan operator pored pridruživanja n Generiraju se privremena imena za izračunavanje prijelaznih operacija Primjer: temp 1 temp 2 temp 3 id 1 = position = initial + rate * 60 id 1 id 2 id 3 = inttoreal(60) = id 3 * temp 1 = id 2 + temp 2 optimizacija temp 3 temp 1 = id 3 * 60. 0 id 1 = id 2 + temp 1 33

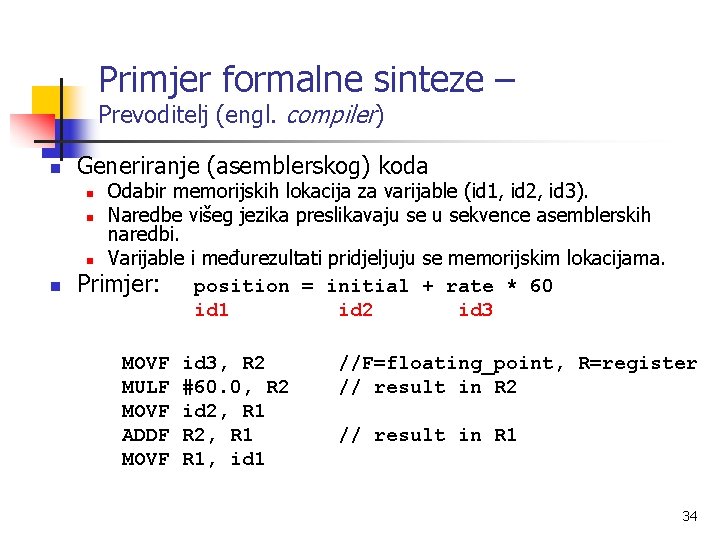

Primjer formalne sinteze – Prevoditelj (engl. compiler) n Generiranje (asemblerskog) koda Odabir memorijskih lokacija za varijable (id 1, id 2, id 3). n Naredbe višeg jezika preslikavaju sekvence asemblerskih naredbi. n Varijable i međurezultati pridjeljuju se memorijskim lokacijama. Primjer: position = initial + rate * 60 id 1 id 2 id 3 n n MOVF MULF MOVF ADDF MOVF id 3, R 2 #60. 0, R 2 id 2, R 1 R 1, id 1 //F=floating_point, R=register // result in R 2 // result in R 1 34

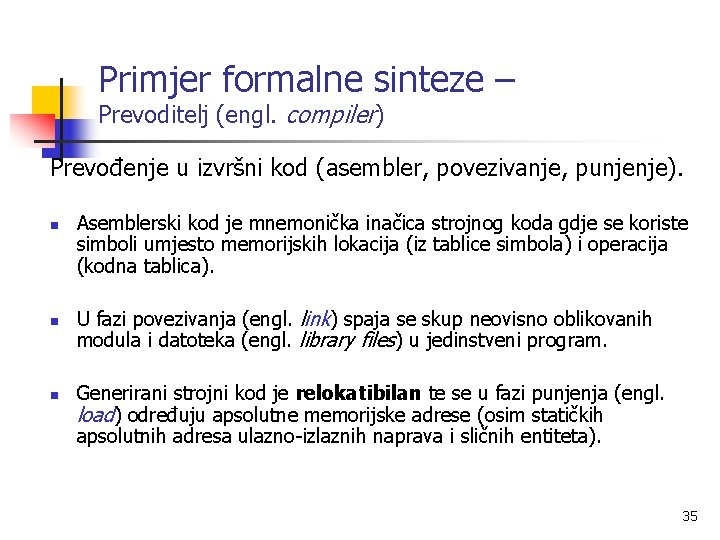

Primjer formalne sinteze – Prevoditelj (engl. compiler) Prevođenje u izvršni kod (asembler, povezivanje, punjenje). n n n Asemblerski kod je mnemonička inačica strojnog koda gdje se koriste simboli umjesto memorijskih lokacija (iz tablice simbola) i operacija (kodna tablica). U fazi povezivanja (engl. link) spaja se skup neovisno oblikovanih modula i datoteka (engl. library files) u jedinstveni program. Generirani strojni kod je relokatibilan te se u fazi punjenja (engl. load) određuju apsolutne memorijske adrese (osim statičkih apsolutnih adresa ulazno-izlaznih naprava i sličnih entiteta). 35

Klasifikacija formalnih metoda (izvor: Daniel Kroning, ETH, Zurich) 36

Formalna verifikacija - FV n n "Debugging": poznato je da postoji "bug" (npr. kao rezultat testiranja) ali nije poznato gdje se točno nalazi. “Program testing can be used to show the presence of bugs, but never to show their absence. ” [Dijkstra, 1972] n Verifikacija: nadamo se da "bug" ne postoji (nije nam poznato) ali želimo biti sigurni. 37

Formalna verifikacija - FV Metode formalne verifikacije Provjera ekvivalentnosti (engl. Equivalence checking): Uspoređuje novo oblikovani model ili implementaciju i izvorni model ili implementaciju. Provjera modela (engl. Model checking): Provjerava da li model implementacije zadovoljava zadano obilježje. Dokazivanje teorema (engl. Theorem proving): Provjerava u nekom logičkom formalizmu da li je implementacija logička posljedica specifikacije. Provjera tvrdnje (engl. Assertion-Based Verification): Provjerava se da neki specifičan uvjet mora uvijek bit zadovoljen. 38

Formalna verifikacija - FV FV metode mogu biti: n Vrlo lagane (engl. very light weight) n n Srednje teške (engl. medium weight) n n n Neispravne (engl. unsound) i nekompletne (engl. incomplete). Dokazivanje obilježja naivnim pretraživanjem. Jednostavna obilježja, efikasna tehnika i lagana za uporabu. Ispravne ali nekompletne. Analiza preko izračunavanja čvrste točke (engl. fixed point), provjera tipova (invarijanti). Teške (engl. heavy weight) n n n Ispravne i kompletne. Verifikacija dokazivanjem logičkih teorema. Složena obilježja sustava, veliki zahtjevi na resurse, teške za uporabu. 39

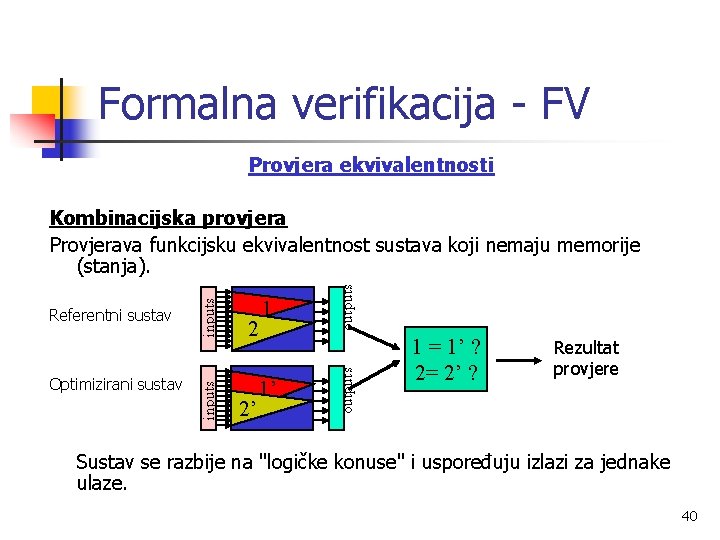

Formalna verifikacija - FV Provjera ekvivalentnosti 2’ 1’ outputs 2 1 outputs Optimizirani sustav inputs Referentni sustav inputs Kombinacijska provjera Provjerava funkcijsku ekvivalentnost sustava koji nemaju memorije (stanja). 1 = 1’ ? 2= 2’ ? Rezultat provjere Sustav se razbije na "logičke konuse" i uspoređuju izlazi za jednake ulaze. 40

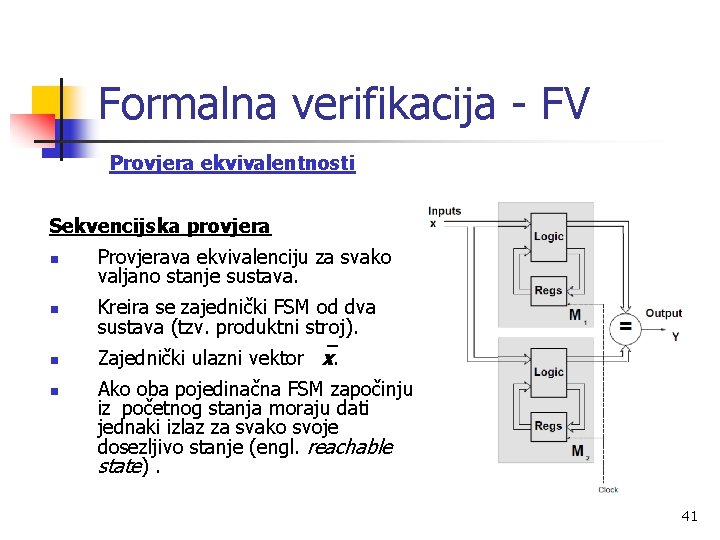

Formalna verifikacija - FV Provjera ekvivalentnosti Sekvencijska provjera n Provjerava ekvivalenciju za svako valjano stanje sustava. n Kreira se zajednički FSM od dva sustava (tzv. produktni stroj). n Zajednički ulazni vektor x. n Ako oba pojedinačna FSM započinju iz početnog stanja moraju dati jednaki izlaz za svako svoje dosezljivo stanje (engl. reachable state). 41

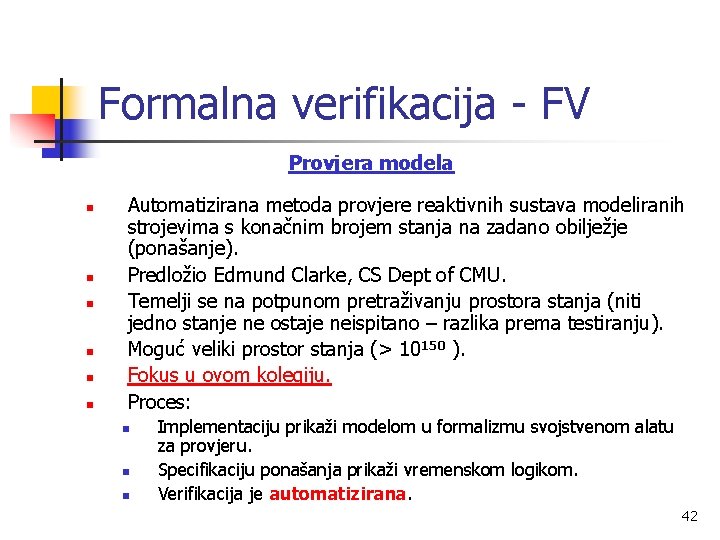

Formalna verifikacija - FV Provjera modela n n n Automatizirana metoda provjere reaktivnih sustava modeliranih strojevima s konačnim brojem stanja na zadano obilježje (ponašanje). Predložio Edmund Clarke, CS Dept of CMU. Temelji se na potpunom pretraživanju prostora stanja (niti jedno stanje ne ostaje neispitano – razlika prema testiranju). Moguć veliki prostor stanja (> 10150 ). Fokus u ovom kolegiju. Proces: n n n Implementaciju prikaži modelom u formalizmu svojstvenom alatu za provjeru. Specifikaciju ponašanja prikaži vremenskom logikom. Verifikacija je automatizirana. 42

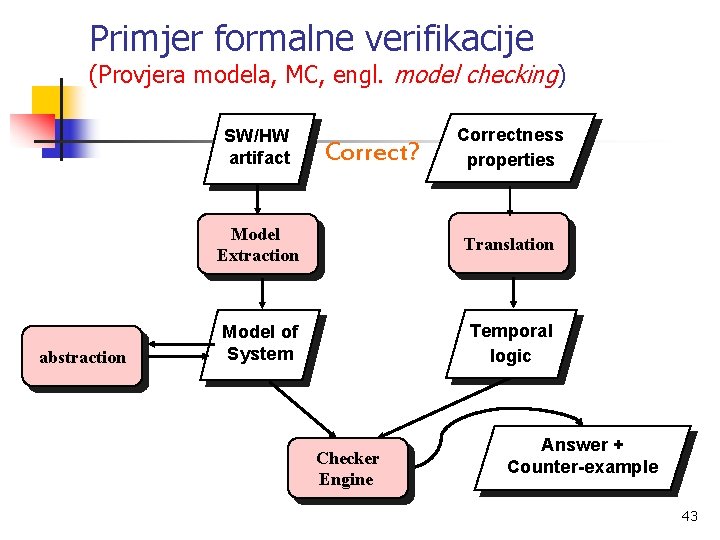

Primjer formalne verifikacije (Provjera modela, MC, engl. model checking) SW/HW artifact abstraction Correct? Correctness properties Model Extraction Translation Model of System Temporal logic Checker Engine Answer + Counter-example 43

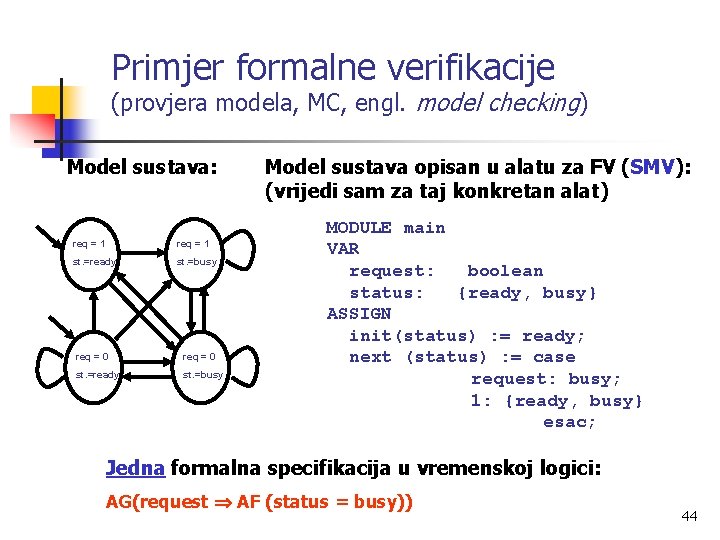

Primjer formalne verifikacije (provjera modela, MC, engl. model checking) Model sustava: req = 1 st. =ready st. =busy req = 0 st. =ready st. =busy Model sustava opisan u alatu za FV (SMV): (vrijedi sam za taj konkretan alat) MODULE main VAR request: boolean status: {ready, busy} ASSIGN init(status) : = ready; next (status) : = case request: busy; 1: {ready, busy} esac; Jedna formalna specifikacija u vremenskoj logici: AG(request AF (status = busy)) 44

Primjer formalne verifikacije (provjera modela, MC, engl. model checking) 2007 Turing Award Winners Announced for their groundbreaking work on Model Checking Edmund M. Clarke, E. Allen Emerson, and Joseph Sifakis are the recipients of the 2007 A. M. Turing Award for their work on an automated method for finding design errors in computer hardware and software. The method, called Model Checking, is the most widely used technique for detecting and diagnosing errors in complex hardware and software design. It has helped to improve the reliability of complex computer chips, systems and networks. 45

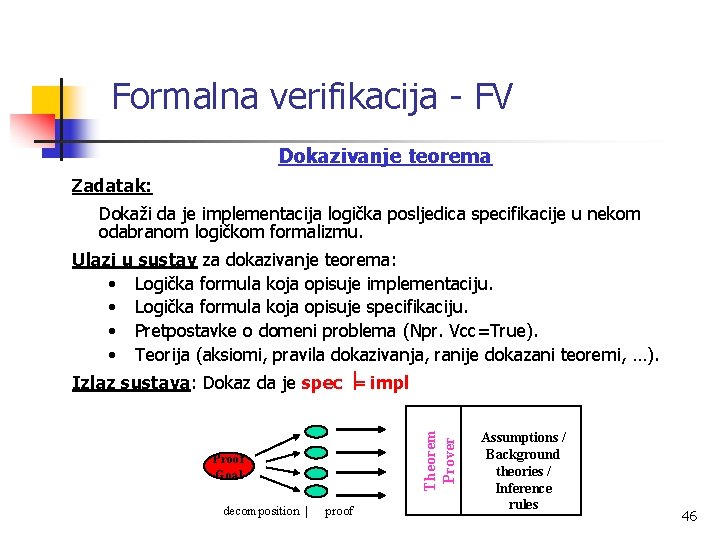

Formalna verifikacija - FV Dokazivanje teorema Zadatak: Dokaži da je implementacija logička posljedica specifikacije u nekom odabranom logičkom formalizmu. Ulazi u sustav za dokazivanje teorema: • Logička formula koja opisuje implementaciju. • Logička formula koja opisuje specifikaciju. • Pretpostavke o domeni problema (Npr. Vcc=True). • Teorija (aksiomi, pravila dokazivanja, ranije dokazani teoremi, …). Theorem Prover Izlaz sustava: Dokaz da je spec impl Proof Goal decomposition | proof Assumptions / Background theories / Inference rules 46

Formalna verifikacija - FV Dokazivanje teorema • Metodu nije jednostavno primijeniti u industriji jer većina inženjera nema znanja o formalnoj matematičkoj logici. • Automatizacija je ograničena, postupak traži ručno vođenje. • Potrebno duboko poznavanje alata za verifikaciju. Primjer: Predikatna logika u verifikaciji programa dokazivanjem teorema: Stanje programa: PSTATE(tekuća_naredba, lista_varijabli) Svaka naredba se mora preslikati u logiku. Npr ASSIGN: ASSIGN(xinstr, zassignto, wexpr, yinstr) xinstr – tekuća naredba, zassignto – varijabla u koju se upisuje, wexpr – izraz evaluacije prije zapisivanja, yinstr – slijedeća naredba Pravila, npr. "Program u stanju 1 naredbom ASSIGN prelazi u stanje 2": (PSTATE_1 ASSIGN) PSTATE_2 47

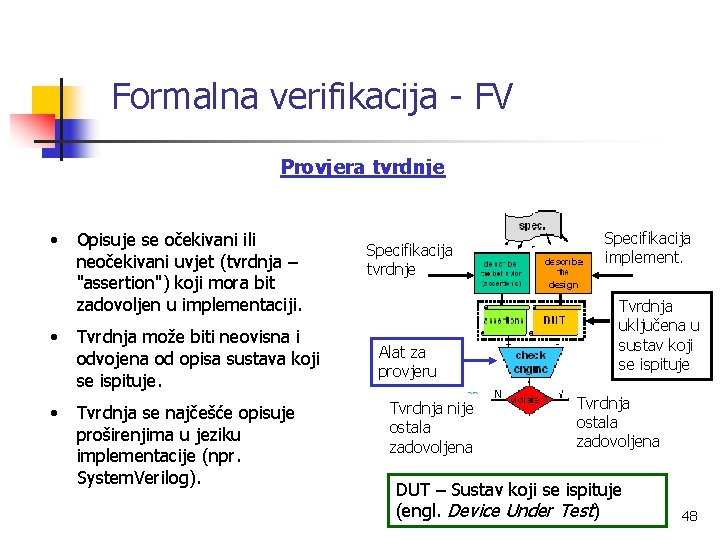

Formalna verifikacija - FV Provjera tvrdnje • Opisuje se očekivani ili neočekivani uvjet (tvrdnja – "assertion") koji mora bit zadovoljen u implementaciji. • Tvrdnja može biti neovisna i odvojena od opisa sustava koji se ispituje. • Tvrdnja se najčešće opisuje proširenjima u jeziku implementacije (npr. System. Verilog). Specifikacija tvrdnje Alat za provjeru Tvrdnja nije ostala zadovoljena Specifikacija implement. Tvrdnja uključena u sustav koji se ispituje Tvrdnja ostala zadovoljena DUT – Sustav koji se ispituje (engl. Device Under Test) 48

Zaključci o formalnim metodama (FM) - 1 n Pojam ispravnosti (engl. correctness) je temeljni intelektualni izazov u industriji složenih sklopovskih i programskih proizvoda. n Verifikacija je rigorozna (matematički utemeljena) demonstracija ispravnosti. n Dok je ručna verifikacija dostatna za male kritične sustave, složeni sustavi traže automatizirane postupke FV. n Automatizirani postupci FV počivaju na skupu efikasnih alata (laganih za primjenu i brzih u donošenju odluke). n Alati za FV potiču još brži razvitak gospodarstva temeljenog na složenim sklopovskim i programskim produktima. n FM trebaju biti ključna inženjerska vještina u računarstvu koja povećava kakvoću produkta i istovremeno smanjuje vrijeme stavljanja proizvoda na tržište (“time to market”), te se mora uključiti u obrazovanje računarstva i elektrotehnike. 49

Zaključci o formalnim metodama (FM) - 2 Ekvivalentni predmeti na nekim drugim sveučilištima: n n n n n ETH, Zurich: Formal verification University of Cambridge, UK: Specification and Verification Charles University in Prague, CZ: Behavior Models and Verification Technische Universitat Munchen: Model Checking MIT: Lightweight Formal Methods Stanford University: Formal Methods for Concurrent and Reactive Systems Berkeley: Model Checking – Computer Aided Verification CMU: Introduction to Model Checking Vanderbilt University: Automated Verification University of Toronto: Formal Methods of Software Design 50

Zaključci o formalnim metodama (FM) - 3 Nastavne cjeline u okviru predmeta “Formalne metode u oblikovanju sustava” na FER-u: n n n Teorijske osnovice (formalna logika, vremenska logika, provjera modela). Formalna verifikacija sklopovlja provjerom modela (Verilog + VIS + vremenska logika). Formalna verifikacija programskih dijelova provjerom modela (Nu. SMV + vremenska logika). Formalna verifikacija komunikacijskih protokola provjerom modela (Promela + SPIN + vremenska logika). Strukture podataka i algoritmi u formalnoj verifikaciji sustava. 51

- Slides: 51