Focus sur les dveloppements lectroniques numriques LLRF pour

- Slides: 15

Focus sur les développements électroniques numériques LLRF pour le RFQ de MYRRHA Multi-purpose h. Ybrid Research Reactor for High-tech Applications S. Berthelot et J-F Yaniche pour l’équipe projet MYRTE task 2. 3 Unité mixte de recherche CNRS-IN 2 P 3 Université Paris-Sud 11 91406 Orsay cedex Tél. : +33 1 69 15 73 40 Fax : +33 1 69 15 64 70 http: //ipnweb. in 2 p 3. fr Équipe (IPNO Électronique) : C. Joly Resp. projet + RF A. Escalda (Electronic CAD) J. Lesrel (RF) M. Pereira (Electronic Integration) Journées VLSI 2018 S. Berthelot J-F Yaniche T. Le Ster (FPGA & VHDL) W. Sarlin (EPICS) 1

Sommaire • Présentation du contexte : le Projet MYRRHA • Le RFQ et ses contraintes • Le système d’asservissements Low Level Radio Frequency • Les cartes numériques utilisées • Les tests en cours • Le futur Journées VLSI 2018 S. Berthelot J-F Yaniche 2

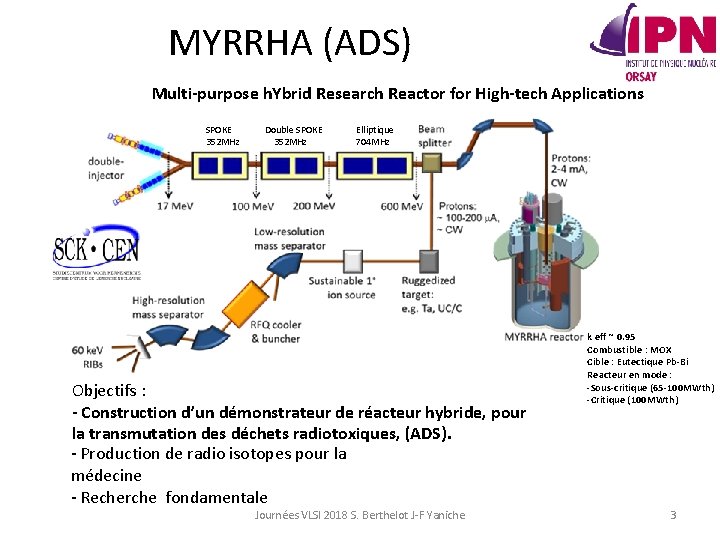

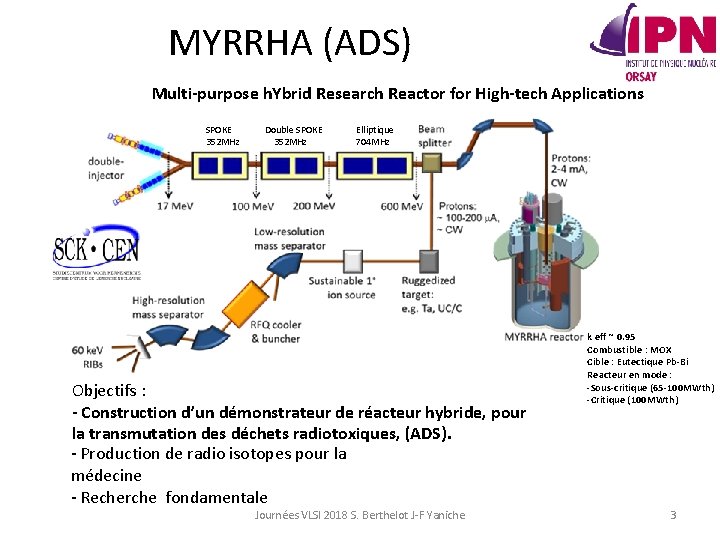

MYRRHA (ADS) Multi-purpose h. Ybrid Research Reactor for High-tech Applications SPOKE 352 MHz Double SPOKE 352 MHz Elliptique 704 MHz Objectifs : - Construction d’un démonstrateur de réacteur hybride, pour la transmutation des déchets radiotoxiques, (ADS). - Production de radio isotopes pour la médecine - Recherche fondamentale Journées VLSI 2018 S. Berthelot J-F Yaniche k eff ~ 0. 95 Combustible : MOX Cible : Eutectique Pb-Bi Reacteur en mode : -Sous-critique (65 -100 MWth) -Critique (100 MWth) 3

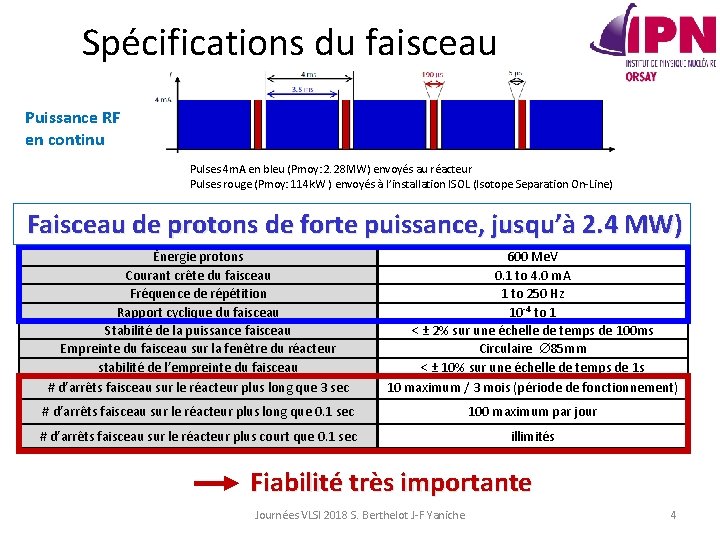

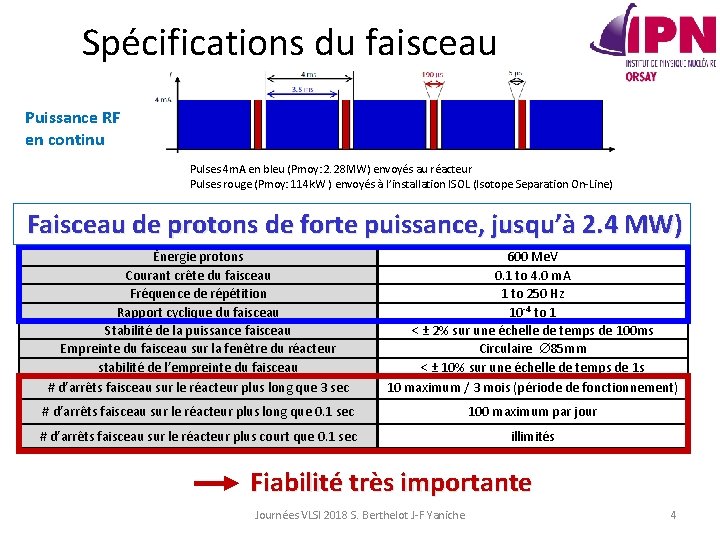

Spécifications du faisceau Puissance RF en continu Pulses 4 m. A en bleu (Pmoy: 2. 28 MW) envoyés au réacteur Pulses rouge (Pmoy: 114 k. W ) envoyés à l’installation ISOL (Isotope Separation On-Line) Faisceau de protons de forte puissance, jusqu’à 2. 4 MW) Énergie protons Courant crête du faisceau Fréquence de répétition Rapport cyclique du faisceau Stabilité de la puissance faisceau Empreinte du faisceau sur la fenêtre du réacteur stabilité de l’empreinte du faisceau # d’arrêts faisceau sur le réacteur plus long que 3 sec 600 Me. V 0. 1 to 4. 0 m. A 1 to 250 Hz 10 -4 to 1 < ± 2% sur une échelle de temps de 100 ms Circulaire 85 mm < ± 10% sur une échelle de temps de 1 s 10 maximum / 3 mois (période de fonctionnement) # d’arrêts faisceau sur le réacteur plus long que 0. 1 sec 100 maximum par jour # d’arrêts faisceau sur le réacteur plus court que 0. 1 sec illimités Fiabilité très importante Journées VLSI 2018 S. Berthelot J-F Yaniche 4

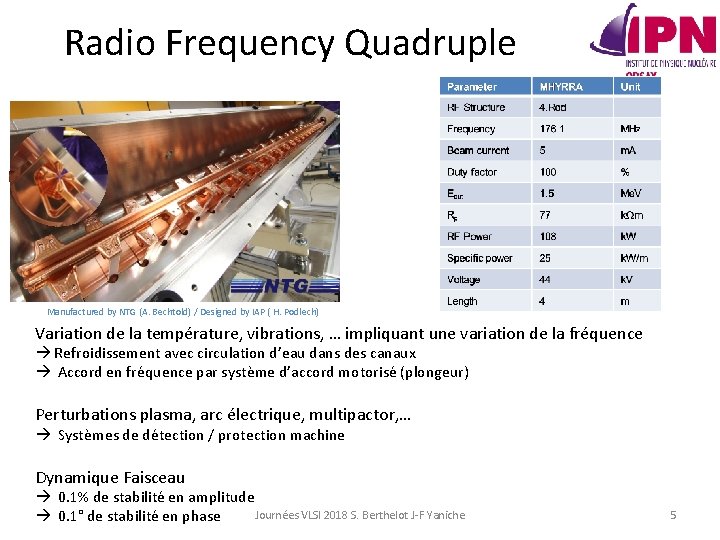

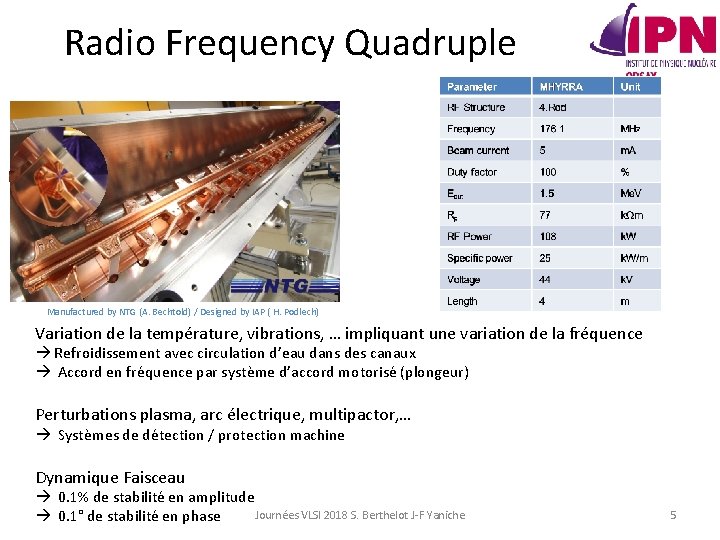

Radio Frequency Quadruple Manufactured by NTG (A. Bechtold) / Designed by IAP ( H. Podlech) Variation de la température, vibrations, … impliquant une variation de la fréquence Refroidissement avec circulation d’eau dans des canaux Accord en fréquence par système d’accord motorisé (plongeur) Perturbations plasma, arc électrique, multipactor, … Systèmes de détection / protection machine Dynamique Faisceau 0. 1% de stabilité en amplitude Journées VLSI 2018 S. Berthelot J-F Yaniche 0. 1° de stabilité en phase 5

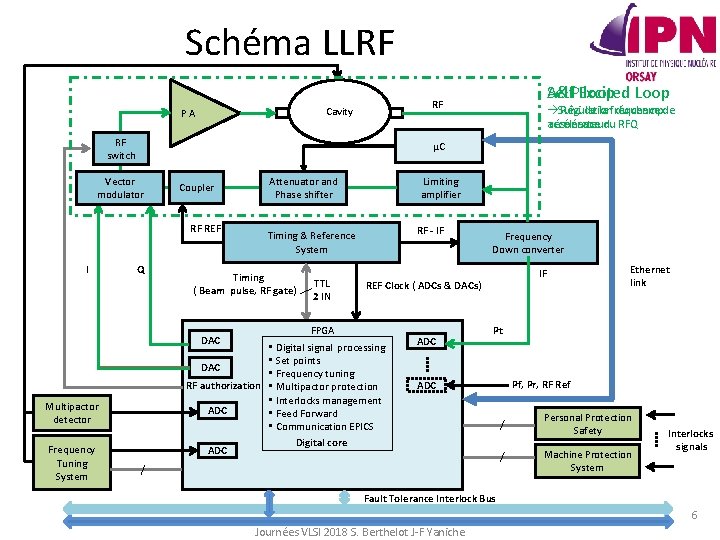

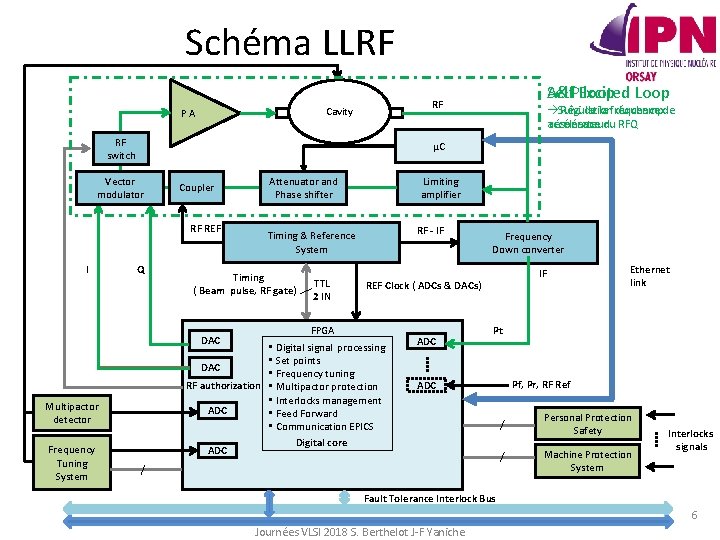

Schéma LLRF Cavity PA RF switch Coupler RF REF Q Frequency Tuning System Attenuator and Phase shifter Limiting amplifier RF - IF Timing & Reference System Timing ( Beam pulse, RF gate) TTL 2 IN Frequency Down converter IF REF Clock ( ADCs & DACs) FPGA • Digital signal processing • Set points DAC • Frequency tuning RF authorization • Multipactor protection • Interlocks management ADC • Feed Forward • Communication EPICS Digital core ADC DAC Multipactor detector Suivi de la fréquence Régulation du champde résonance du RFQ accélérateur µC Vector modulator I Self A&PExcited loop Loop RF ADC Ethernet link Pt ADC Pf, Pr, RF Ref Personal Protection Safety Machine Protection System Interlocks signals Fault Tolerance Interlock Bus 6 Journées VLSI 2018 S. Berthelot J-F Yaniche

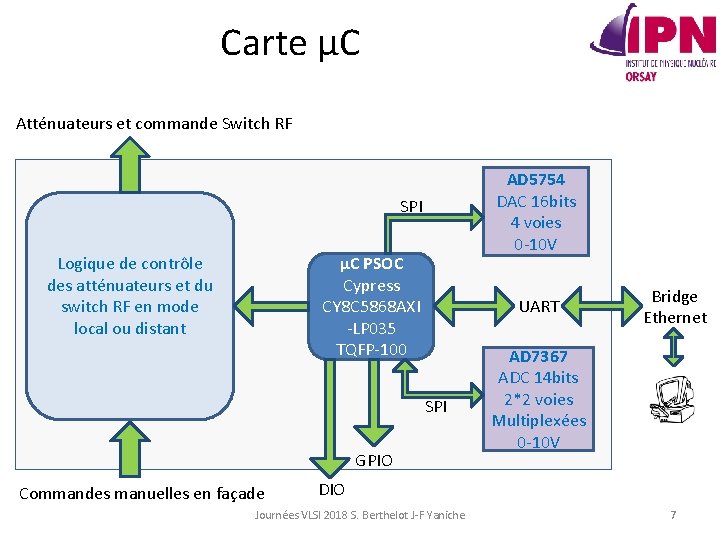

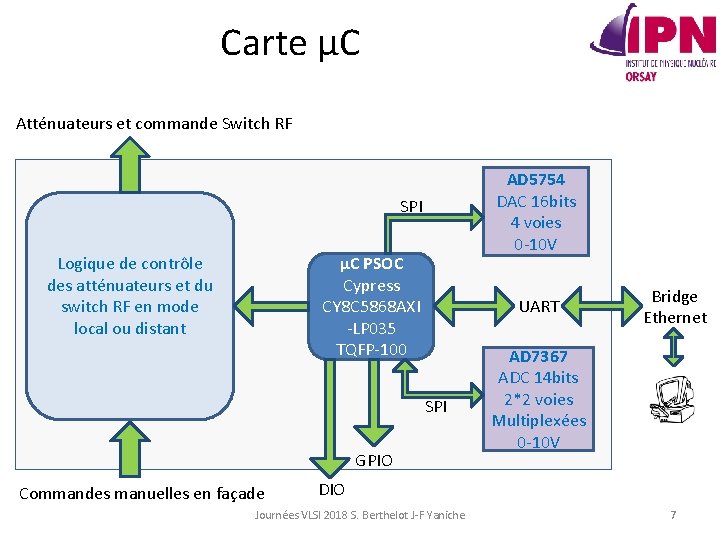

Carte µC Atténuateurs et commande Switch RF AD 5754 DAC 16 bits 4 voies 0 -10 V SPI µC PSOC Cypress CY 8 C 5868 AXI -LP 035 TQFP-100 Logique de contrôle des atténuateurs et du switch RF en mode local ou distant UART SPI GPIO Commandes manuelles en façade Bridge Ethernet AD 7367 ADC 14 bits 2*2 voies Multiplexées 0 -10 V DIO Journées VLSI 2018 S. Berthelot J-F Yaniche 7

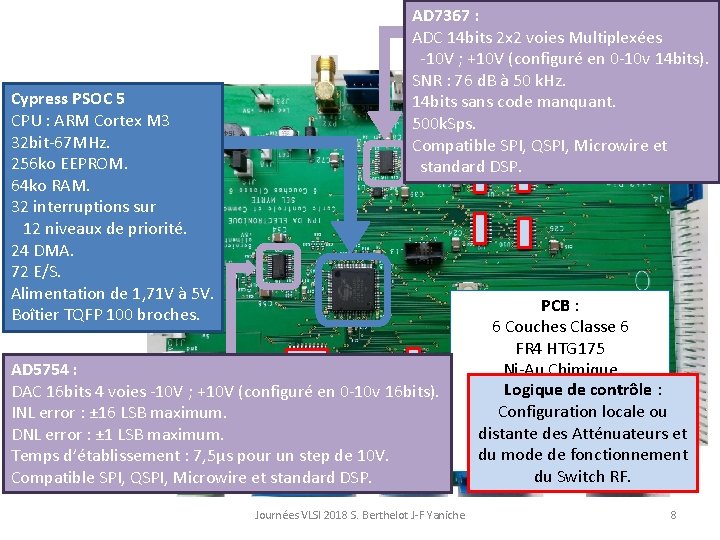

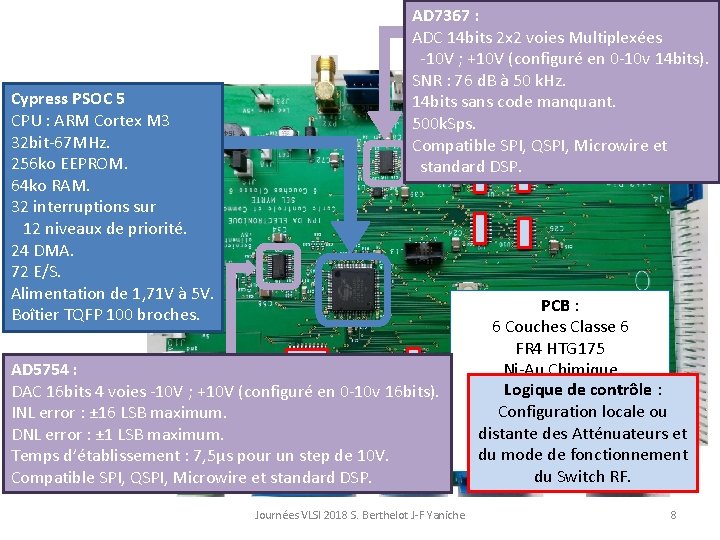

Cypress PSOC 5 CPU : ARM Cortex M 3 32 bit-67 MHz. 256 ko EEPROM. 64 ko RAM. 32 interruptions sur 12 niveaux de priorité. 24 DMA. 72 E/S. Alimentation de 1, 71 V à 5 V. Boîtier TQFP 100 broches. AD 7367 : ADC 14 bits 2 x 2 voies Multiplexées -10 V ; +10 V (configuré en 0 -10 v 14 bits). SNR : 76 d. B à 50 k. Hz. 14 bits sans code manquant. 500 k. Sps. Compatible SPI, QSPI, Microwire et standard DSP. AD 5754 : DAC 16 bits 4 voies -10 V ; +10 V (configuré en 0 -10 v 16 bits). INL error : ± 16 LSB maximum. DNL error : ± 1 LSB maximum. Temps d’établissement : 7, 5µs pour un step de 10 V. Compatible SPI, QSPI, Microwire et standard DSP. Journées VLSI 2018 S. Berthelot J-F Yaniche PCB : 6 Couches Classe 6 FR 4 HTG 175 Ni-Au Chimique Logique de contrôle : Configuration locale Câblage CMS au sein du ou distanteservice des Atténuateurs et du mode de fonctionnement du Switch RF. 8

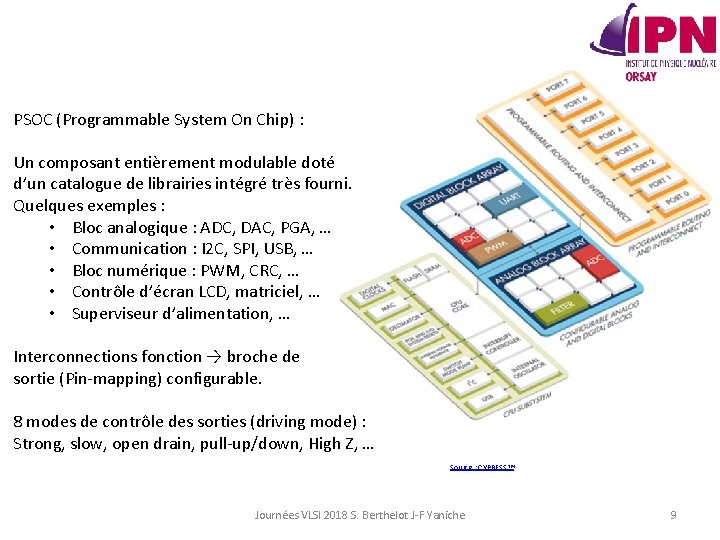

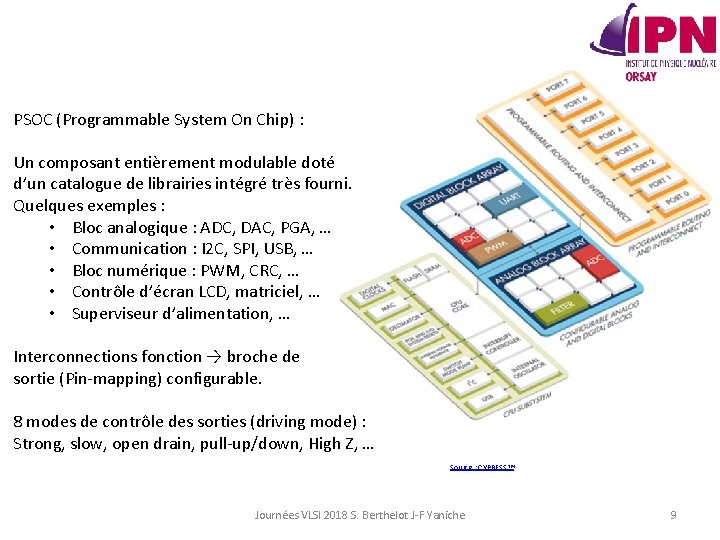

PSOC (Programmable System On Chip) : Un composant entièrement modulable doté d’un catalogue de librairies intégré très fourni. Quelques exemples : • Bloc analogique : ADC, DAC, PGA, … • Communication : I 2 C, SPI, USB, … • Bloc numérique : PWM, CRC, … • Contrôle d’écran LCD, matriciel, … • Superviseur d’alimentation, … Interconnections fonction → broche de sortie (Pin-mapping) configurable. 8 modes de contrôle des sorties (driving mode) : Strong, slow, open drain, pull-up/down, High Z, … Source : CYPRESS ™ Journées VLSI 2018 S. Berthelot J-F Yaniche 9

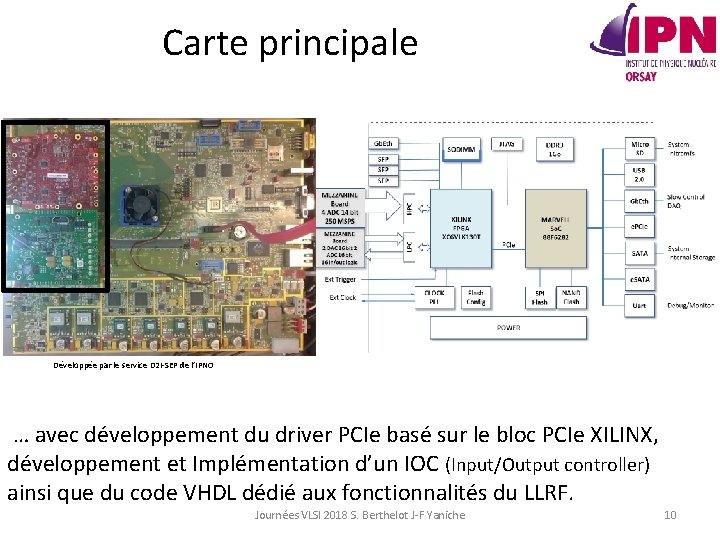

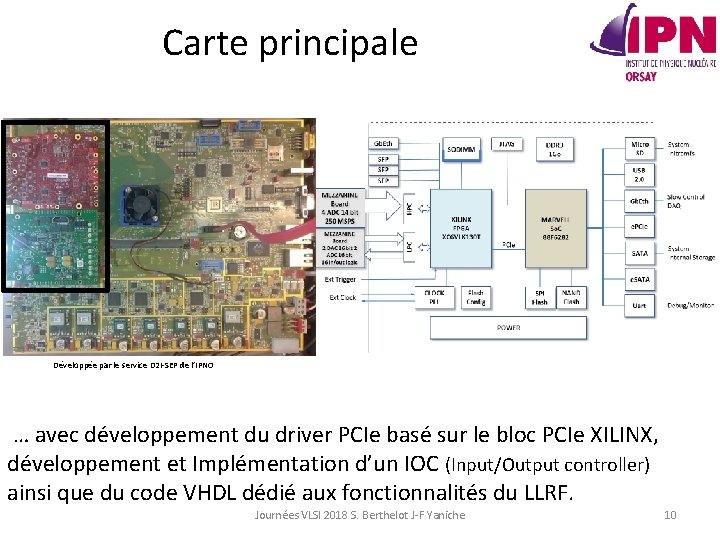

Carte principale Développée par le service D 2 I-SEP de l’IPNO … avec développement du driver PCIe basé sur le bloc PCIe XILINX, développement et Implémentation d’un IOC (Input/Output controller) ainsi que du code VHDL dédié aux fonctionnalités du LLRF. Journées VLSI 2018 S. Berthelot J-F Yaniche 10

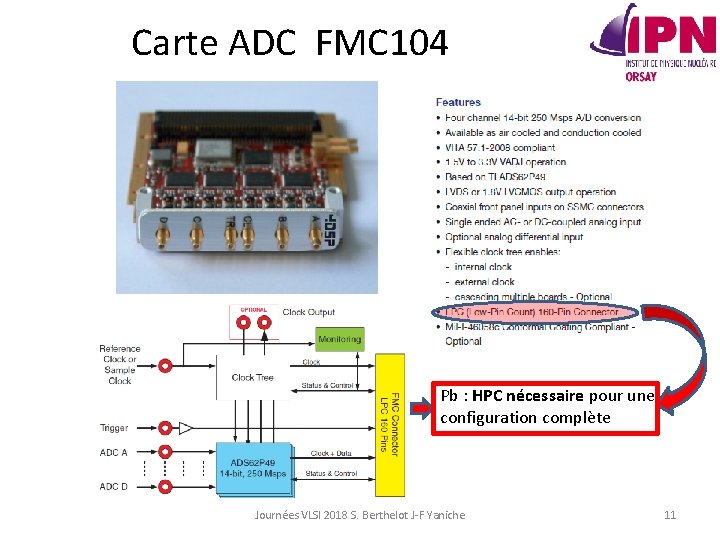

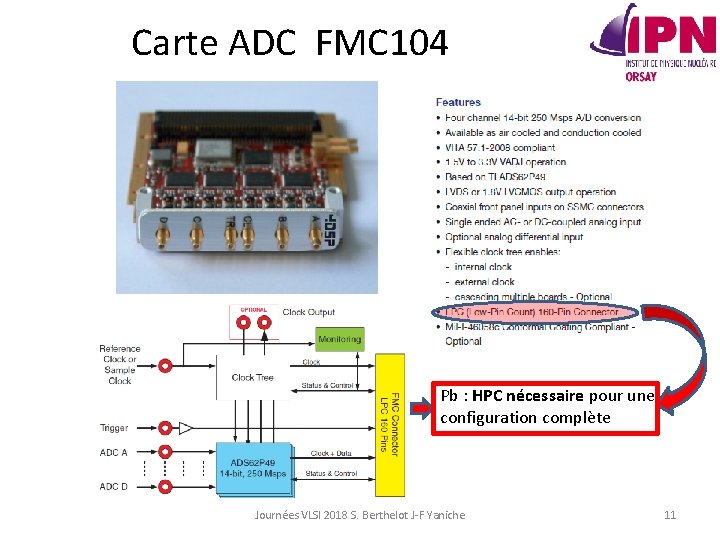

Carte ADC FMC 104 Pb : HPC nécessaire pour une configuration complète Journées VLSI 2018 S. Berthelot J-F Yaniche 11

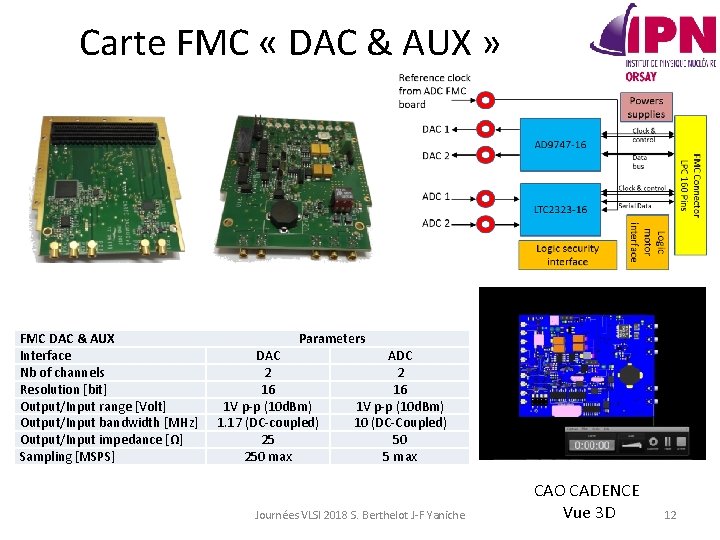

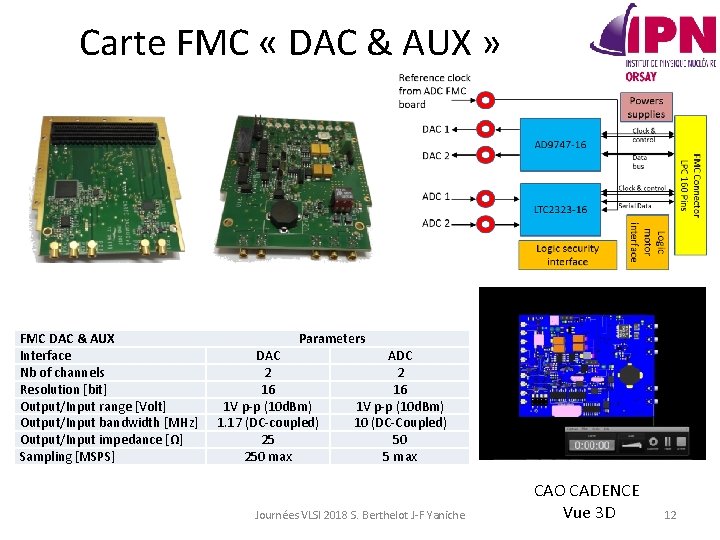

Carte FMC « DAC & AUX » FMC DAC & AUX Interface Nb of channels Resolution [bit] Output/Input range [Volt] Output/Input bandwidth [MHz] Output/Input impedance [Ω] Sampling [MSPS] Parameters DAC 2 16 1 V p-p (10 d. Bm) 1. 17 (DC-coupled) 25 250 max ADC 2 16 1 V p-p (10 d. Bm) 10 (DC-Coupled) 50 5 max Journées VLSI 2018 S. Berthelot J-F Yaniche CAO CADENCE Vue 3 D 12

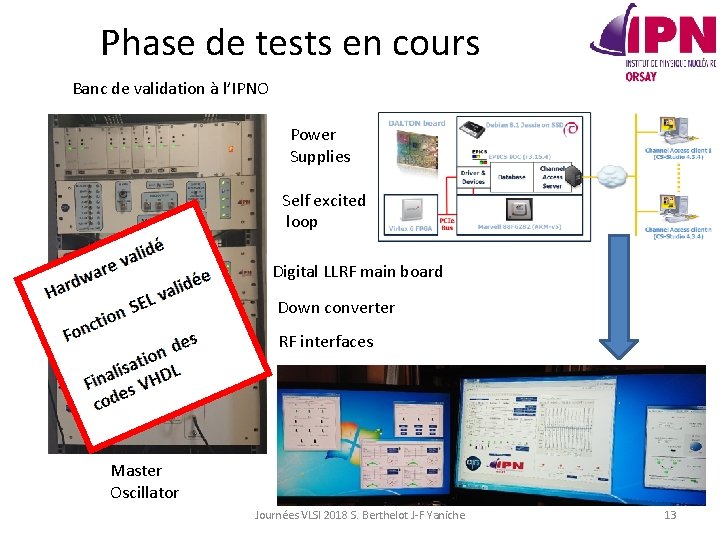

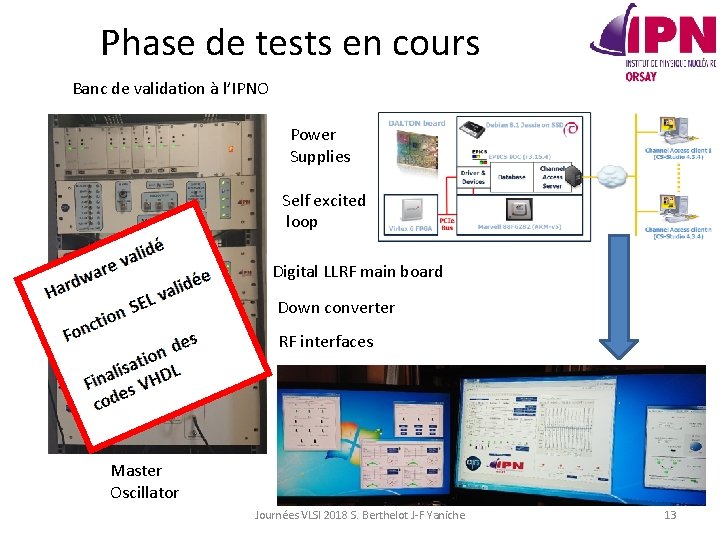

Phase de tests en cours Banc de validation à l’IPNO Power Supplies Self excited loop Digital LLRF main board Down converter RF interfaces Master Oscillator Journées VLSI 2018 S. Berthelot J-F Yaniche 13

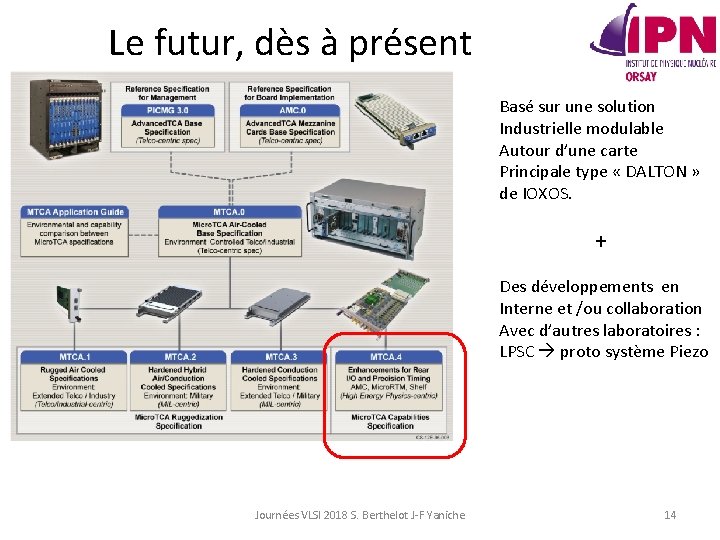

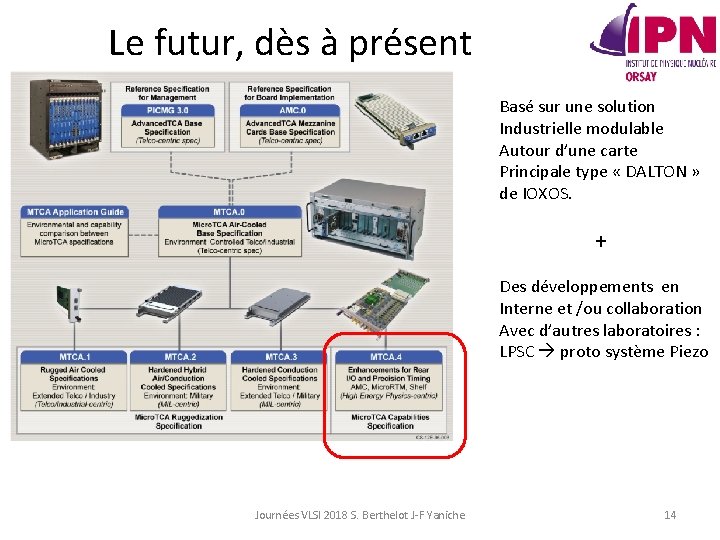

Le futur, dès à présent Basé sur une solution Industrielle modulable Autour d’une carte Principale type « DALTON » de IOXOS. + Des développements en Interne et /ou collaboration Avec d’autres laboratoires : LPSC proto système Piezo Journées VLSI 2018 S. Berthelot J-F Yaniche 14

Merci de votre attention. Bâtiment réacteur Site de Mol en Belgique cte u d n o ac supr c a n i L ur Bâtiment injecteur Remerciements aux membres de la collaboration MYRTE et aux équipes associées Journées VLSI 2018 S. Berthelot J-F Yaniche 15