Flynns Taxonomy of Computer Architectures Source Wikipedia Michael

- Slides: 13

Flynn’s Taxonomy of Computer Architectures Source: Wikipedia Michael Flynn 1966 CMPS 5433 – Parallel Processing

Flynn’s Taxonomy Proposed in 1966 General 4 category system Does not clearly classify all models in use today There are combinations, also.

Four Categories - Terminology S = Single I = Instruction Stream M = Multiple D = Data Stream SISD SIMD MISD MIMD

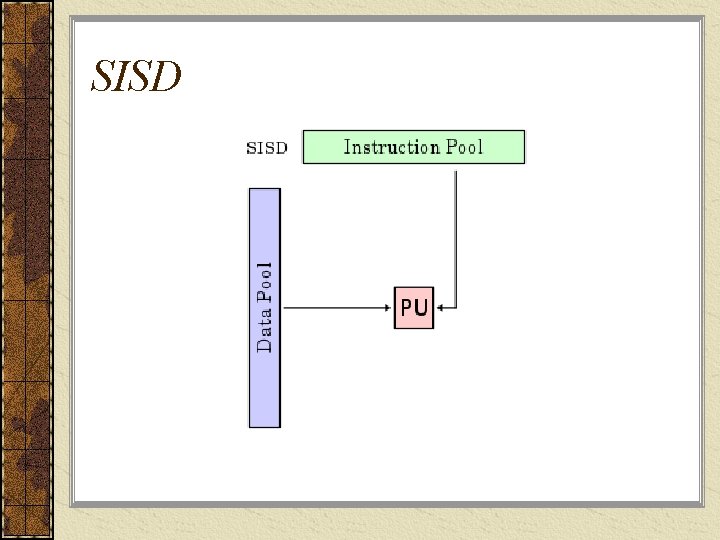

SISD Single Instruction, Single Data stream A sequential computer which exploits no parallelism in either the instruction or data streams. Examples of SISD architecture are the traditional single processor machines like a PC (currently manufactured PC's have multiple processors) or old mainframes.

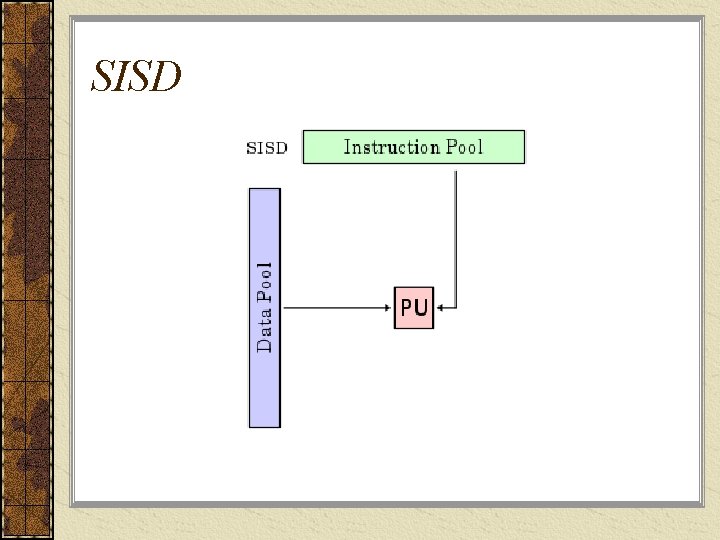

SISD

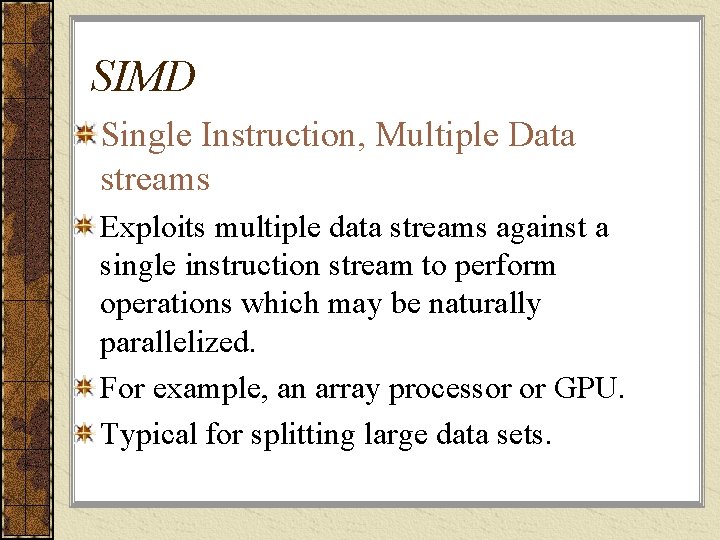

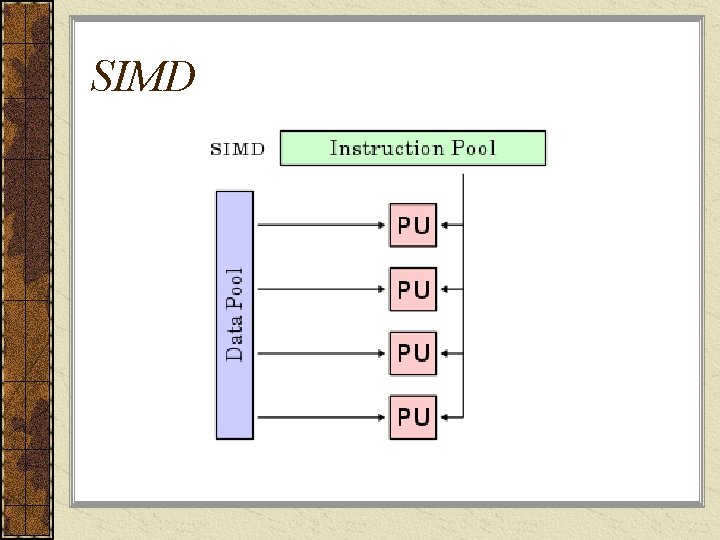

SIMD Single Instruction, Multiple Data streams Exploits multiple data streams against a single instruction stream to perform operations which may be naturally parallelized. For example, an array processor or GPU. Typical for splitting large data sets.

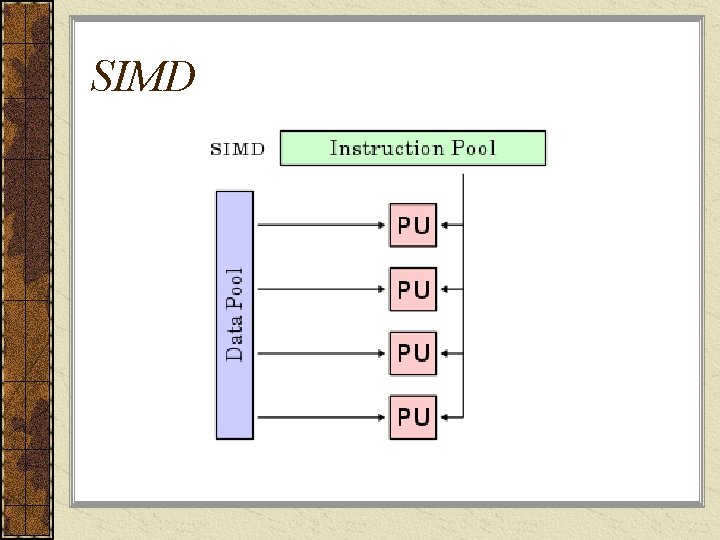

SIMD

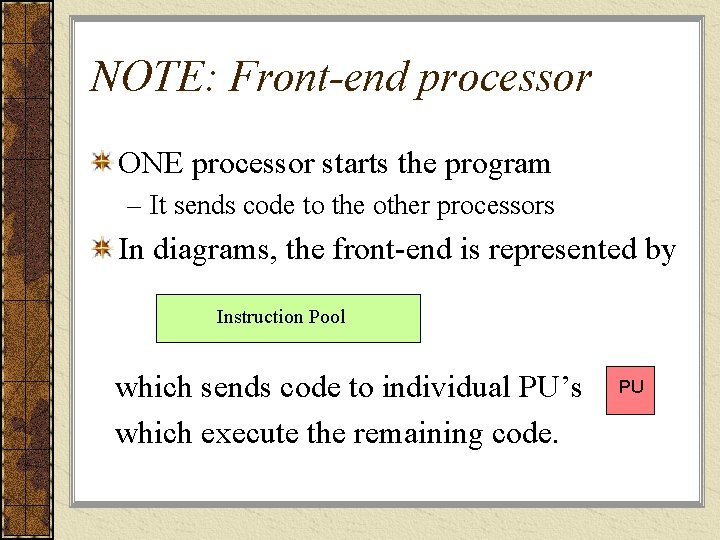

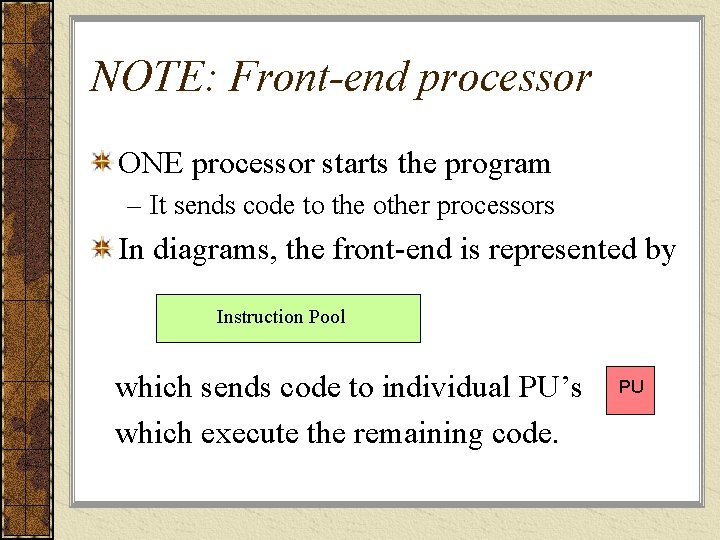

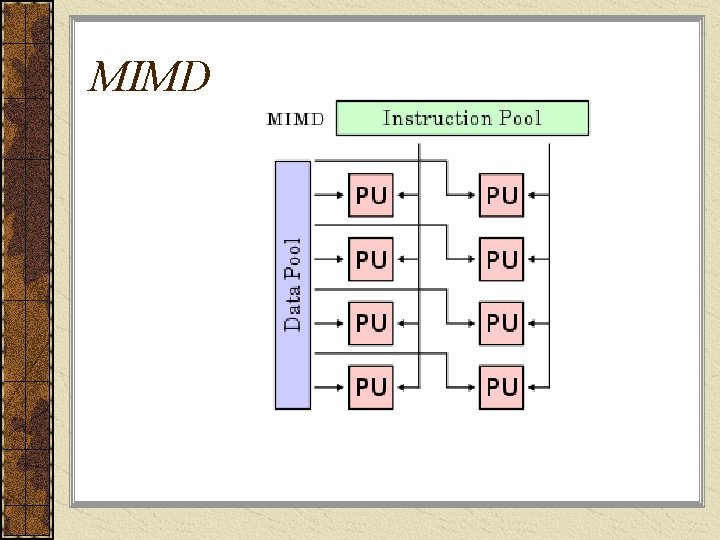

NOTE: Front-end processor ONE processor starts the program – It sends code to the other processors In diagrams, the front-end is represented by Instruction Pool which sends code to individual PU’s which execute the remaining code. PU

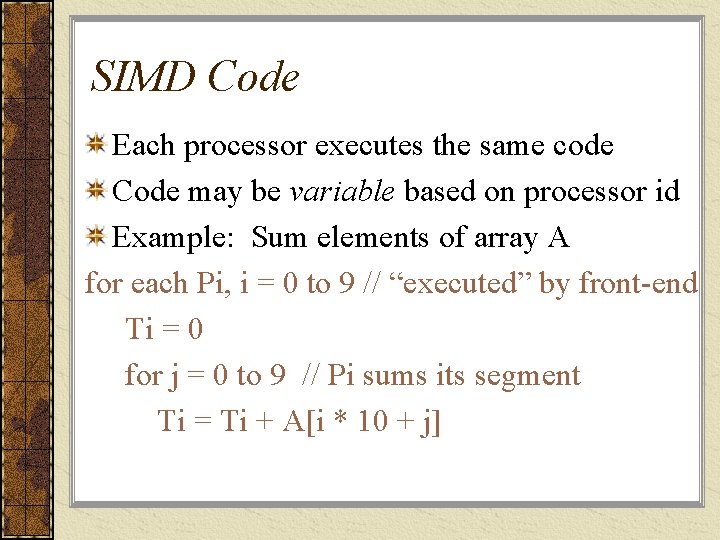

SIMD Code Each processor executes the same code Code may be variable based on processor id Example: Sum elements of array A for each Pi, i = 0 to 9 // “executed” by front-end Ti = 0 for j = 0 to 9 // Pi sums its segment Ti = Ti + A[i * 10 + j]

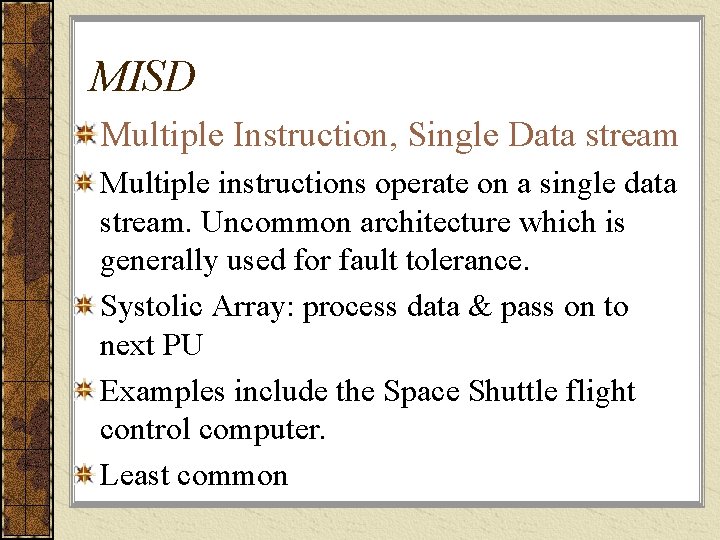

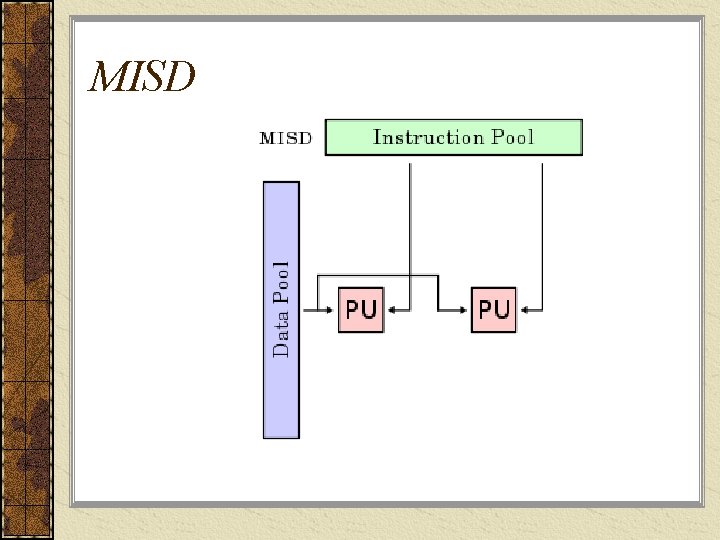

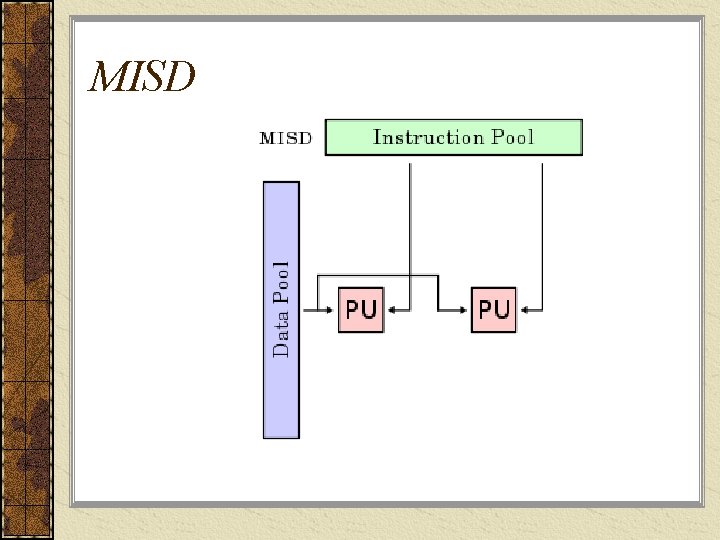

MISD Multiple Instruction, Single Data stream Multiple instructions operate on a single data stream. Uncommon architecture which is generally used for fault tolerance. Systolic Array: process data & pass on to next PU Examples include the Space Shuttle flight control computer. Least common

MISD

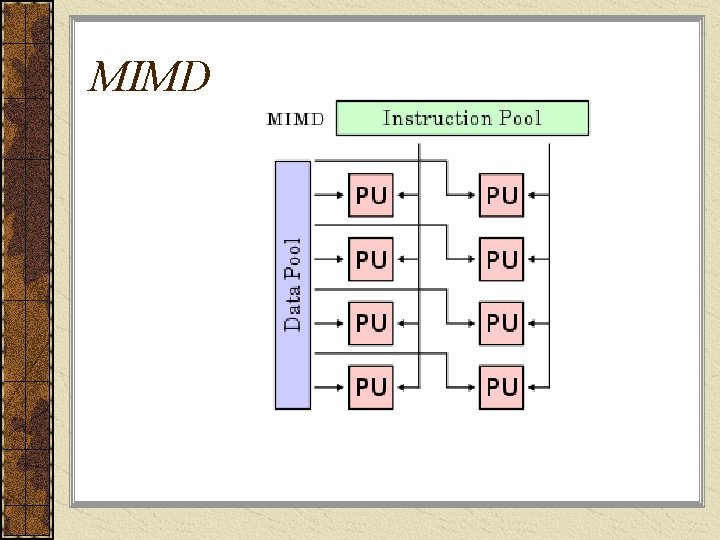

MIMD Multiple Instruction, Multiple Data streams Multiple autonomous processors simultaneously executing different instructions on different data. May send results to central location. Distributed systems – can be shared memory space or distributed memory space.

MIMD