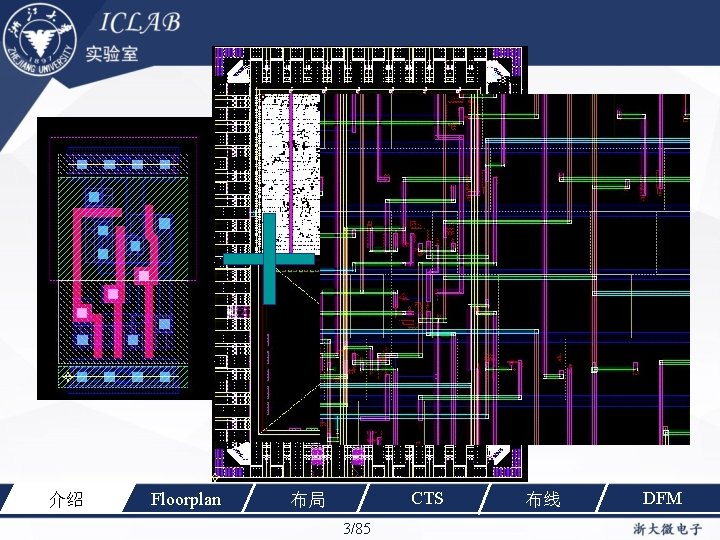

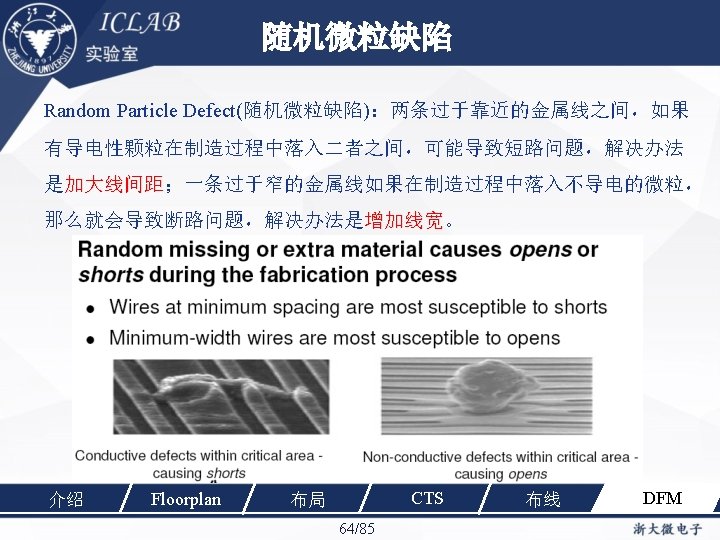

Floorplan CTS 385 DFM ICC Floorplan CTS 685

![. tdf文件语法 set_pad_physical_constraints objects | -pad_name stringpad_name [-side_number] [-order_number] 介绍 Floorplan CTS 布局 16/85 . tdf文件语法 set_pad_physical_constraints objects | -pad_name stringpad_name [-side_number] [-order_number] 介绍 Floorplan CTS 布局 16/85](https://slidetodoc.com/presentation_image_h/00c306ac76fde34d06546469aa00b928/image-16.jpg)

![CTS-定义时钟 在sdc文件中用create_clock命令创建时钟,同时定义了时钟源点如: create_clock [get_pins U_TOP_PAD/Pad_inout_PF 5_CAM_PCLK/C] -name CPCK -period 10 –waveform {0 5} CTS-定义时钟 在sdc文件中用create_clock命令创建时钟,同时定义了时钟源点如: create_clock [get_pins U_TOP_PAD/Pad_inout_PF 5_CAM_PCLK/C] -name CPCK -period 10 –waveform {0 5}](https://slidetodoc.com/presentation_image_h/00c306ac76fde34d06546469aa00b928/image-39.jpg)

- Slides: 83

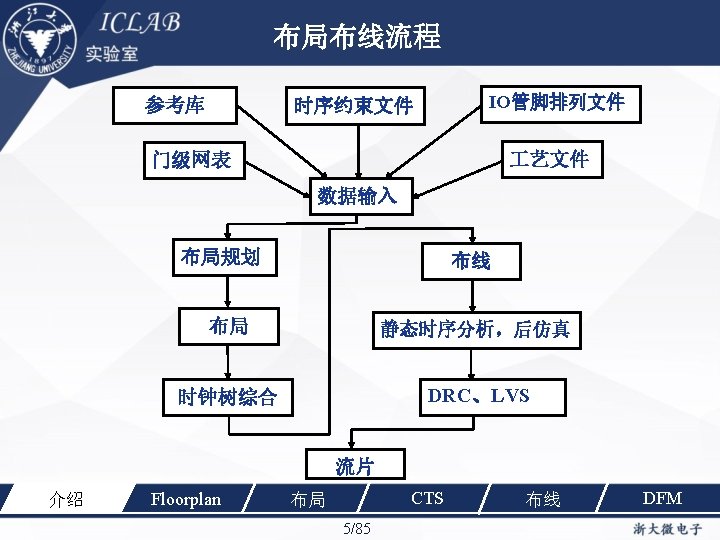

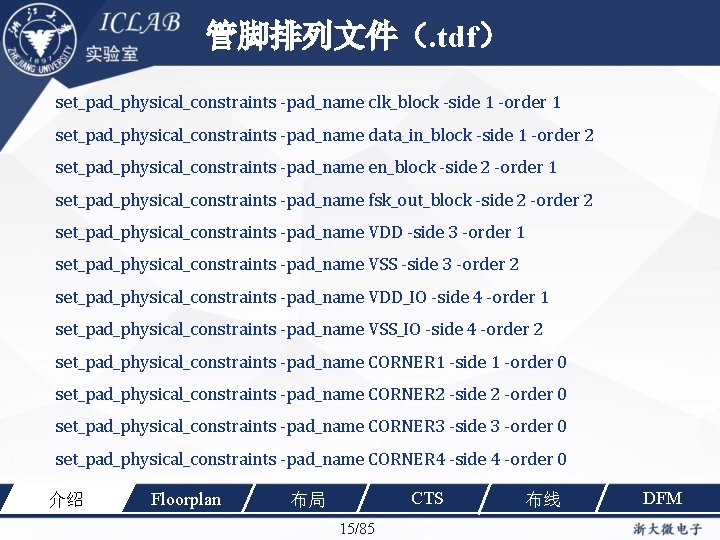

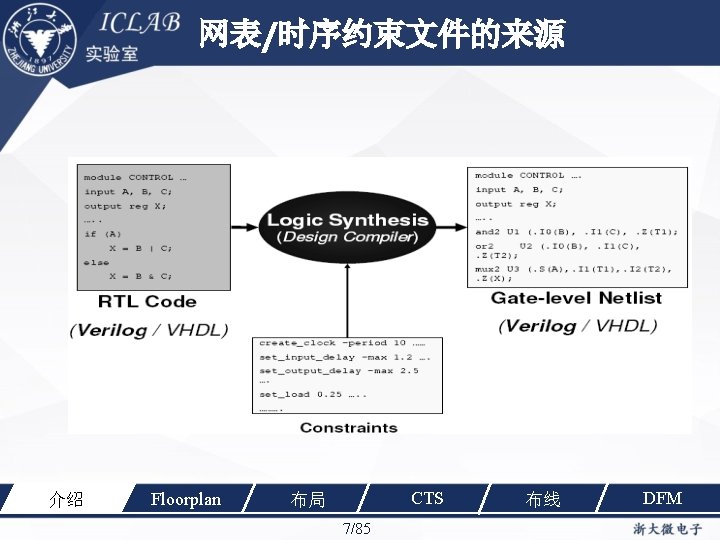

介绍 Floorplan CTS 布局 3/85 布线 DFM

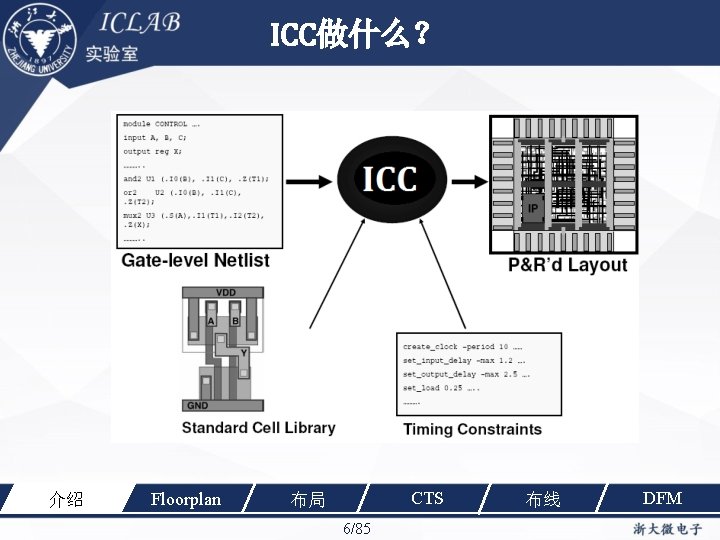

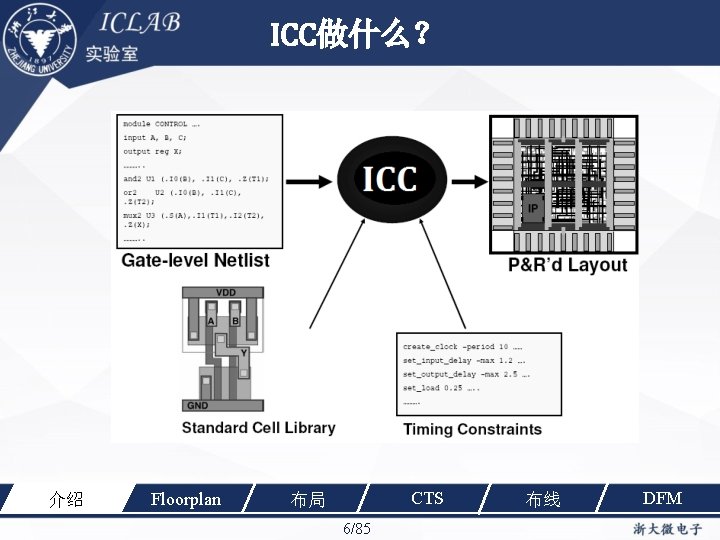

ICC做什么? 介绍 Floorplan CTS 布局 6/85 布线 DFM

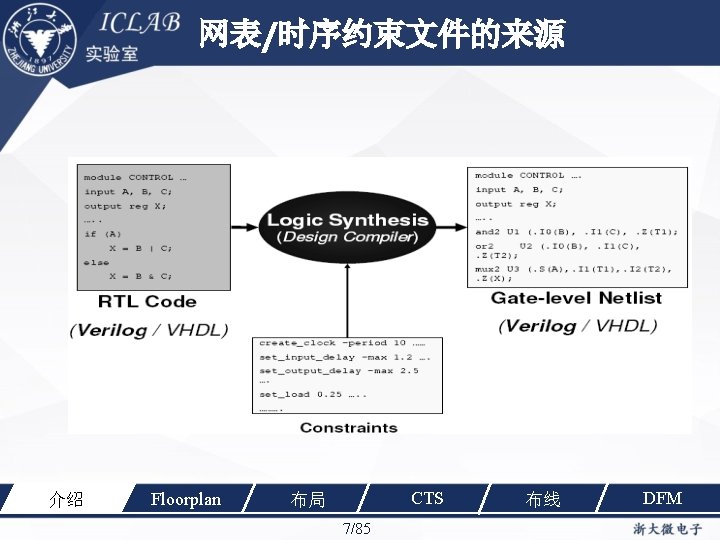

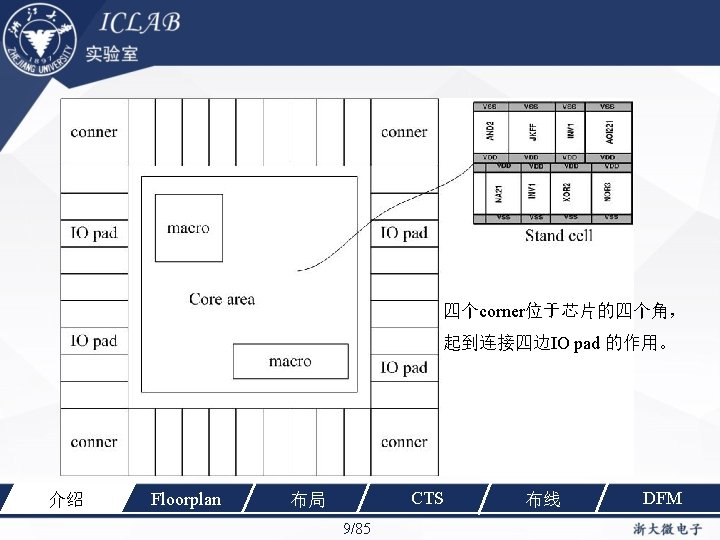

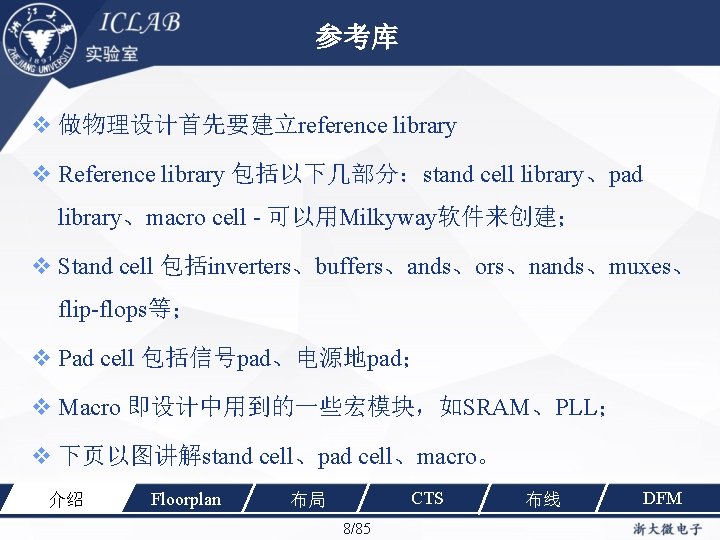

参考库 做物理设计首先要建立reference library Reference library 包括以下几部分:stand cell library、pad library、macro cell - 可以用Milkyway软件来创建; Stand cell 包括inverters、buffers、ands、ors、nands、muxes、 flip-flops等; Pad cell 包括信号pad、电源地pad; Macro 即设计中用到的一些宏模块,如SRAM、PLL; 下页以图讲解stand cell、pad cell、macro。 介绍 Floorplan CTS 布局 8/85 布线 DFM

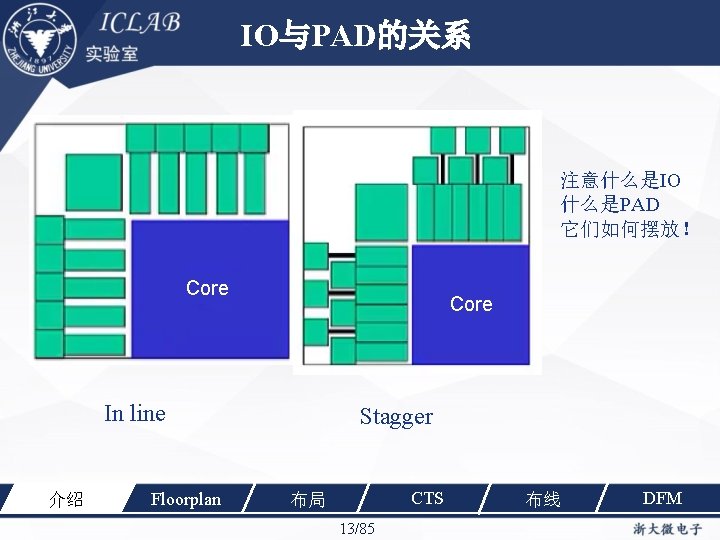

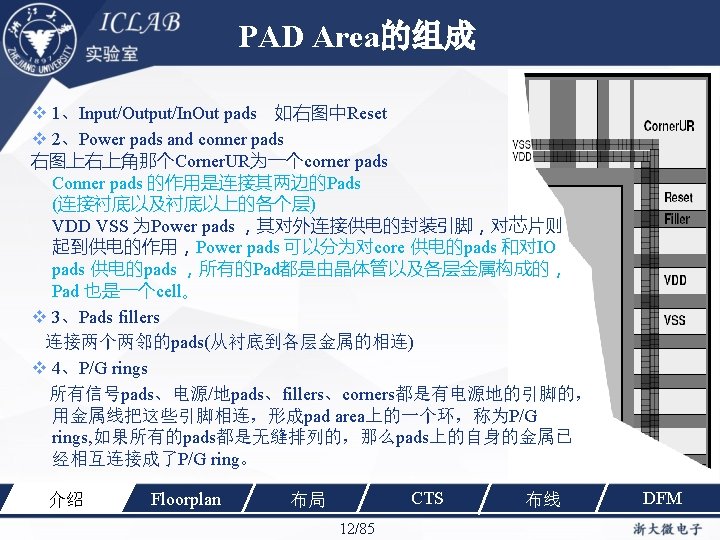

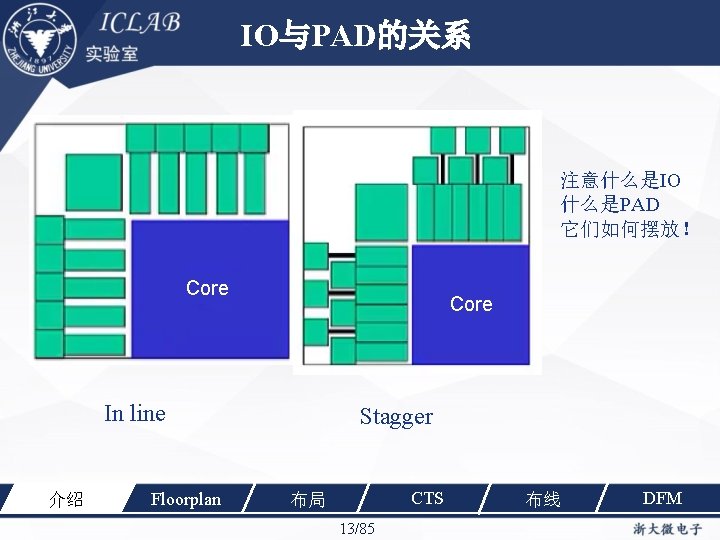

IO与PAD的关系 注意什么是IO 什么是PAD 它们如何摆放! Core In line 介绍 Floorplan Stagger CTS 布局 13/85 布线 DFM

IO与PAD的关系续 Triple Stagger IO 注意什么是IO,什么 是PAD 介绍 Floorplan CTS 布局 14/85 布线 DFM

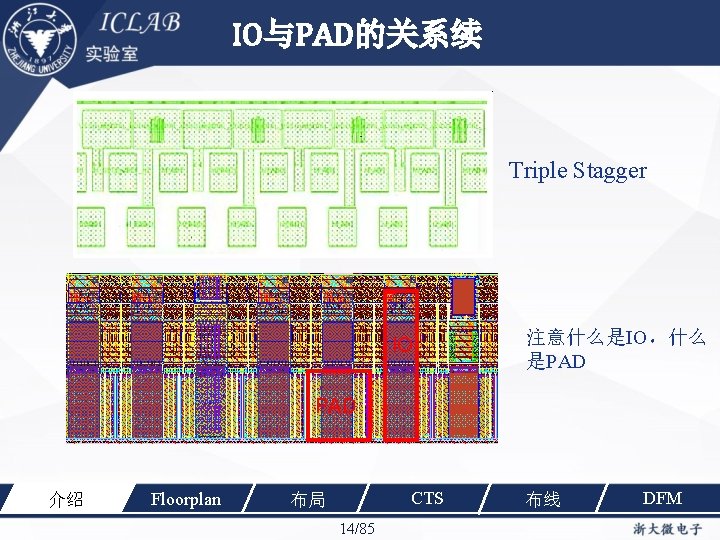

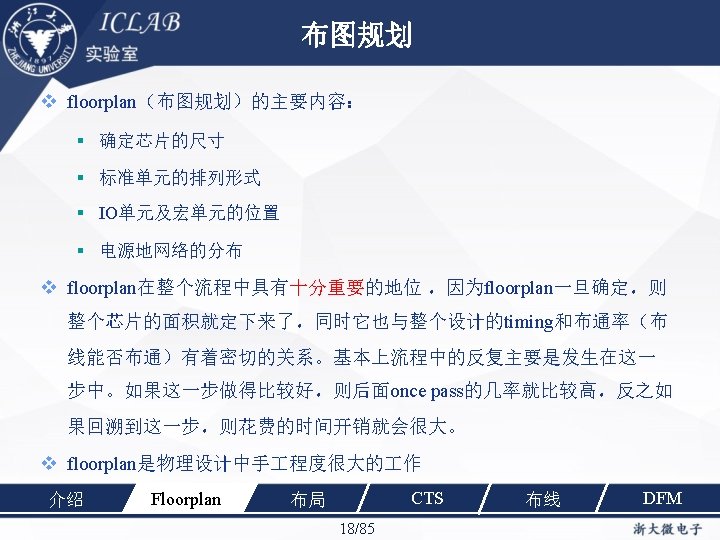

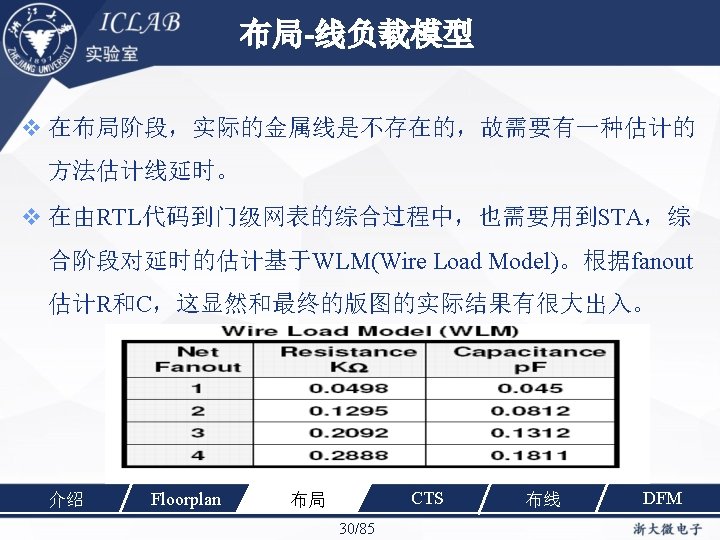

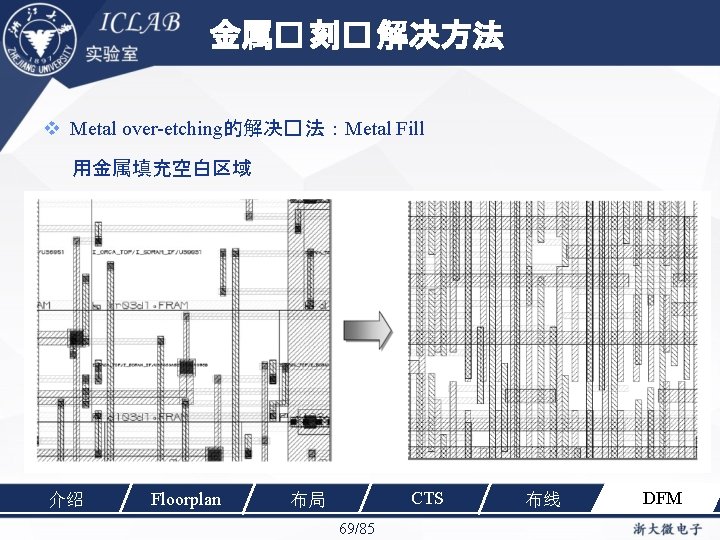

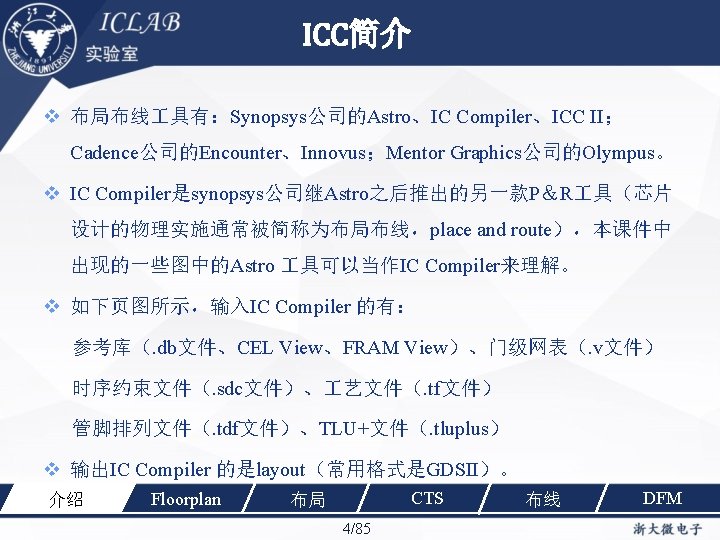

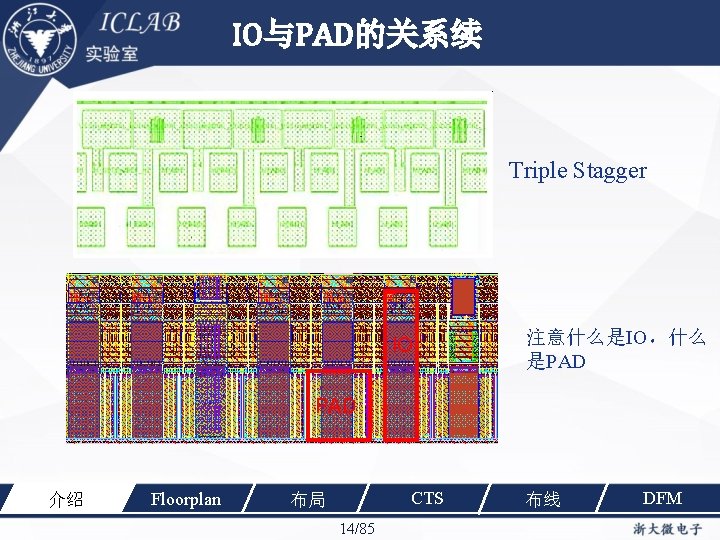

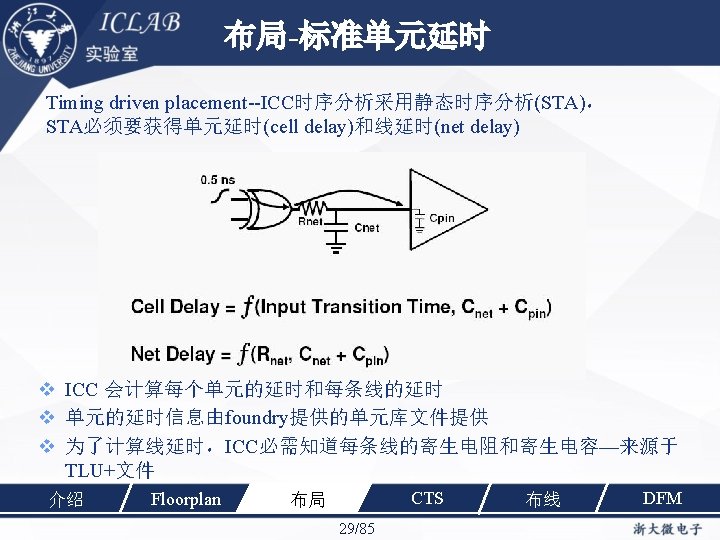

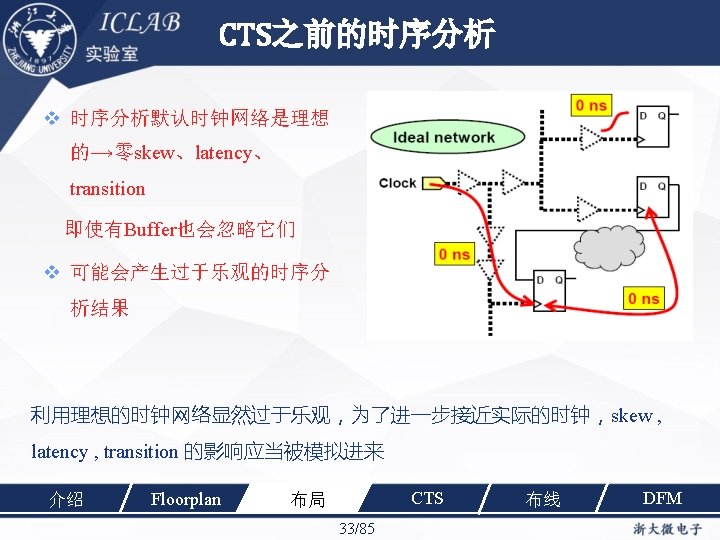

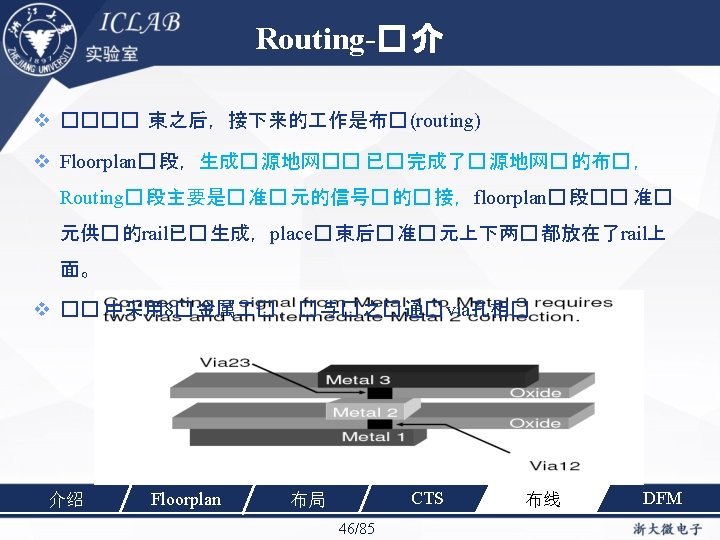

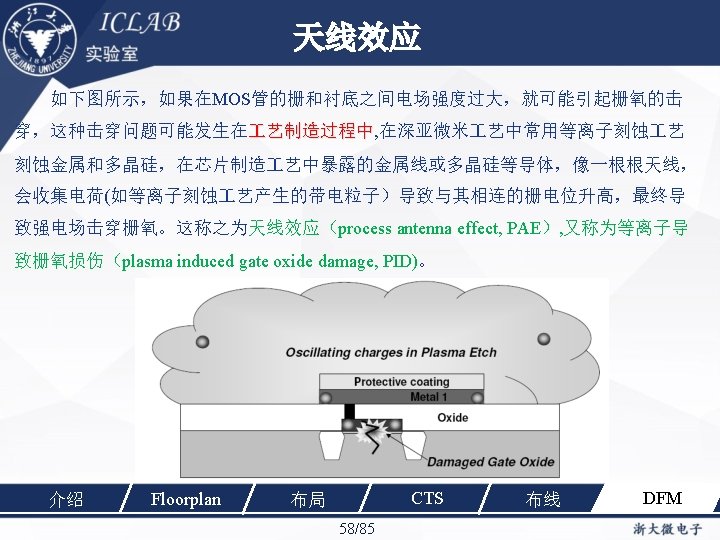

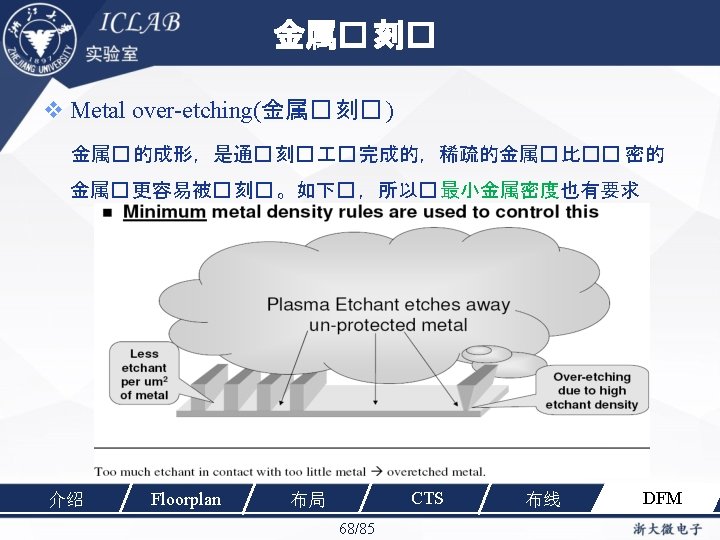

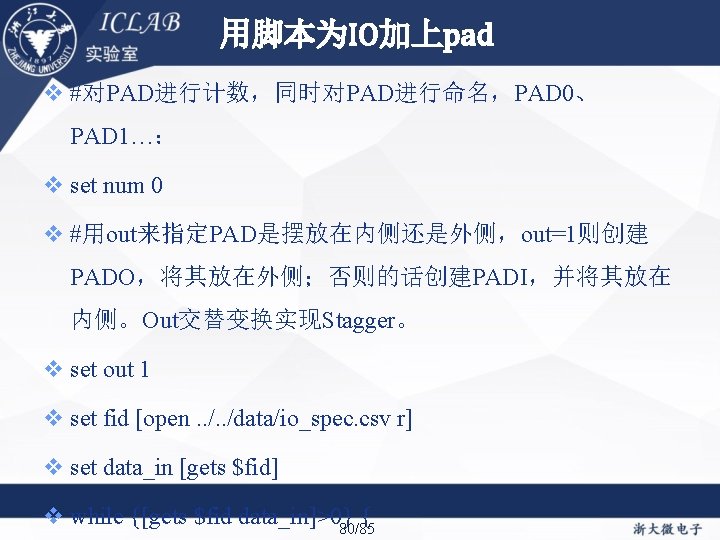

管脚排列文件(. tdf) set_pad_physical_constraints -pad_name clk_block -side 1 -order 1 set_pad_physical_constraints -pad_name data_in_block -side 1 -order 2 set_pad_physical_constraints -pad_name en_block -side 2 -order 1 set_pad_physical_constraints -pad_name fsk_out_block -side 2 -order 2 set_pad_physical_constraints -pad_name VDD -side 3 -order 1 set_pad_physical_constraints -pad_name VSS -side 3 -order 2 set_pad_physical_constraints -pad_name VDD_IO -side 4 -order 1 set_pad_physical_constraints -pad_name VSS_IO -side 4 -order 2 set_pad_physical_constraints -pad_name CORNER 1 -side 1 -order 0 set_pad_physical_constraints -pad_name CORNER 2 -side 2 -order 0 set_pad_physical_constraints -pad_name CORNER 3 -side 3 -order 0 set_pad_physical_constraints -pad_name CORNER 4 -side 4 -order 0 介绍 Floorplan CTS 布局 15/85 布线 DFM

![tdf文件语法 setpadphysicalconstraints objects padname stringpadname sidenumber ordernumber 介绍 Floorplan CTS 布局 1685 . tdf文件语法 set_pad_physical_constraints objects | -pad_name stringpad_name [-side_number] [-order_number] 介绍 Floorplan CTS 布局 16/85](https://slidetodoc.com/presentation_image_h/00c306ac76fde34d06546469aa00b928/image-16.jpg)

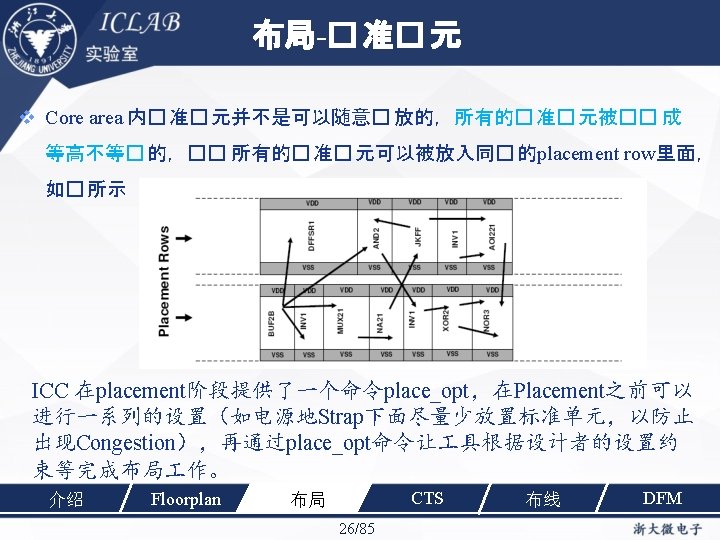

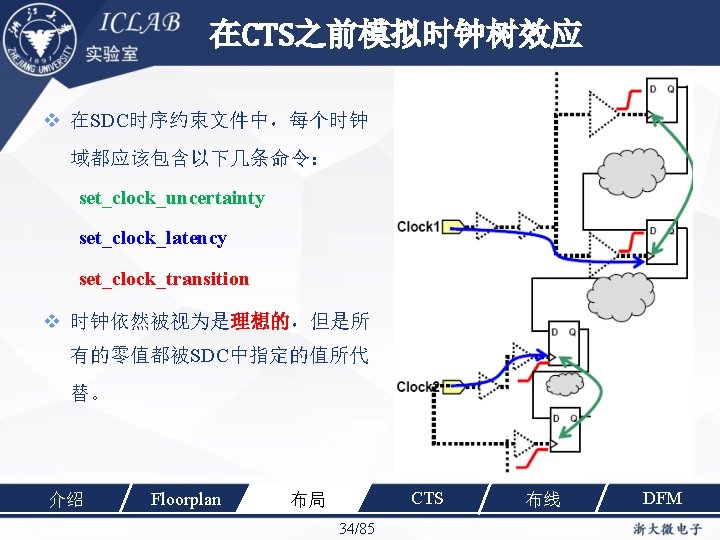

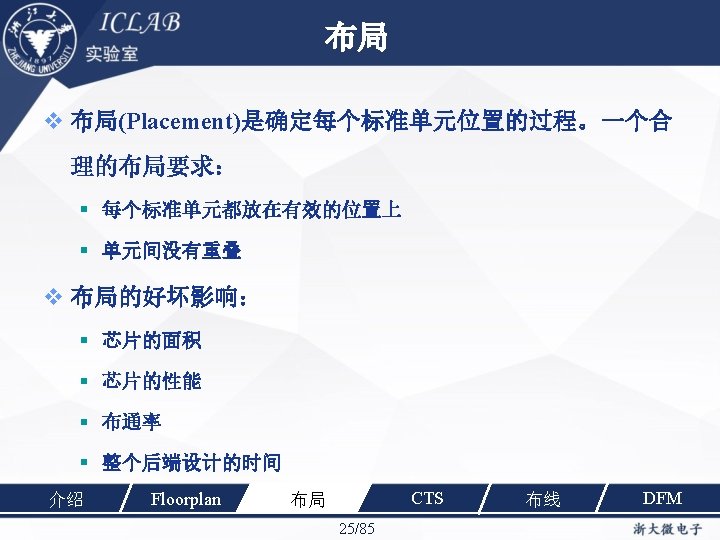

. tdf文件语法 set_pad_physical_constraints objects | -pad_name stringpad_name [-side_number] [-order_number] 介绍 Floorplan CTS 布局 16/85 布线 DFM

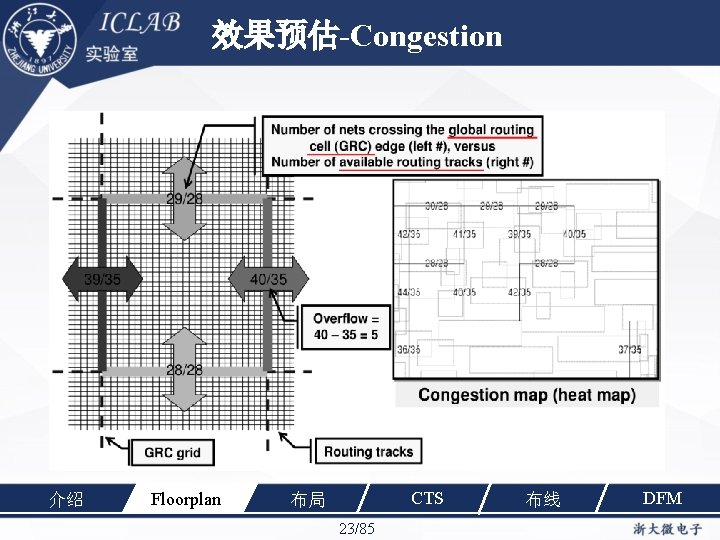

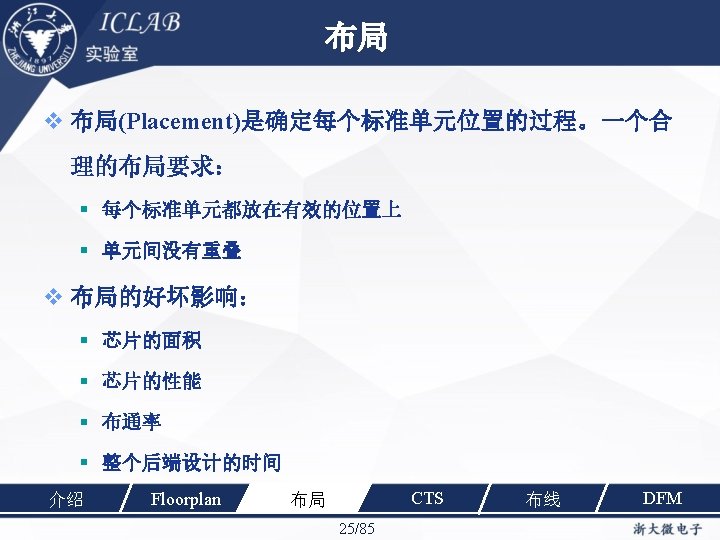

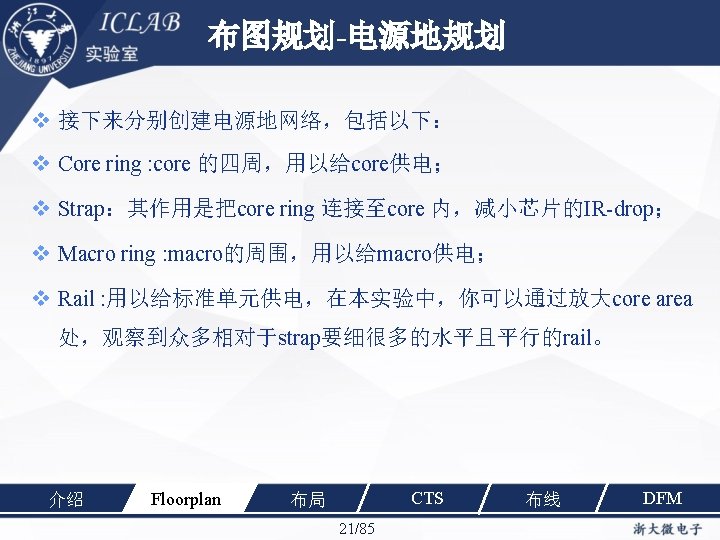

效果预估-Congestion 介绍 Floorplan CTS 布局 23/85 布线 DFM

![CTS定义时钟 在sdc文件中用createclock命令创建时钟同时定义了时钟源点如 createclock getpins UTOPPADPadinoutPF 5CAMPCLKC name CPCK period 10 waveform 0 5 CTS-定义时钟 在sdc文件中用create_clock命令创建时钟,同时定义了时钟源点如: create_clock [get_pins U_TOP_PAD/Pad_inout_PF 5_CAM_PCLK/C] -name CPCK -period 10 –waveform {0 5}](https://slidetodoc.com/presentation_image_h/00c306ac76fde34d06546469aa00b928/image-39.jpg)

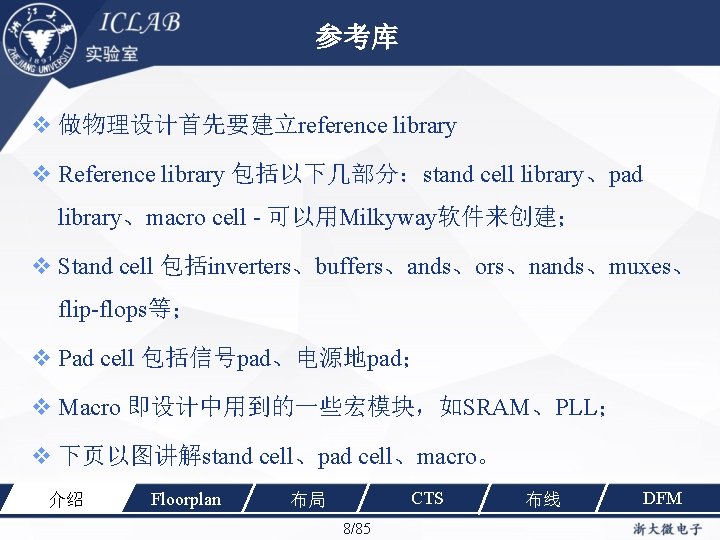

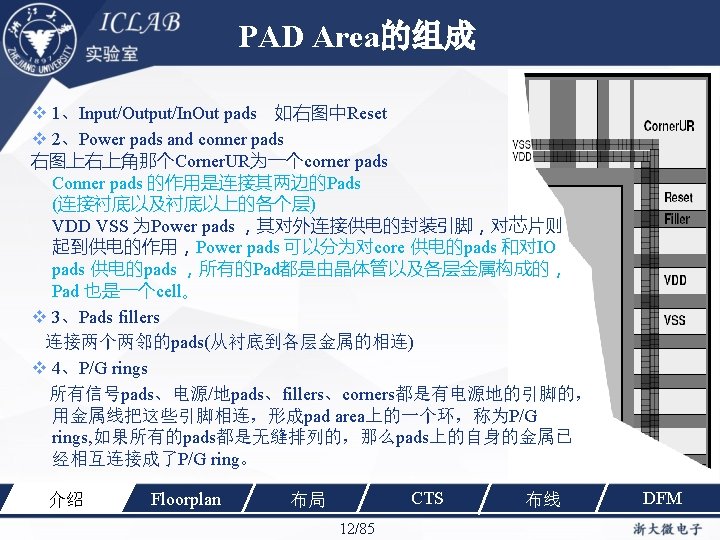

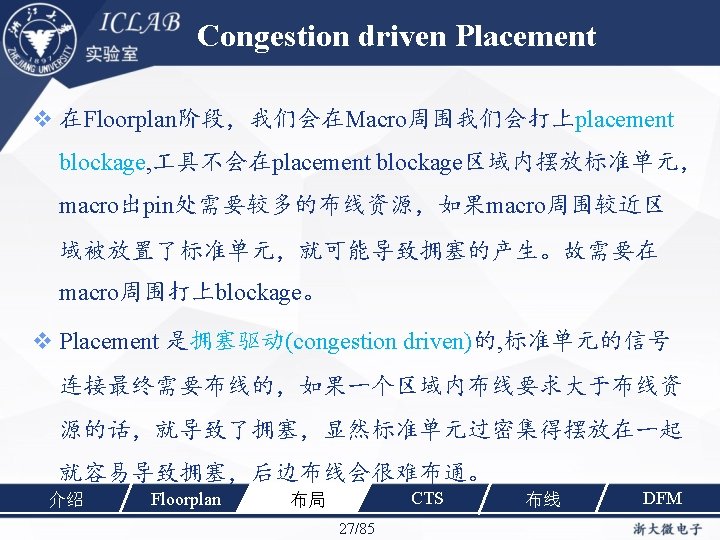

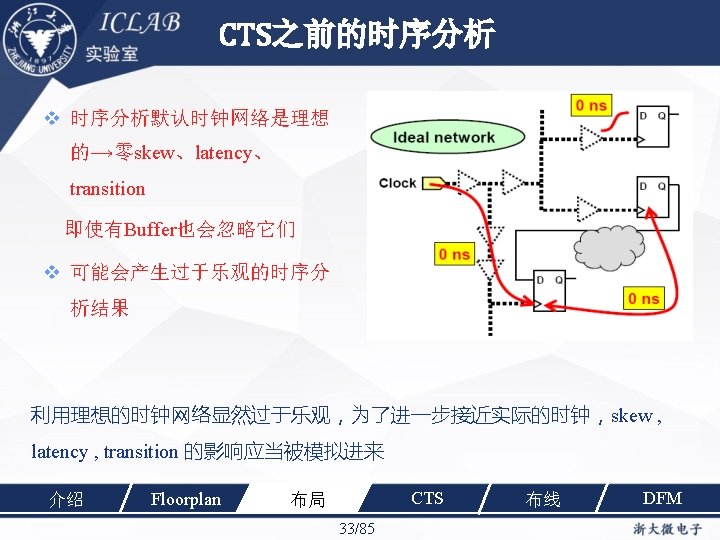

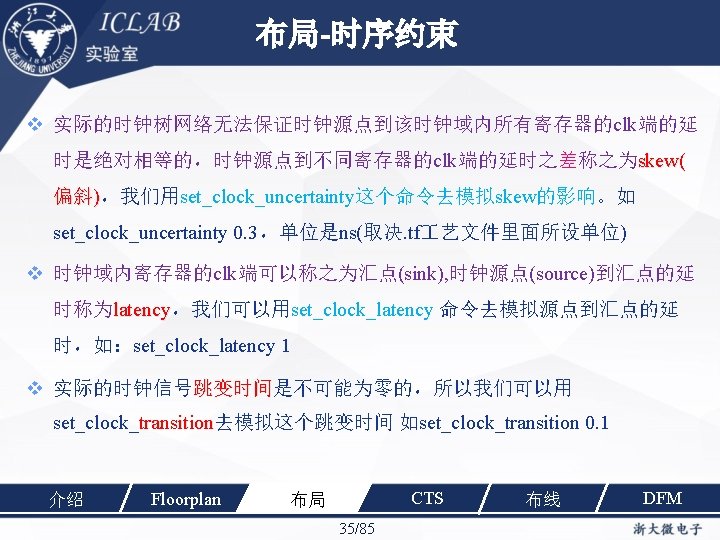

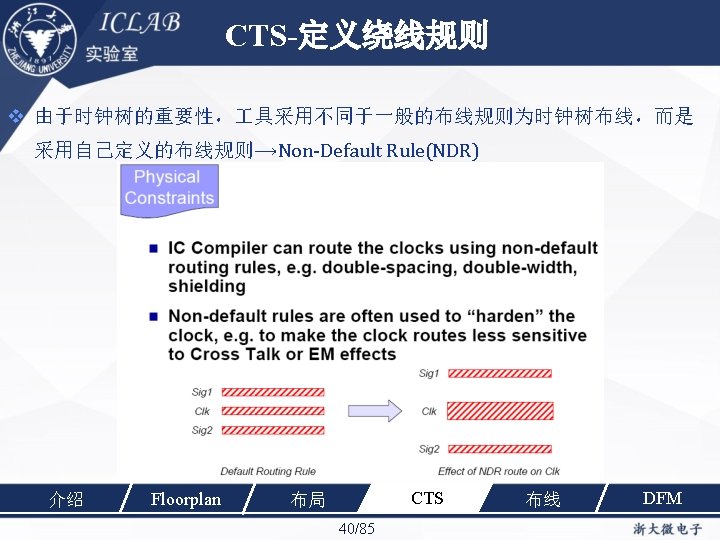

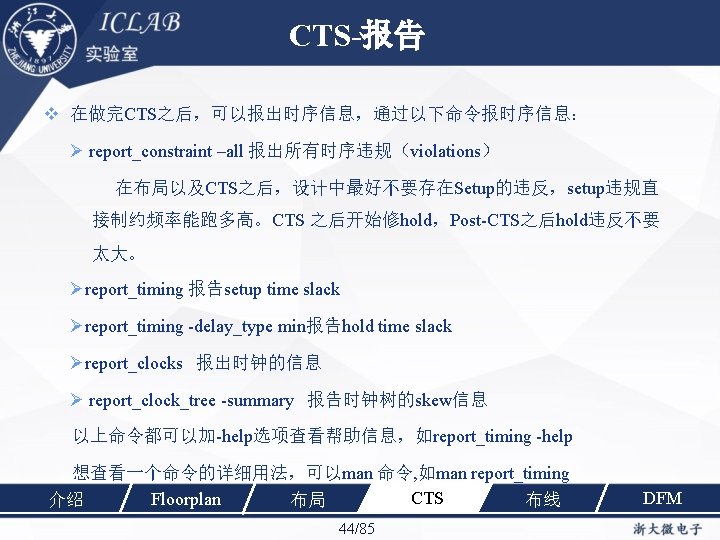

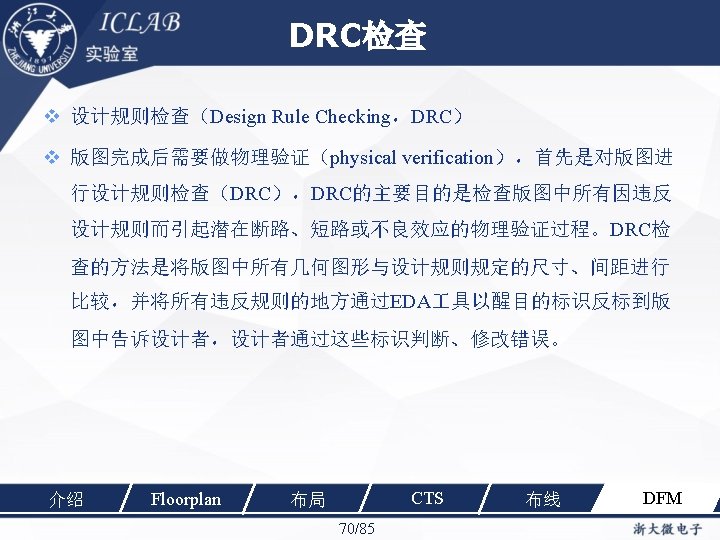

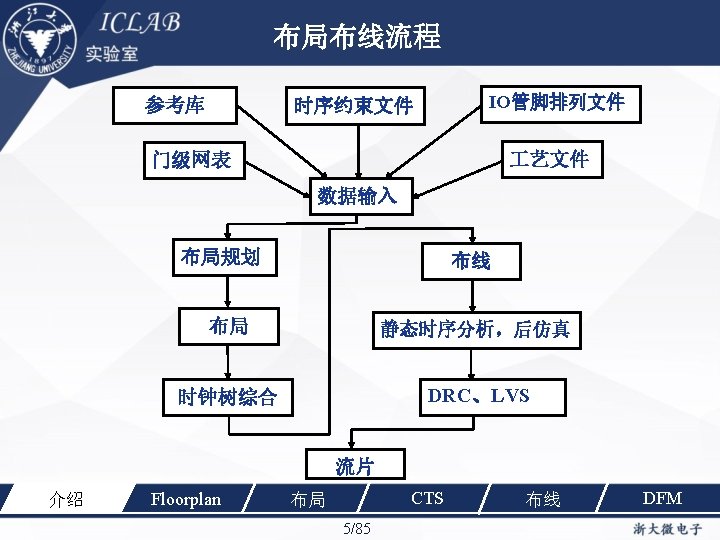

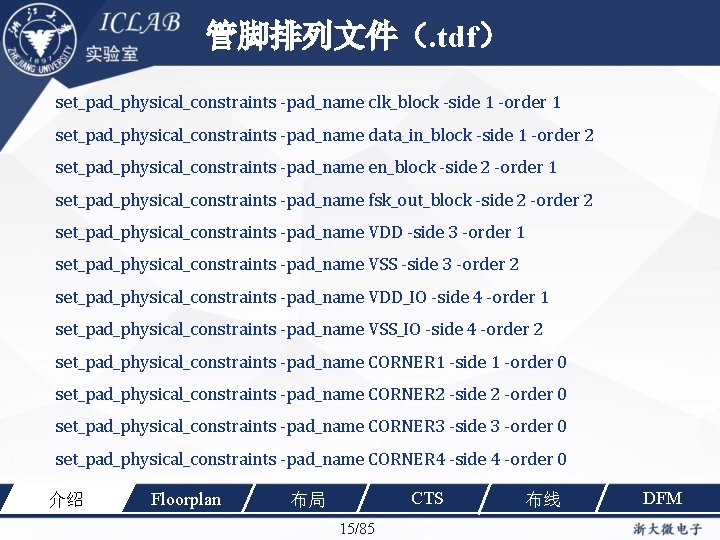

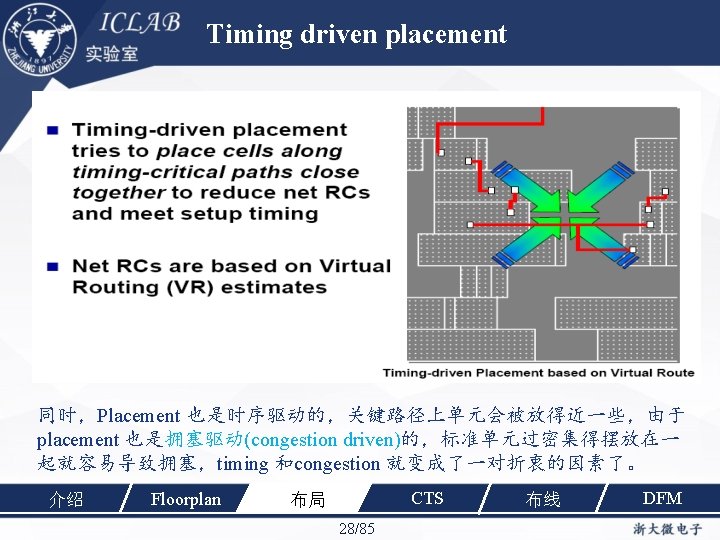

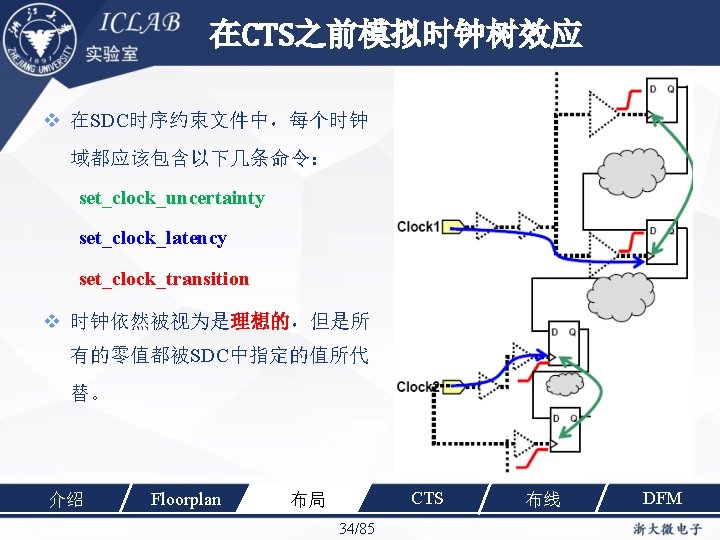

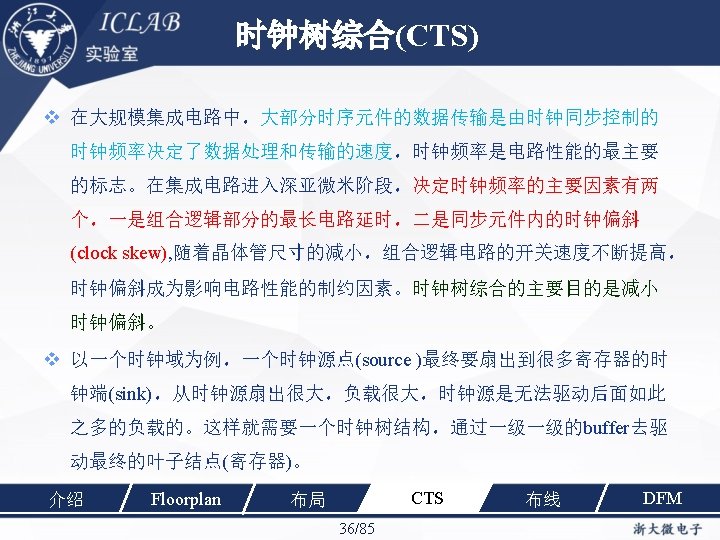

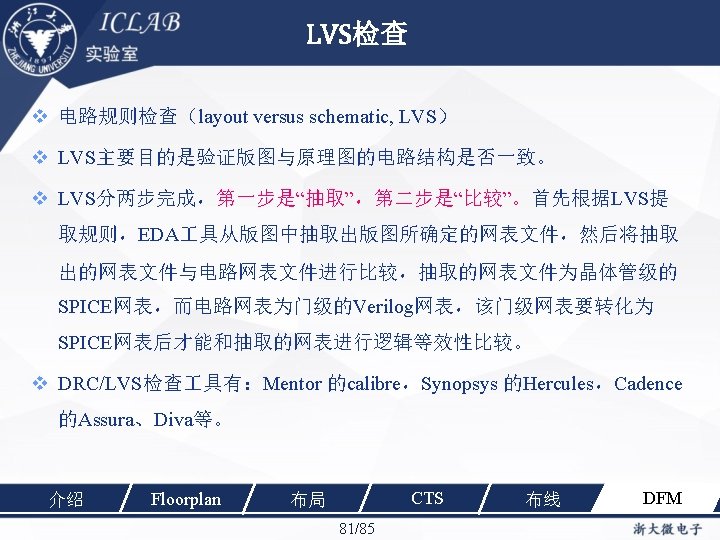

CTS-定义时钟 在sdc文件中用create_clock命令创建时钟,同时定义了时钟源点如: create_clock [get_pins U_TOP_PAD/Pad_inout_PF 5_CAM_PCLK/C] -name CPCK -period 10 –waveform {0 5} 这条命令在U_TOP_PAD/Pad_inout_PF 5_CAM_PCLK/C这个pin处创建了 时钟,这个pin就是名为CPCK的时钟的时钟源点 介绍 Floorplan CTS 布局 39/85 布线 DFM

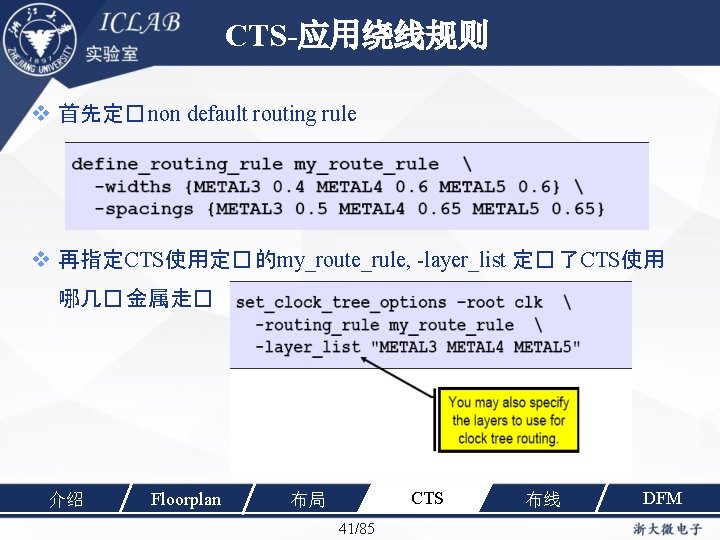

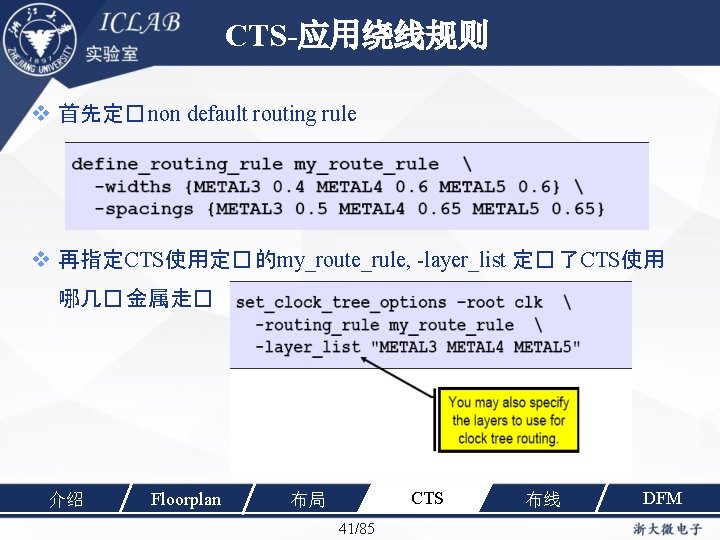

CTS-应用绕线规则 首先定� non default routing rule 再指定CTS使用定� 的my_route_rule, -layer_list 定� 了CTS使用 哪几� 金属走� 介绍 Floorplan CTS 布局 41/85 布线 DFM

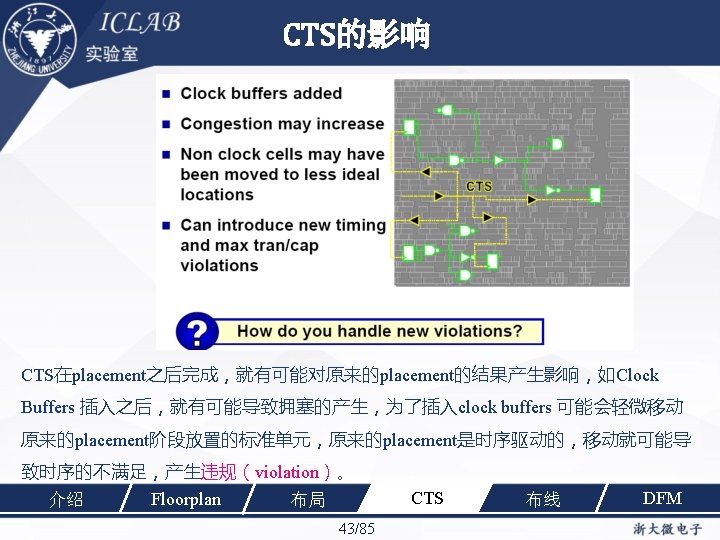

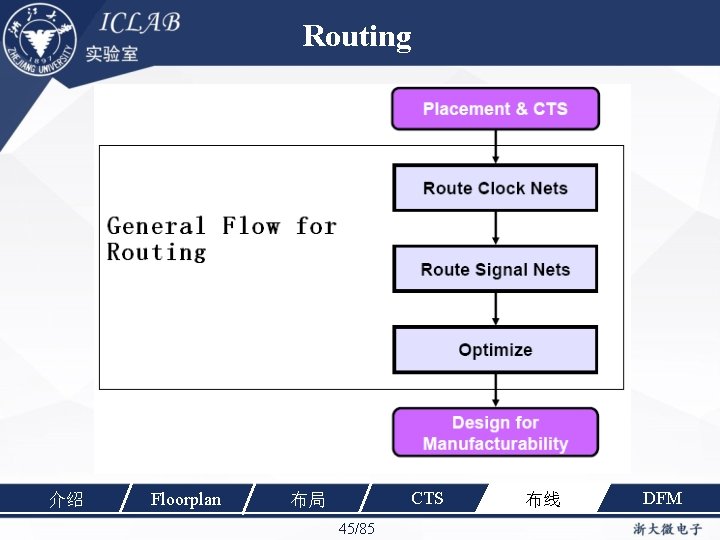

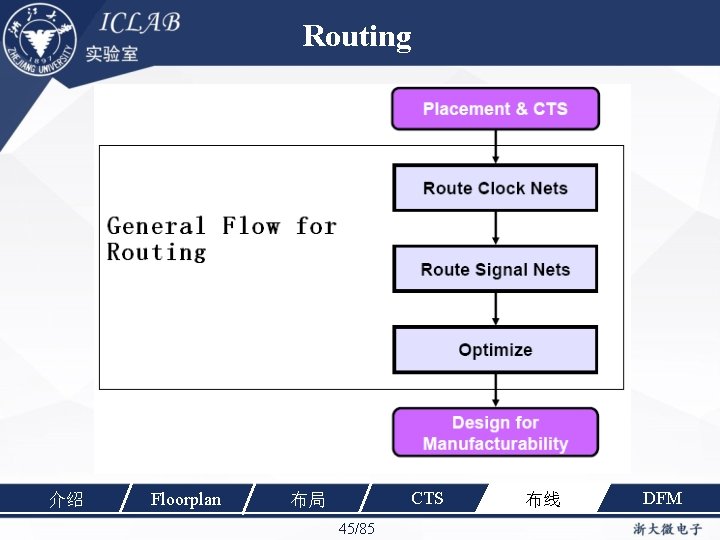

Routing 介绍 Floorplan CTS 布局 45/85 布线 DFM

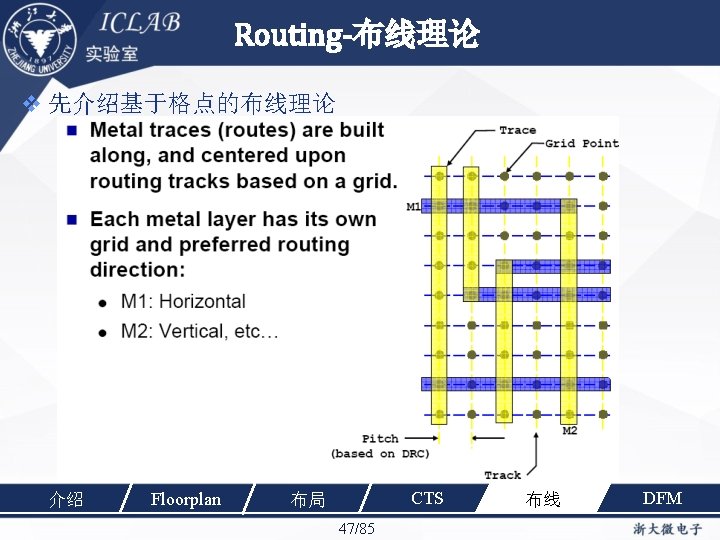

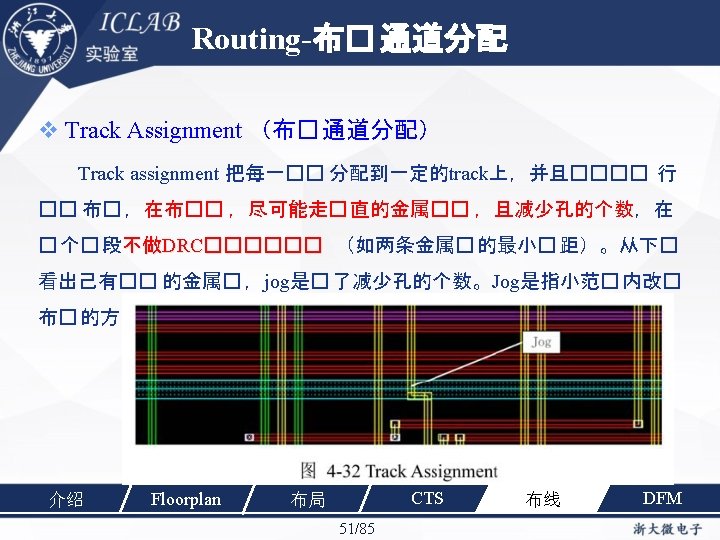

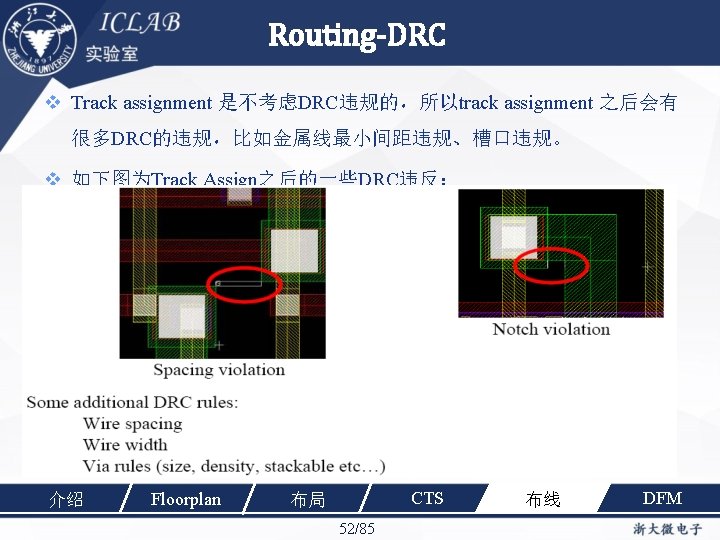

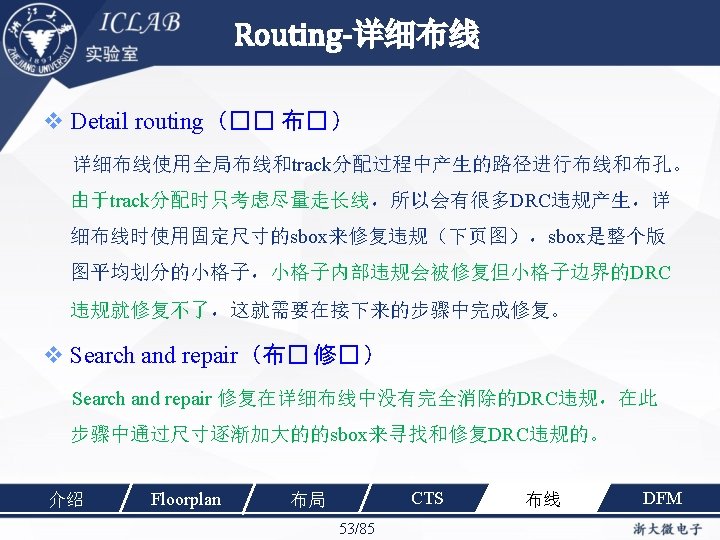

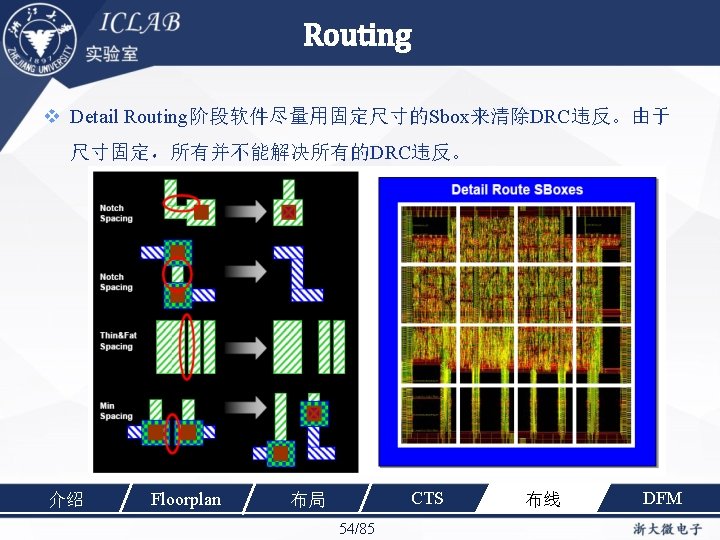

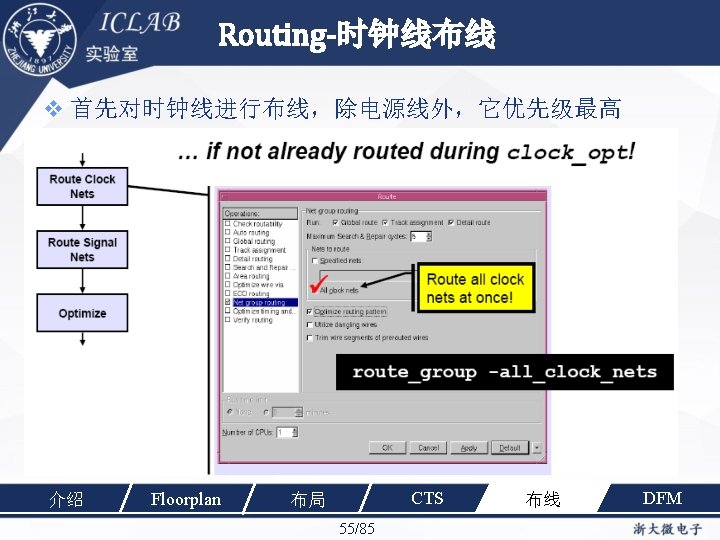

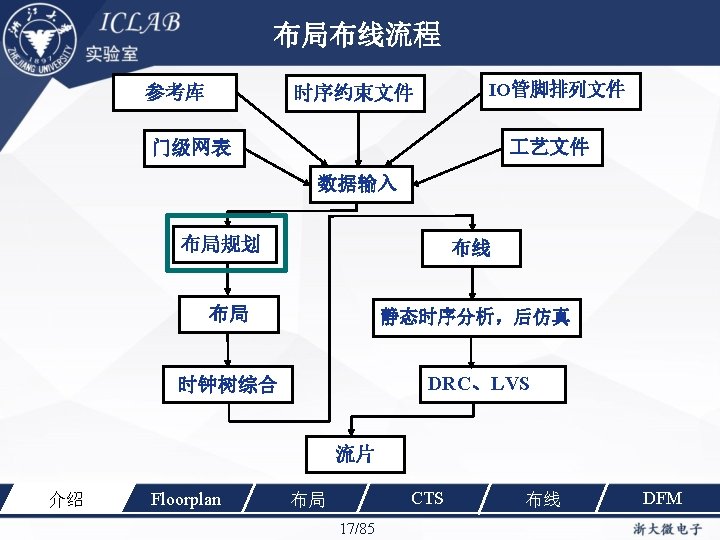

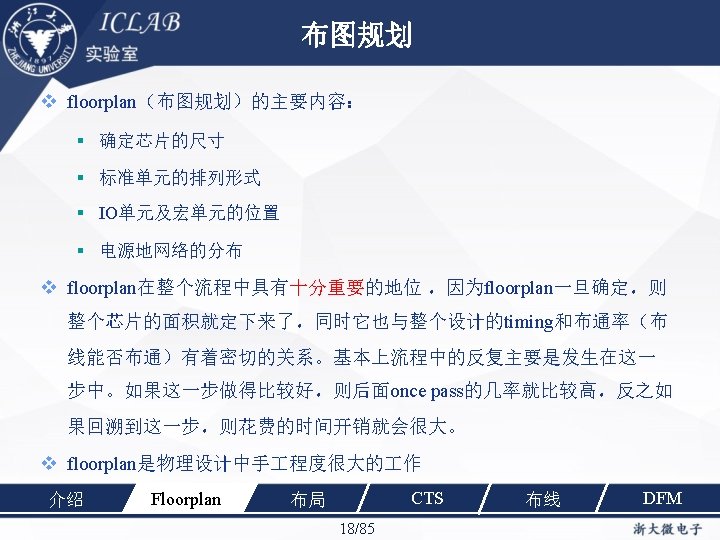

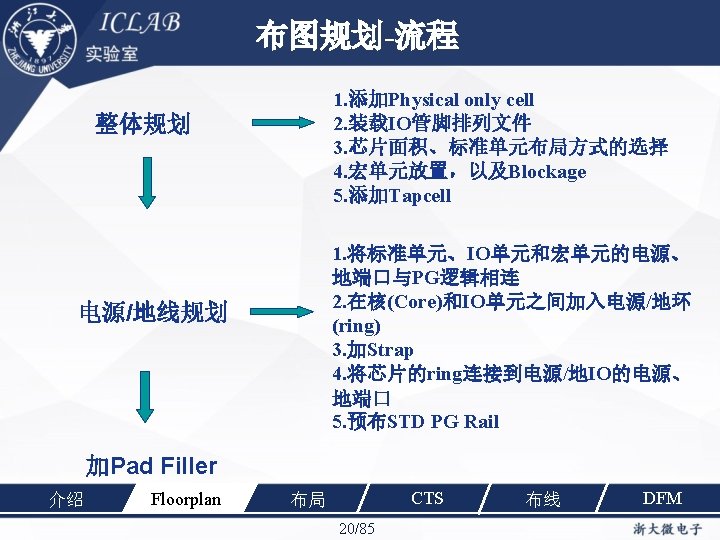

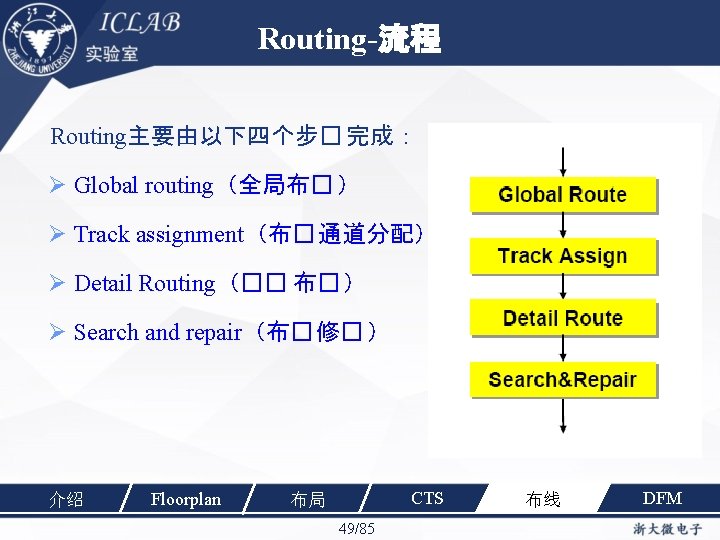

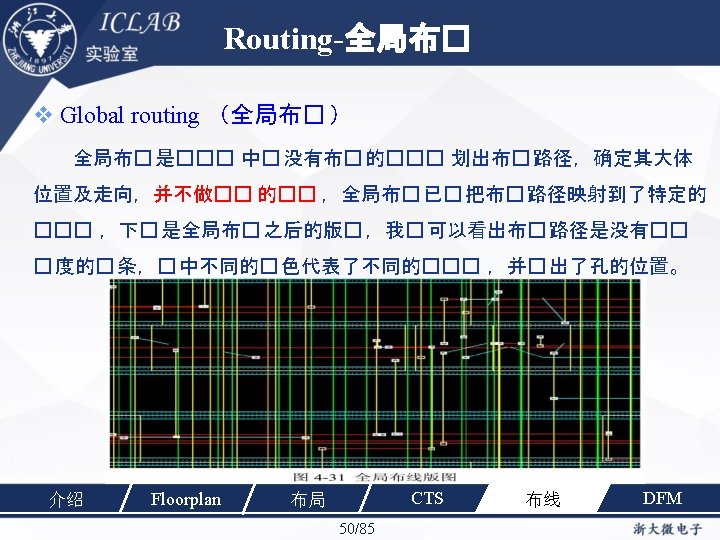

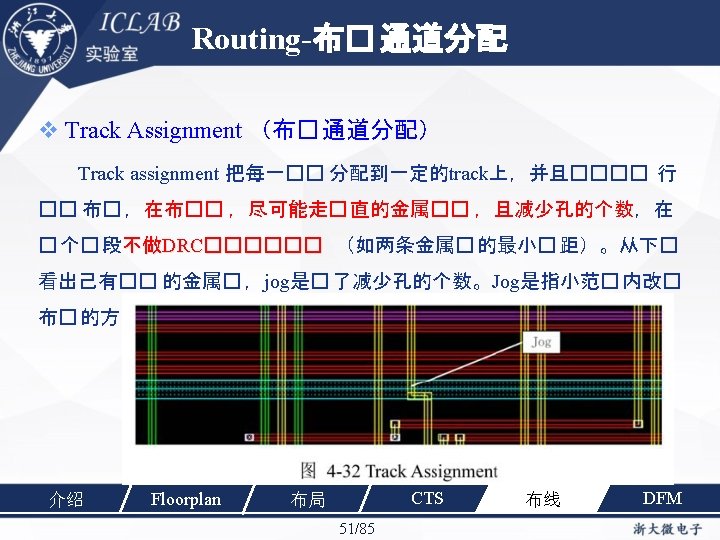

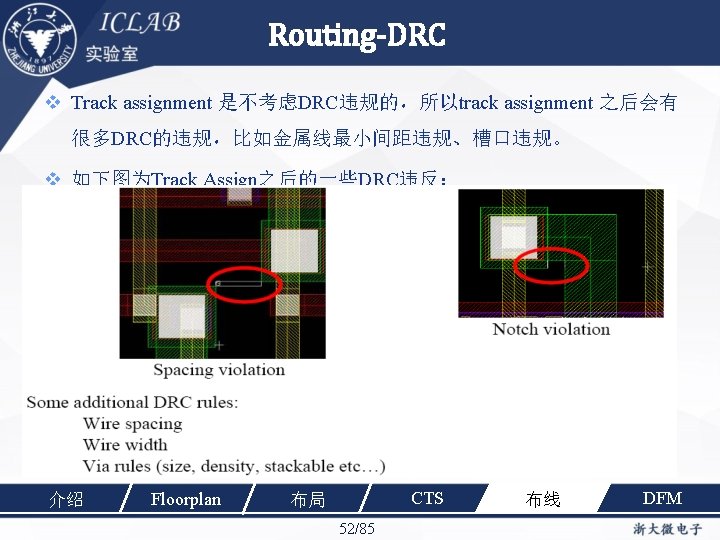

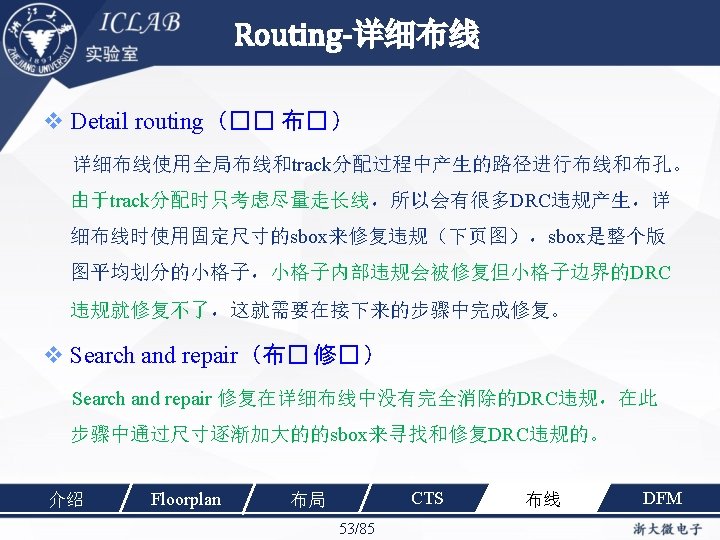

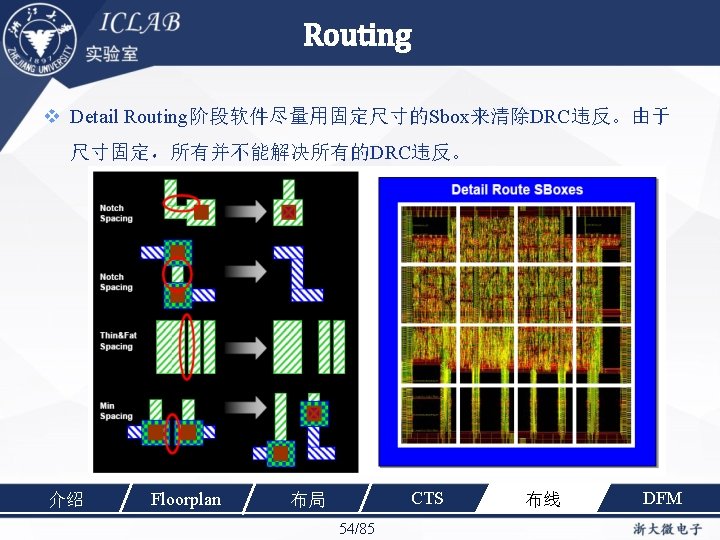

Routing-流程 Routing主要由以下四个步� 完成: Ø Global routing(全局布� ) Ø Track assignment(布� 通道分配) Ø Detail Routing(�� 布� ) Ø Search and repair(布� 修� ) 介绍 Floorplan CTS 布局 49/85 布线 DFM

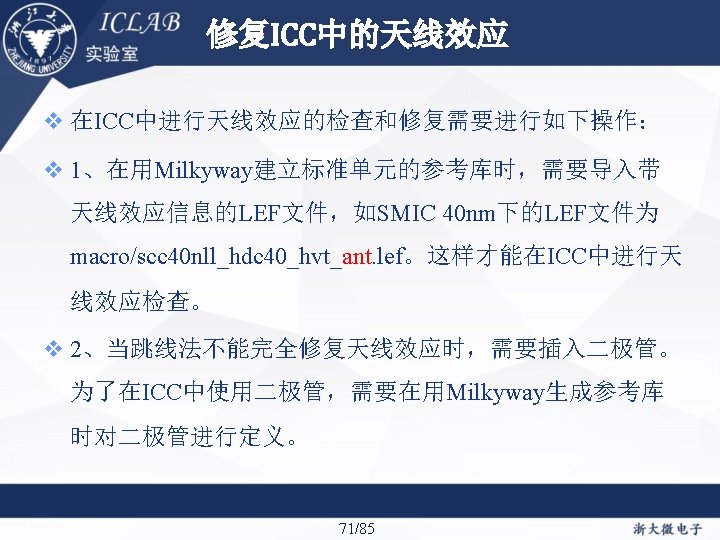

修复ICC中的天线效应 定义天线效应二极管的Milkyway命令: define lib. Id (db. Get. Current. Lib. Id) db. Convert. Port. To. Diode. Port lib. Id "F_DIODE 2_8 TH 40" "A" db. Convert. Port. To. Diode. Port lib. Id "F_DIODE 4_8 TH 40" "A" db. Convert. Port. To. Diode. Port lib. Id "F_DIODE 8_8 TH 40" "A" 72/85

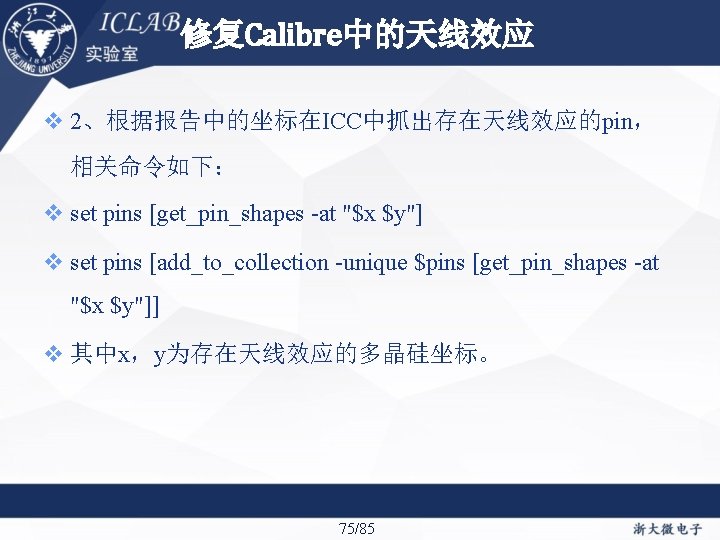

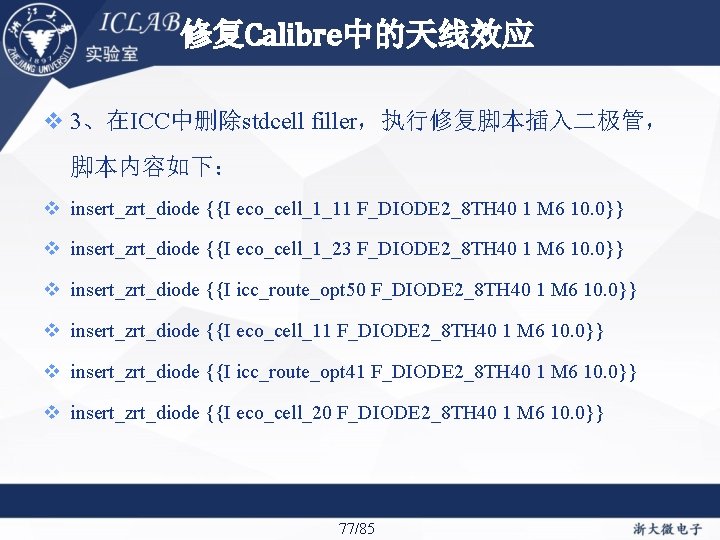

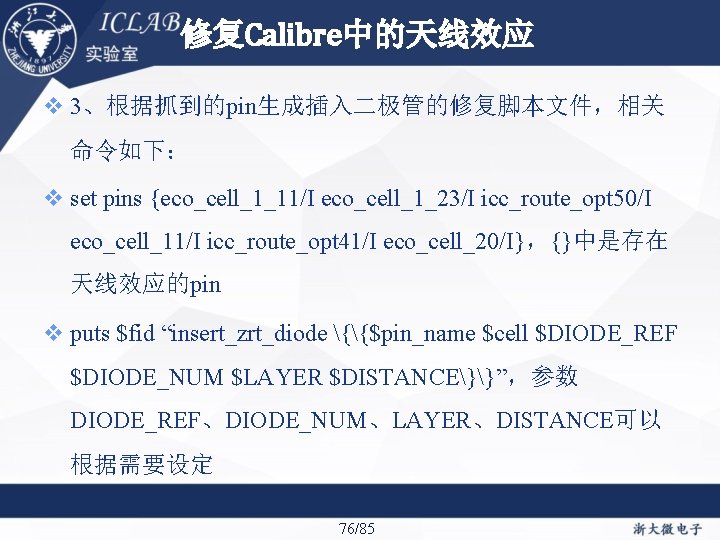

修复Calibre中的天线效应 3、根据抓到的pin生成插入二极管的修复脚本文件,相关 命令如下: set pins {eco_cell_1_11/I eco_cell_1_23/I icc_route_opt 50/I eco_cell_11/I icc_route_opt 41/I eco_cell_20/I},{}中是存在 天线效应的pin puts $fid “insert_zrt_diode {{$pin_name $cell $DIODE_REF $DIODE_NUM $LAYER $DISTANCE}}”,参数 DIODE_REF、DIODE_NUM、LAYER、DISTANCE可以 根据需要设定 76/85

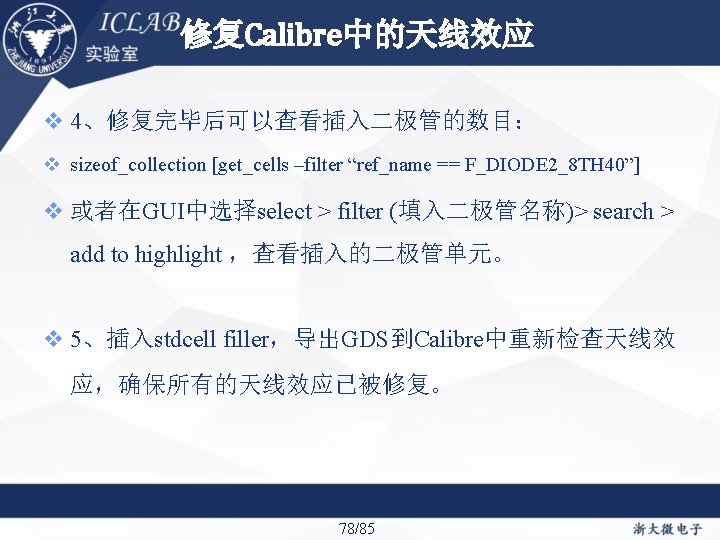

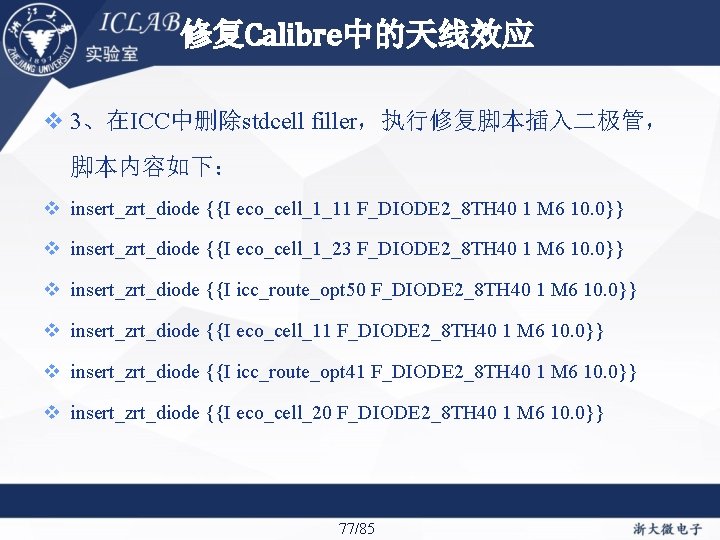

修复Calibre中的天线效应 3、在ICC中删除stdcell filler,执行修复脚本插入二极管, 脚本内容如下: insert_zrt_diode {{I eco_cell_1_11 F_DIODE 2_8 TH 40 1 M 6 10. 0}} insert_zrt_diode {{I eco_cell_1_23 F_DIODE 2_8 TH 40 1 M 6 10. 0}} insert_zrt_diode {{I icc_route_opt 50 F_DIODE 2_8 TH 40 1 M 6 10. 0}} insert_zrt_diode {{I eco_cell_11 F_DIODE 2_8 TH 40 1 M 6 10. 0}} insert_zrt_diode {{I icc_route_opt 41 F_DIODE 2_8 TH 40 1 M 6 10. 0}} insert_zrt_diode {{I eco_cell_20 F_DIODE 2_8 TH 40 1 M 6 10. 0}} 77/85

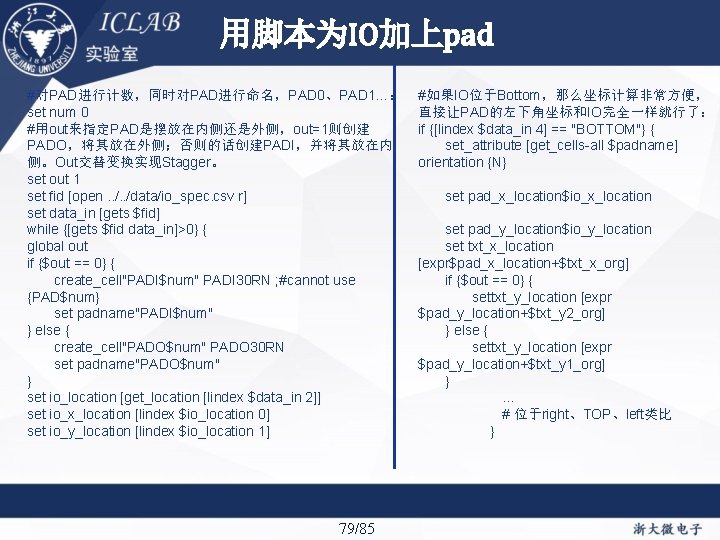

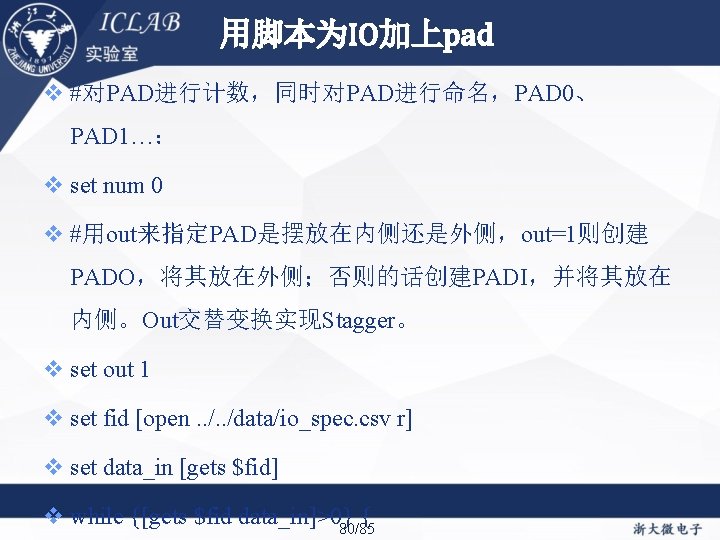

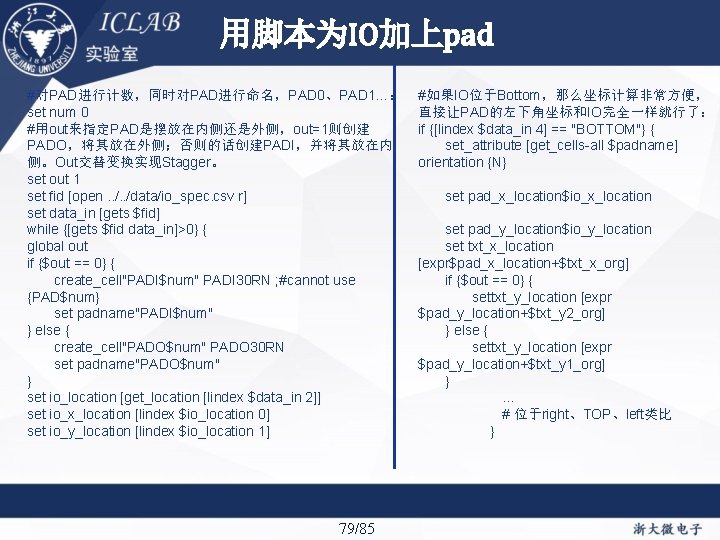

用脚本为IO加上pad #对PAD进行计数,同时对PAD进行命名,PAD 0、PAD 1…: set num 0 #用out来指定PAD是摆放在内侧还是外侧,out=1则创建 PADO,将其放在外侧;否则的话创建PADI,并将其放在内 侧。Out交替变换实现Stagger。 set out 1 set fid [open. . /data/io_spec. csv r] set data_in [gets $fid] while {[gets $fid data_in]>0} { global out if {$out == 0} { create_cell"PADI$num" PADI 30 RN ; #cannot use {PAD$num} set padname"PADI$num" } else { create_cell"PADO$num" PADO 30 RN set padname"PADO$num" } set io_location [get_location [lindex $data_in 2]] set io_x_location [lindex $io_location 0] set io_y_location [lindex $io_location 1] 79/85 #如果IO位于Bottom,那么坐标计算非常方便, 直接让PAD的左下角坐标和IO完全一样就行了: if {[lindex $data_in 4] == "BOTTOM"} { set_attribute [get_cells-all $padname] orientation {N} set pad_x_location$io_x_location set pad_y_location$io_y_location set txt_x_location [expr$pad_x_location+$txt_x_org] if {$out == 0} { settxt_y_location [expr $pad_y_location+$txt_y 2_org] } else { settxt_y_location [expr $pad_y_location+$txt_y 1_org] }. . . # 位于right、TOP、left类比 }

用脚本为IO加上pad #对PAD进行计数,同时对PAD进行命名,PAD 0、 PAD 1…: set num 0 #用out来指定PAD是摆放在内侧还是外侧,out=1则创建 PADO,将其放在外侧;否则的话创建PADI,并将其放在 内侧。Out交替变换实现Stagger。 set out 1 set fid [open. . /data/io_spec. csv r] set data_in [gets $fid] while {[gets $fid data_in]>0} { 80/85

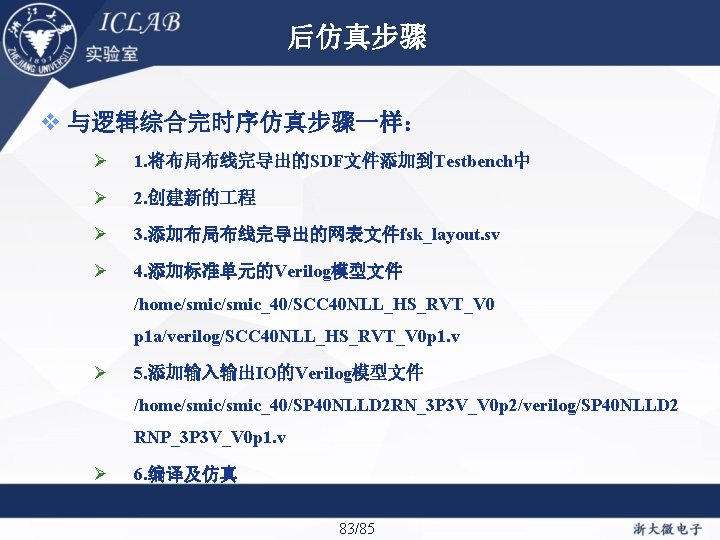

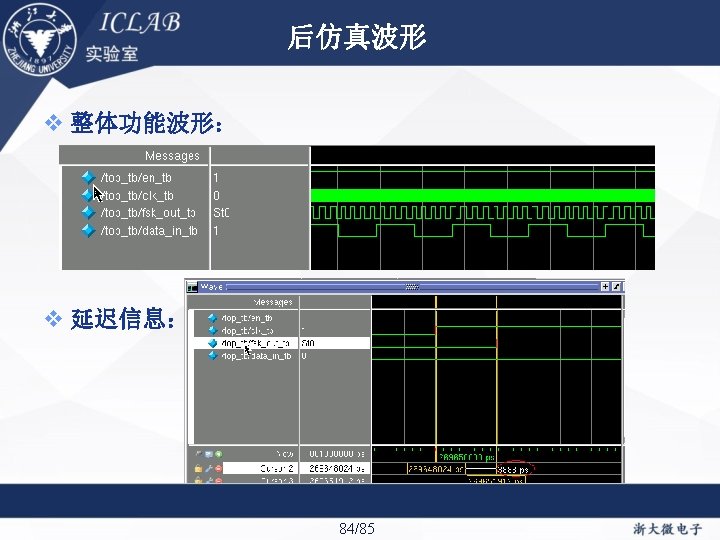

后仿真步骤 与逻辑综合完时序仿真步骤一样: Ø 1. 将布局布线完导出的SDF文件添加到Testbench中 Ø 2. 创建新的 程 Ø 3. 添加布局布线完导出的网表文件fsk_layout. sv Ø 4. 添加标准单元的Verilog模型文件 /home/smic_40/SCC 40 NLL_HS_RVT_V 0 p 1 a/verilog/SCC 40 NLL_HS_RVT_V 0 p 1. v Ø 5. 添加输入输出IO的Verilog模型文件 /home/smic_40/SP 40 NLLD 2 RN_3 P 3 V_V 0 p 2/verilog/SP 40 NLLD 2 RNP_3 P 3 V_V 0 p 1. v Ø 6. 编译及仿真 83/85

THANK YOU! 85/85