FloatingGate Circuits Systems and Adaptation Paul Hasler Integrated

![Drain-Gate Dynamic Equation W = 1 -h. E[Vg Vd] - e. W Drain-Gate Dynamic Equation W = 1 -h. E[Vg Vd] - e. W](https://slidetodoc.com/presentation_image/ae4eb7eb4244da2853188fc7c40dc3d6/image-25.jpg)

- Slides: 30

Floating-Gate Circuits, Systems, and Adaptation Paul Hasler Integrated Computational Electronics (ICE) Laboratory for Neural Engineering Georgia Institute of Technology

Things I don’t needed to cover Why use subthreshold devices? or can’t everything be built from op-amps and resistors? What are Floating-gate circuits? Why use neurobiology as inspiration for engineering systems? Where will this be used in an RF application?

Where we work

Laboratory for Neural Engineering Faculty: Robert Butera, Robert Cargill, Steve Deweerth, Bill Ditto, Paul Hasler, Michelle La. Placa Key Directions: • Neural Interfacing / Implants • Hybrid Neural-Silicon Systems / Computations • Neuromorphic Engineering

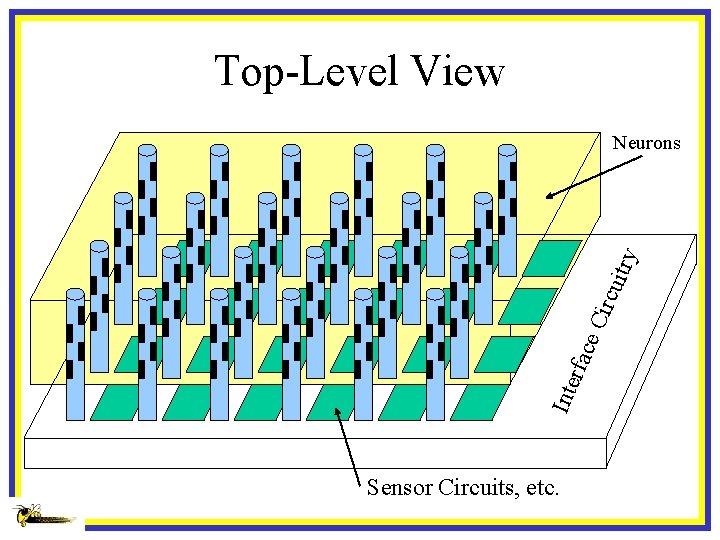

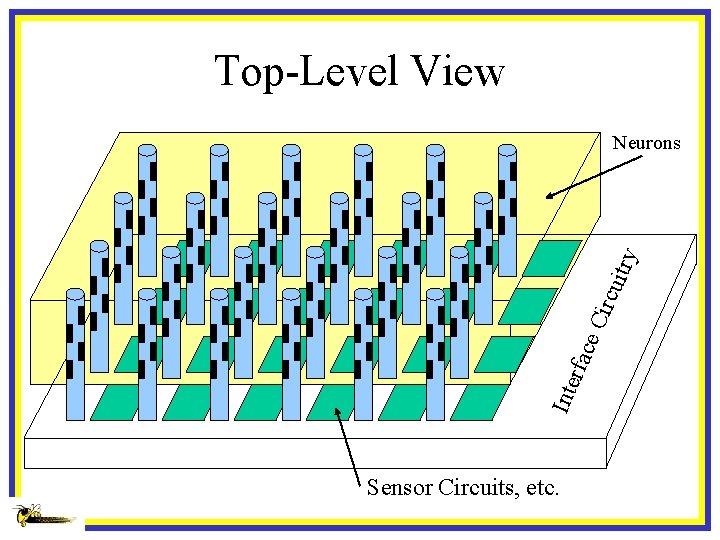

Top-Level View Inte rfac e. C ircu itry Neurons Sensor Circuits, etc.

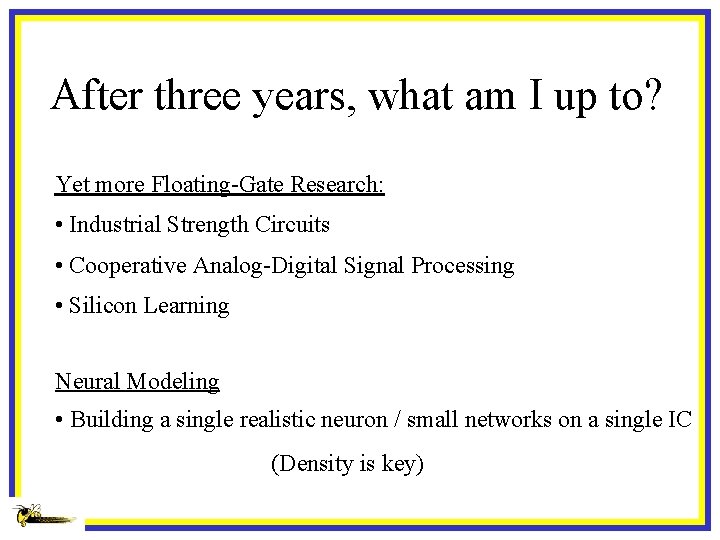

After three years, what am I up to? Yet more Floating-Gate Research: • Industrial Strength Circuits • Cooperative Analog-Digital Signal Processing • Silicon Learning Neural Modeling • Building a single realistic neuron / small networks on a single IC (Density is key)

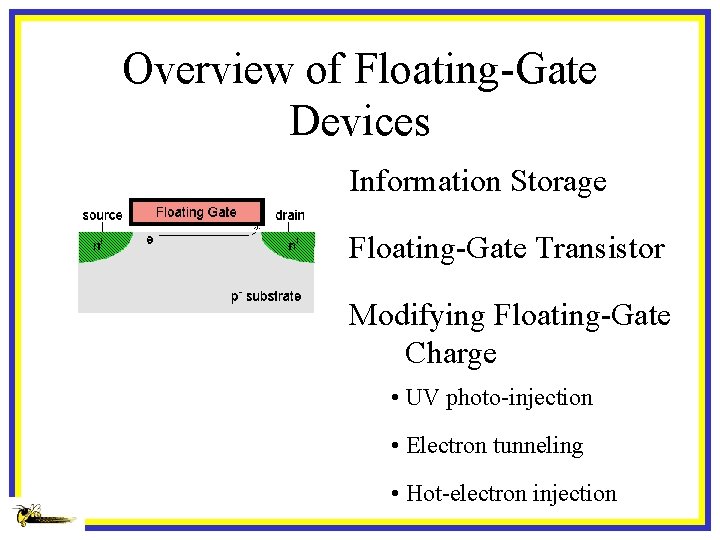

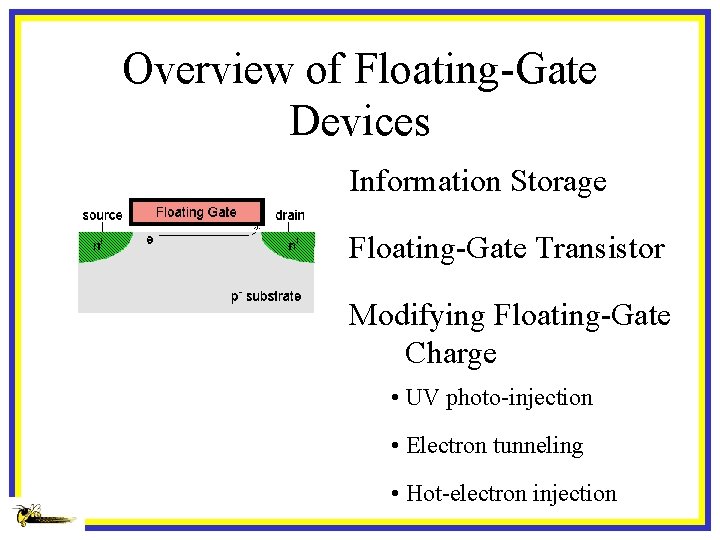

Overview of Floating-Gate Devices Information Storage Floating-Gate Transistor Modifying Floating-Gate Charge • UV photo-injection • Electron tunneling • Hot-electron injection

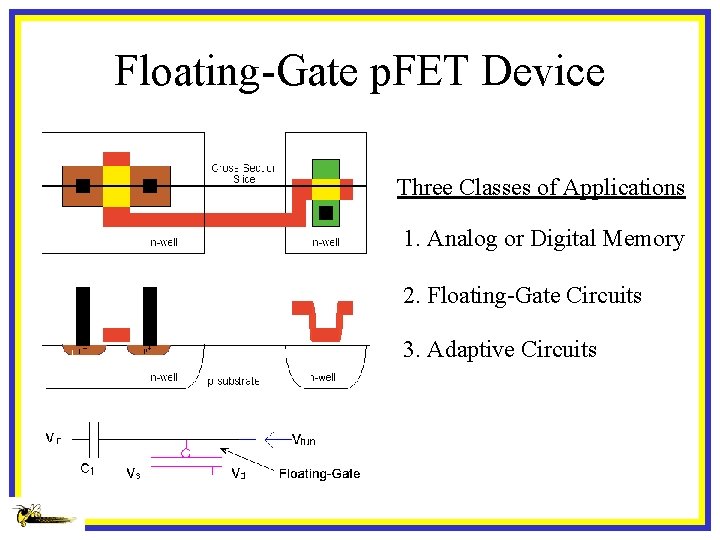

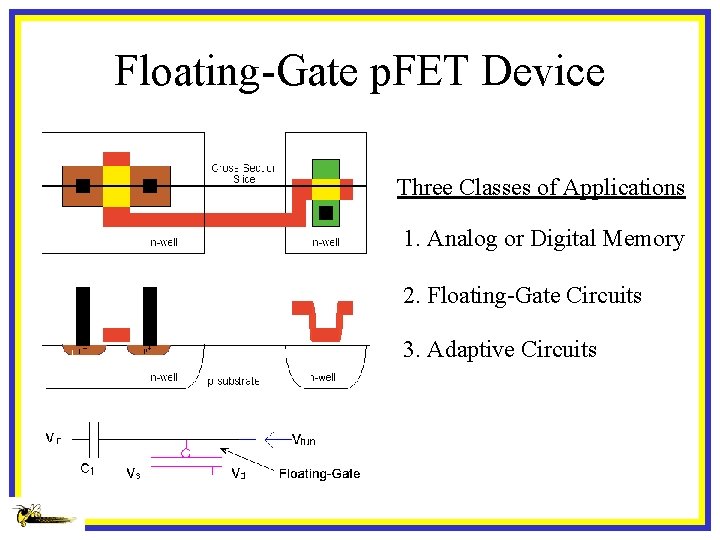

Floating-Gate p. FET Device Three Classes of Applications 1. Analog or Digital Memory 2. Floating-Gate Circuits 3. Adaptive Circuits

World of Floating-Gate Circuits

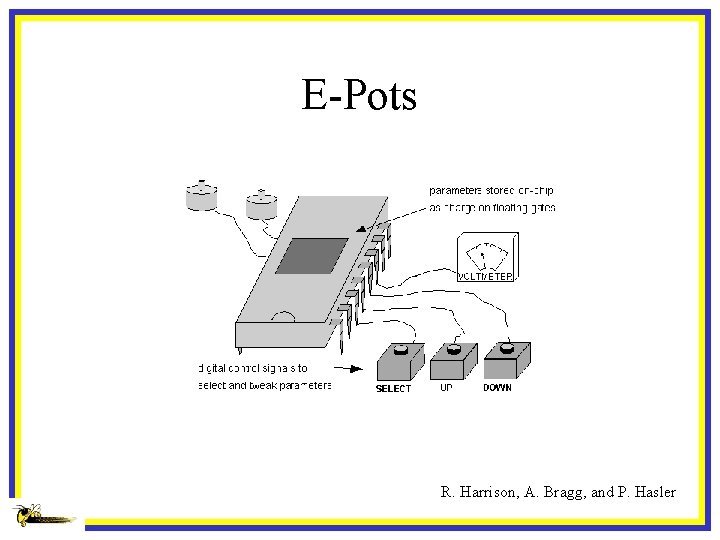

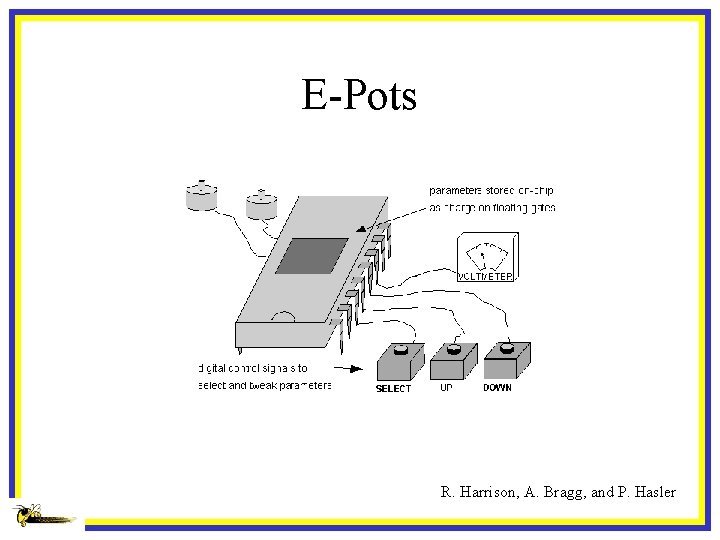

E-Pots R. Harrison, A. Bragg, and P. Hasler

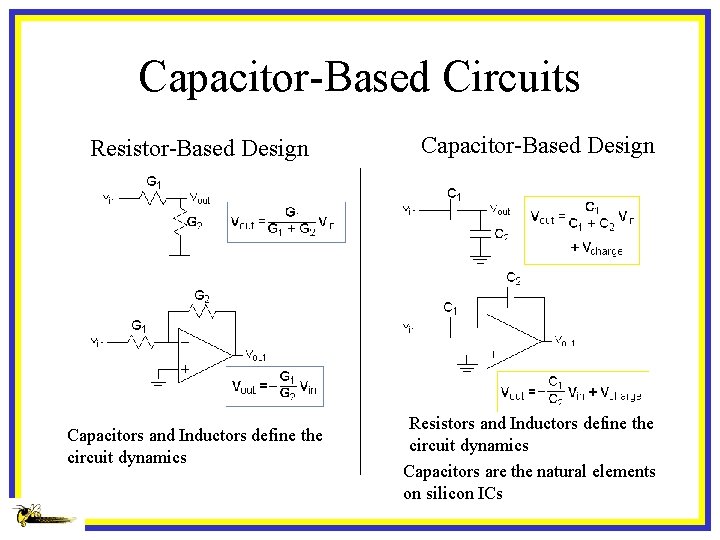

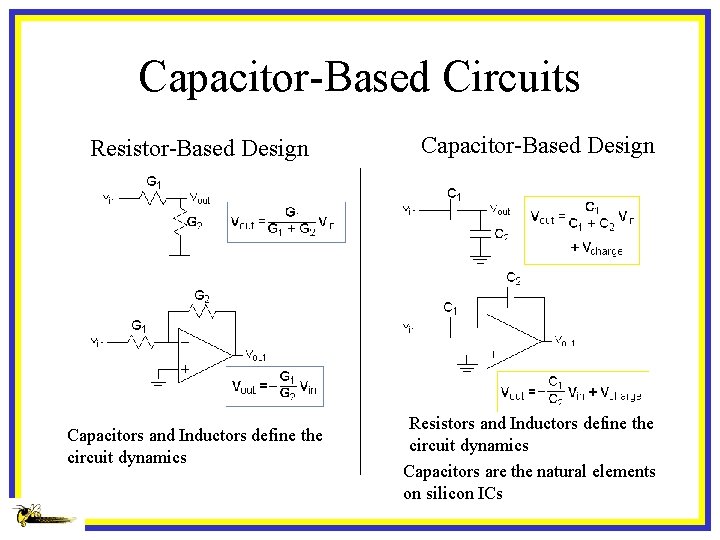

Capacitor-Based Circuits Resistor-Based Design Capacitors and Inductors define the circuit dynamics Capacitor-Based Design Resistors and Inductors define the circuit dynamics Capacitors are the natural elements on silicon ICs

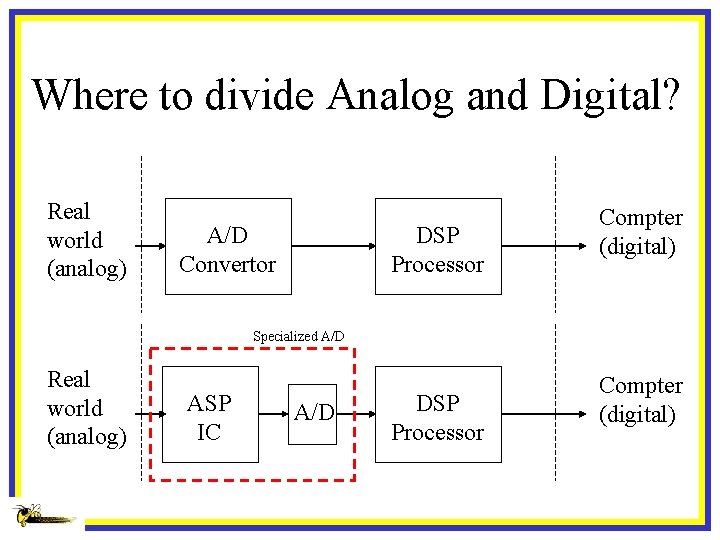

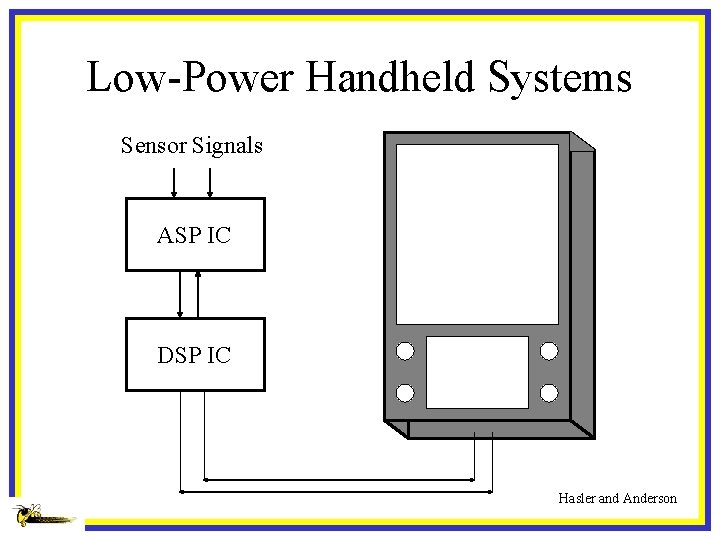

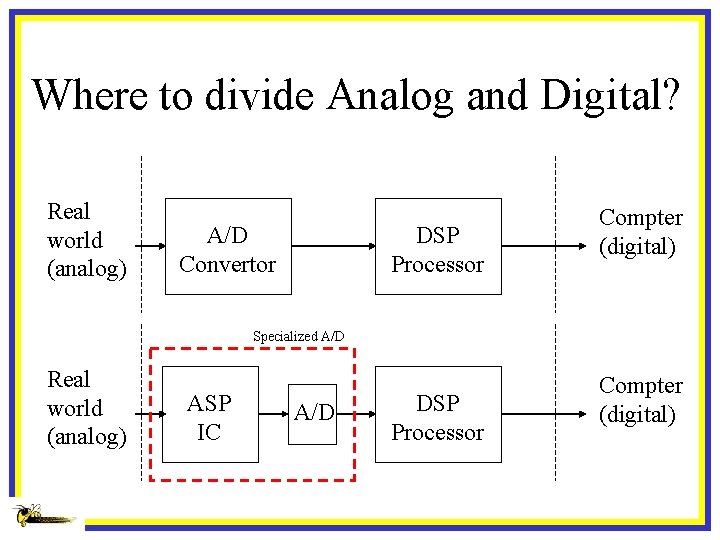

Where to divide Analog and Digital? Real world (analog) A/D Convertor DSP Processor Compter (digital) Specialized A/D Real world (analog) ASP IC A/D DSP Processor Compter (digital)

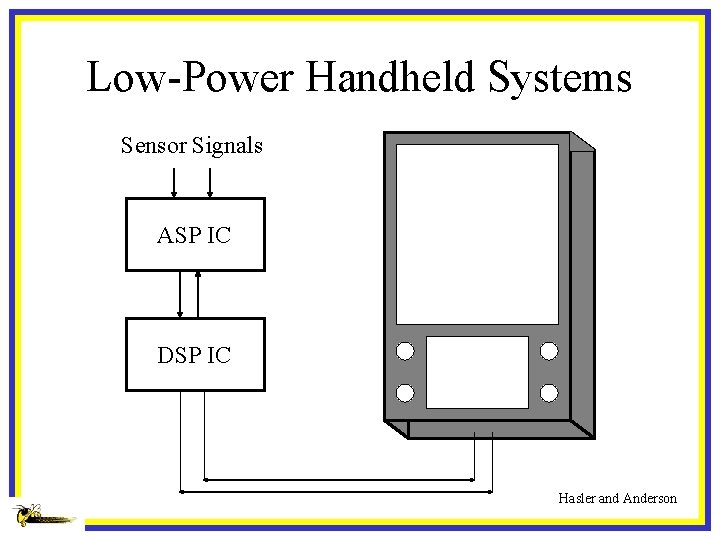

Low-Power Handheld Systems Sensor Signals ASP IC DSP IC Hasler and Anderson

Analog Computing Arrays

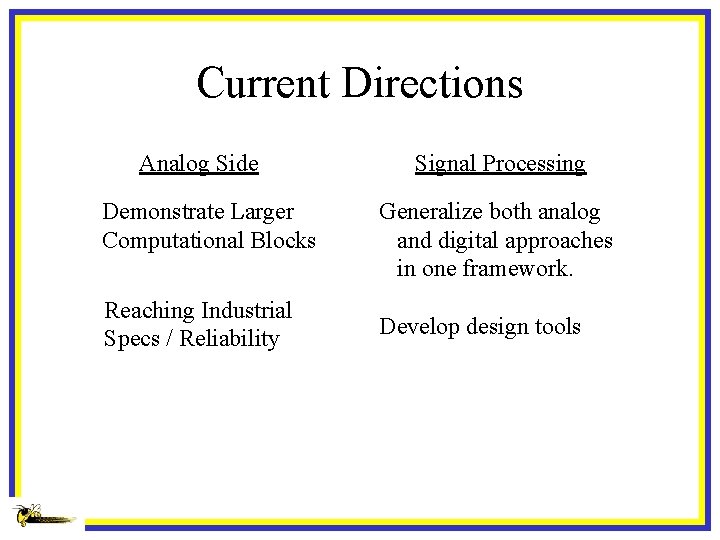

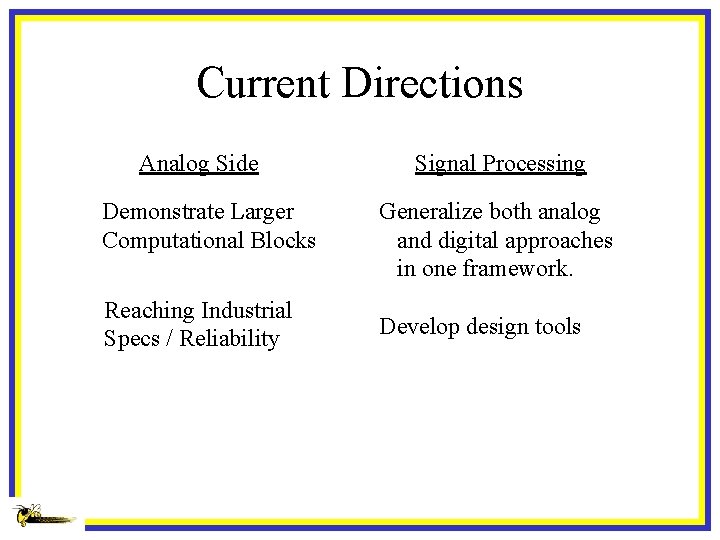

Current Directions Analog Side Demonstrate Larger Computational Blocks Reaching Industrial Specs / Reliability Signal Processing Generalize both analog and digital approaches in one framework. Develop design tools

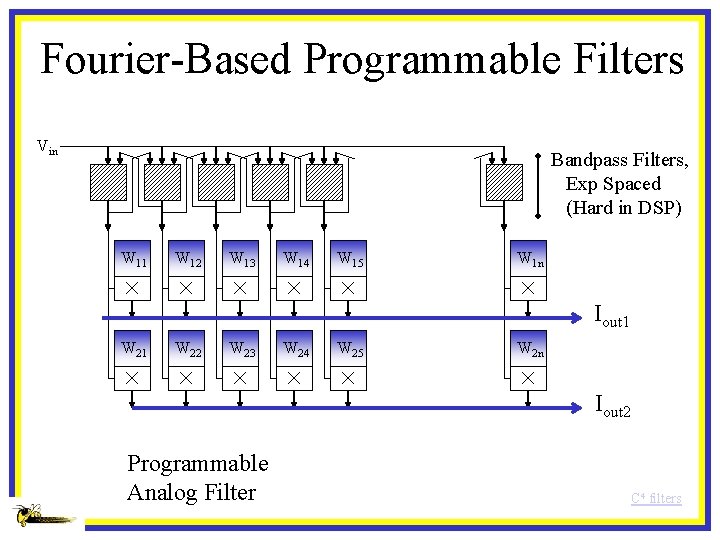

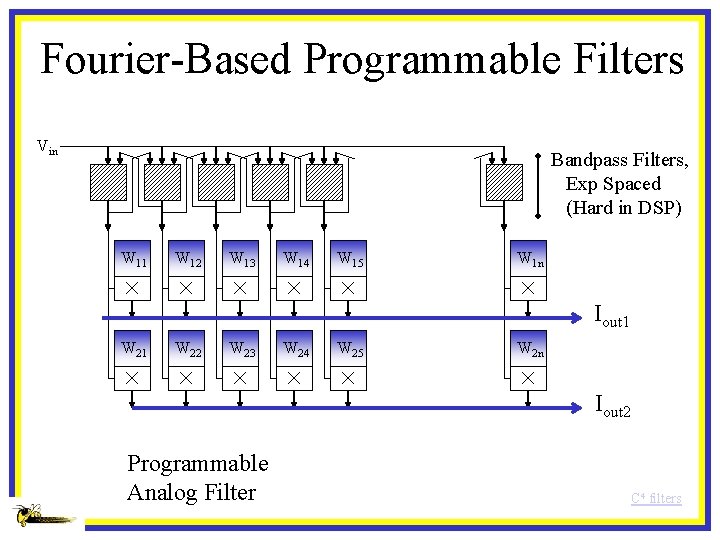

Fourier-Based Programmable Filters Vin Bandpass Filters, Exp Spaced (Hard in DSP) W 11 W 12 W 13 W 14 W 15 W 1 n Iout 1 W 22 W 23 W 24 W 25 W 2 n Iout 2 Programmable Analog Filter C 4 filters

Basic Programming Structure

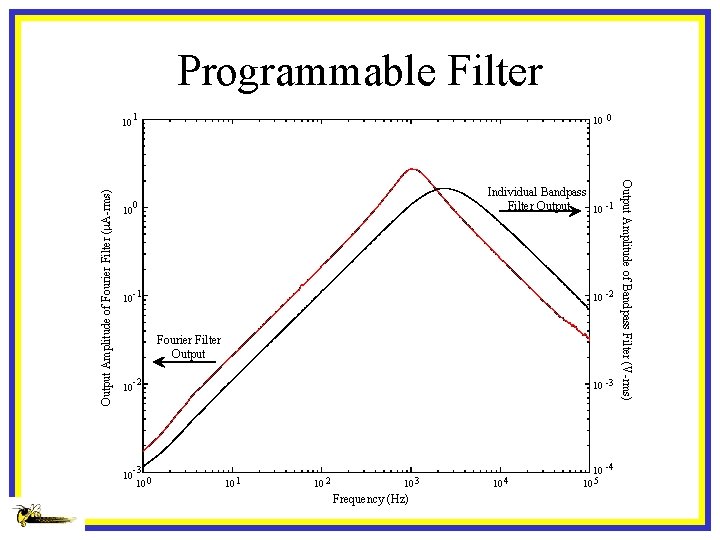

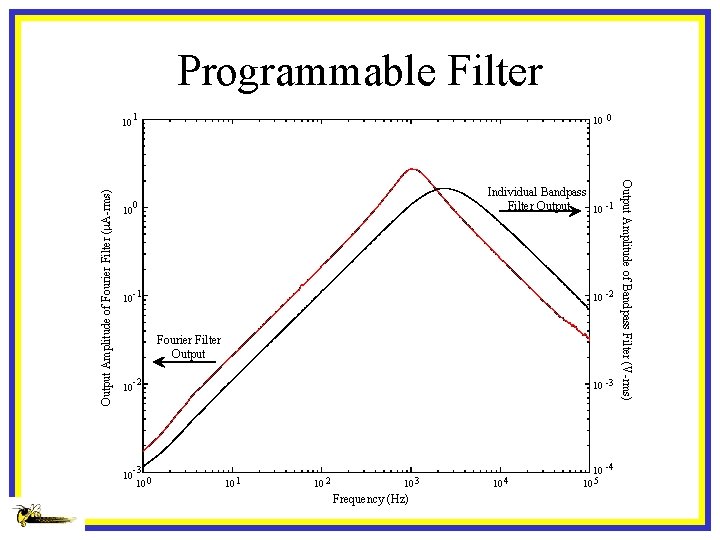

Programmable Filter 10 10 1 10 0 0 Individual Bandpass Filter Output 10 -1 -1 10 -2 Fourier Filter Output 10 10 -2 -3 10 0 10 -3 10 1 10 2 10 3 Frequency (Hz) 10 4 10 -4 10 5 Output Amplitude of Bandpass Filter (V-rms) Output Amplitude of Fourier Filter (m. A-rms) 10

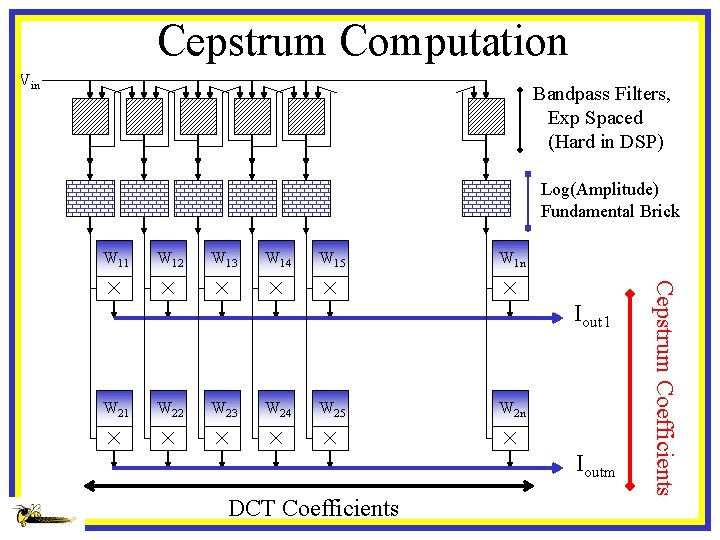

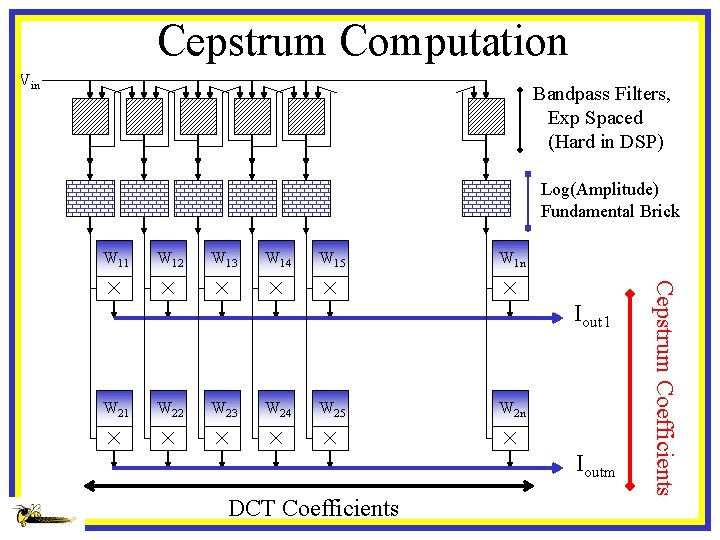

Cepstrum Computation Vin Bandpass Filters, Exp Spaced (Hard in DSP) Log(Amplitude) Fundamental Brick W 11 W 12 W 13 W 14 W 15 W 1 n W 21 W 22 W 23 W 24 W 25 W 2 n Ioutm DCT Coefficients Cepstrum Coefficients Iout 1

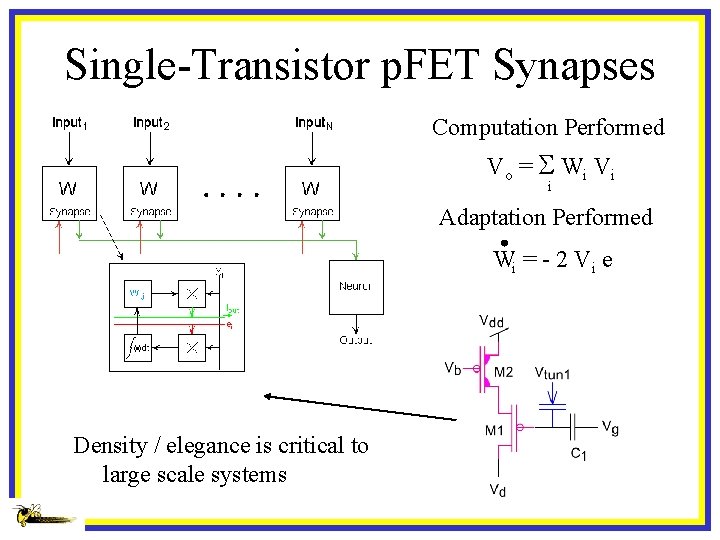

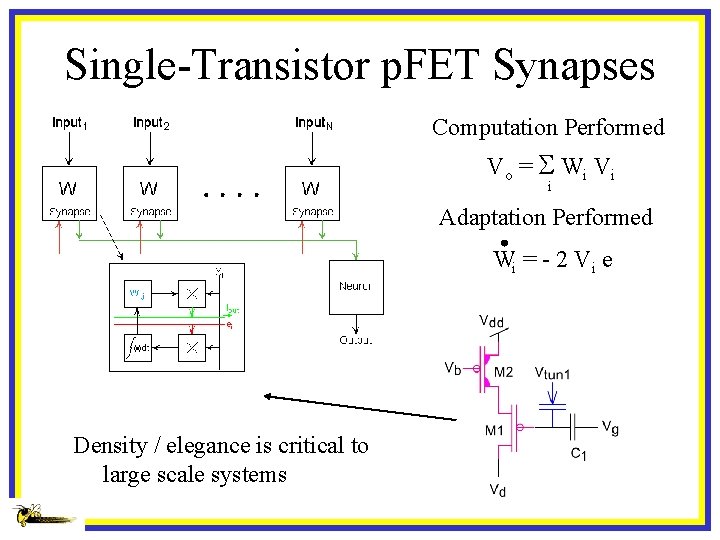

Single-Transistor p. FET Synapses Computation Performed Vo = S W i Vi i Adaptation Performed Wi = - 2 Vi e Density / elegance is critical to large scale systems

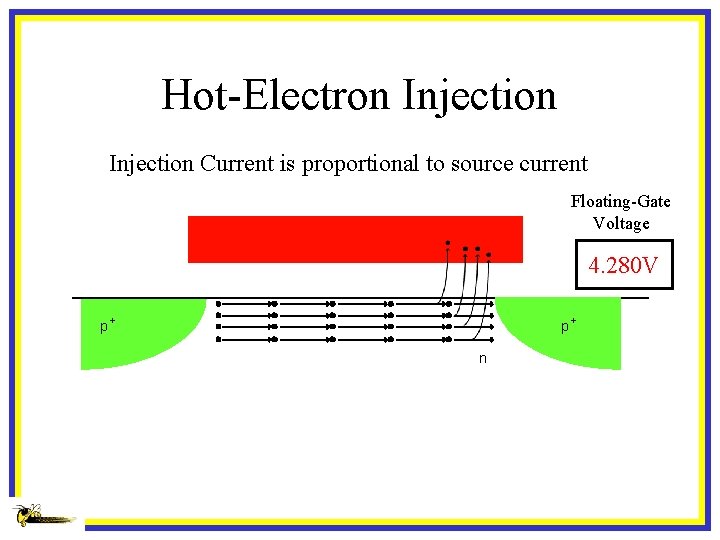

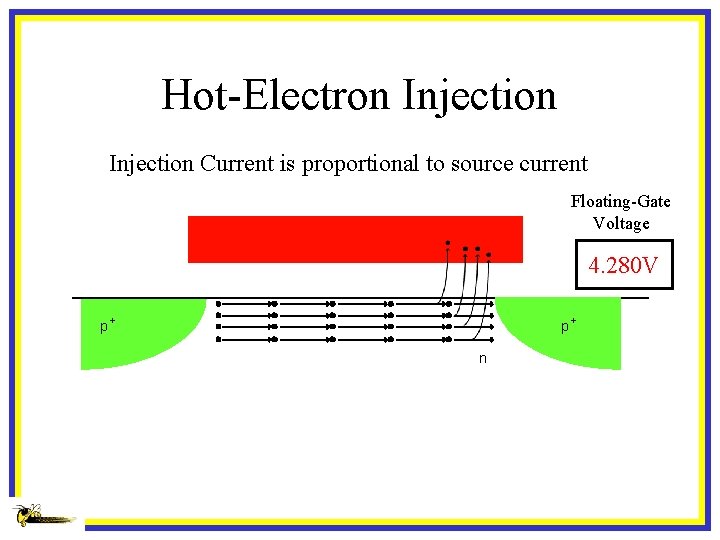

Hot-Electron Injection Current is proportional to source current Floating-Gate Voltage 4. 319 V 4. 351 V 4. 280 V 4. 352 V p+ p+ n

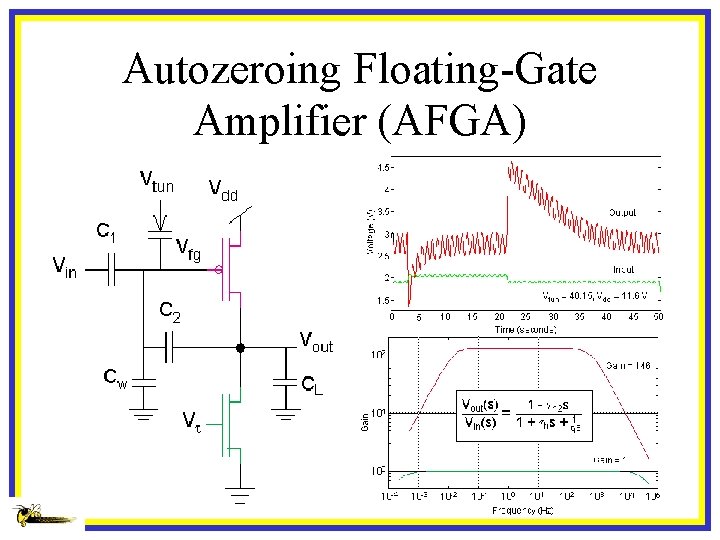

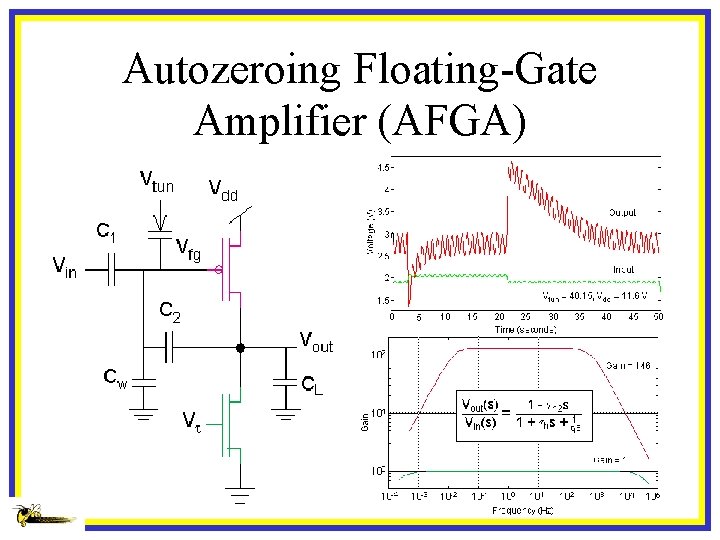

Autozeroing Floating-Gate Amplifier (AFGA)

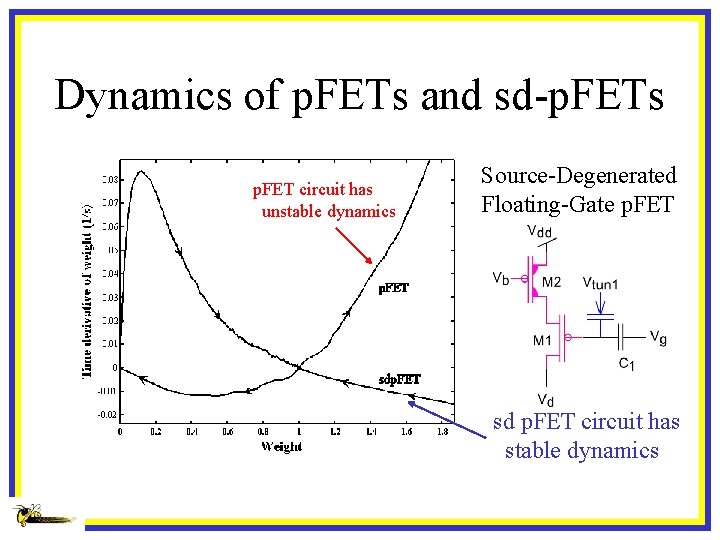

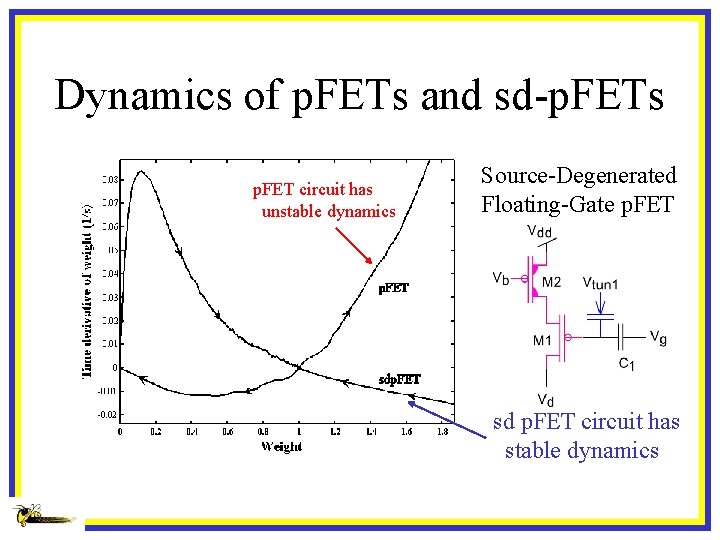

Dynamics of p. FETs and sd-p. FETs p. FET circuit has unstable dynamics Source-Degenerated Floating-Gate p. FET sd p. FET circuit has stable dynamics

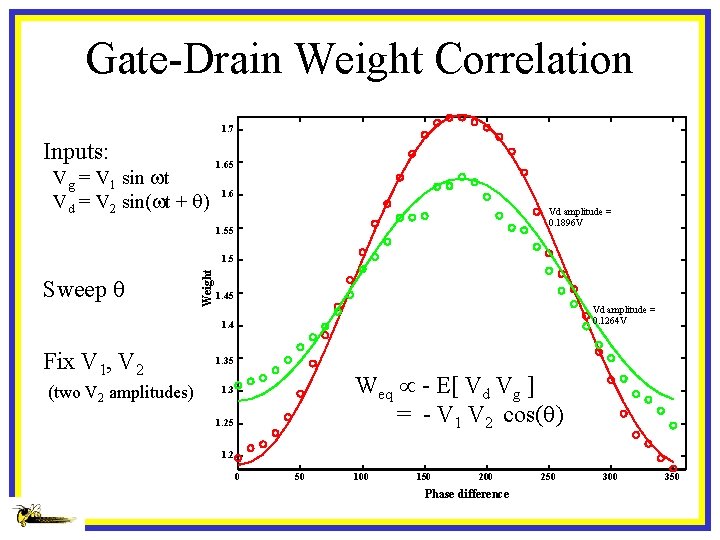

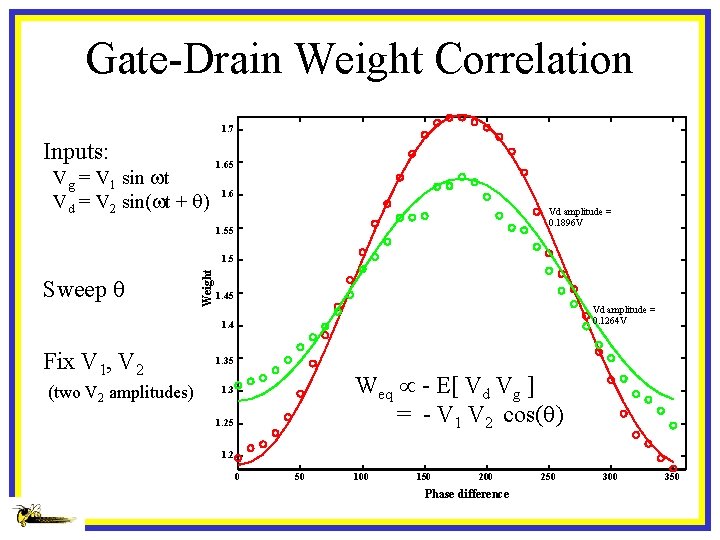

Gate-Drain Weight Correlation 1. 7 Inputs: Vg = V 1 sin wt Vd = V 2 sin(wt + q) 1. 65 1. 6 Vd amplitude = 0. 1896 V 1. 55 Sweep q Weight 1. 5 1. 45 Vd amplitude = 0. 1264 V 1. 4 Fix V 1, V 2 (two V 2 amplitudes) 1. 35 Weq - E[ Vd Vg ] = - V 1 V 2 cos(q) 1. 3 1. 25 1. 2 0 50 100 150 200 Phase difference 250 300 350

![DrainGate Dynamic Equation W 1 h EVg Vd e W Drain-Gate Dynamic Equation W = 1 -h. E[Vg Vd] - e. W](https://slidetodoc.com/presentation_image/ae4eb7eb4244da2853188fc7c40dc3d6/image-25.jpg)

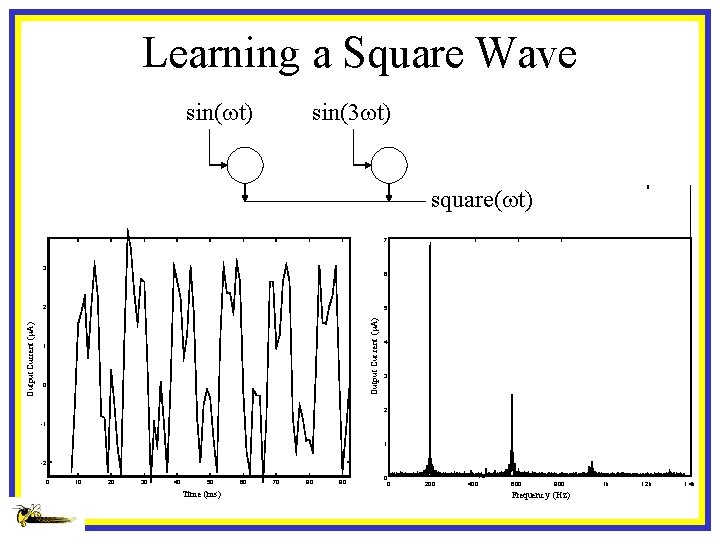

Drain-Gate Dynamic Equation W = 1 -h. E[Vg Vd] - e. W

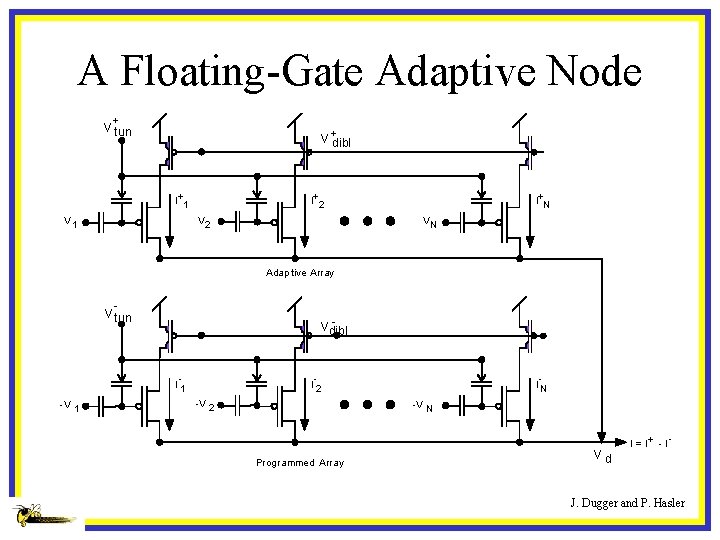

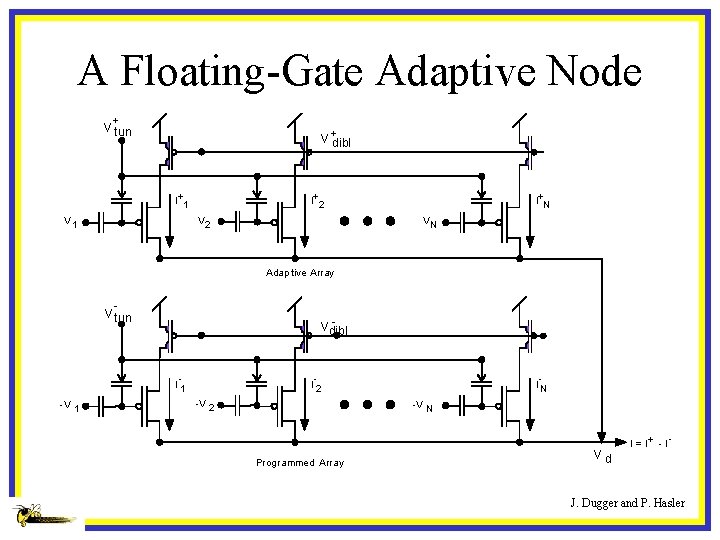

A Floating-Gate Adaptive Node + V tun V +dibl I+1 I+2 V 1 I+N VN Adap tive Array V tun Vdibl I 1 -V 1 I 2 -V 2 IN -V N Progr ammed Array Vd I = I+ - I J. Dugger and P. Hasler

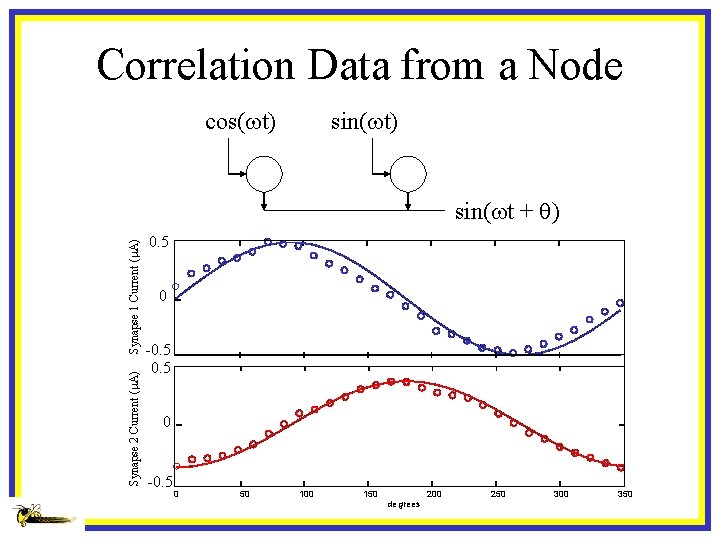

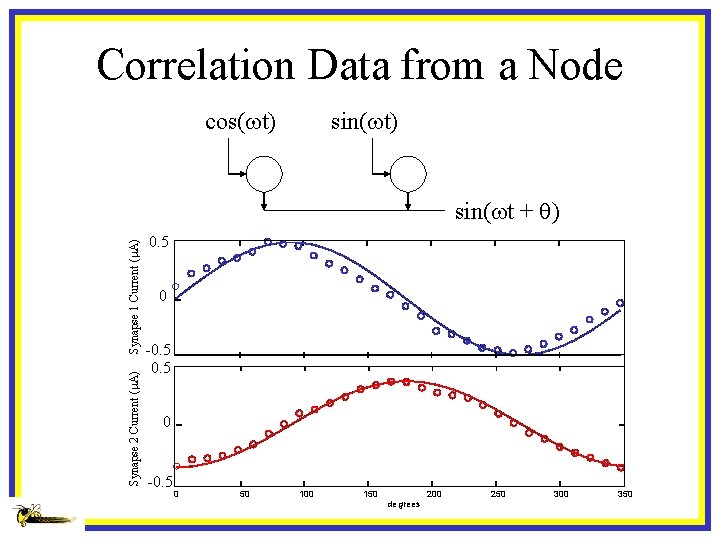

Correlation Data from a Node cos(wt) sin(wt) Synapse 2 Current (m. A) Synapse 1 Current (m. A) sin(wt + q) 0. 5 0 -0. 5 0 50 100 150 degrees 200 250 300 350

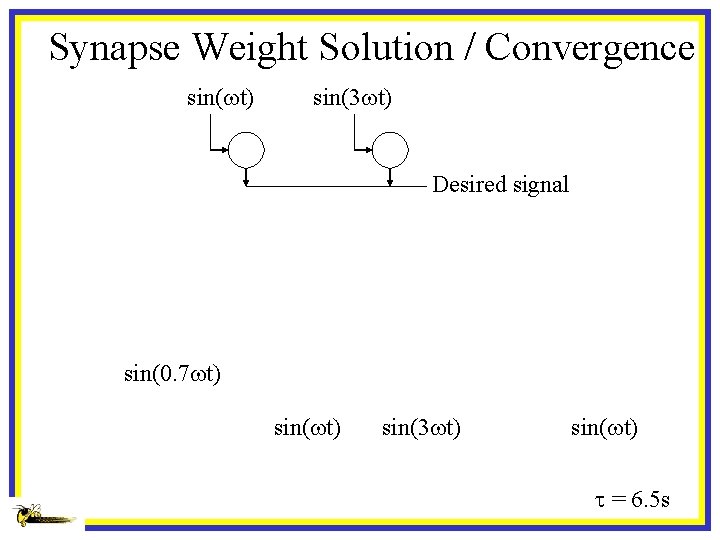

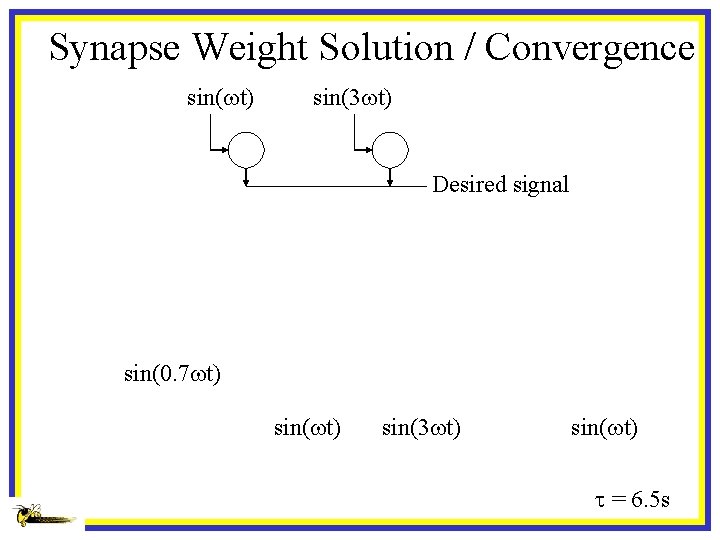

Synapse Weight Solution / Convergence sin(wt) sin(3 wt) Desired signal sin(0. 7 wt) sin(3 wt) sin(wt) t = 6. 5 s

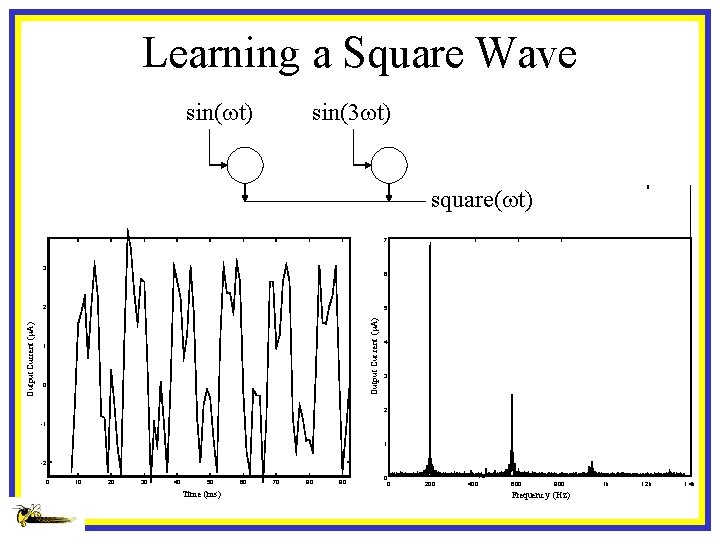

Learning a Square Wave sin(wt) sin(3 wt) square(wt) 7 3 6 5 Outpu t Cur rent (m. A) Output Current (m. A) 2 1 0 4 3 2 -1 1 -2 0 10 20 30 40 50 Time (ms) 60 70 80 90 0 0 200 400 600 800 Frequenc y (Hz) 1 k 1. 2 k 1. 4 k

Conclusions • Floating-Gate Devices / Circuits are starting to move towards the system level, and are moving towards industrial standards / not user hostile • We can not only build adaptive Floating-Gate circuits, but floating-gate circuits that adapt as a function of input “statistics”. • Floating-gate Systems are becoming important tools in neuromorphic modeling