FLIPPED CLASSROOM ACTIVITY IDP in Educational Technology IIT

- Slides: 25

FLIPPED CLASSROOM ACTIVITY IDP in Educational Technology, IIT Bombay

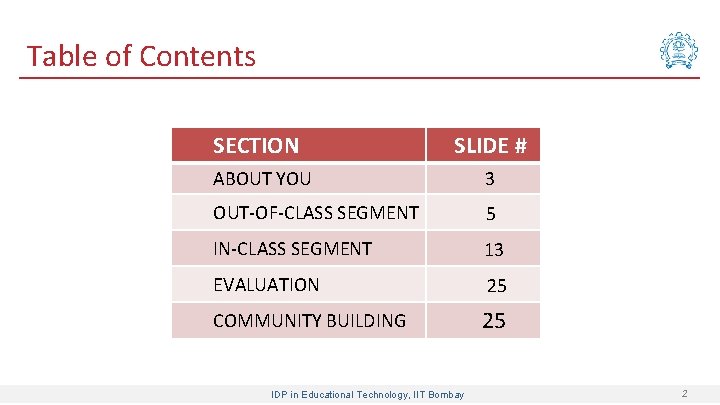

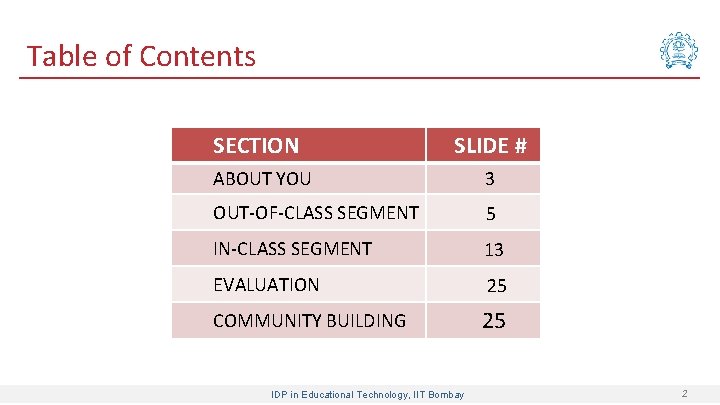

Table of Contents SECTION SLIDE # ABOUT YOU 3 OUT-OF-CLASS SEGMENT 5 IN-CLASS SEGMENT 13 EVALUATION 25 COMMUNITY BUILDING 25 IDP in Educational Technology, IIT Bombay 2

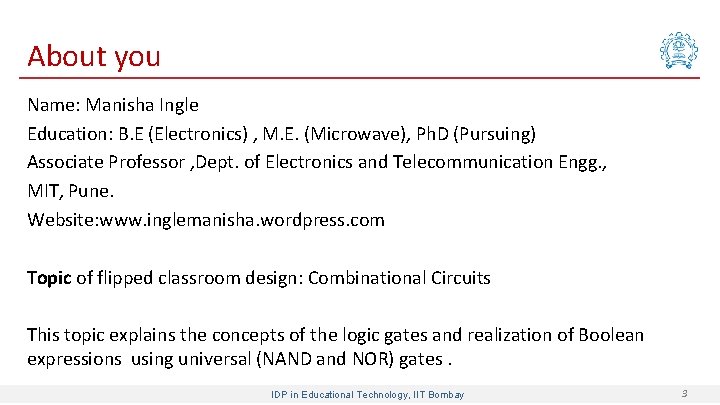

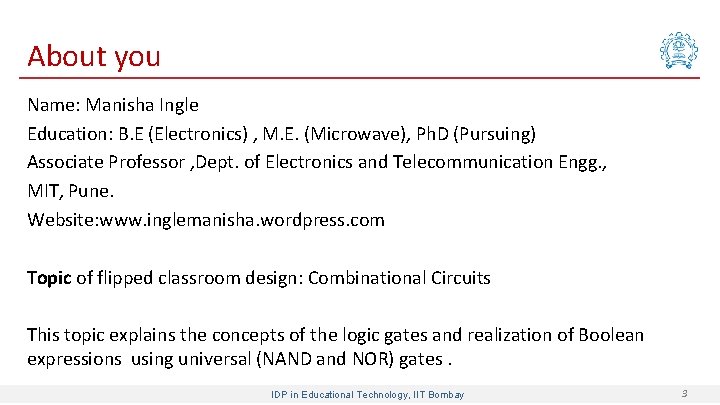

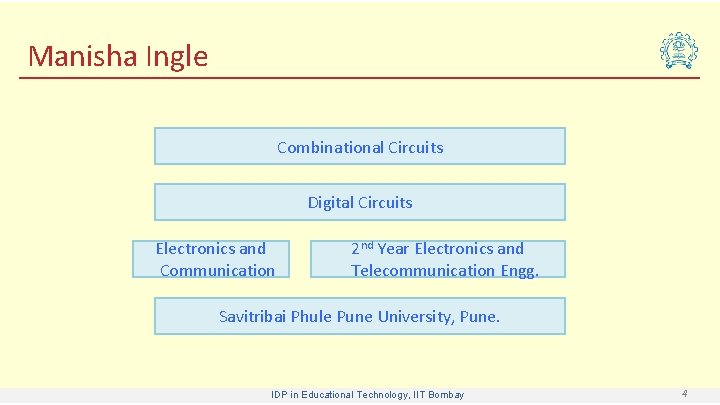

About you Name: Manisha Ingle Education: B. E (Electronics) , M. E. (Microwave), Ph. D (Pursuing) Associate Professor , Dept. of Electronics and Telecommunication Engg. , MIT, Pune. Website: www. inglemanisha. wordpress. com Topic of flipped classroom design: Combinational Circuits This topic explains the concepts of the logic gates and realization of Boolean expressions using universal (NAND and NOR) gates. IDP in Educational Technology, IIT Bombay 3

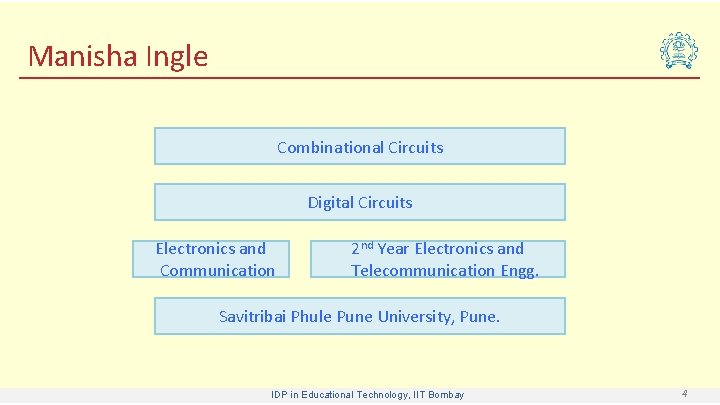

Manisha Ingle Combinational Circuits Digital Circuits Electronics and Communication 2 nd Year Electronics and Telecommunication Engg. Savitribai Phule Pune University, Pune. IDP in Educational Technology, IIT Bombay 4

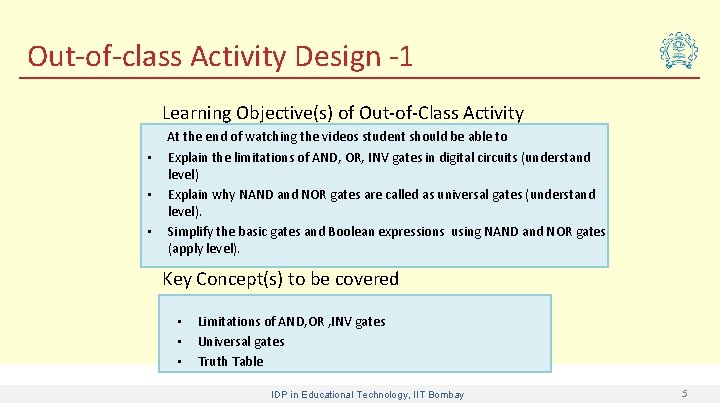

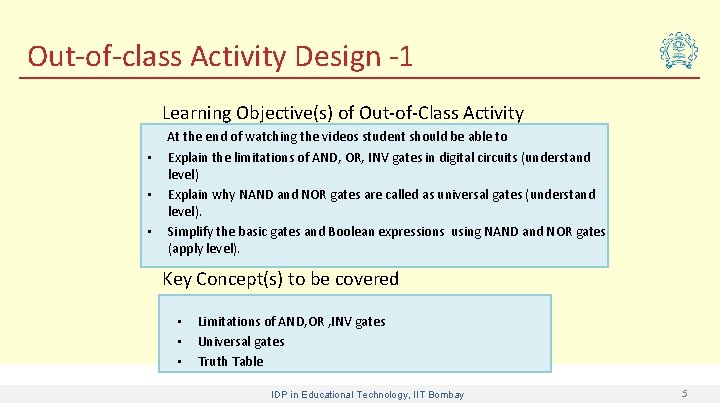

Out-of-class Activity Design -1 Learning Objective(s) of Out-of-Class Activity At the end of watching the videos student should be able to • • • Explain the limitations of AND, OR, INV gates in digital circuits (understand level) Explain why NAND and NOR gates are called as universal gates (understand level). Simplify the basic gates and Boolean expressions using NAND and NOR gates (apply level). Key Concept(s) to be covered • • • Limitations of AND, OR , INV gates Universal gates Truth Table IDP in Educational Technology, IIT Bombay 5

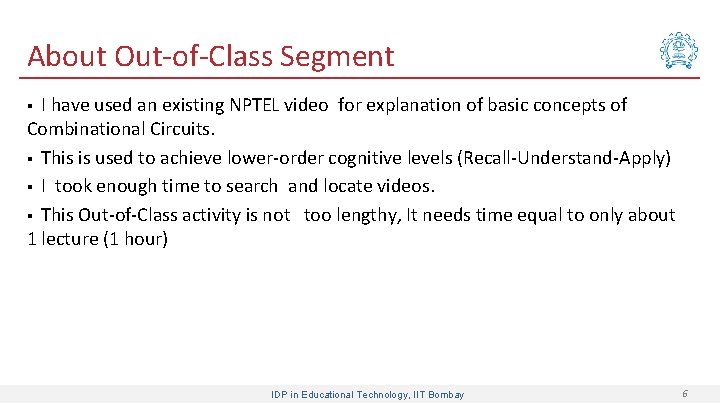

About Out-of-Class Segment I have used an existing NPTEL video for explanation of basic concepts of Combinational Circuits. § This is used to achieve lower-order cognitive levels (Recall-Understand-Apply) § I took enough time to search and locate videos. § This Out-of-Class activity is not too lengthy, It needs time equal to only about 1 lecture (1 hour) § IDP in Educational Technology, IIT Bombay 6

My Video Selection process: I searched for videos on Combinational Circuits in the recommended sequence. Video selection is done from NPTEL repository for following reasons(i) Videos are abundantly available (ii) I was familiar with manoeuvring the NPTEL repository. § IDP in Educational Technology, IIT Bombay 7

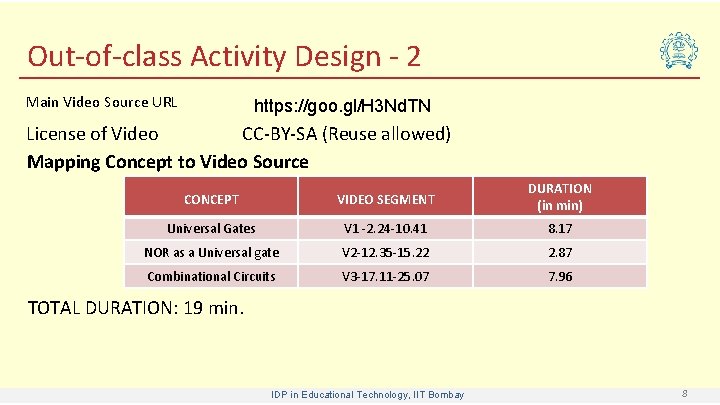

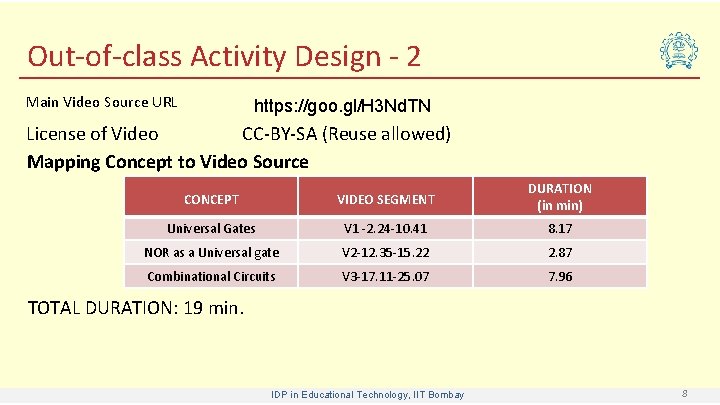

Out-of-class Activity Design - 2 Main Video Source URL https: //goo. gl/H 3 Nd. TN CC-BY-SA (Reuse allowed) License of Video Mapping Concept to Video Source CONCEPT VIDEO SEGMENT DURATION (in min) Universal Gates V 1 -2. 24 -10. 41 8. 17 NOR as a Universal gate V 2 -12. 35 -15. 22 2. 87 Combinational Circuits V 3 -17. 11 -25. 07 7. 96 TOTAL DURATION: 19 min. IDP in Educational Technology, IIT Bombay 8

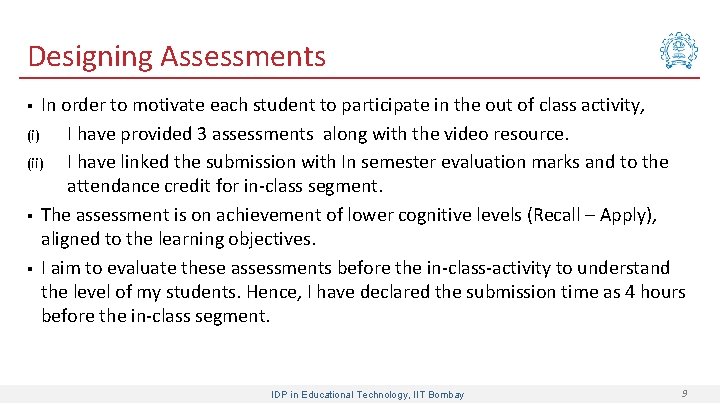

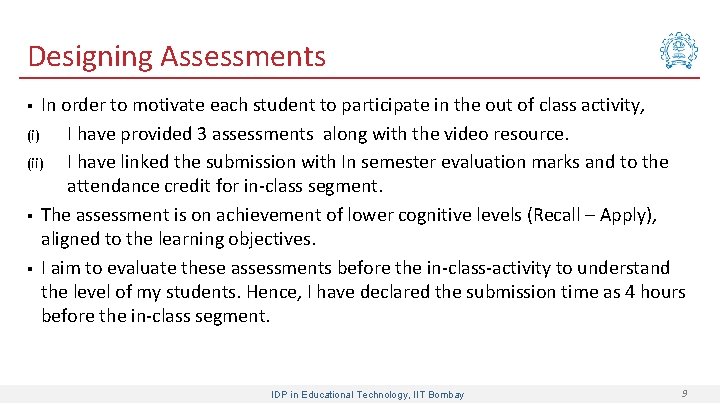

Designing Assessments In order to motivate each student to participate in the out of class activity, (i) I have provided 3 assessments along with the video resource. (ii) I have linked the submission with In semester evaluation marks and to the attendance credit for in-class segment. § The assessment is on achievement of lower cognitive levels (Recall – Apply), aligned to the learning objectives. § I aim to evaluate these assessments before the in-class-activity to understand the level of my students. Hence, I have declared the submission time as 4 hours before the in-class segment. § IDP in Educational Technology, IIT Bombay 9

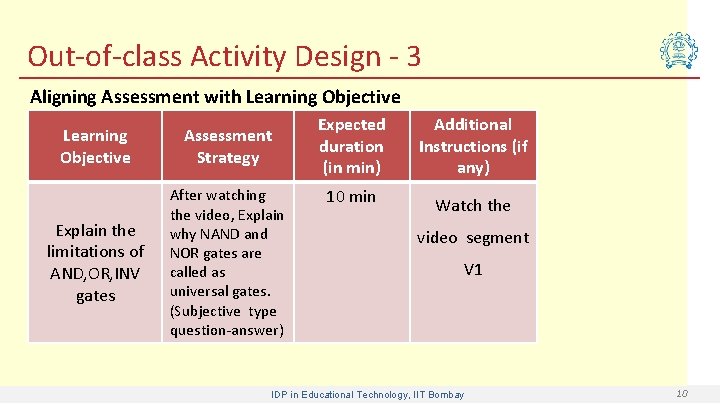

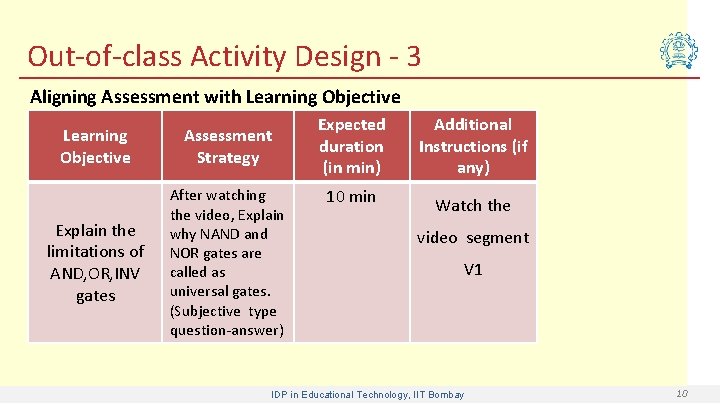

Out-of-class Activity Design - 3 Aligning Assessment with Learning Objective Assessment Strategy Explain the limitations of AND, OR, INV gates After watching the video, Explain why NAND and NOR gates are called as universal gates. (Subjective type question-answer) Expected duration (in min) Additional Instructions (if any) 10 min Watch the video segment V 1 IDP in Educational Technology, IIT Bombay 10

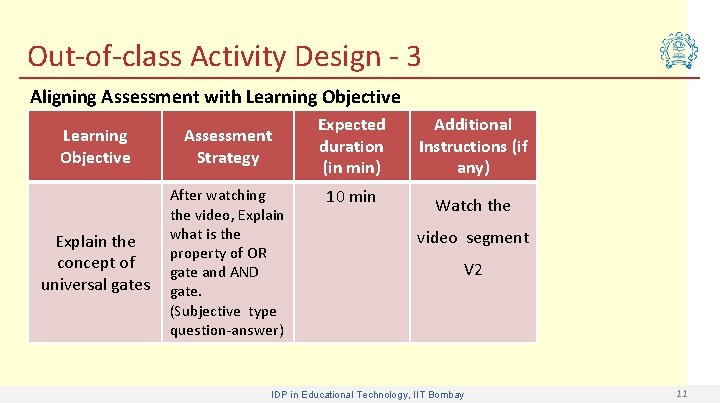

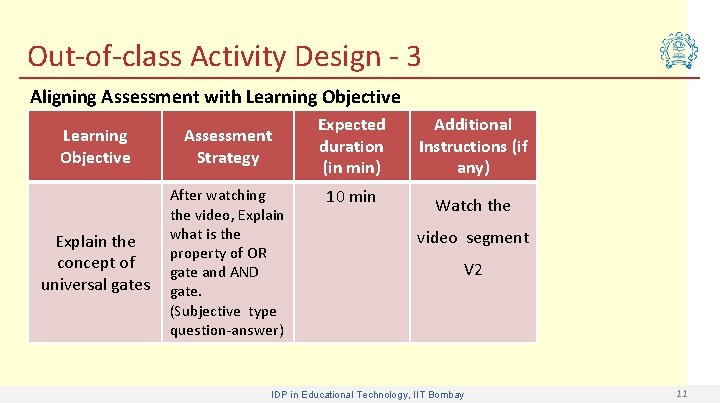

Out-of-class Activity Design - 3 Aligning Assessment with Learning Objective Assessment Strategy Explain the concept of universal gates After watching the video, Explain what is the property of OR gate and AND gate. (Subjective type question-answer) Expected duration (in min) Additional Instructions (if any) 10 min Watch the video segment V 2 IDP in Educational Technology, IIT Bombay 11

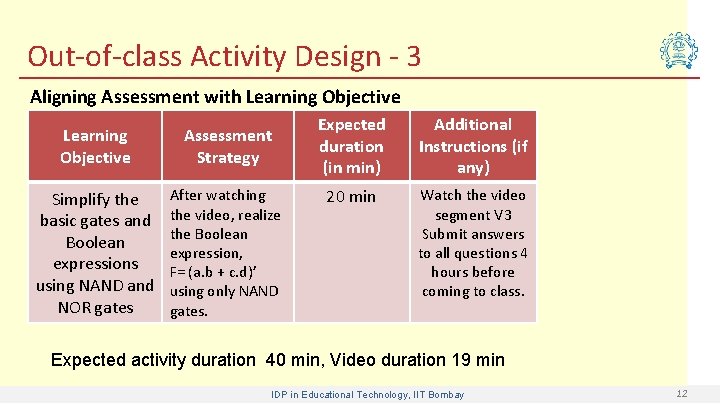

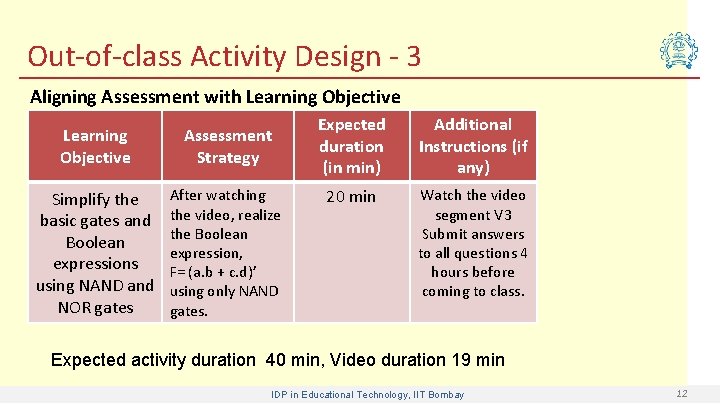

Out-of-class Activity Design - 3 Aligning Assessment with Learning Objective Assessment Strategy Simplify the basic gates and Boolean expressions using NAND and NOR gates After watching the video, realize the Boolean expression, F= (a. b + c. d)’ using only NAND gates. Expected duration (in min) Additional Instructions (if any) 20 min Watch the video segment V 3 Submit answers to all questions 4 hours before coming to class. Expected activity duration 40 min, Video duration 19 min IDP in Educational Technology, IIT Bombay 12

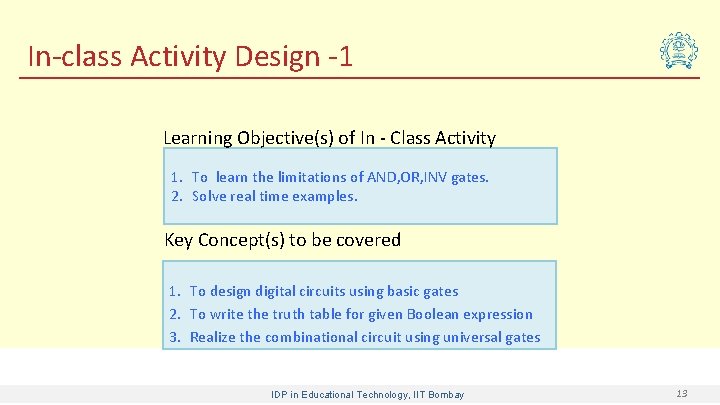

In-class Activity Design -1 Learning Objective(s) of In - Class Activity 1. To learn the limitations of AND, OR, INV gates. 2. Solve real time examples. Key Concept(s) to be covered 1. To design digital circuits using basic gates 2. To write the truth table for given Boolean expression 3. Realize the combinational circuit using universal gates IDP in Educational Technology, IIT Bombay 13

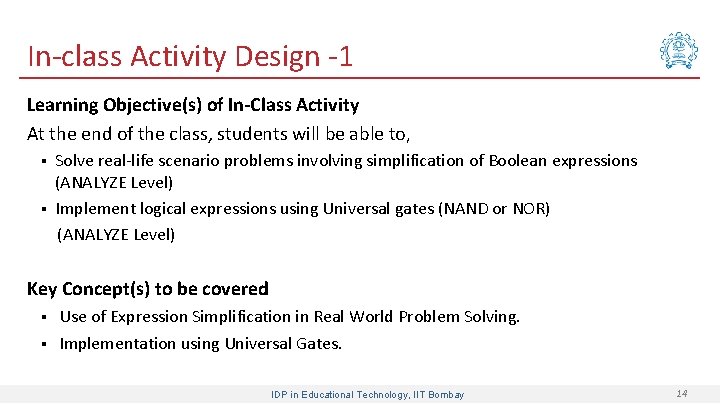

In-class Activity Design -1 Learning Objective(s) of In-Class Activity At the end of the class, students will be able to, § § Solve real-life scenario problems involving simplification of Boolean expressions (ANALYZE Level) Implement logical expressions using Universal gates (NAND or NOR) (ANALYZE Level) Key Concept(s) to be covered § Use of Expression Simplification in Real World Problem Solving. § Implementation using Universal Gates. IDP in Educational Technology, IIT Bombay 14

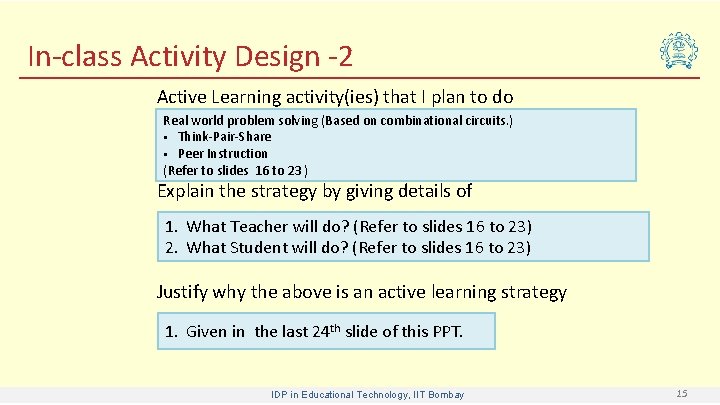

In-class Activity Design -2 Active Learning activity(ies) that I plan to do Real world problem solving (Based on combinational circuits. ) § Think-Pair-Share § Peer Instruction (Refer to slides 16 to 23 ) Explain the strategy by giving details of 1. What Teacher will do? (Refer to slides 16 to 23) 2. What Student will do? (Refer to slides 16 to 23) Justify why the above is an active learning strategy 1. Given in the last 24 th slide of this PPT. IDP in Educational Technology, IIT Bombay 15

In-class Activity Design -2 Active Learning activity(ies) that I plan to do • Concept clarification of Boolean expression , truth table and digital circuit realization using universal gates with the help of Peer Instruction. • Real world problem solving using Think-Pair-Share IDP in Educational Technology, IIT Bombay 16

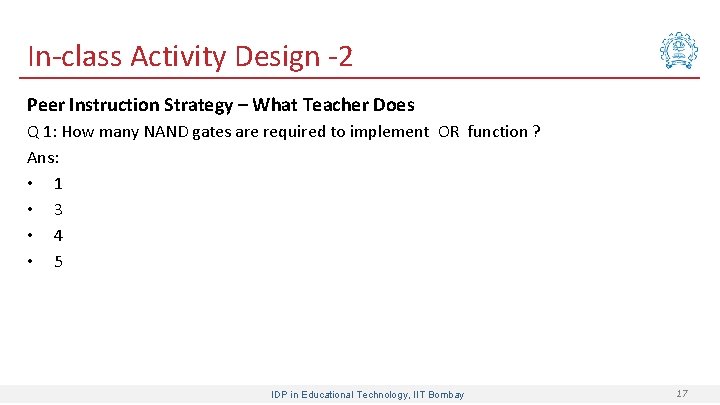

In-class Activity Design -2 Peer Instruction Strategy – What Teacher Does Q 1: How many NAND gates are required to implement OR function ? Ans: • 1 • 3 • 4 • 5 IDP in Educational Technology, IIT Bombay 17

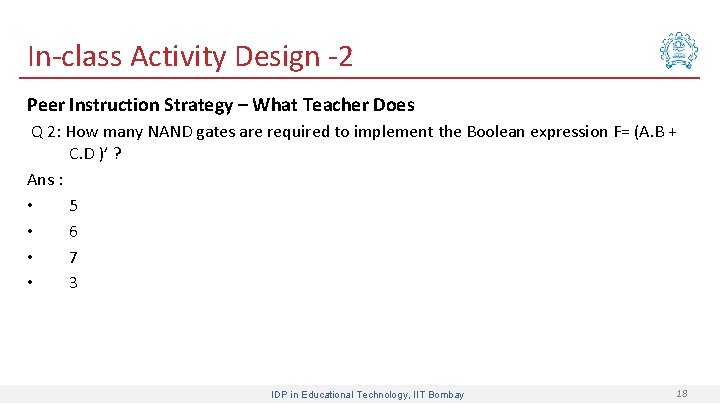

In-class Activity Design -2 Peer Instruction Strategy – What Teacher Does Q 2: How many NAND gates are required to implement the Boolean expression F= (A. B + C. D )’ ? Ans : • 5 • 6 • 7 • 3 IDP in Educational Technology, IIT Bombay 18

In-class Activity Design -2 Peer Instruction Strategy – What Student Does § § § For each question learners will first vote individually. Then they will discuss with peers and come to consensus. Listen to instructors explanation. IDP in Educational Technology, IIT Bombay 19

In-class Activity Design -2 TPS Strategy – What Instructor does First provide a premise Situations: A: I want to go to a movie on Sunday. B: If it is a holiday C: exam F: Go to movie: I go to movie on Sunday or on holiday when there is no exam. Analyze the above situations so that the digital circuit will work. Make sure that true outputs are generated at right time when A is true or B is true and C not true. What is the digital circuit ? IDP in Educational Technology, IIT Bombay 20

In-class Activity Design -2 TPS Strategy – What Instructor does Think (~2 minutes) Instruction: Assuming that A, B, C are three Boolean variables, when the true condition of F will occur ? Think individually and identify the scenario (Boolean expression) in which a high output (F) will occur. IDP in Educational Technology, IIT Bombay 21

In-class Activity Design -2 TPS Strategy – What Instructor does Pair (~5 minutes) Instruction: Learners are asked to pair up and compare the answers. Agree on one final answer. While students are pairing and discussing, visit to 2~3 sections to see what they are doing. Now assuming that three variables A (true) , B (true)and C (not true), develop a Boolean expression so that F will have true value. IDP in Educational Technology, IIT Bombay 22

In-class Activity Design -2 TPS Strategy – What Instructor does Share (~8 minutes) Instructor asks a group to share their answer with class and see whethere are different answers. After sharing is done, instructor gives feedback on the correct solution and how minimizations using Boolean expression play a major role in real life applications, In the next iteration of TPS, in the Think Phase , ask students to convert the Boolean expression in the form of NAND only logic. In the pair phase ask students to compare the answers. In the share phase again the different answers are sought. IDP in Educational Technology, IIT Bombay 23

In-class Activity Design -2 Justify why the above is an active learning strategy In the above strategies, students are required to go beyond mere listening and execution of prescribed steps. They are required to think deeply about the content they were familiarized in out-of-class and do higher order thinking. There is also feedback provided (either through peer discussion or instructor summary) IDP in Educational Technology, IIT Bombay 24

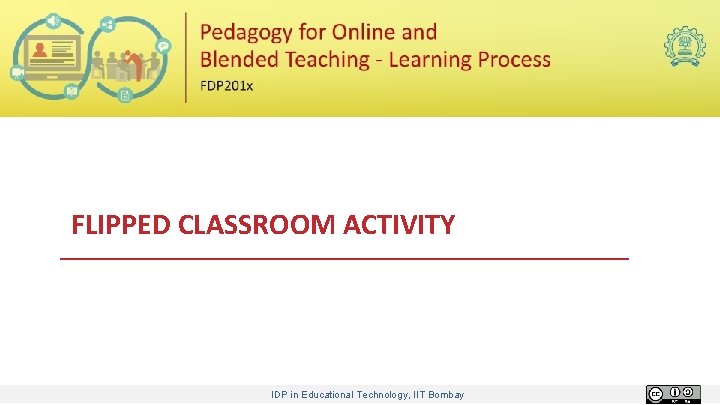

Evaluation and Team Building Standard results and designs related to the above activity are discussed with the students along with the peer evaluation and feedback was given to the students. The same strategy was followed by my co-teacher in other class learners participated actively and found to be successful. IDP in Educational Technology, IIT Bombay 25