FLIPPED CLASSROOM ACTIVITY CONSTRUCTOR USING EXISTING CONTENT IDP

- Slides: 18

FLIPPED CLASSROOM ACTIVITY CONSTRUCTOR – USING EXISTING CONTENT IDP in Educational Technology, IIT Bombay

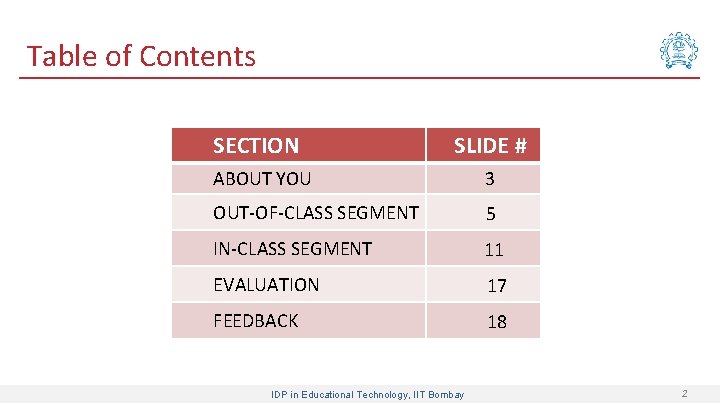

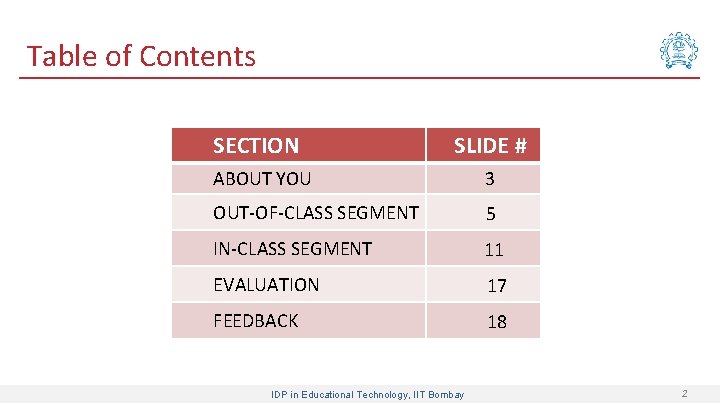

Table of Contents SECTION SLIDE # ABOUT YOU 3 OUT-OF-CLASS SEGMENT 5 IN-CLASS SEGMENT 11 EVALUATION 17 FEEDBACK 18 IDP in Educational Technology, IIT Bombay 2

About you I am Asmita A. Chavan The topic that I have selected for my flip classroom activity is combinational circuit. I like to work on this topic as combinational circuits plays the vital part in logic design. Students should know about basic of logic design and their design. IDP in Educational Technology, IIT Bombay 3

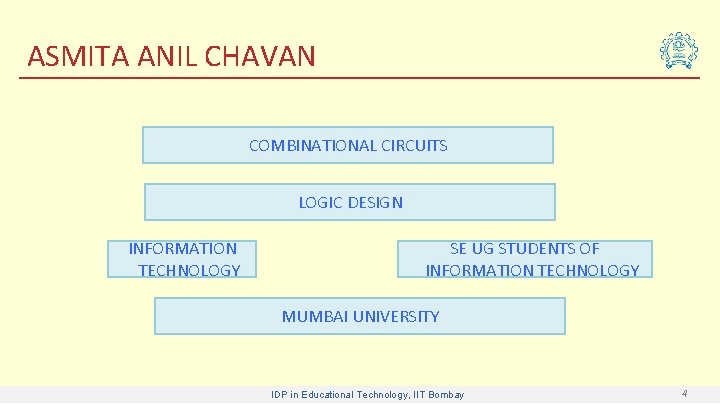

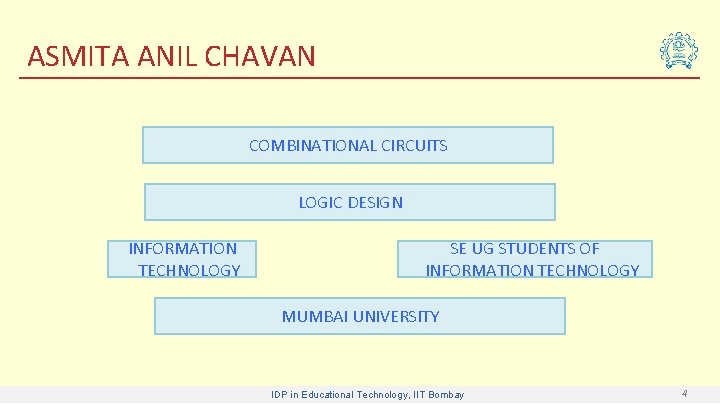

ASMITA ANIL CHAVAN COMBINATIONAL CIRCUITS LOGIC DESIGN INFORMATION TECHNOLOGY SE UG STUDENTS OF INFORMATION TECHNOLOGY MUMBAI UNIVERSITY IDP in Educational Technology, IIT Bombay 4

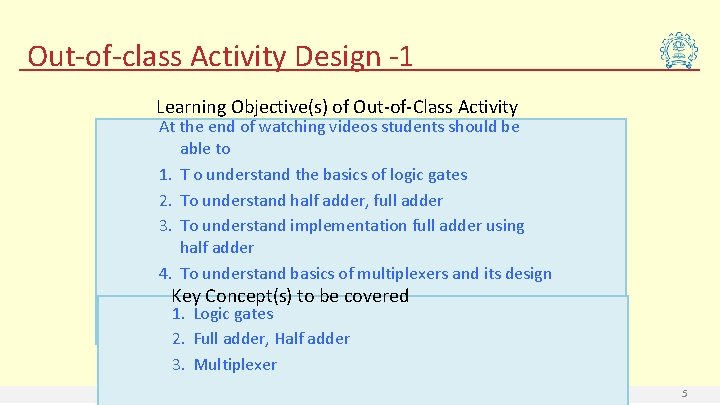

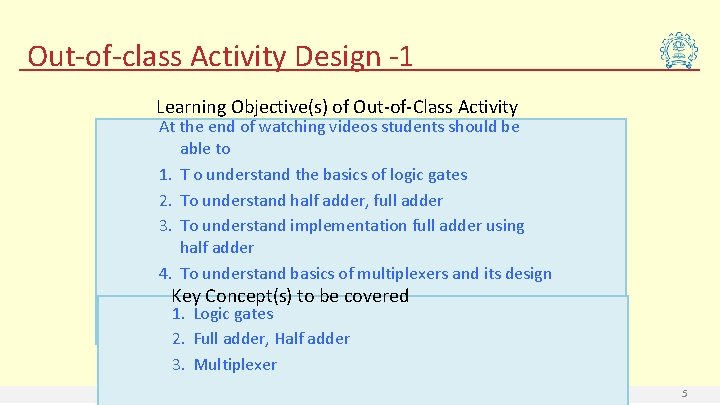

Out-of-class Activity Design -1 Learning Objective(s) of Out-of-Class Activity At the end of watching videos students should be able to 1. T o understand the basics of logic gates 2. To understand half adder, full adder 3. To understand implementation full adder using half adder 4. To understand basics of multiplexers and its design Key Concept(s) to be covered 1. Logic gates 2. Full adder, Half adder 3. Multiplexer IDP in Educational Technology, IIT Bombay 5

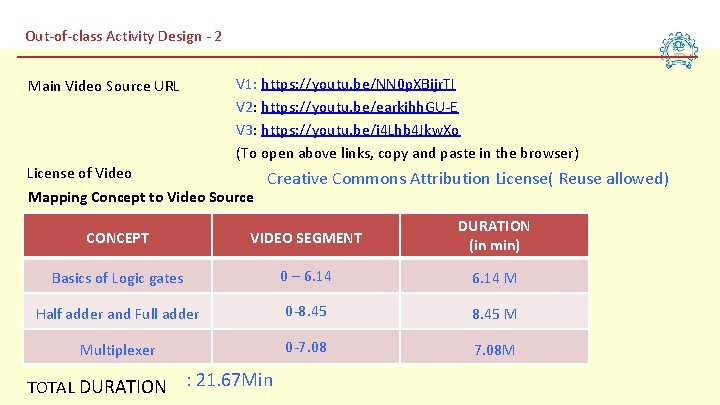

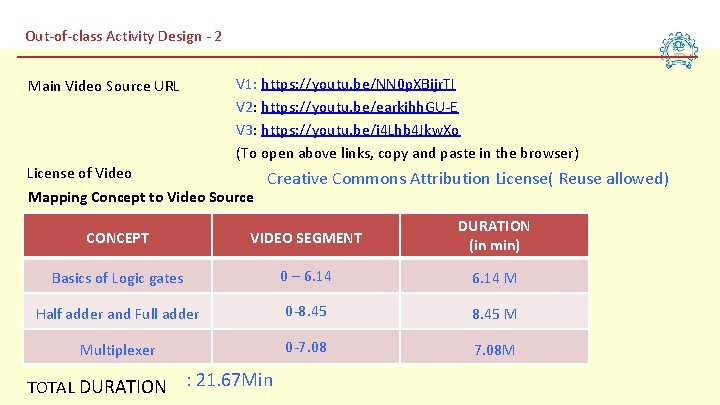

Out-of-class Activity Design - 2 V 1: https: //youtu. be/NN 0 p. XBijr. TI V 2: https: //youtu. be/earkihh. GU-E V 3: https: //youtu. be/i 4 Lhb 4 Jkw. Xo (To open above links, copy and paste in the browser) Main Video Source URL License of Video Mapping Concept to Video Source Creative Commons Attribution License( Reuse allowed) CONCEPT VIDEO SEGMENT DURATION (in min) Basics of Logic gates 0 – 6. 14 M Half adder and Full adder 0 -8. 45 M Multiplexer 0 -7. 08 M TOTAL DURATION : 21. 67 Min IDP in Educational Technology, IIT Bombay 6

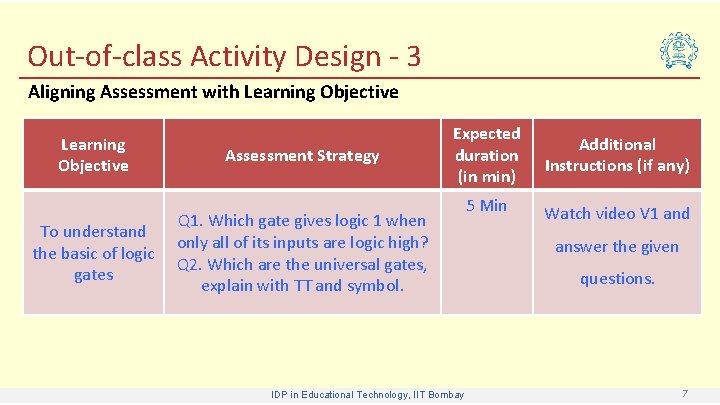

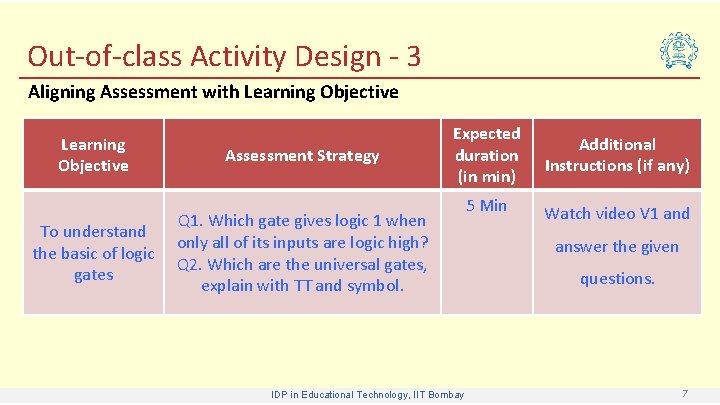

Out-of-class Activity Design - 3 Aligning Assessment with Learning Objective To understand the basic of logic gates Assessment Strategy Expected duration (in min) Additional Instructions (if any) 5 Min Watch video V 1 and Q 1. Which gate gives logic 1 when only all of its inputs are logic high? Q 2. Which are the universal gates, explain with TT and symbol. IDP in Educational Technology, IIT Bombay answer the given questions. 7

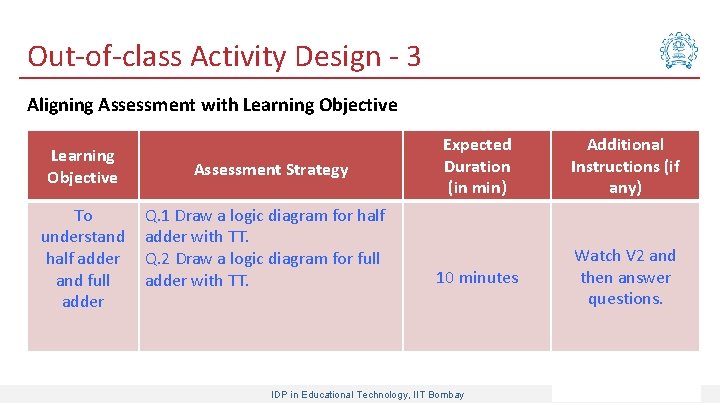

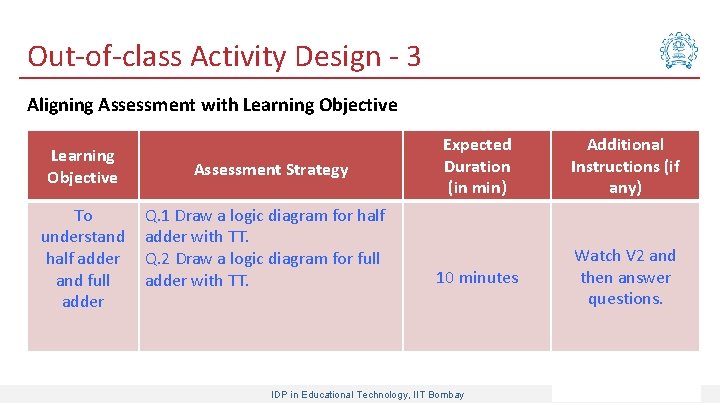

Out-of-class Activity Design - 3 Aligning Assessment with Learning Objective To understand half adder and full adder Assessment Strategy Q. 1 Draw a logic diagram for half adder with TT. Q. 2 Draw a logic diagram for full adder with TT. Expected Duration (in min) Additional Instructions (if any) 10 minutes Watch V 2 and then answer questions. IDP in Educational Technology, IIT Bombay EXAMPLE 8

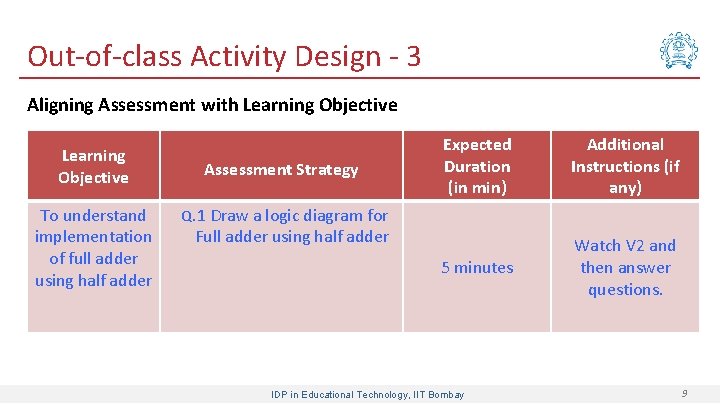

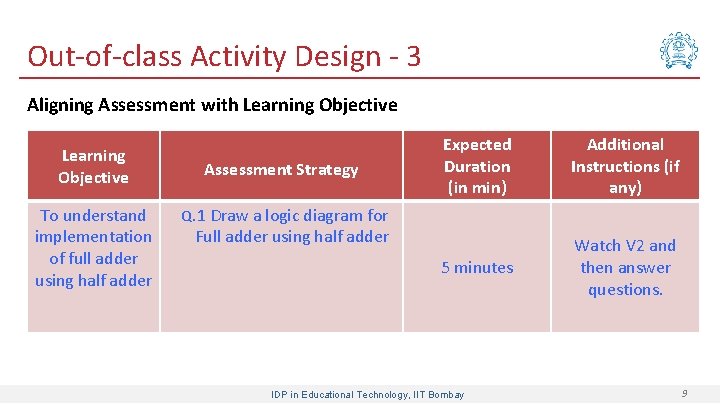

Out-of-class Activity Design - 3 Aligning Assessment with Learning Objective To understand implementation of full adder using half adder Assessment Strategy Expected Duration (in min) Additional Instructions (if any) 5 minutes Watch V 2 and then answer questions. Q. 1 Draw a logic diagram for Full adder using half adder EXAMPLE IDP in Educational Technology, IIT Bombay 9

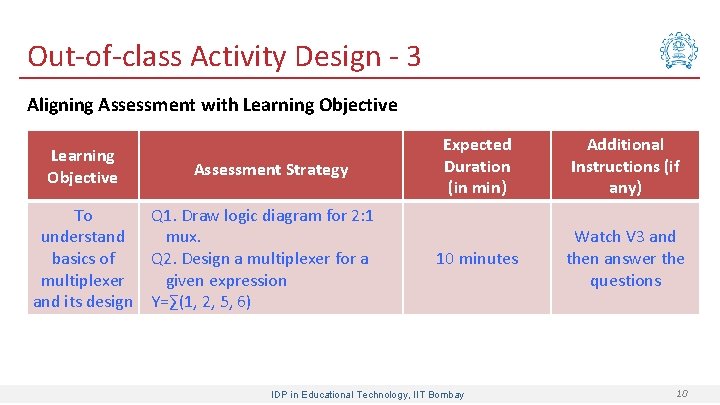

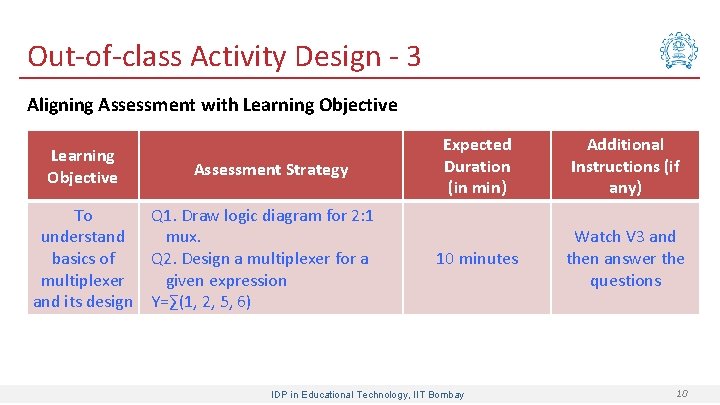

Out-of-class Activity Design - 3 Aligning Assessment with Learning Objective To understand basics of multiplexer and its design Assessment Strategy Q 1. Draw logic diagram for 2: 1 mux. Q 2. Design a multiplexer for a given expression Y=∑(1, 2, 5, 6) Expected Duration (in min) Additional Instructions (if any) 10 minutes Watch V 3 and then answer the questions EXAMPLE IDP in Educational Technology, IIT Bombay 10

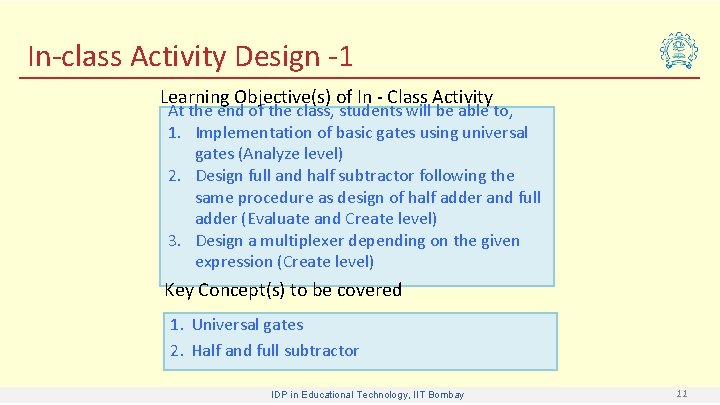

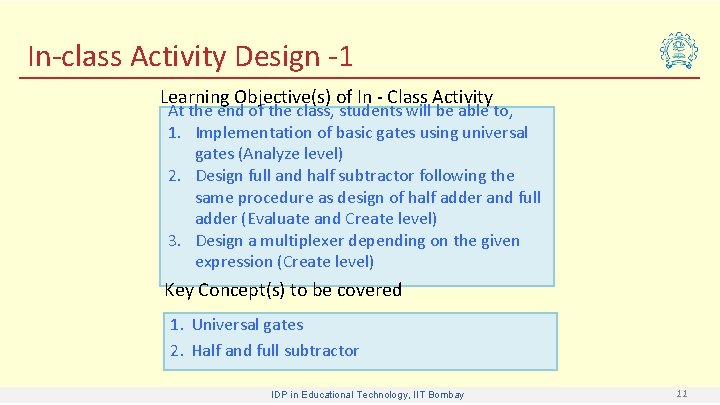

In-class Activity Design -1 Learning Objective(s) of In - Class Activity At the end of the class, students will be able to, 1. Implementation of basic gates using universal gates (Analyze level) 2. Design full and half subtractor following the same procedure as design of half adder and full adder (Evaluate and Create level) 3. Design a multiplexer depending on the given expression (Create level) Key Concept(s) to be covered 1. Universal gates 2. Half and full subtractor IDP in Educational Technology, IIT Bombay 11

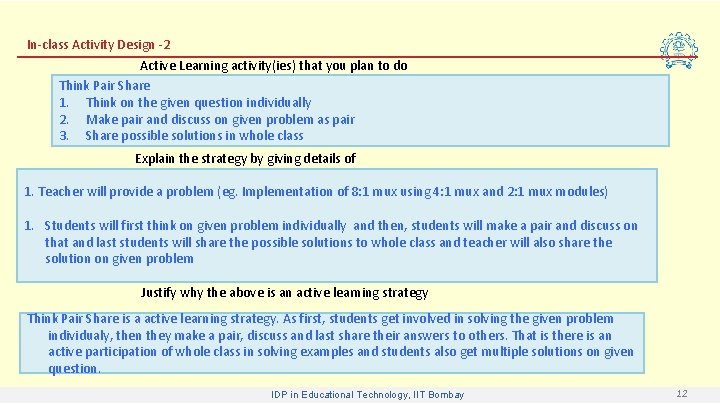

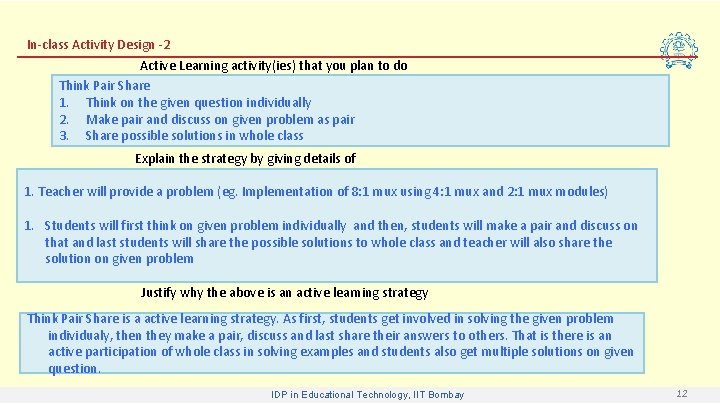

In-class Activity Design -2 Active Learning activity(ies) that you plan to do Think Pair Share 1. Think on the given question individually 2. Make pair and discuss on given problem as pair 3. Share possible solutions in whole class Explain the strategy by giving details of 1. Teacher will provide a problem (eg. Implementation of 8: 1 mux using 4: 1 mux and 2: 1 mux modules) 1. Students will first think on given problem individually and then, students will make a pair and discuss on that and last students will share the possible solutions to whole class and teacher will also share the solution on given problem Justify why the above is an active learning strategy Think Pair Share is a active learning strategy. As first, students get involved in solving the given problem individualy, then they make a pair, discuss and last share their answers to others. That is there is an active participation of whole class in solving examples and students also get multiple solutions on given question. IDP in Educational Technology, IIT Bombay 12

In-class Activity Design -2 TPS Strategy – What Instructor does Ques. Design a 8: 1 multiplexer using 4: 1 and 2: 1 multiplexers modules. EXAMPLE IDP in Educational Technology, IIT Bombay 13

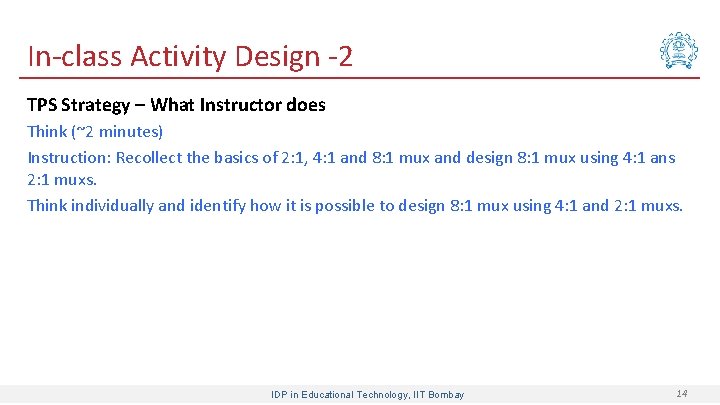

In-class Activity Design -2 TPS Strategy – What Instructor does Think (~2 minutes) Instruction: Recollect the basics of 2: 1, 4: 1 and 8: 1 mux and design 8: 1 mux using 4: 1 ans 2: 1 muxs. Think individually and identify how it is possible to design 8: 1 mux using 4: 1 and 2: 1 muxs. EXAMPLE IDP in Educational Technology, IIT Bombay 14

In-class Activity Design -2 TPS Strategy – What Instructor does Pair (~5 minutes) Instruction: Students have to make a pair, discuss answers and agree on valid answer. Teacher has to visit 2 -3 pairs to see what they have done. Now assume any combination of select line and find which signal will appear at output. EXAMPLE IDP in Educational Technology, IIT Bombay 15

In-class Activity Design -2 TPS Strategy – What Instructor does Share (~8 minutes) Students have to share their answer with class and see whethere are different answers. After sharing is done, teacher gives feedback on the correct solution In the next iteration of TPS, in the Think Phase ask students to design 16: 1 mux using 8: 1 muxs In the share phase again the different answers are sought. EXAMPLE IDP in Educational Technology, IIT Bombay 16

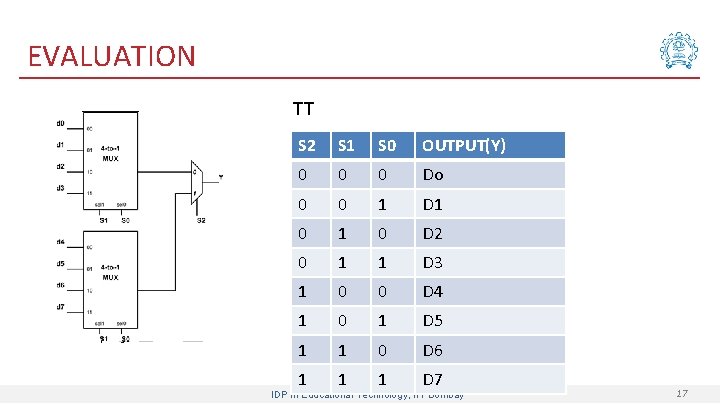

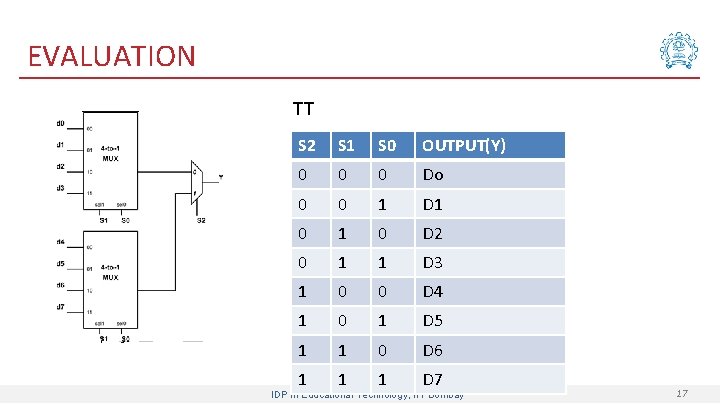

EVALUATION TT S 2 S 1 S 0 OUTPUT(Y) 0 0 0 Do 0 0 1 D 1 0 D 2 0 1 1 D 3 1 0 0 D 4 1 0 1 D 5 1 1 0 D 6 1 1 1 D 7 IDP in Educational Technology, IIT Bombay 17

In-class Activity Design -2 Justify why the above is an active learning strategy Think Pair Share plays a vital role in having a active participation of students in class Students think on given problem and come put with multiple possible solutions. This also helps to clarify the concept and application of that knowledge in problem solving. There is also feedback provided (either through peer discussion or instructor summary) Feedback: 1. Students also implements full subtractor using two half subtractor. 2. Students came with multiple ways to design mux. They also design 16: 1 using a single 4: 1 muxs as well as 8: 1 muxs. 3. They also design mux using logic gates( instead of direct IC). 4. They also shared that think pair share is an effective way of learning. EXAMPLE IDP in Educational Technology, IIT Bombay 18