FLIPFLOP Pendahuluan Rangkaian Logika terbagi menjadi dua kelompok

FLIP-FLOP

Pendahuluan • Rangkaian Logika terbagi menjadi dua kelompok yaitu : 1. Rangkaian logika kombinasional adalah rangkaian yang kondisi keluarannya (output) dipengaruhi oleh kondisi masukan (input). Rangkaian yang termasuk rangkaian logika kombinasional yaitu Dekoder, Enkoder, Multiplekser, Demultiplekser. Pada rangkaian -rangkaian itu terlihat bahwa kondisi keluaran hanya dipengaruhi oleh kondisi masukan pada saat itu. 2. Rangkaian logika sekuensial adalah rangkaian logika yang kondisi keluarannya dipengaruhi oleh masukan dan keadaan keluaran sebelumnya atau dapat dikatakan rangkaian yang bekerja berdasarkan urutan waktu. Ciri rangkaian logika sekuensial yang utama adalah adanya jalur umpan balik (feedback) di dalam rangkaiannya. Adapun contoh rangkaian yang termasuk rangkaian sekuensial yaitu flip-flop, counter, dan register.

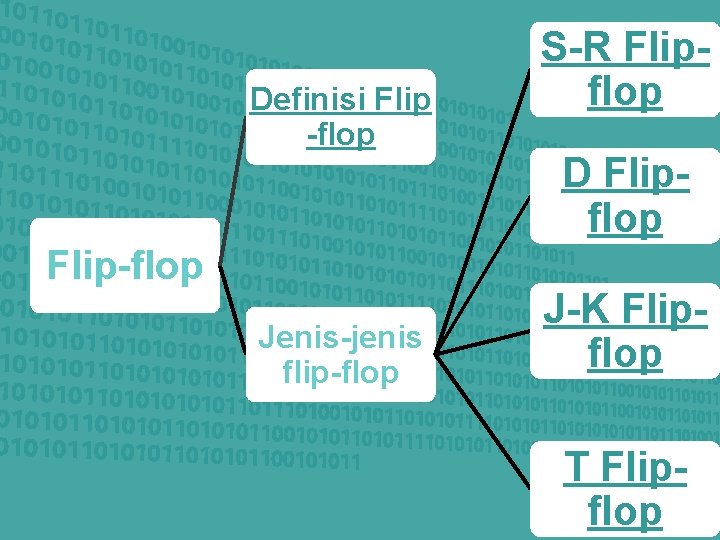

Definisi Flip -flop Flip-flop Jenis-jenis flip-flop S-R Flipflop D Flipflop J-K Flipflop T Flipflop

DEFINISI FLIP FLOP 1. Flip-flop adalah rangkaian yang mempunyai fungsi pengingat (memory). Artinya rangkaian ini mampu melakukan proses penyimpanan data sesuai dengan kombinasi masukan yang diberikan kepadanya. Data yang tersimpan itu dapat dikeluarkan sesuai dengan kombinasi masukan yang diberikan. 2. Flip-flop merupakan suatu rangkaian sekuensial yang dapat menyimpan data sementara dimana bagian outputnya akan merespons input dengan cara mengunci nilai input yang diberikan atau mengingat input tersebut. Dengan menambah suatu gerbang ke setiap masukan rangkaian dasar, flip-flop tersebut dapat diubah untuk menanggapi masukan selama adanya suatu pulsa waktu. Flip-flop mempunyai dua kondisi output yang stabil dan saling berlawanan. Perubahan dari setiap keadaan output dapat terjadi jika diberikan trigger pada flip-flop tersebut. Triger –nya berupa sinyal logika “ 1” dan “ 0” yang kontinyu. 3. Counter, register serta rangkaian sekuensial lain disusun dengan menggunakan flip-flop sebagai komponen utama.

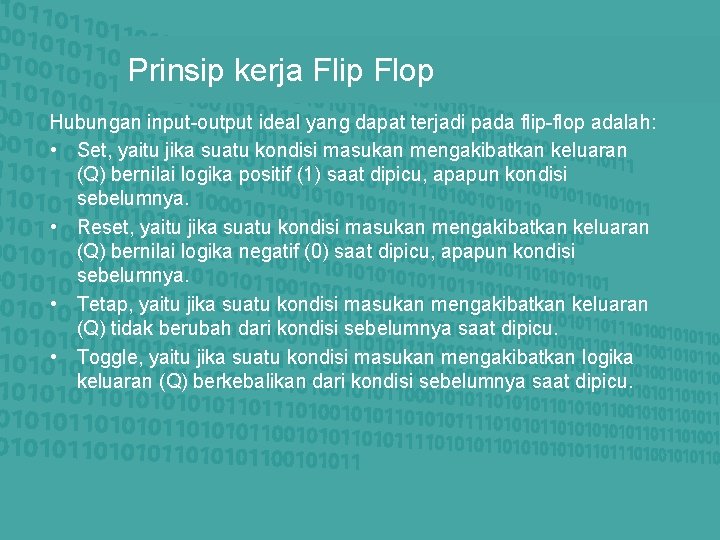

Prinsip kerja Flip Flop Hubungan input-output ideal yang dapat terjadi pada flip-flop adalah: • Set, yaitu jika suatu kondisi masukan mengakibatkan keluaran (Q) bernilai logika positif (1) saat dipicu, apapun kondisi sebelumnya. • Reset, yaitu jika suatu kondisi masukan mengakibatkan keluaran (Q) bernilai logika negatif (0) saat dipicu, apapun kondisi sebelumnya. • Tetap, yaitu jika suatu kondisi masukan mengakibatkan keluaran (Q) tidak berubah dari kondisi sebelumnya saat dipicu. • Toggle, yaitu jika suatu kondisi masukan mengakibatkan logika keluaran (Q) berkebalikan dari kondisi sebelumnya saat dipicu.

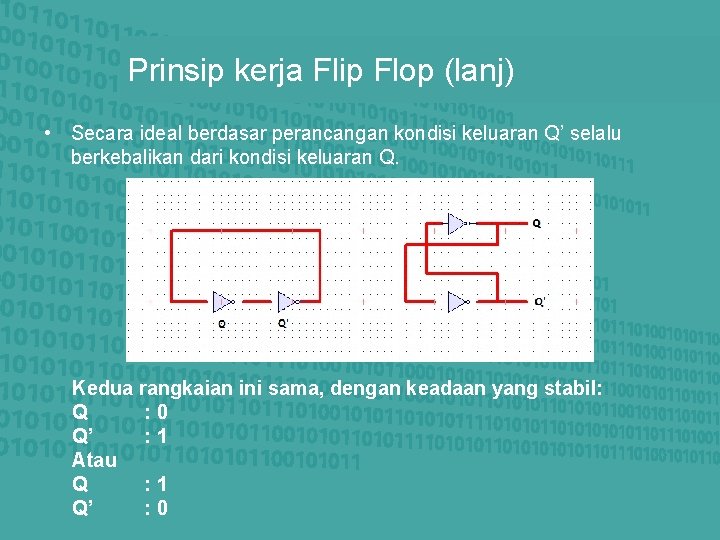

Prinsip kerja Flip Flop (lanj) • Secara ideal berdasar perancangan kondisi keluaran Q’ selalu berkebalikan dari kondisi keluaran Q. Kedua rangkaian ini sama, dengan keadaan yang stabil: Q : 0 Q’ : 1 Atau Q : 1 Q’ : 0

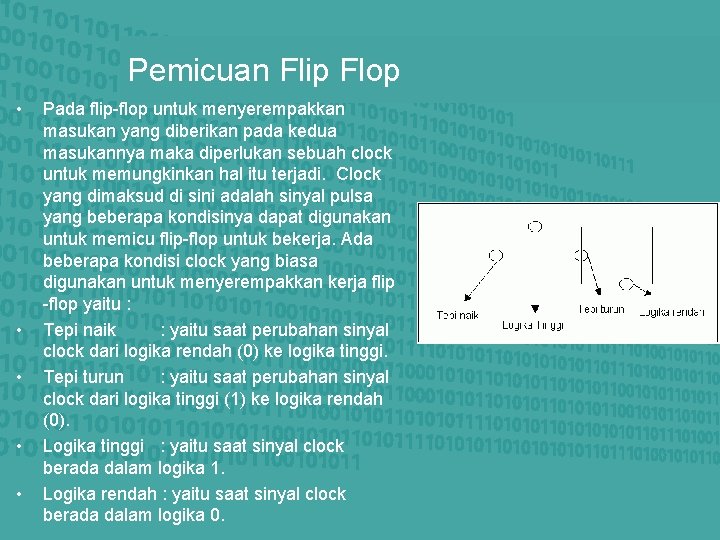

Pemicuan Flip Flop • • • Pada flip-flop untuk menyerempakkan masukan yang diberikan pada kedua masukannya maka diperlukan sebuah clock untuk memungkinkan hal itu terjadi. Clock yang dimaksud di sini adalah sinyal pulsa yang beberapa kondisinya dapat digunakan untuk memicu flip-flop untuk bekerja. Ada beberapa kondisi clock yang biasa digunakan untuk menyerempakkan kerja flip -flop yaitu : Tepi naik : yaitu saat perubahan sinyal clock dari logika rendah (0) ke logika tinggi. Tepi turun : yaitu saat perubahan sinyal clock dari logika tinggi (1) ke logika rendah (0). Logika tinggi : yaitu saat sinyal clock berada dalam logika 1. Logika rendah : yaitu saat sinyal clock berada dalam logika 0.

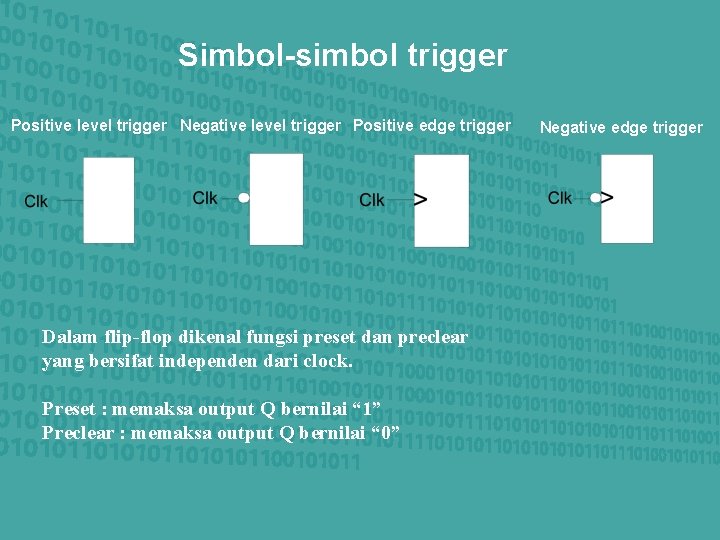

Simbol-simbol trigger Positive level trigger Negative level trigger Positive edge trigger Dalam flip-flop dikenal fungsi preset dan preclear yang bersifat independen dari clock. Preset : memaksa output Q bernilai “ 1” Preclear : memaksa output Q bernilai “ 0” Negative edge trigger

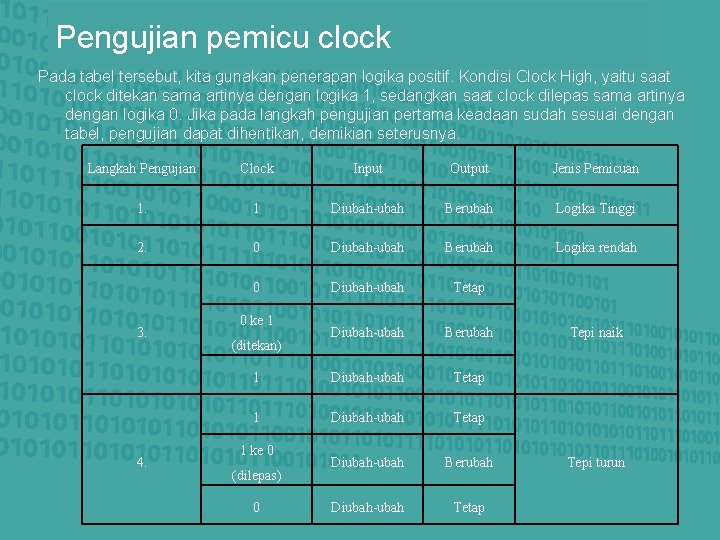

Pengujian pemicu clock Pada tabel tersebut, kita gunakan penerapan logika positif. Kondisi Clock High, yaitu saat clock ditekan sama artinya dengan logika 1, sedangkan saat clock dilepas sama artinya dengan logika 0. Jika pada langkah pengujian pertama keadaan sudah sesuai dengan tabel, pengujian dapat dihentikan, demikian seterusnya. Langkah Pengujian Clock Input Output Jenis Pemicuan 1. 1 Diubah-ubah Berubah Logika Tinggi 2. 0 Diubah-ubah Berubah Logika rendah 0 Diubah-ubah Tetap Diubah-ubah Berubah 1 Diubah-ubah Tetap Diubah-ubah Berubah Diubah-ubah Tetap 3. 4. 0 ke 1 (ditekan) 1 ke 0 (dilepas) 0 Tepi naik Tepi turun

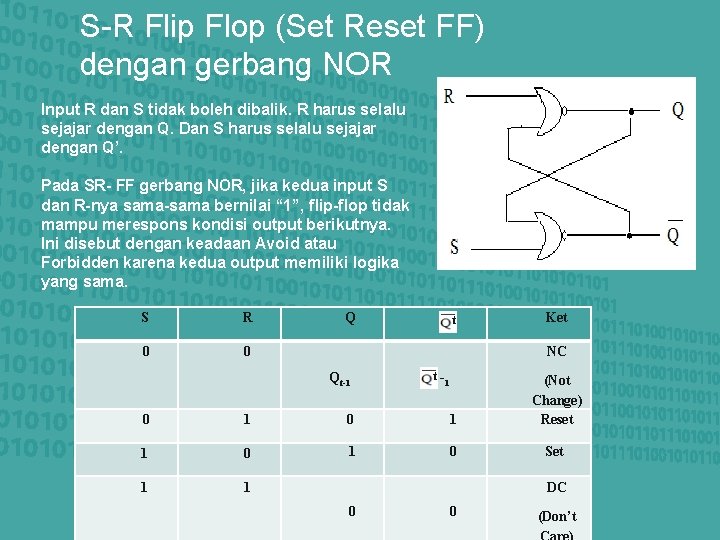

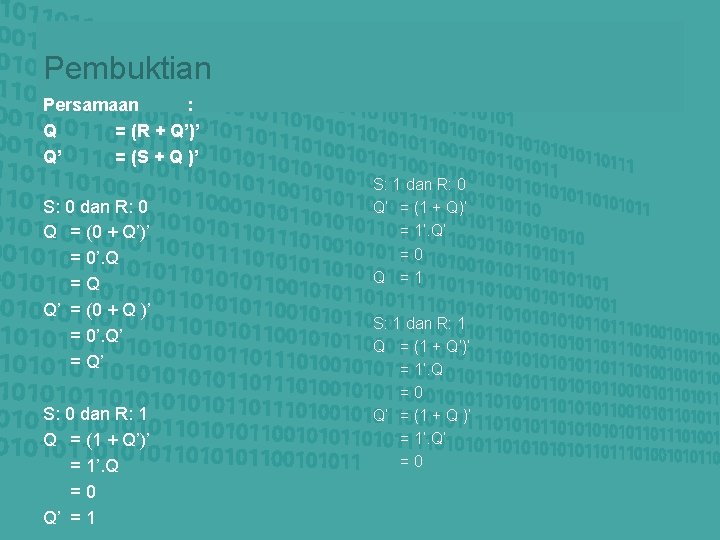

S-R Flip Flop (Set Reset FF) dengan gerbang NOR Input R dan S tidak boleh dibalik. R harus selalu sejajar dengan Q. Dan S harus selalu sejajar dengan Q’. Pada SR- FF gerbang NOR, jika kedua input S dan R-nya sama-sama bernilai “ 1”, flip-flop tidak mampu merespons kondisi output berikutnya. Ini disebut dengan keadaan Avoid atau Forbidden karena kedua output memiliki logika yang sama. S R 0 0 Q t Ket NC Qt-1 t- 1 0 1 1 (Not Change) Reset Set DC 0 0 (Don’t

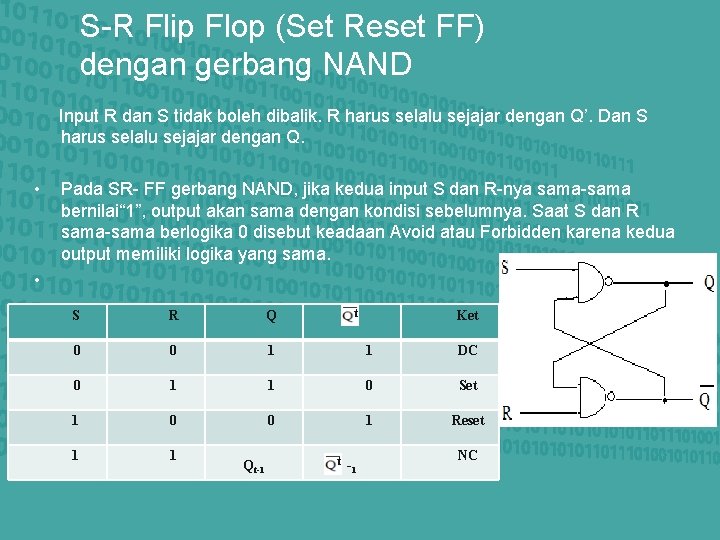

S-R Flip Flop (Set Reset FF) dengan gerbang NAND Input R dan S tidak boleh dibalik. R harus selalu sejajar dengan Q’. Dan S harus selalu sejajar dengan Q. • • Pada SR- FF gerbang NAND, jika kedua input S dan R-nya sama-sama bernilai“ 1”, output akan sama dengan kondisi sebelumnya. Saat S dan R sama-sama berlogika 0 disebut keadaan Avoid atau Forbidden karena kedua output memiliki logika yang sama. t S R Q 0 0 1 1 DC 0 1 1 0 Set 1 0 0 1 Reset 1 1 Qt-1 t 1 Ket NC

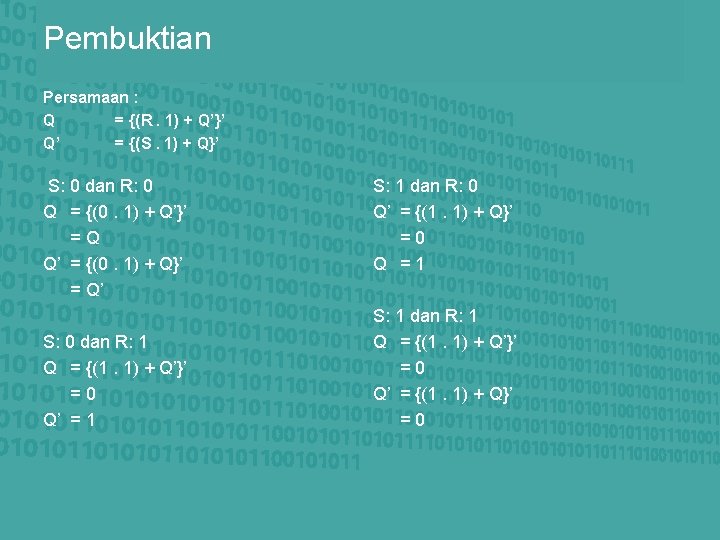

Tuliskan persamaannya dan buktikan. . !!!

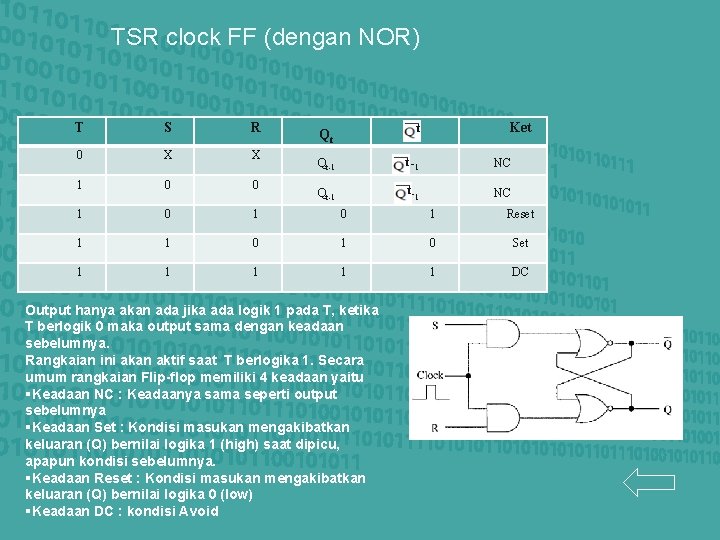

TSR clock FF (dengan NOR) T S R Ket 0 X X 1 0 0 1 0 1 Reset 1 1 0 Set 1 1 1 DC Qt t Qt-1 t -1 NC Qt-1 NC Output hanya akan ada jika ada logik 1 pada T, ketika T berlogik 0 maka output sama dengan keadaan sebelumnya. Rangkaian ini akan aktif saat T berlogika 1. Secara umum rangkaian Flip-flop memiliki 4 keadaan yaitu §Keadaan NC : Keadaanya sama seperti output sebelumnya §Keadaan Set : Kondisi masukan mengakibatkan keluaran (Q) bernilai logika 1 (high) saat dipicu, apapun kondisi sebelumnya. §Keadaan Reset : Kondisi masukan mengakibatkan keluaran (Q) bernilai logika 0 (low) §Keadaan DC : kondisi Avoid

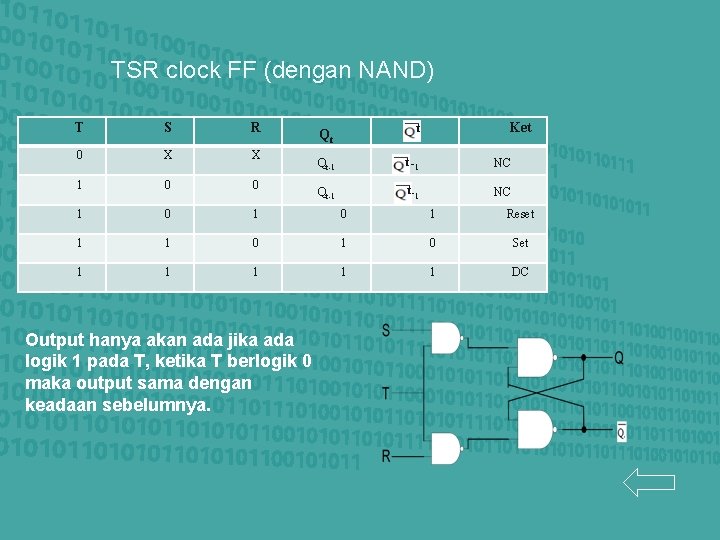

TSR clock FF (dengan NAND) T S R 0 X X 1 0 0 1 0 1 Reset 1 1 0 Set 1 1 1 DC Output hanya akan ada jika ada logik 1 pada T, ketika T berlogik 0 maka output sama dengan keadaan sebelumnya. Ket Qt-1 t -1 NC Qt-1 NC

Tuliskan persamaannya dan buktikan. . !!!

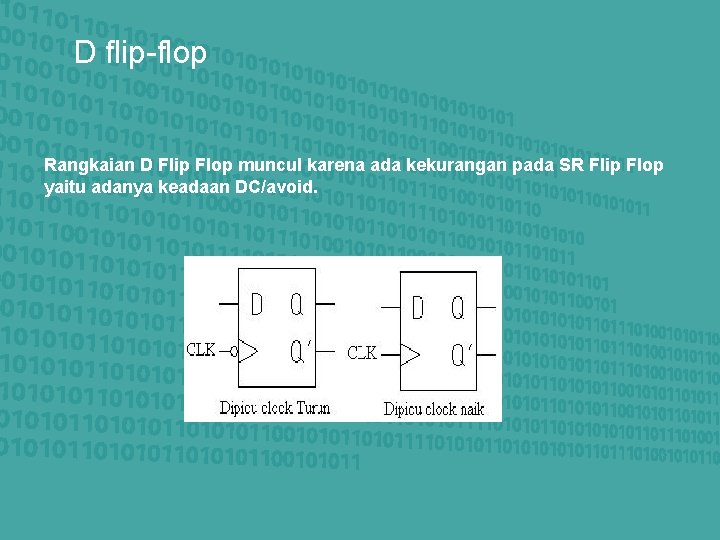

D flip-flop Rangkaian D Flip Flop muncul karena ada kekurangan pada SR Flip Flop yaitu adanya keadaan DC/avoid.

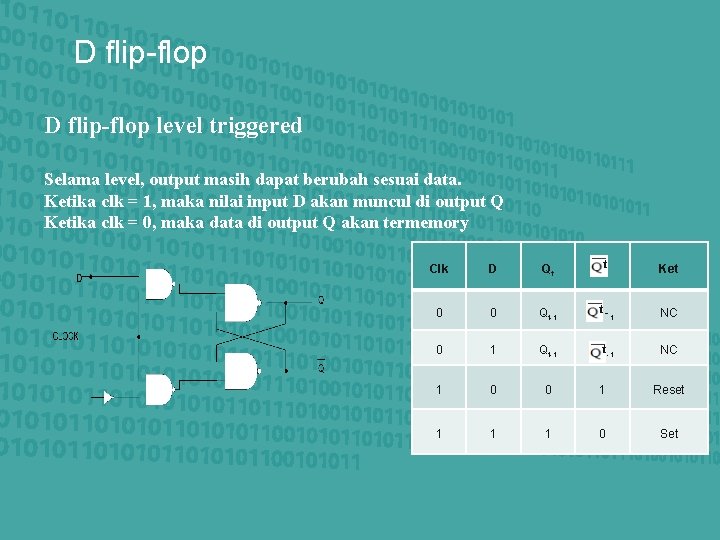

D flip-flop level triggered Selama level, output masih dapat berubah sesuai data. Ketika clk = 1, maka nilai input D akan muncul di output Q Ketika clk = 0, maka data di output Q akan termemory Clk D Qt t Ket 0 0 Qt-1 t t- 1 NC 0 1 Qt-1 t t- -1 NC 1 0 0 1 Reset 1 1 1 0 Set

Timing Diagram D Flip Flop Pada flip-flop untuk menyerempakkan masukan yang diberikan pada kedua masukannya maka diperlukan sebuah clock untuk memungkinkan hal itu terjadi. Clock yang dimaksud di sini adalah sinyal pulsa yang beberapa kondisinya dapat digunakan untuk memicu flip-flop untuk bekerja. Ada beberapa kondisi clock yang biasa digunakan untuk menyerempakkan kerja flip-flop yaitu : q. Tepi naik : yaitu saat perubahan sinyal clock dari logika rendah (0) ke logika tinggi. q. Tepi turun : yaitu saat perubahan sinyal clock dari logika tinggi (1) ke logika rendah (0). q. Logika tinggi : yaitu saat sinyal clock berada dalam logika 1. q. Logika rendah : yaitu saat sinyal clock berada dalam logika 0.

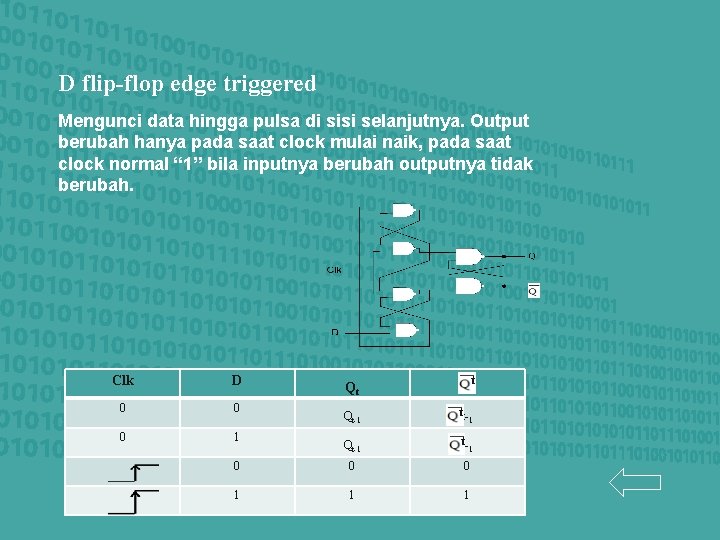

D flip-flop edge triggered Mengunci data hingga pulsa di sisi selanjutnya. Output berubah hanya pada saat clock mulai naik, pada saat clock normal “ 1” bila inputnya berubah outputnya tidak berubah. Clk D 0 0 0 1 t Qt T Qt-1 tt 1 0 0 0 1 1 1

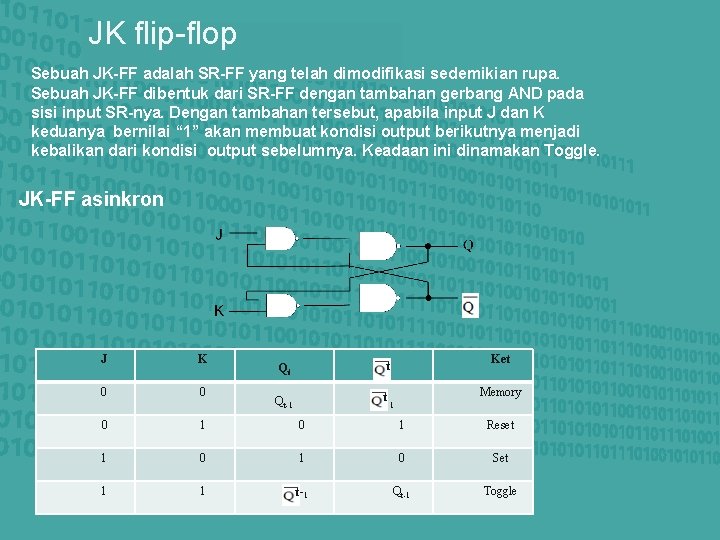

JK flip-flop Sebuah JK-FF adalah SR-FF yang telah dimodifikasi sedemikian rupa. Sebuah JK-FF dibentuk dari SR-FF dengan tambahan gerbang AND pada sisi input SR-nya. Dengan tambahan tersebut, apabila input J dan K keduanya bernilai “ 1” akan membuat kondisi output berikutnya menjadi kebalikan dari kondisi output sebelumnya. Keadaan ini dinamakan Toggle. JK-FF asinkron J K Ket 0 0 0 1 Reset 1 0 Set 1 1 tt-1 Qt-1 Toggle Qt Qt-1 t Qt 1 Memory

Tuliskan persamaannya dan buktikan. . !!!

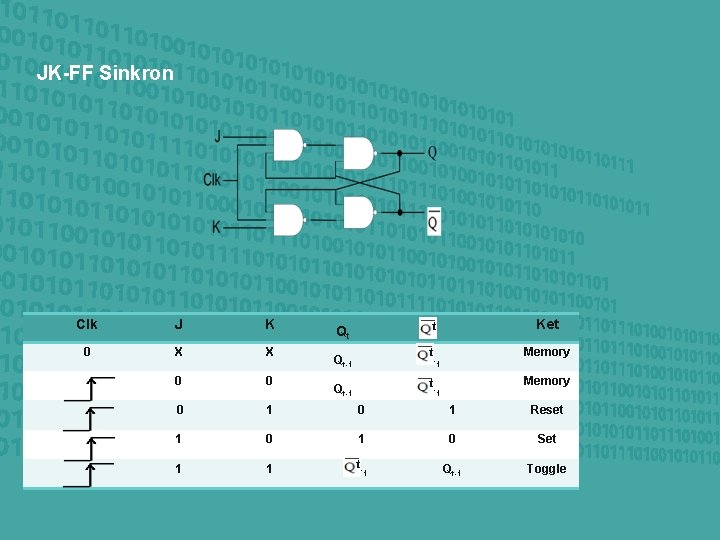

JK-FF Sinkron Clk J K t Ket 0 X X Qt-1 t t-1 Memory 0 0 Qt-1 t t 1 Memory 0 1 Reset 1 0 Set 1 1 t t 1 Qt-1 Toggle Qt

Tuliskan persamaannya dan buktikan. . !!!

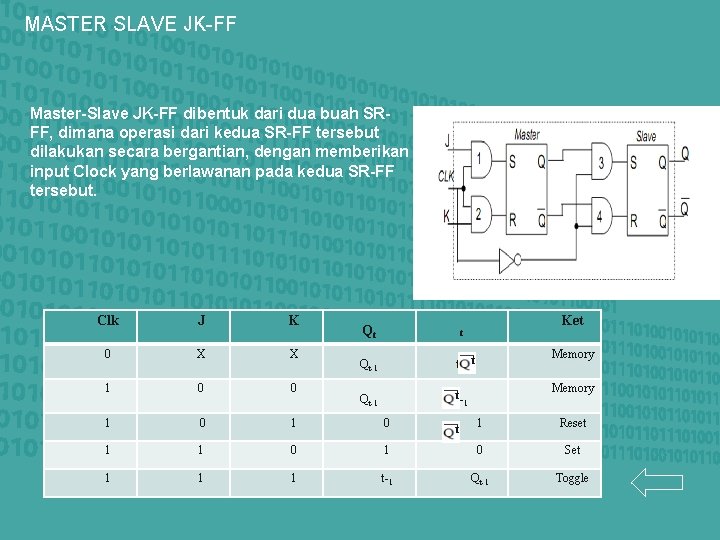

MASTER SLAVE JK-FF Master-Slave JK-FF dibentuk dari dua buah SRFF, dimana operasi dari kedua SR-FF tersebut dilakukan secara bergantian, dengan memberikan input Clock yang berlawanan pada kedua SR-FF tersebut. Clk J K 0 X X 1 0 0 1 0 1 1 1 Qt Ket t Qt-1 tt 1 Memory 1 Reset 1 0 Set t-1 Qt-1 Toggle t

Tuliskan persamaannya dan buktikan. . !!!

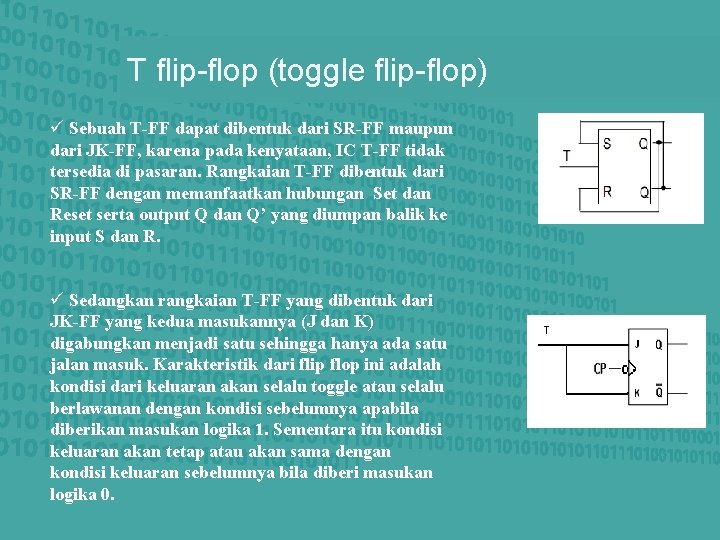

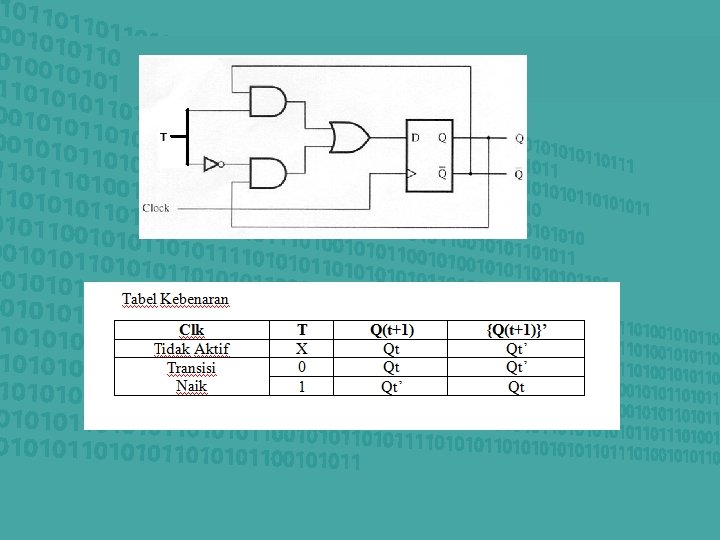

T flip-flop (toggle flip-flop) ü Sebuah T-FF dapat dibentuk dari SR-FF maupun dari JK-FF, karena pada kenyataan, IC T-FF tidak tersedia di pasaran. Rangkaian T-FF dibentuk dari SR-FF dengan memanfaatkan hubungan Set dan Reset serta output Q dan Q’ yang diumpan balik ke input S dan R. ü Sedangkan rangkaian T-FF yang dibentuk dari JK-FF yang kedua masukannya (J dan K) digabungkan menjadi satu sehingga hanya ada satu jalan masuk. Karakteristik dari flip flop ini adalah kondisi dari keluaran akan selalu toggle atau selalu berlawanan dengan kondisi sebelumnya apabila diberikan masukan logika 1. Sementara itu kondisi keluaran akan tetap atau akan sama dengan kondisi keluaran sebelumnya bila diberi masukan logika 0.

Tuliskan persamaannya dan buktikan. . !!!

TERIMA KASIH ATAS PERHATIAN NYA!!!

- Slides: 32