Flip Flops Objectives SR latch SR Latch with

Flip Flops

Objectives • • • SR latch SR Latch with enable (SR Flip-Flop) D Flip-Flop JK Flip-Flop T Flip-Flop

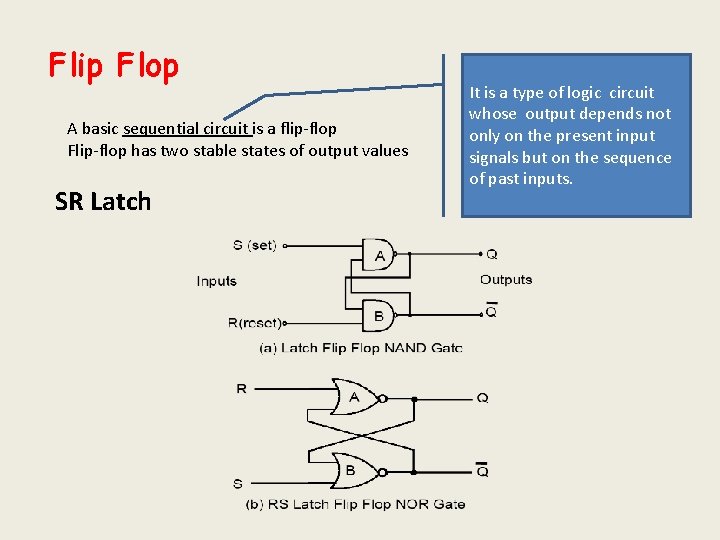

Flip Flop A basic sequential circuit is a flip-flop Flip-flop has two stable states of output values SR Latch It is a type of logic circuit whose output depends not only on the present input signals but on the sequence of past inputs.

Flip-Flops • Latches are “transparent” (= any change on the inputs is seen at the outputs immediately). • This causes synchronization problems. • Solution: use latches to create flip-flops that can respond (update) only on specific times (instead of any time). • Types: RS flip-flop , D flip-flop etc.

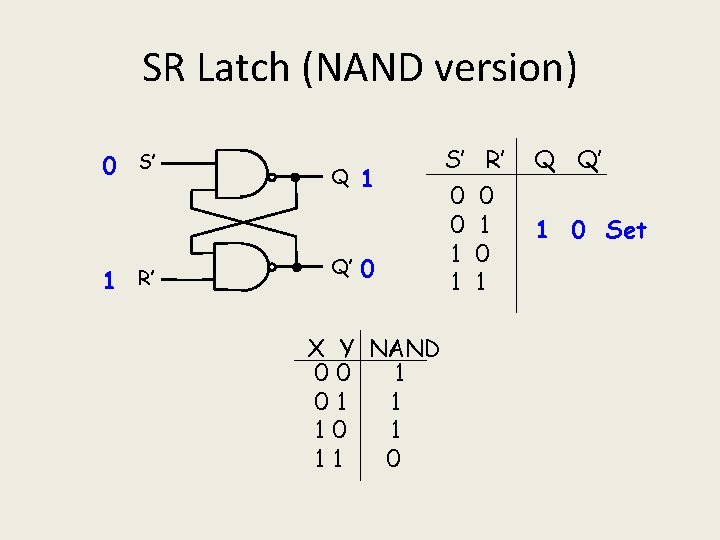

SR Latch (NAND version) 0 S’ 1 R’ Q Q’ 1 0 X Y NAND 00 1 01 1 10 1 11 0 S’ 0 0 1 1 R’ 0 1 Q Q’ 1 0 Set

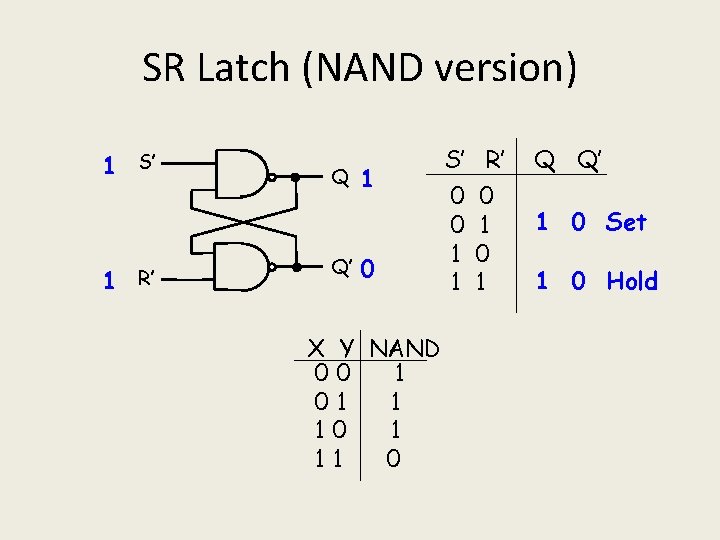

SR Latch (NAND version) 1 S’ 1 R’ Q Q’ 1 0 X Y NAND 00 1 01 1 10 1 11 0 S’ 0 0 1 1 R’ 0 1 Q Q’ 1 0 Set 1 0 Hold

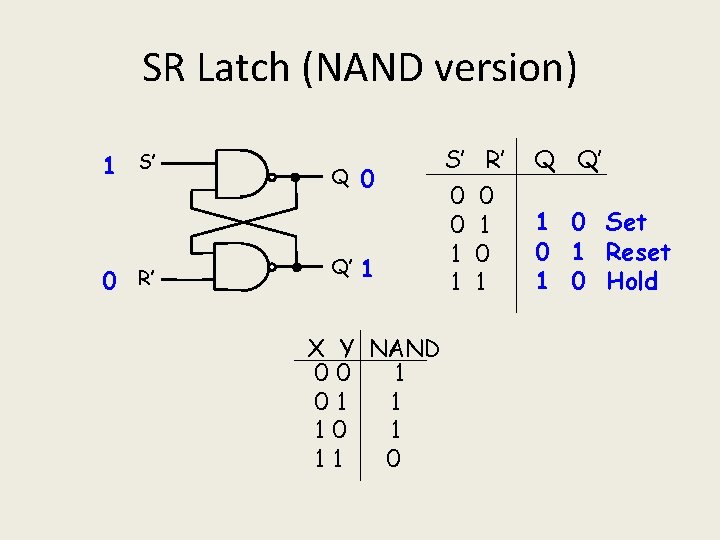

SR Latch (NAND version) 1 S’ 0 R’ Q Q’ 0 1 X Y NAND 00 1 01 1 10 1 11 0 S’ 0 0 1 1 R’ 0 1 Q Q’ 1 0 Set 0 1 Reset 1 0 Hold

SR Latch (NAND version) 1 S’ 1 R’ Q Q’ 0 1 X Y NAND 00 1 01 1 10 1 11 0 S’ 0 0 1 1 R’ 0 1 Q Q’ 1 0 0 1 Set Reset Hold

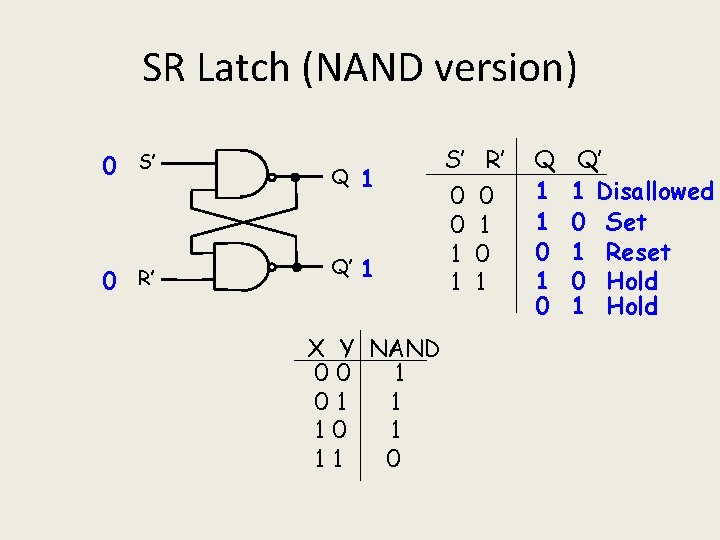

SR Latch (NAND version) 0 S’ 0 R’ Q 1 Q’ 1 X Y NAND 00 1 01 1 10 1 11 0 S’ 0 0 1 1 R’ 0 1 Q 1 1 0 Q’ 1 Disallowed 0 Set 1 Reset 0 Hold 1 Hold

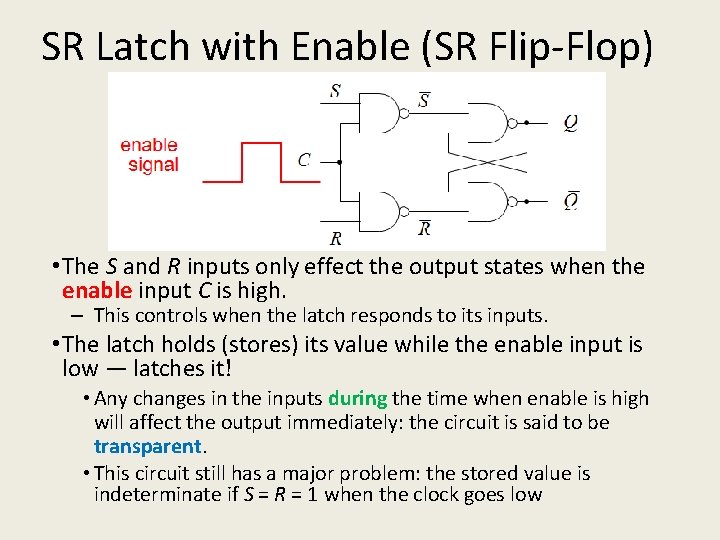

SR Latch with Enable (SR Flip-Flop) • The S and R inputs only effect the output states when the enable input C is high. – This controls when the latch responds to its inputs. • The latch holds (stores) its value while the enable input is low — latches it! • Any changes in the inputs during the time when enable is high will affect the output immediately: the circuit is said to be transparent. • This circuit still has a major problem: the stored value is indeterminate if S = R = 1 when the clock goes low

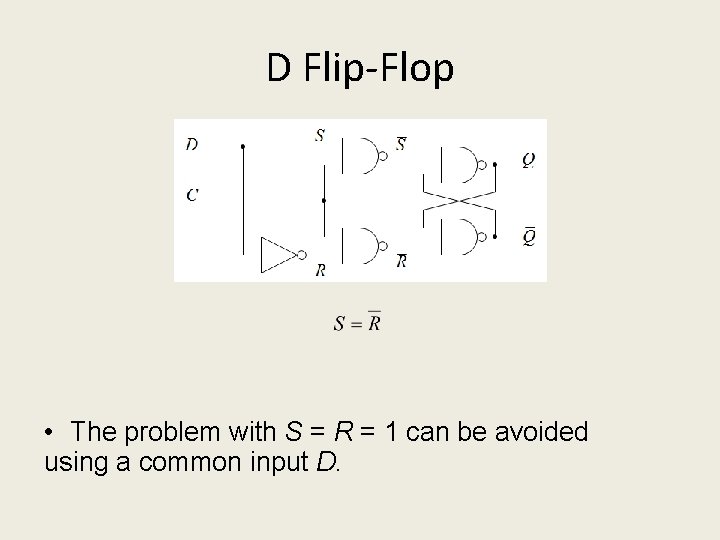

D Flip-Flop • The problem with S = R = 1 can be avoided using a common input D.

D Flip-Flop D C Qn Qn+1 0 0 1 0 1 1 description D Q Clear (reset) Set input at clock output outpu t befor Qn +1 = D after e clock A D flip-flop simply stores the value on its D input at the clock transition. The previous value stored, Qn, has no effect, unlike other flip-flops. It therefore acts as a simple memory or ‘latch’. The most widely used flip-flops: simple to build and design with. A register comprises several D flip-flops, one for each bit to be stored. Q

JK Flip-Flop

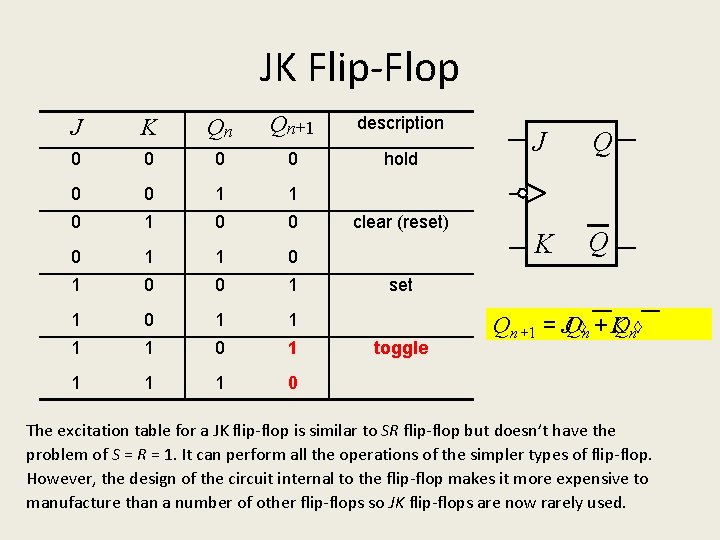

JK Flip-Flop J K Qn Qn+1 description 0 0 hold 0 0 1 1 0 1 0 0 1 1 1 1 0 clear (reset) J Q K Q set toggle Qn+1 = JQ◊n + K Qn◊ The excitation table for a JK flip-flop is similar to SR flip-flop but doesn’t have the problem of S = R = 1. It can perform all the operations of the simpler types of flip-flop. However, the design of the circuit internal to the flip-flop makes it more expensive to manufacture than a number of other flip-flops so JK flip-flops are now rarely used.

T-flip-flop

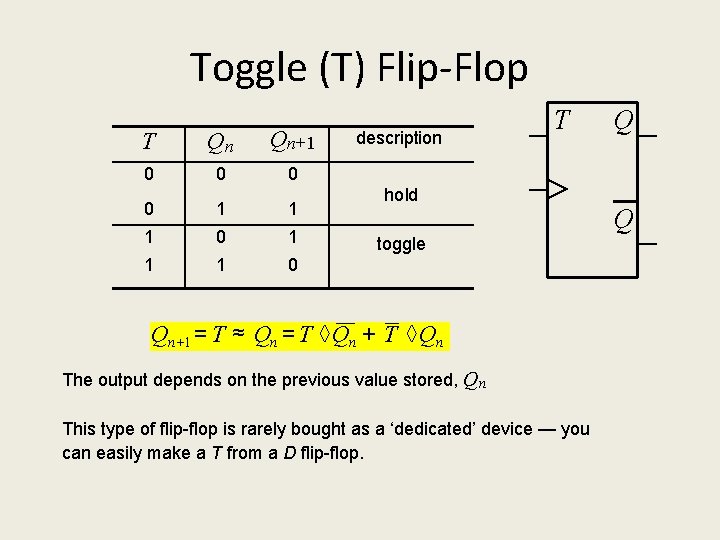

Toggle (T) Flip-Flop T Qn Qn+1 0 0 1 1 1 0 description T hold toggle Qn +1 = T ≈ Qn = T ◊ Qn + T ◊ Qn The output depends on the previous value stored, Qn. This type of flip-flop is rarely bought as a ‘dedicated’ device — you can easily make a T from a D flip-flop. Q Q

K N A H T OU Y

- Slides: 17