Fixedgain CMOS Differential Amplifiers for the 40 K

![IV. 5 Cryogenic tests: DC Vout [V] Vin [V] DC transfer characteristic for two IV. 5 Cryogenic tests: DC Vout [V] Vin [V] DC transfer characteristic for two](https://slidetodoc.com/presentation_image_h2/42ebbcde7035342aa402053adeef28fc/image-18.jpg)

- Slides: 24

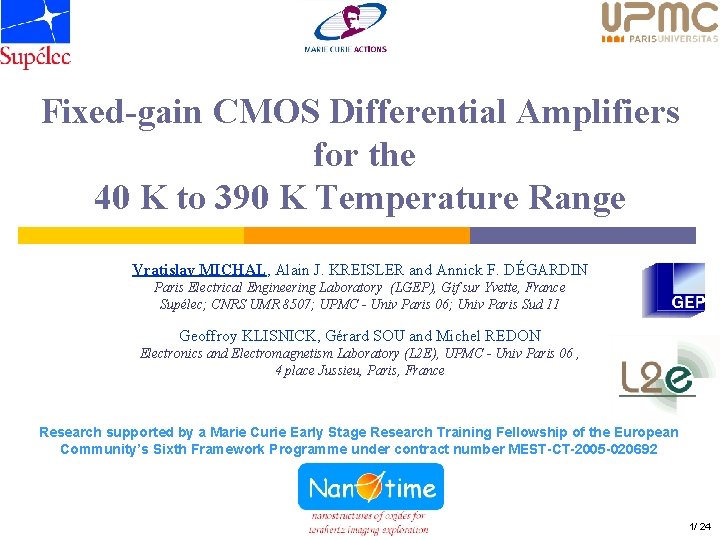

Fixed-gain CMOS Differential Amplifiers for the 40 K to 390 K Temperature Range Vratislav MICHAL, Alain J. KREISLER and Annick F. DÉGARDIN Paris Electrical Engineering Laboratory (LGEP), Gif sur Yvette, France Supélec; CNRS UMR 8507; UPMC - Univ Paris 06; Univ Paris Sud 11 Geoffroy KLISNICK, Gérard SOU and Michel REDON Electronics and Electromagnetism Laboratory (L 2 E), UPMC - Univ Paris 06 , 4 place Jussieu, Paris, France Research supported by a Marie Curie Early Stage Research Training Fellowship of the European Community’s Sixth Framework Programme under contract number MEST-CT-2005 -020692 1/ 24

Outline I. Our objectives II. Introduction / design approach III. First design & results IV. Second design & results V. Conclusions Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 2

I. Our objectives Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 3

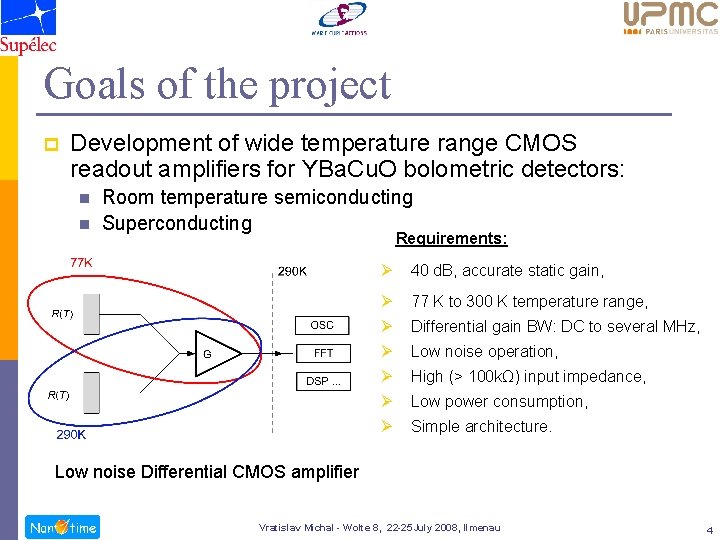

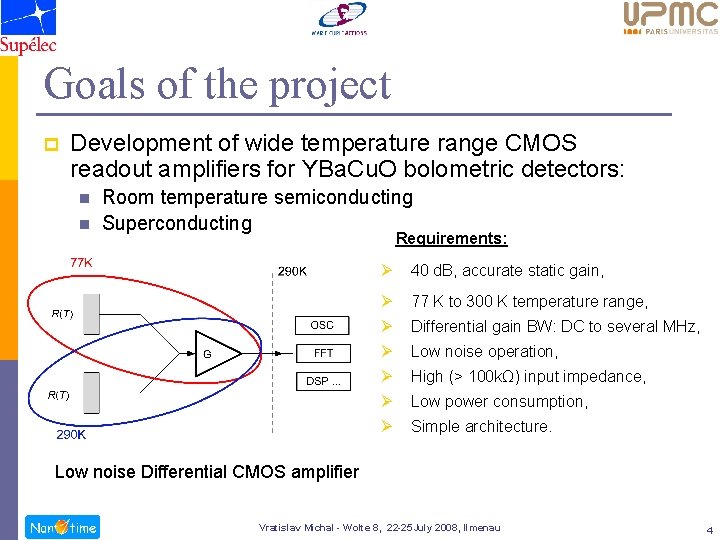

Goals of the project p Development of wide temperature range CMOS readout amplifiers for YBa. Cu. O bolometric detectors: n n Room temperature semiconducting Superconducting Requirements: Ø 40 d. B, accurate static gain, Ø 77 K to 300 K temperature range, Ø Differential gain BW: DC to several MHz, Ø Low noise operation, Ø High (> 100 kΩ) input impedance, Ø Low power consumption, Ø Simple architecture. Low noise Differential CMOS amplifier Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 4

II. Introduction / design approach Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 5

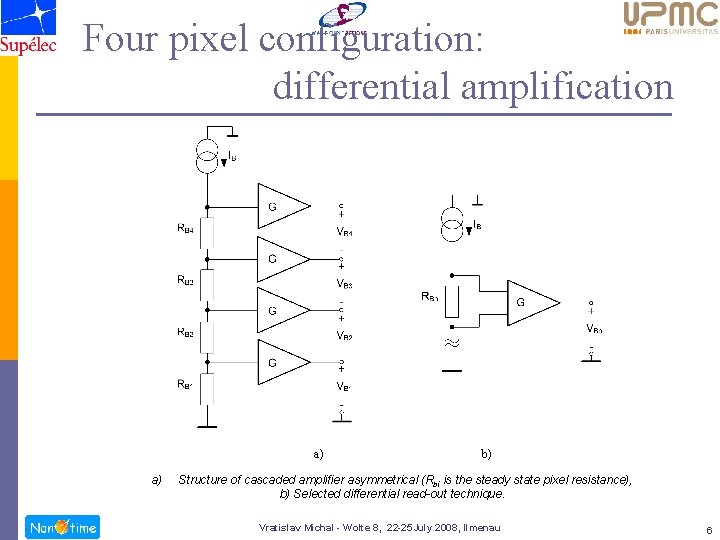

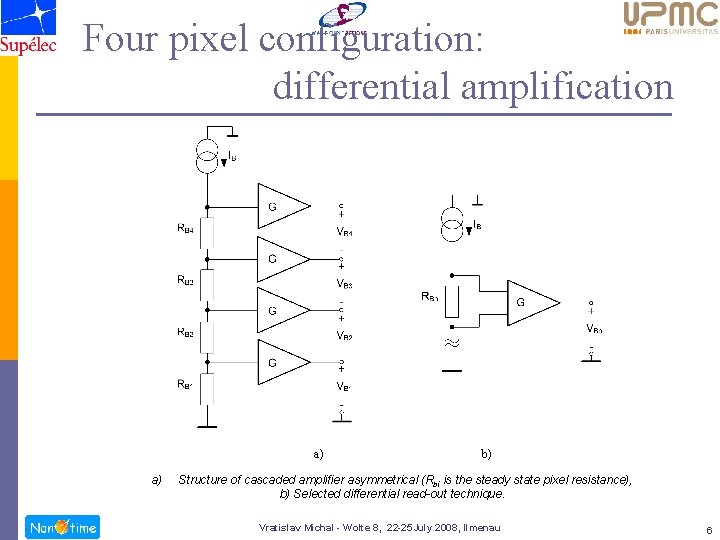

Four pixel configuration: differential amplification a) a) b) Structure of cascaded amplifier asymmetrical (Rbi is the steady state pixel resistance), b) Selected differential read-out technique. Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 6

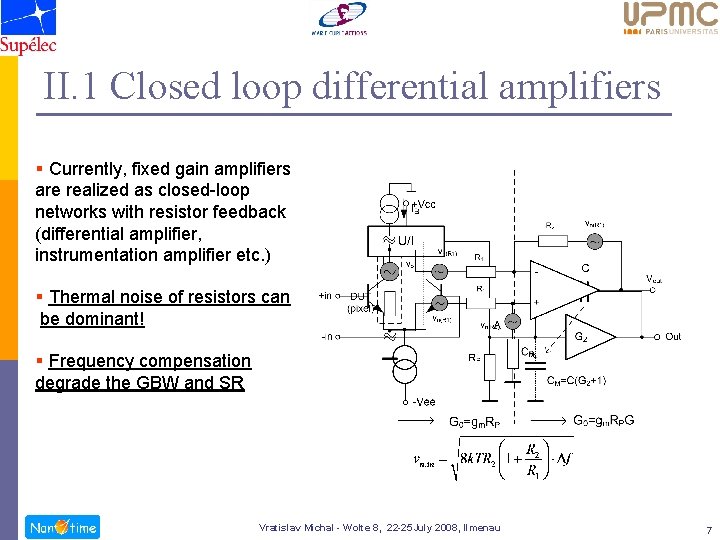

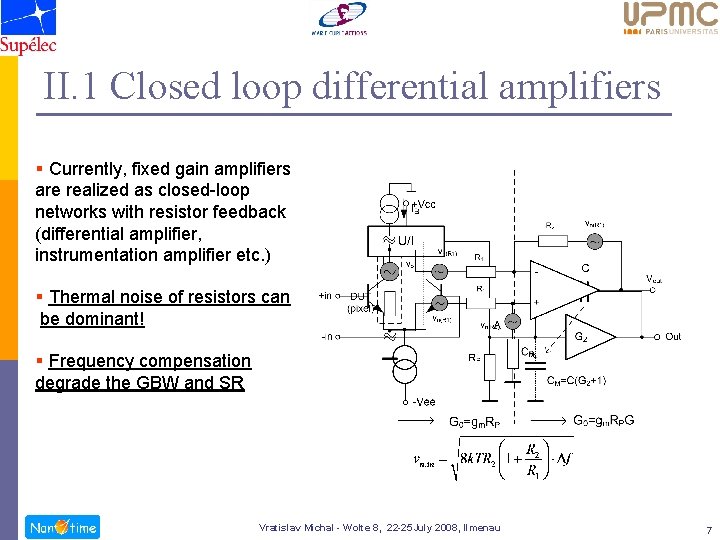

II. 1 Closed loop differential amplifiers § Currently, fixed gain amplifiers are realized as closed-loop networks with resistor feedback (differential amplifier, instrumentation amplifier etc. ) § Thermal noise of resistors can be dominant! § Frequency compensation degrade the GBW and SR Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 7

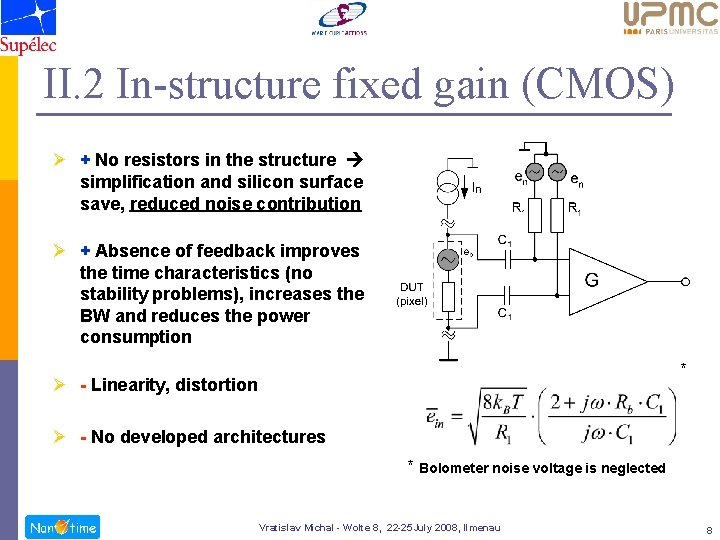

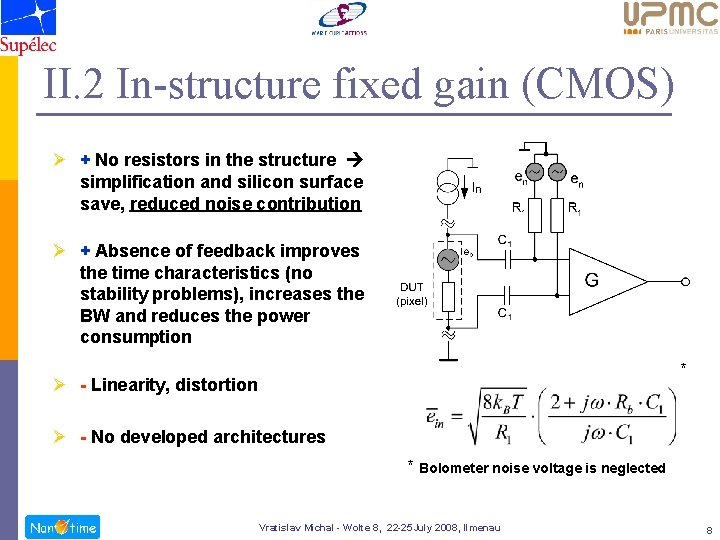

II. 2 In-structure fixed gain (CMOS) Ø + No resistors in the structure simplification and silicon surface save, reduced noise contribution Ø + Absence of feedback improves the time characteristics (no stability problems), increases the BW and reduces the power consumption * Ø - Linearity, distortion Ø - No developed architectures * Bolometer noise voltage is neglected Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 8

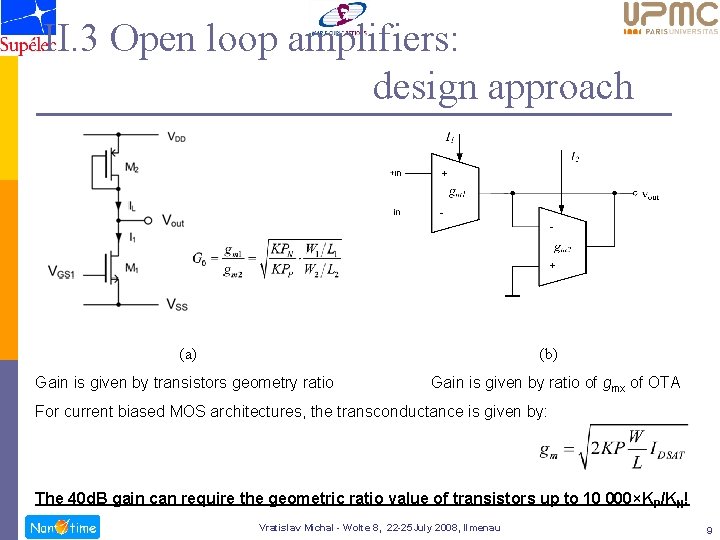

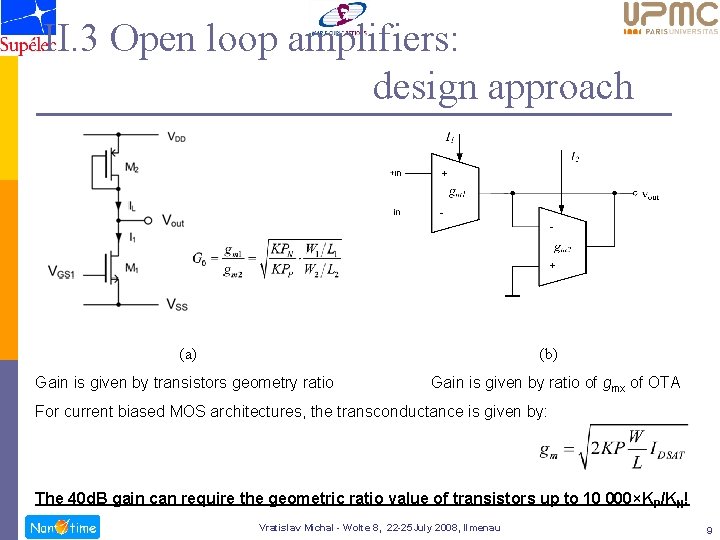

II. 3 Open loop amplifiers: design approach (a) (b) Gain is given by transistors geometry ratio Gain is given by ratio of gmx of OTA For current biased MOS architectures, the transconductance is given by: The 40 d. B gain can require the geometric ratio value of transistors up to 10 000×KP/KN! Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 9

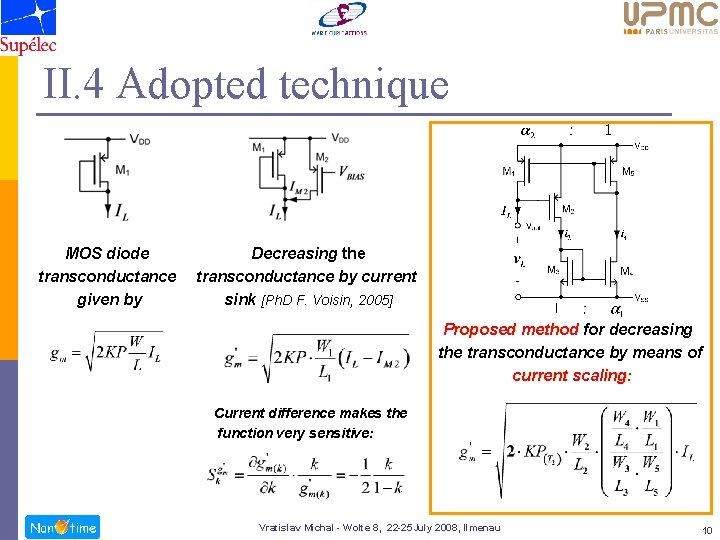

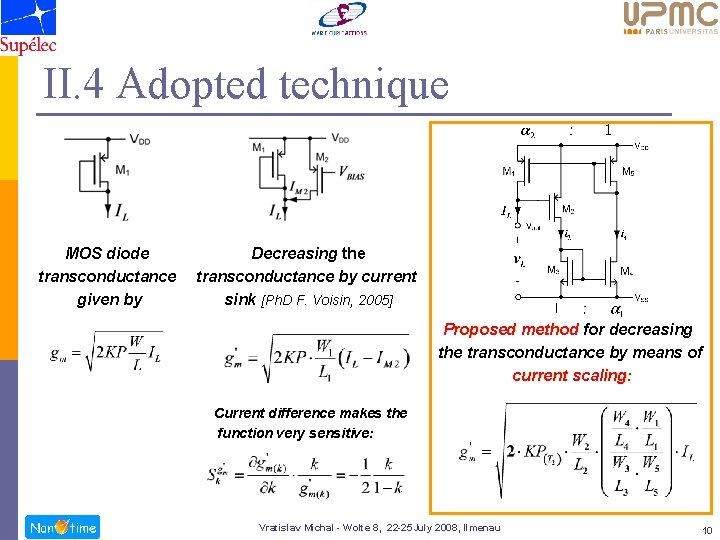

II. 4 Adopted technique MOS diode transconductance given by Decreasing the transconductance by current sink [Ph. D F. Voisin, 2005] Proposed method for decreasing the transconductance by means of current scaling: Current difference makes the function very sensitive: Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 10

III. First design & results Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 11

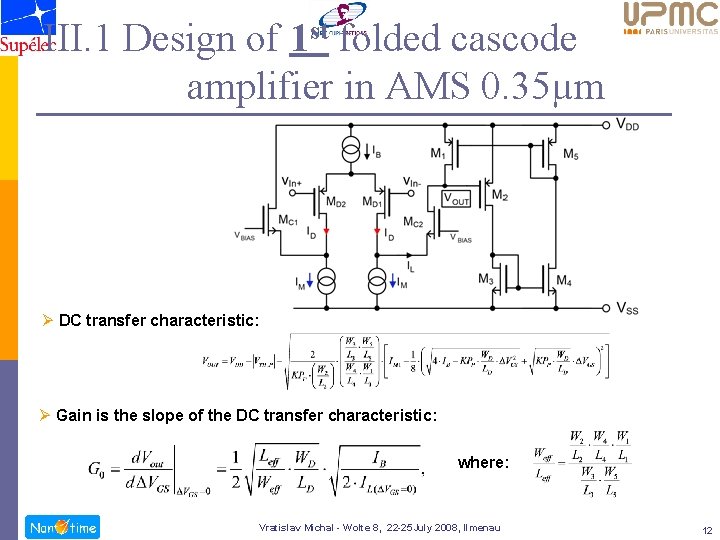

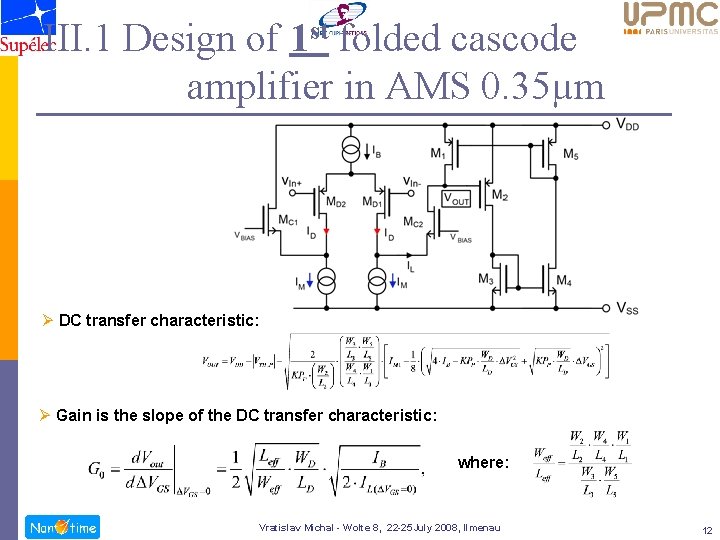

III. 1 Design of 1 st folded cascode amplifier in AMS 0. 35µm Ø DC transfer characteristic: Ø Gain is the slope of the DC transfer characteristic: where: Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 12

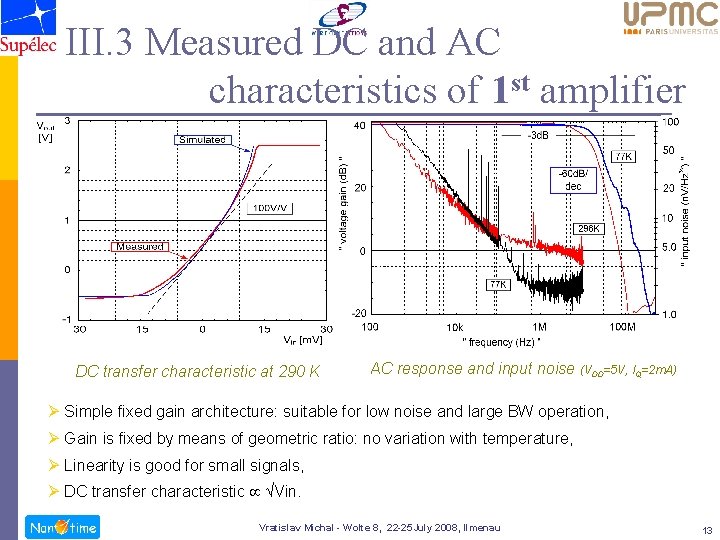

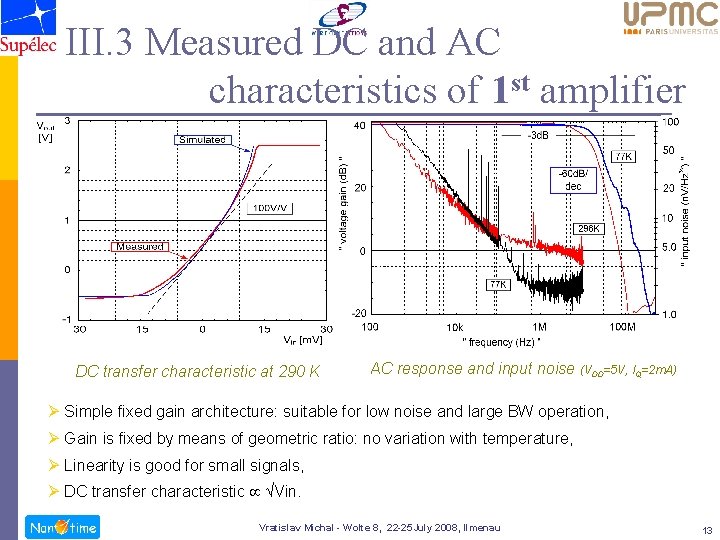

III. 3 Measured DC and AC characteristics of 1 st amplifier DC transfer characteristic at 290 K AC response and input noise (VDD=5 V, IQ=2 m. A) Ø Simple fixed gain architecture: suitable for low noise and large BW operation, Ø Gain is fixed by means of geometric ratio: no variation with temperature, Ø Linearity is good for small signals, Ø DC transfer characteristic √Vin. Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 13

IV. Second design & results Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 14

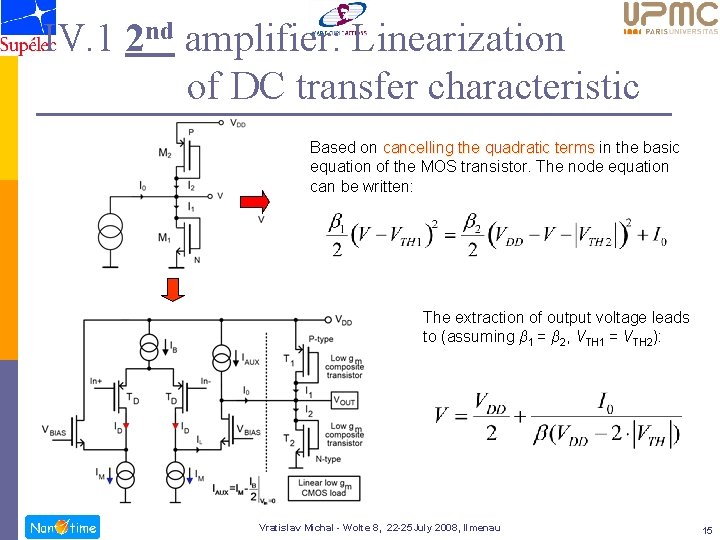

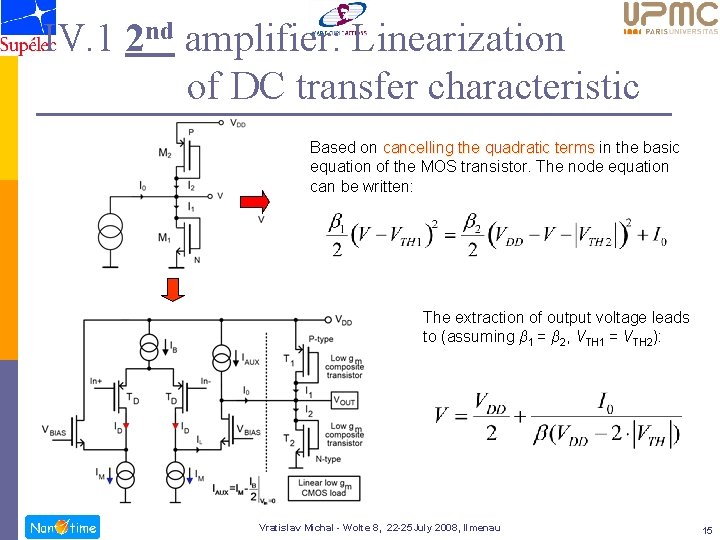

IV. 1 2 nd amplifier: Linearization of DC transfer characteristic Based on cancelling the quadratic terms in the basic equation of the MOS transistor. The node equation can be written: The extraction of output voltage leads to (assuming β 1 = β 2, VTH 1 = VTH 2): Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 15

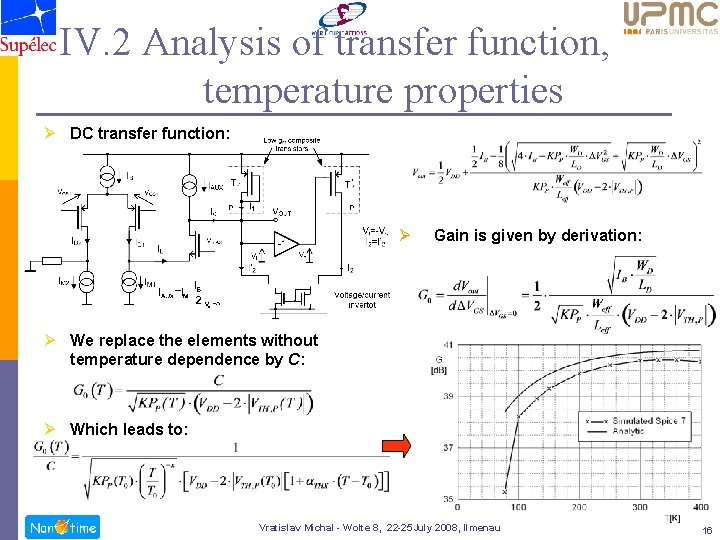

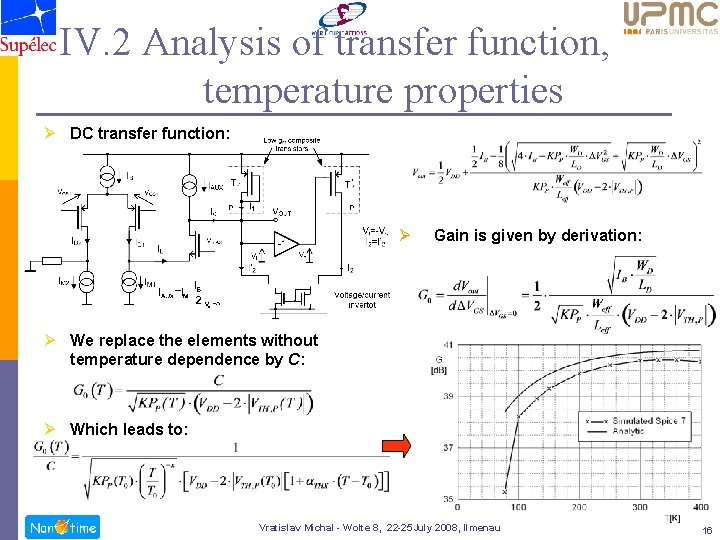

IV. 2 Analysis of transfer function, temperature properties Ø DC transfer function: Ø Gain is given by derivation: Ø We replace the elements without temperature dependence by C: Ø Which leads to: Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 16

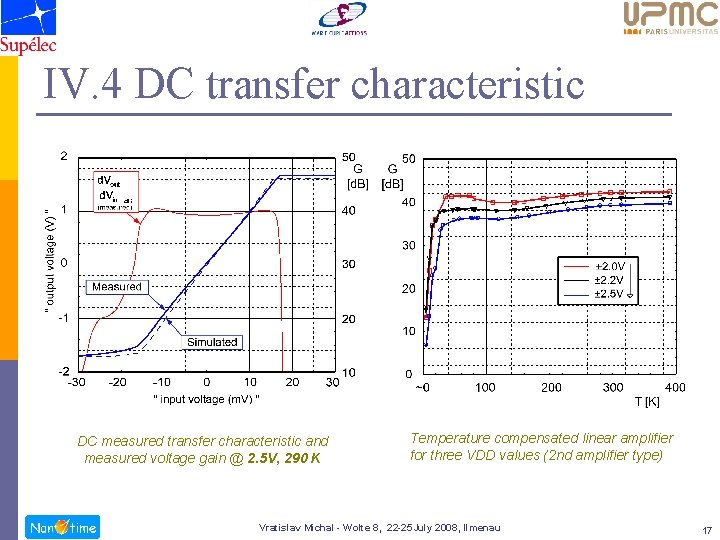

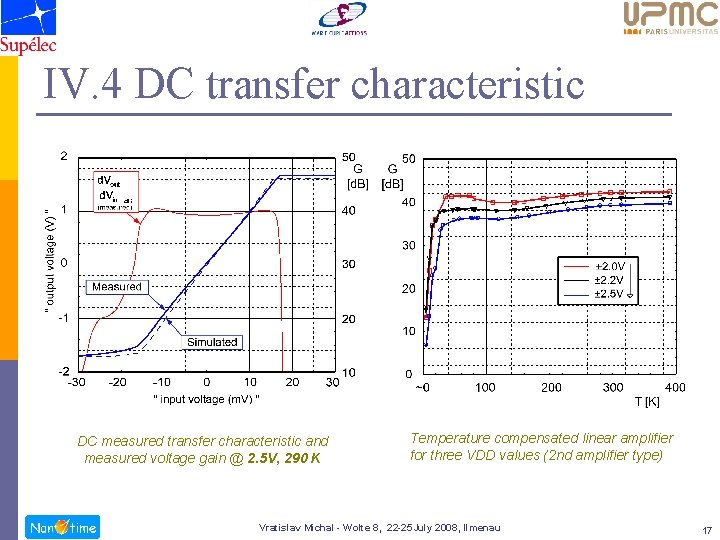

IV. 4 DC transfer characteristic DC measured transfer characteristic and measured voltage gain @ 2. 5 V, 290 K Temperature compensated linear amplifier for three VDD values (2 nd amplifier type) Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 17

![IV 5 Cryogenic tests DC Vout V Vin V DC transfer characteristic for two IV. 5 Cryogenic tests: DC Vout [V] Vin [V] DC transfer characteristic for two](https://slidetodoc.com/presentation_image_h2/42ebbcde7035342aa402053adeef28fc/image-18.jpg)

IV. 5 Cryogenic tests: DC Vout [V] Vin [V] DC transfer characteristic for two DC supply values (2 nd type linear amplifier) Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 18

V. Conclusions Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 19

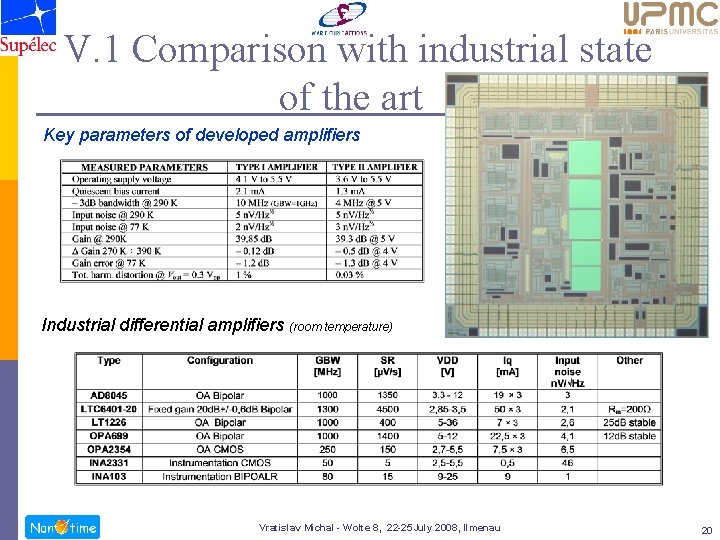

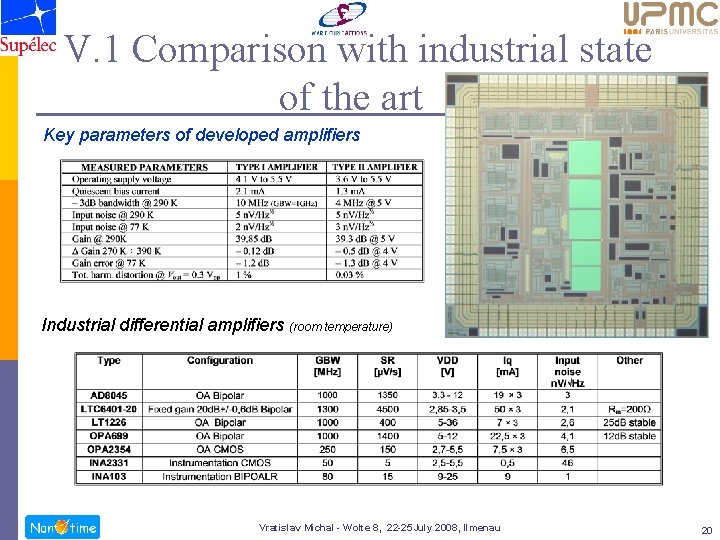

V. 1 Comparison with industrial state of the art Key parameters of developed amplifiers Industrial differential amplifiers (room temperature) Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 20

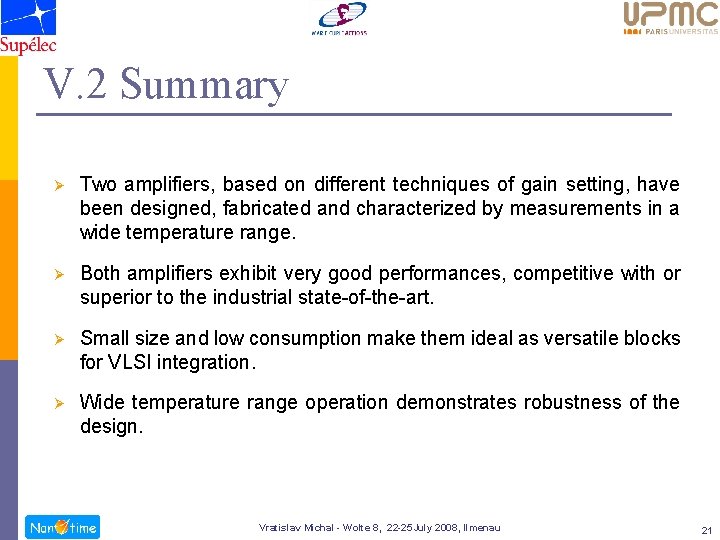

V. 2 Summary Ø Two amplifiers, based on different techniques of gain setting, have been designed, fabricated and characterized by measurements in a wide temperature range. Ø Both amplifiers exhibit very good performances, competitive with or superior to the industrial state-of-the-art. Ø Small size and low consumption make them ideal as versatile blocks for VLSI integration. Ø Wide temperature range operation demonstrates robustness of the design. Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 21

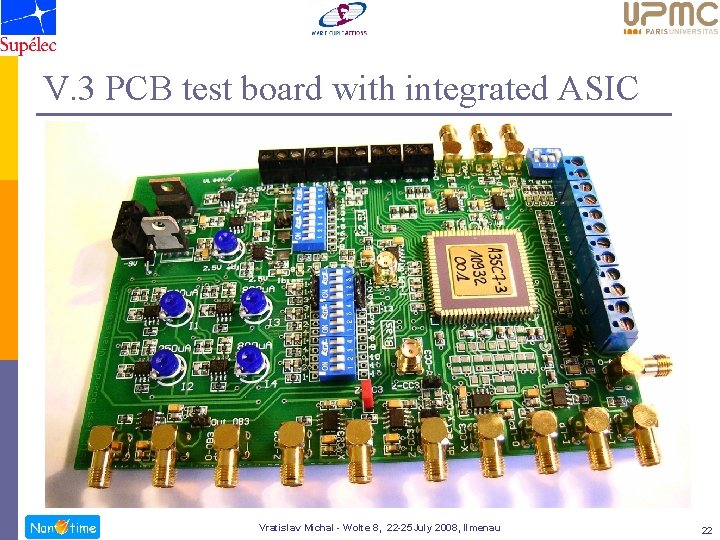

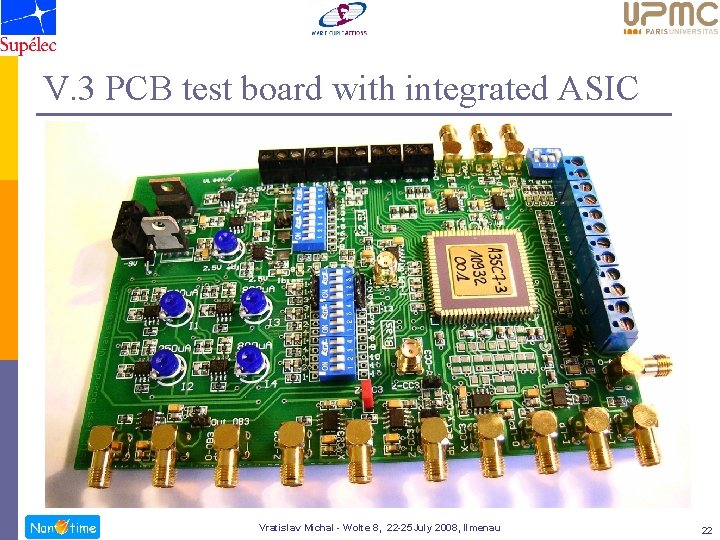

V. 3 PCB test board with integrated ASIC Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 22

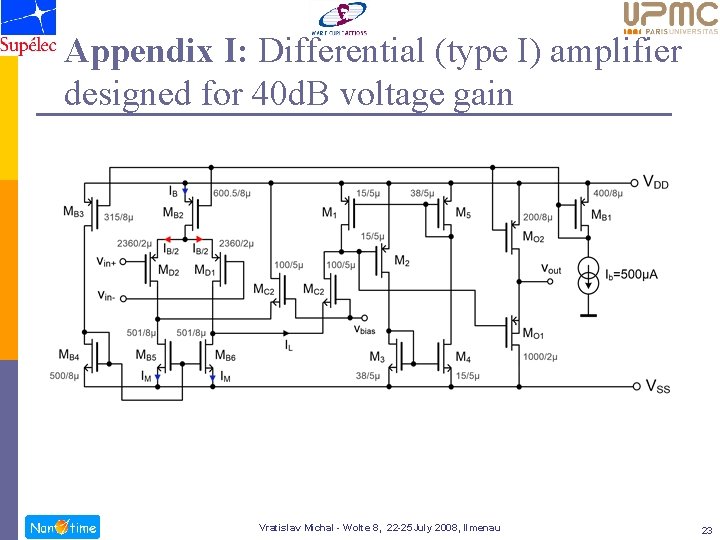

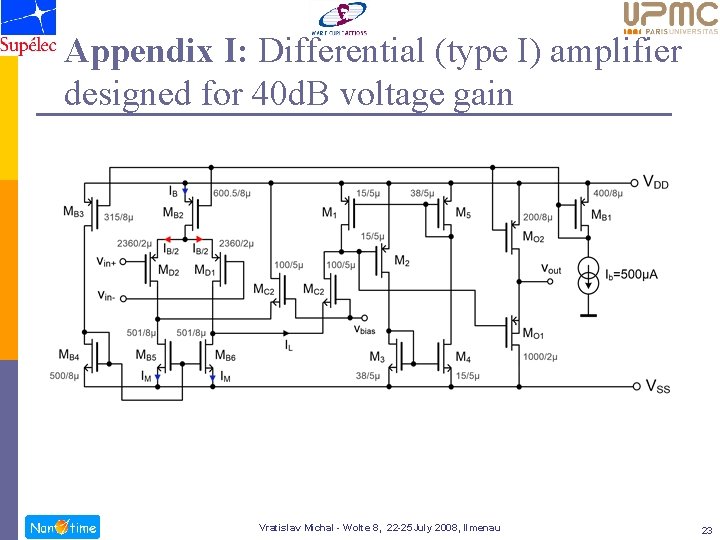

Appendix I: Differential (type I) amplifier designed for 40 d. B voltage gain Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 23

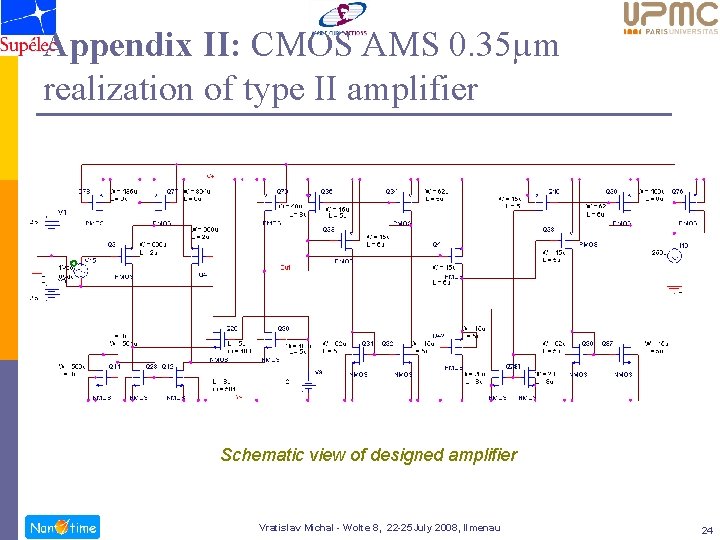

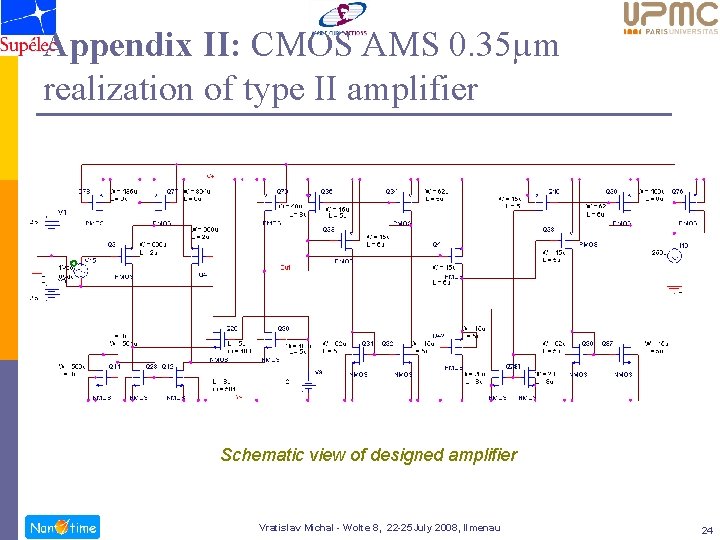

Appendix II: CMOS AMS 0. 35µm realization of type II amplifier Schematic view of designed amplifier Vratislav Michal - Wolte 8, 22 -25 July 2008, Ilmenau 24