First lab measurements of CLICpix 2 Edinei Santin

(First) lab measurements of CLICpix 2 Edinei Santin & Adrian Fiergolski CERN, March 16 th 2017

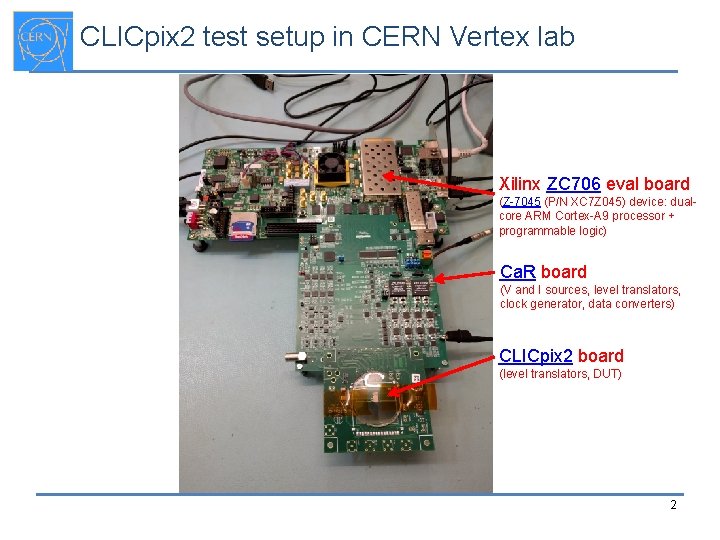

CLICpix 2 test setup in CERN Vertex lab Xilinx ZC 706 eval board (Z-7045 (P/N XC 7 Z 045) device: dualcore ARM Cortex-A 9 processor + programmable logic) Ca. R board (V and I sources, level translators, clock generator, data converters) CLICpix 2 board (level translators, DUT) 2

List of workarounds in Ca. R board n n n Missing Molex power connector (P/N 43650 -0401) soldered temporary connector Incorrect resistor values soldered correct resistors (4 out of 5 LCD boards sent back to SOFTCOM and received today) LVDS/CMOS translators do not have VDD (apparently caused by a typo in global pin names: PWR_OUTx vs PWR_OUT_x) soldered a wire from the intended VDD to the translators VDD pin 3

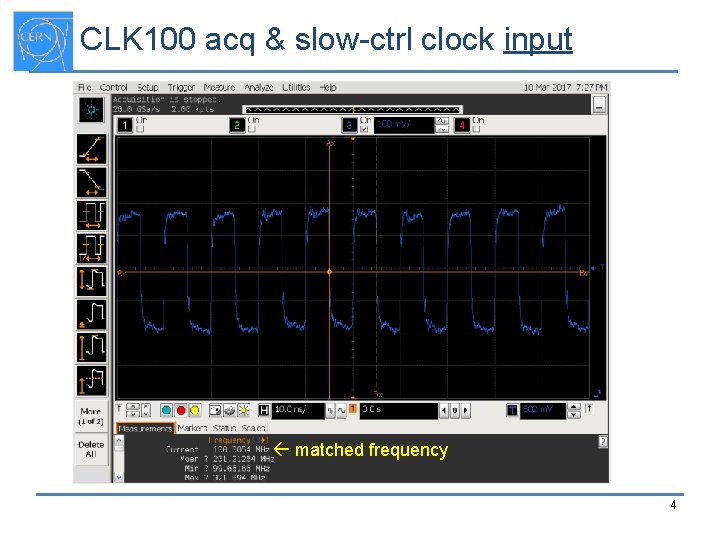

CLK 100 acq & slow-ctrl clock input matched frequency 4

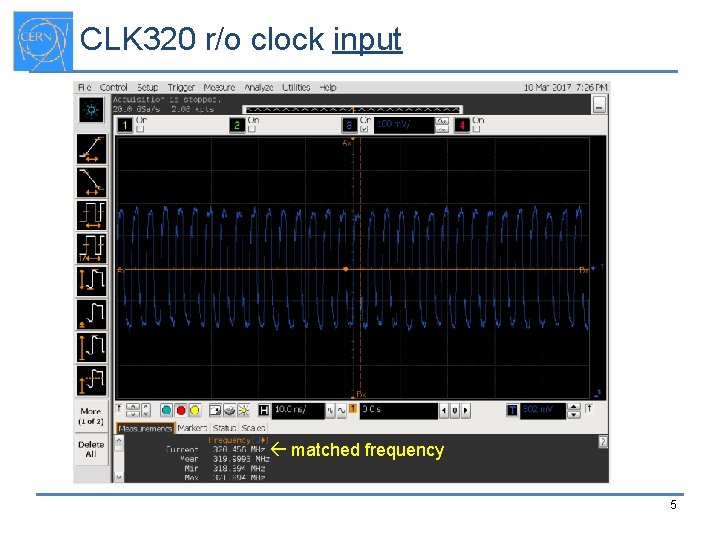

CLK 320 r/o clock input matched frequency 5

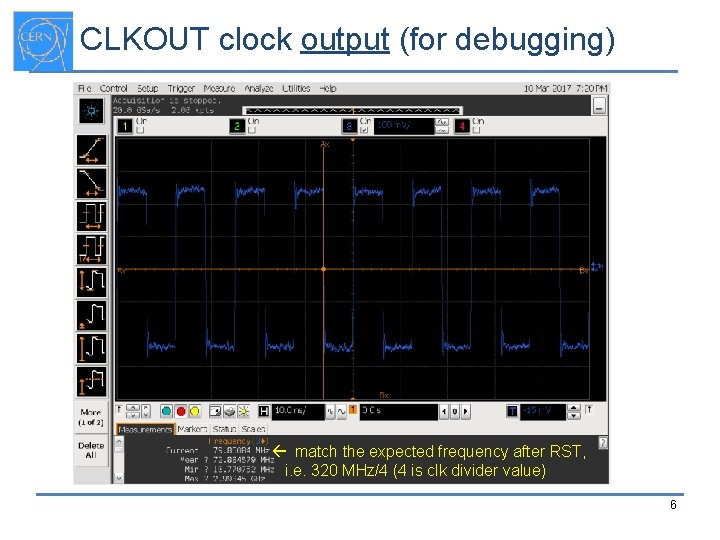

CLKOUT clock output (for debugging) match the expected frequency after RST, i. e. 320 MHz/4 (4 is clk divider value) 6

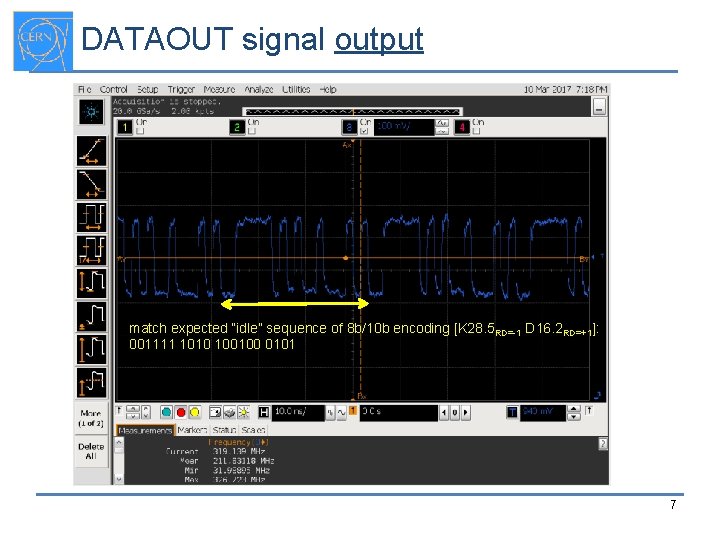

DATAOUT signal output match expected “idle” sequence of 8 b/10 b encoding [K 28. 5 RD=-1 D 16. 2 RD=+1]: 001111 1010 100100 0101 7

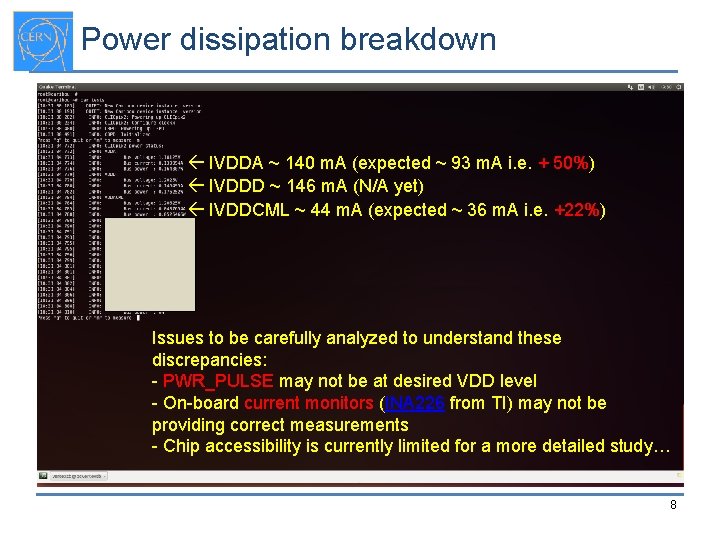

Power dissipation breakdown IVDDA ~ 140 m. A (expected ~ 93 m. A i. e. + 50%) IVDDD ~ 146 m. A (N/A yet) IVDDCML ~ 44 m. A (expected ~ 36 m. A i. e. +22%) Issues to be carefully analyzed to understand these discrepancies: - PWR_PULSE may not be at desired VDD level - On-board current monitors (INA 226 from TI) may not be providing correct measurements - Chip accessibility is currently limited for a more detailed study… 8

- Slides: 8