Firing rule for Grafcet ConcurrentBranching Structure in Grafcet

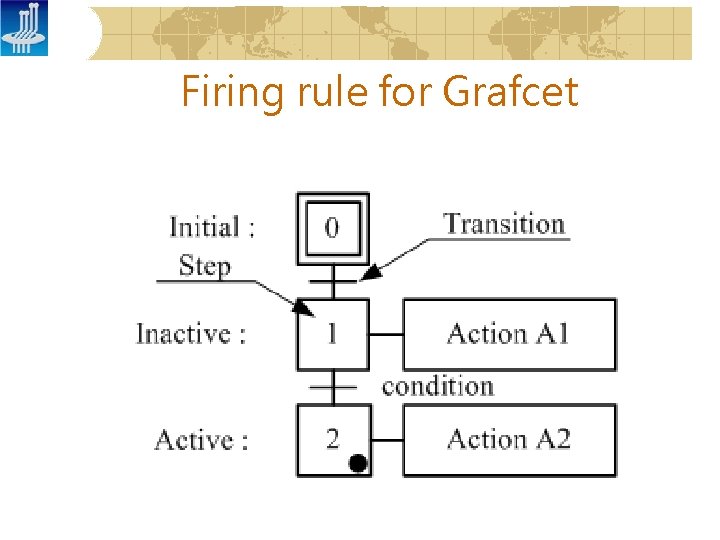

Firing rule for Grafcet

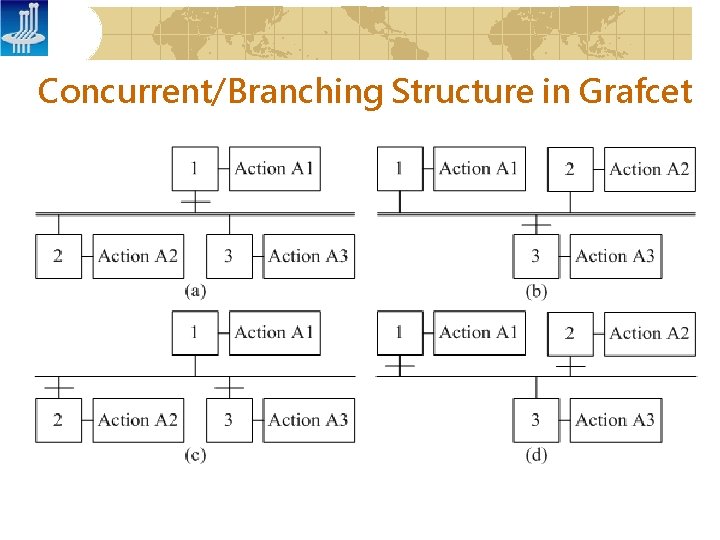

Concurrent/Branching Structure in Grafcet

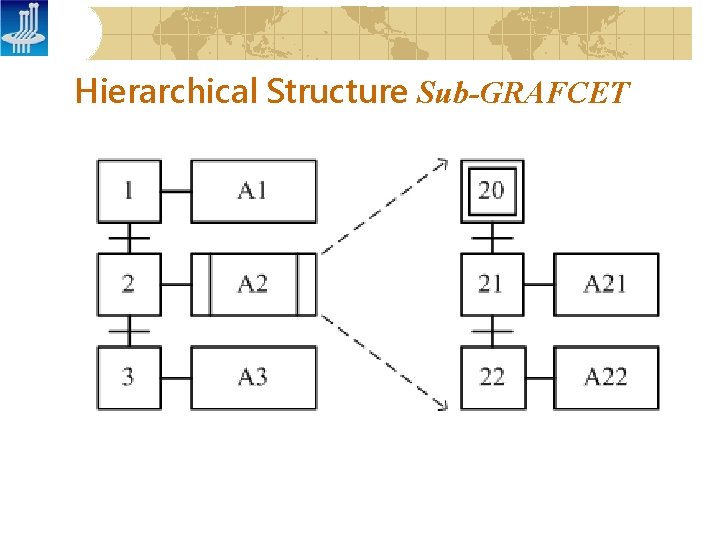

Hierarchical Structure Sub-GRAFCET

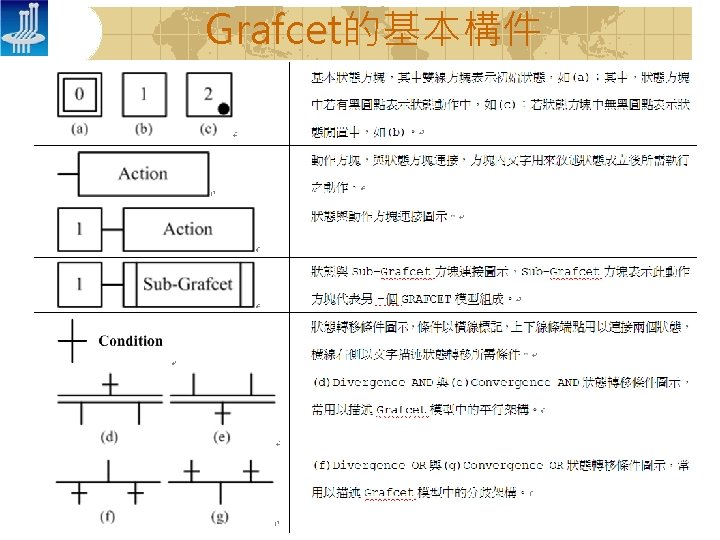

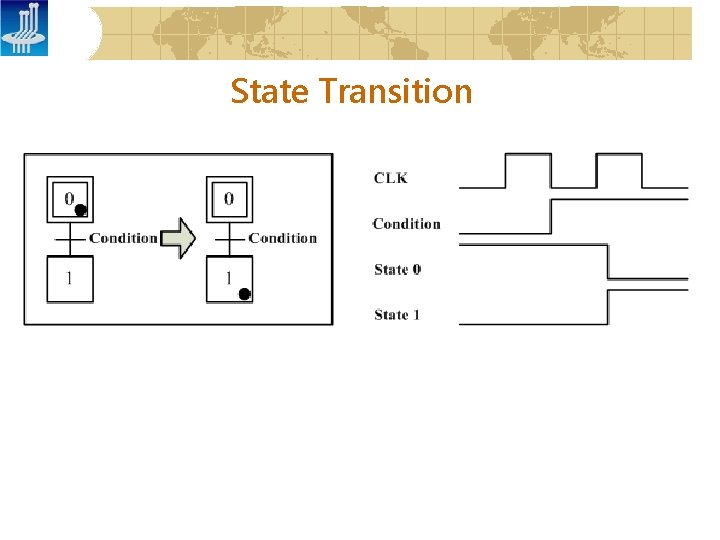

State Transition

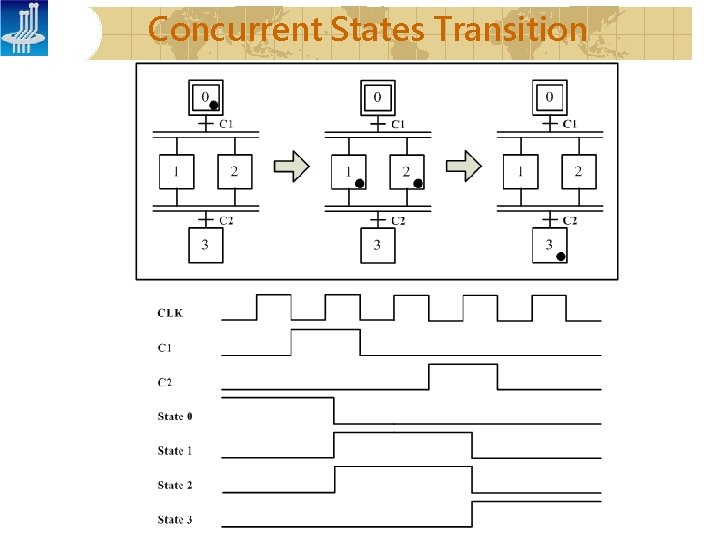

Concurrent States Transition

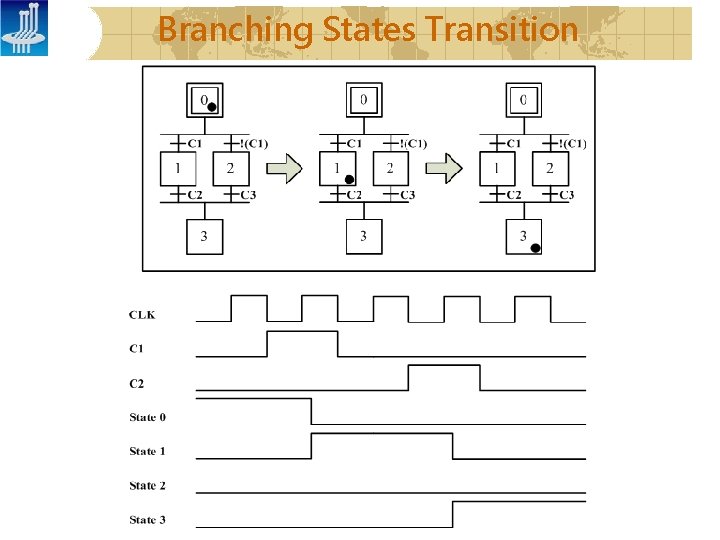

Branching States Transition

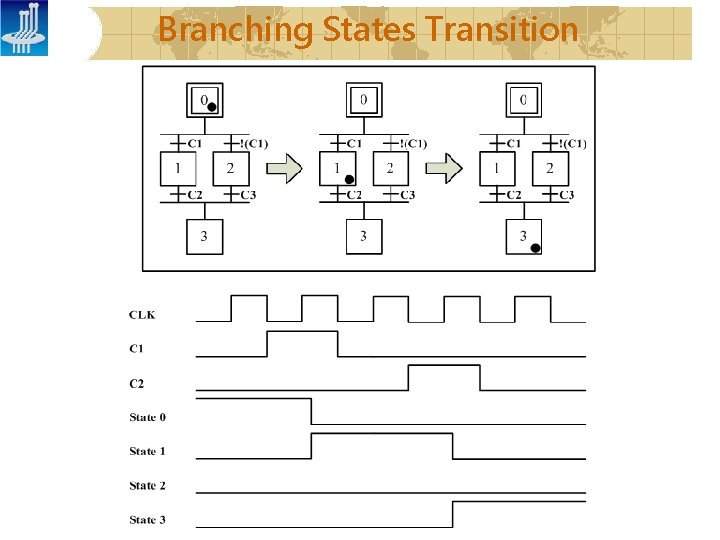

Branching States Transition

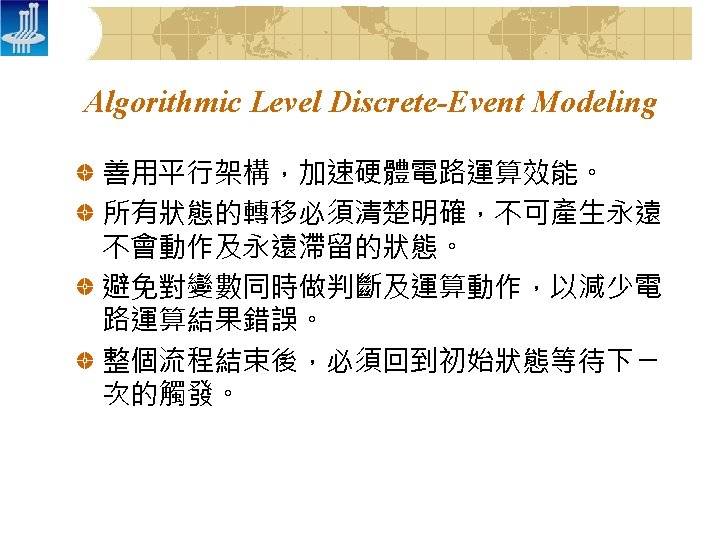

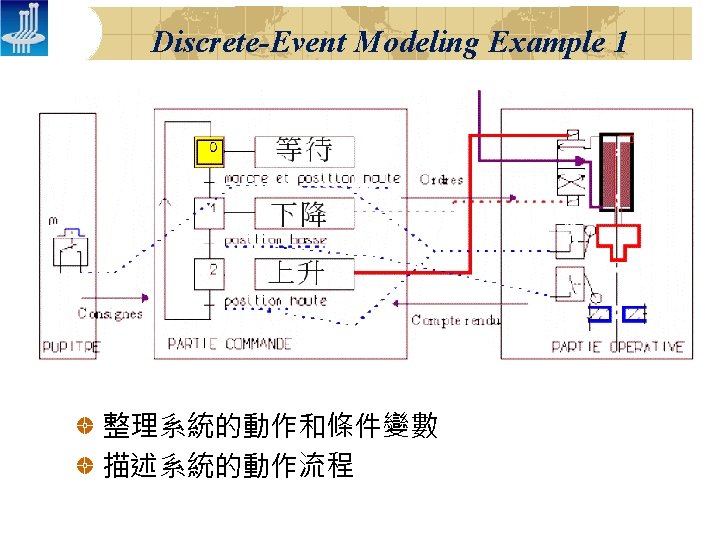

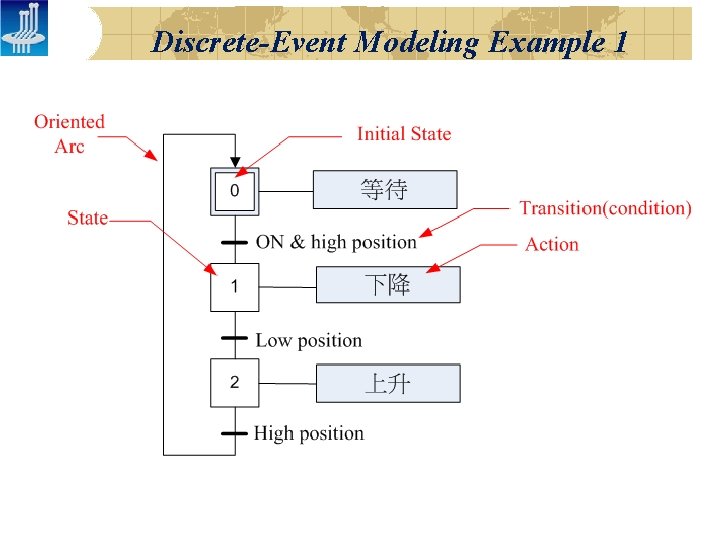

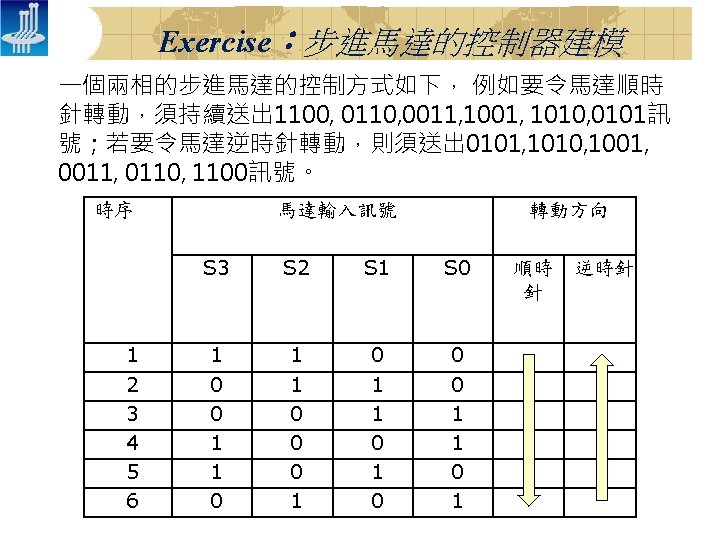

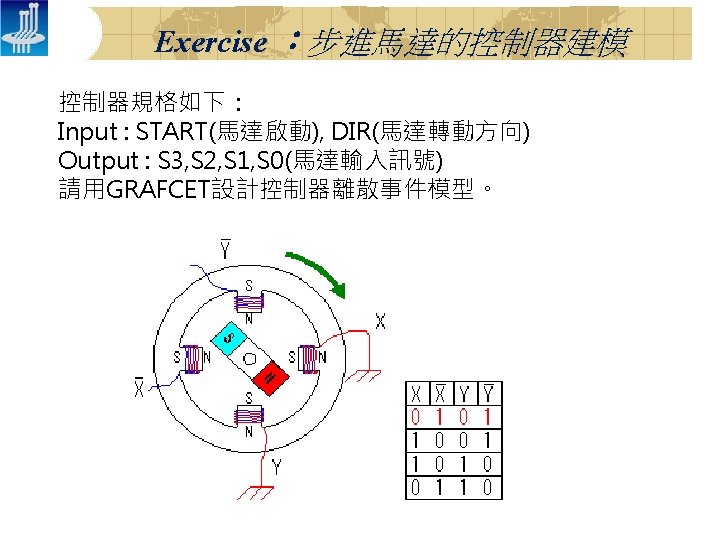

Discrete-Event Modeling Example 1

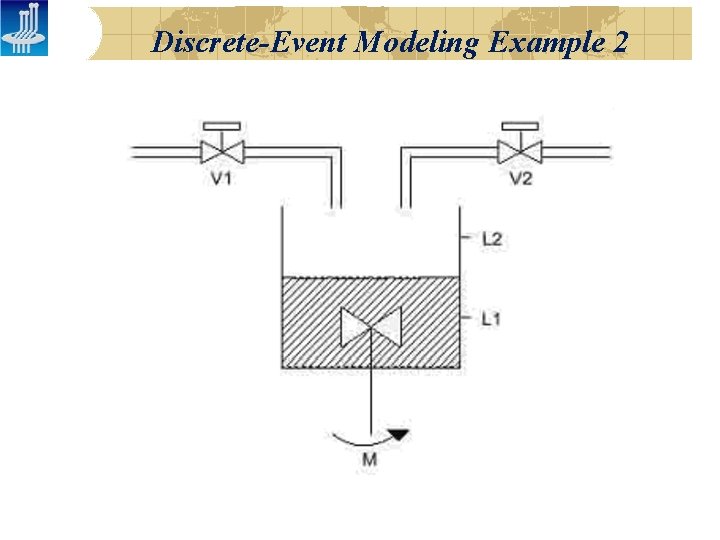

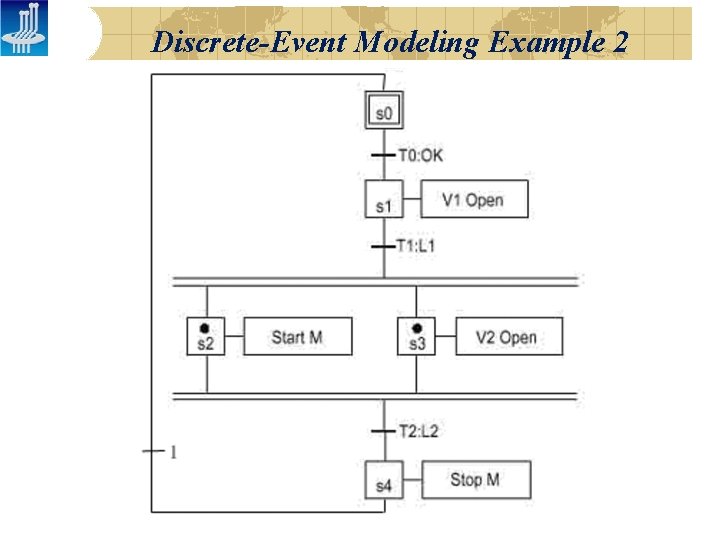

Discrete-Event Modeling Example 2

Discrete-Event Modeling Example 2

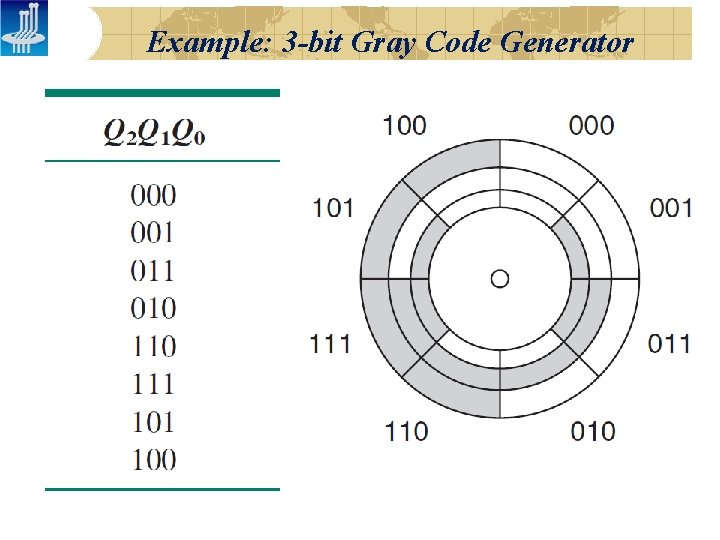

Example: 3 -bit Gray Code Generator

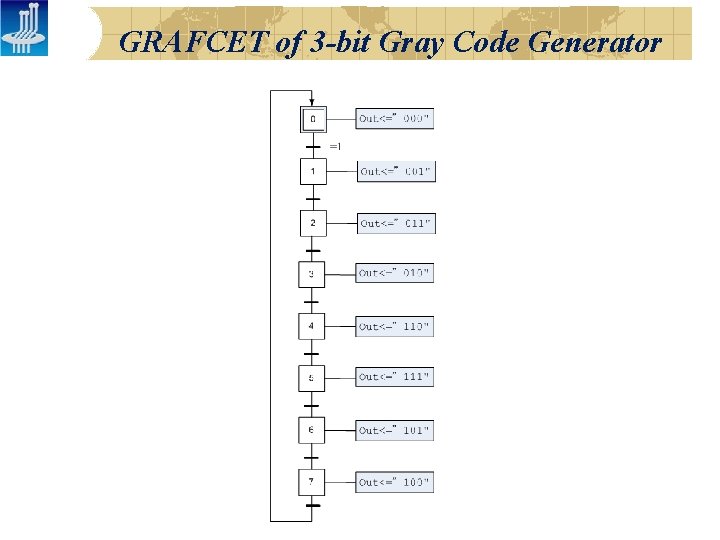

GRAFCET of 3 -bit Gray Code Generator

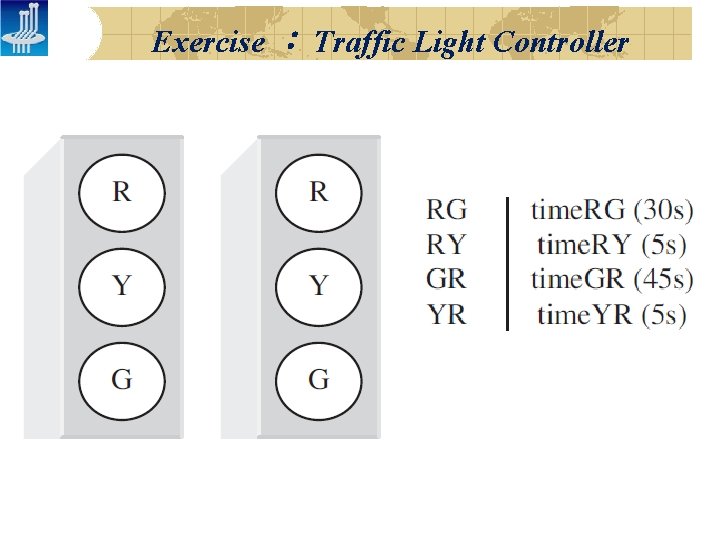

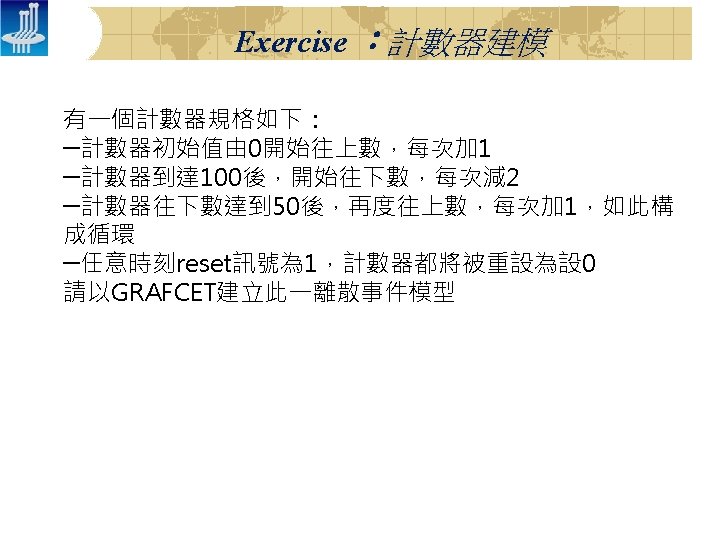

Exercise : Traffic Light Controller

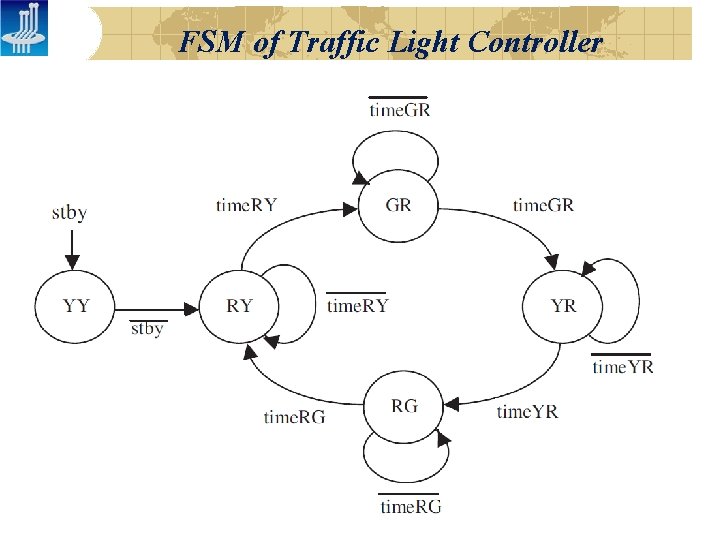

FSM of Traffic Light Controller

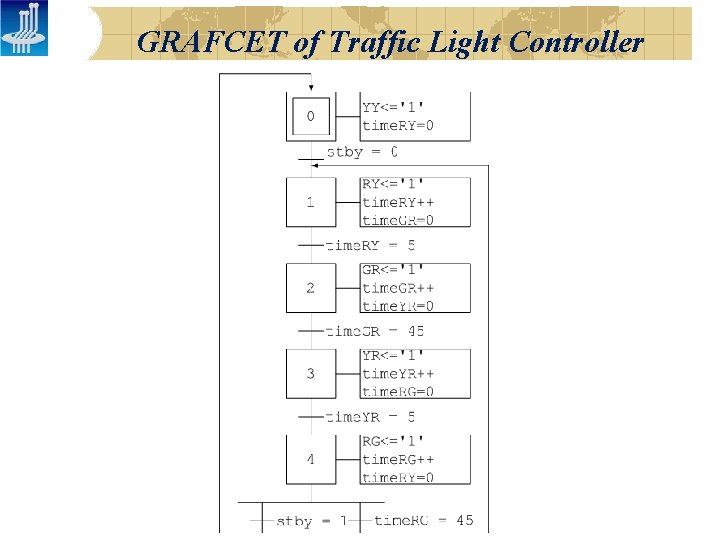

GRAFCET of Traffic Light Controller

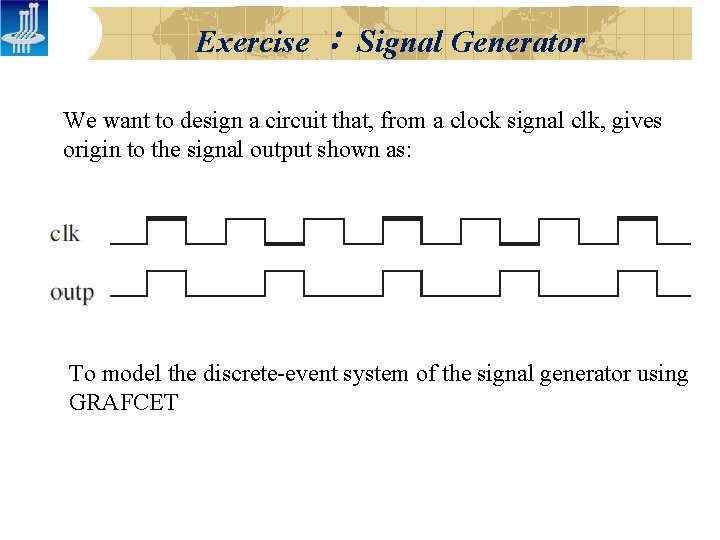

Exercise : Signal Generator We want to design a circuit that, from a clock signal clk, gives origin to the signal output shown as: To model the discrete-event system of the signal generator using GRAFCET

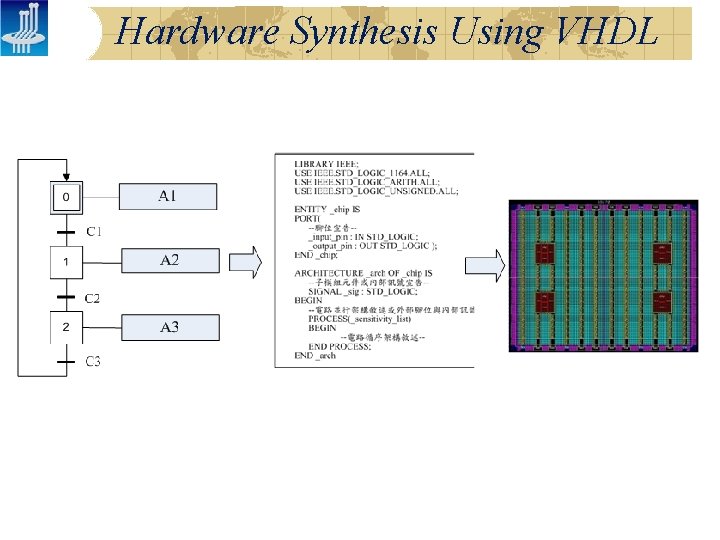

Hardware Synthesis Using VHDL

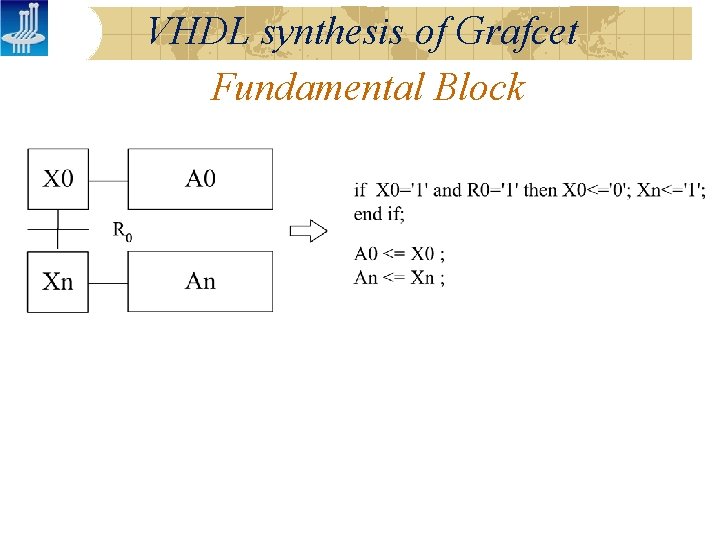

VHDL synthesis of Grafcet Fundamental Block

VHDL synthesis of Grafcet Convergence AND

VHDL synthesis of Grafcet Divergence AND

VHDL synthesis of Grafcet Convergence OR

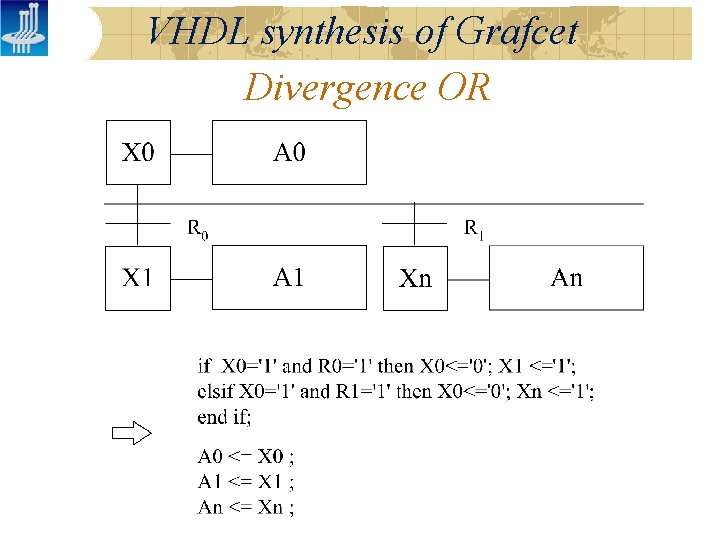

VHDL synthesis of Grafcet Divergence OR

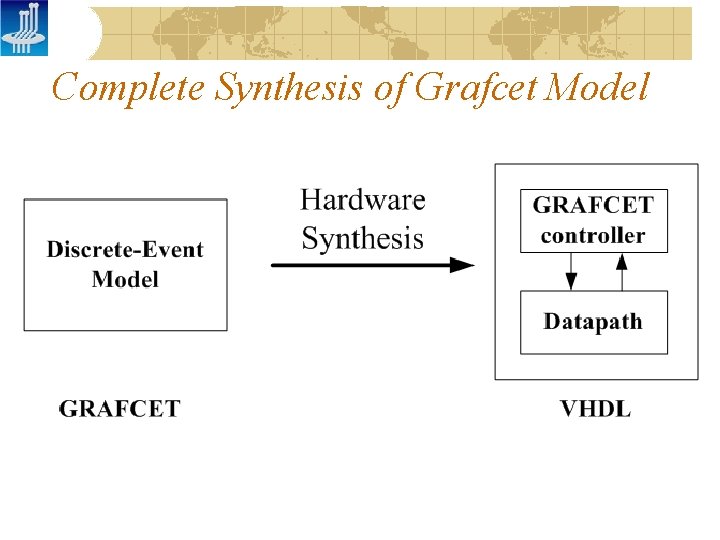

Complete Synthesis of Grafcet Model

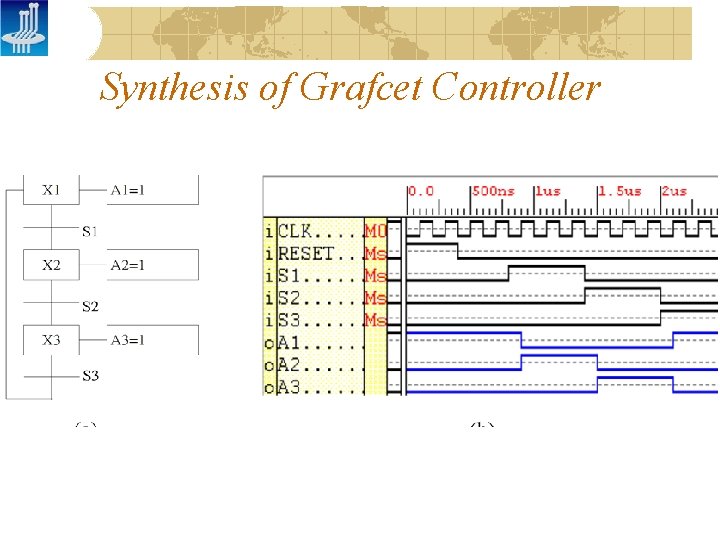

Synthesis of Grafcet Controller

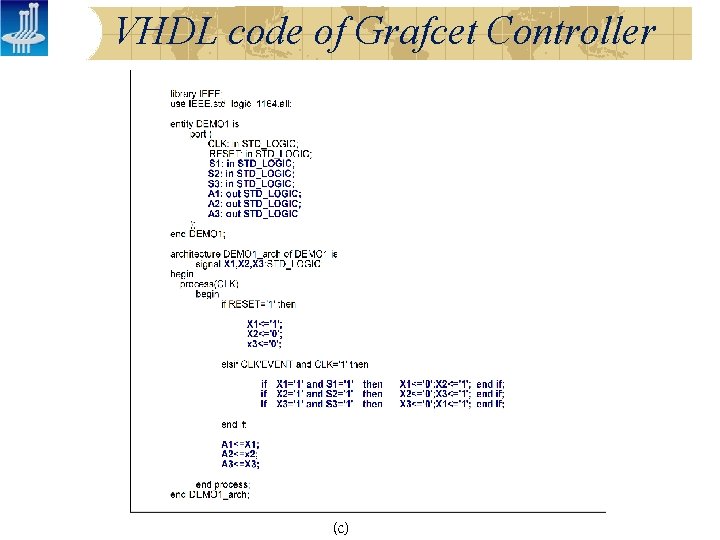

VHDL code of Grafcet Controller

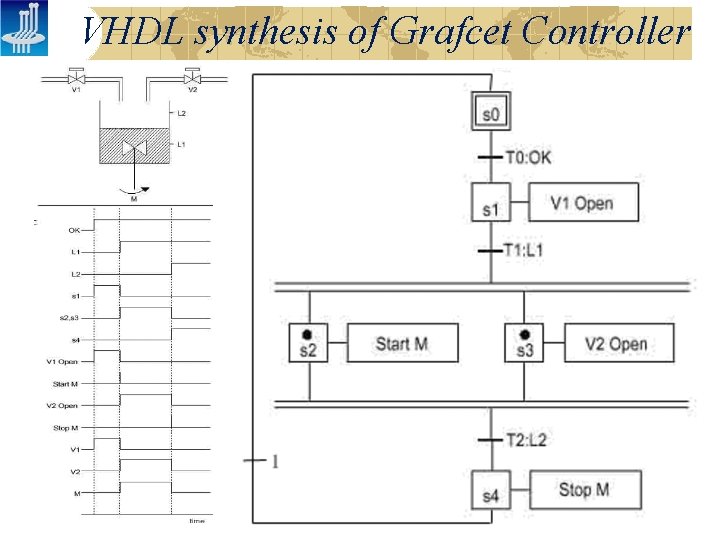

VHDL synthesis of Grafcet Controller

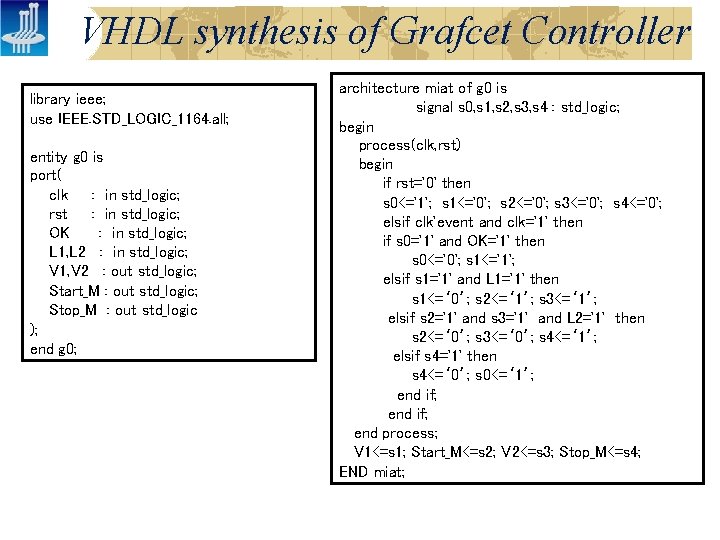

VHDL synthesis of Grafcet Controller library ieee; use IEEE. STD_LOGIC_1164. all; entity g 0 is port( clk : in std_logic; rst : in std_logic; OK : in std_logic; L 1, L 2 : in std_logic; V 1, V 2 : out std_logic; Start_M : out std_logic; Stop_M : out std_logic ); end g 0; architecture miat of g 0 is signal s 0, s 1, s 2, s 3, s 4 : std_logic; begin process(clk, rst) begin if rst='0' then s 0<='1'; s 1<='0'; s 2<='0'; s 3<='0'; s 4<='0'; elsif clk'event and clk='1' then if s 0='1' and OK='1' then s 0<='0'; s 1<='1'; elsif s 1='1' and L 1='1' then s 1<=‘ 0’; s 2<=‘ 1’; s 3<=‘ 1’; elsif s 2='1' and s 3='1' and L 2='1' then s 2<=‘ 0’; s 3<=‘ 0’; s 4<=‘ 1’; elsif s 4='1' then s 4<=‘ 0’; s 0<=‘ 1’; end if; end process; V 1<=s 1; Start_M<=s 2; V 2<=s 3; Stop_M<=s 4; END miat;

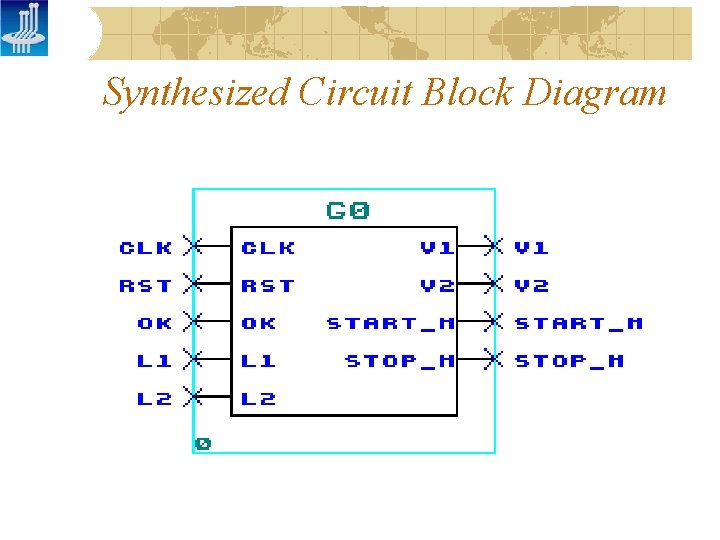

Synthesized Circuit Block Diagram

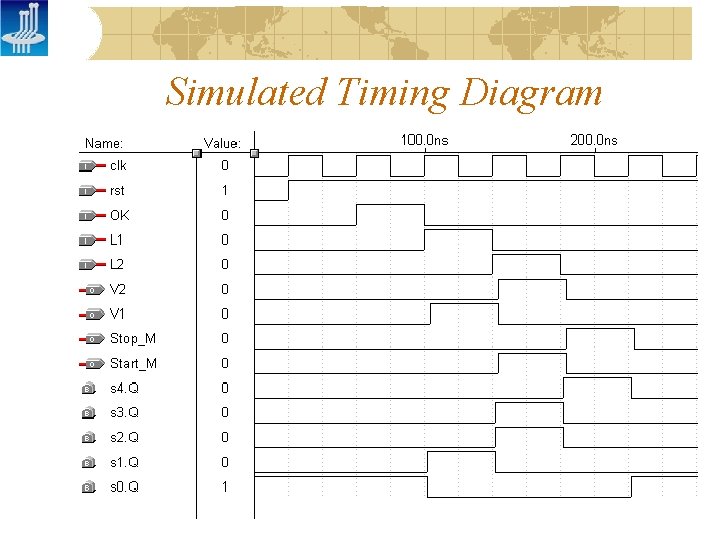

Simulated Timing Diagram

- Slides: 39