Finite State Machines Discussion D 7 1 Mealy

- Slides: 21

Finite State Machines Discussion D 7. 1 Mealy and Moore Machines

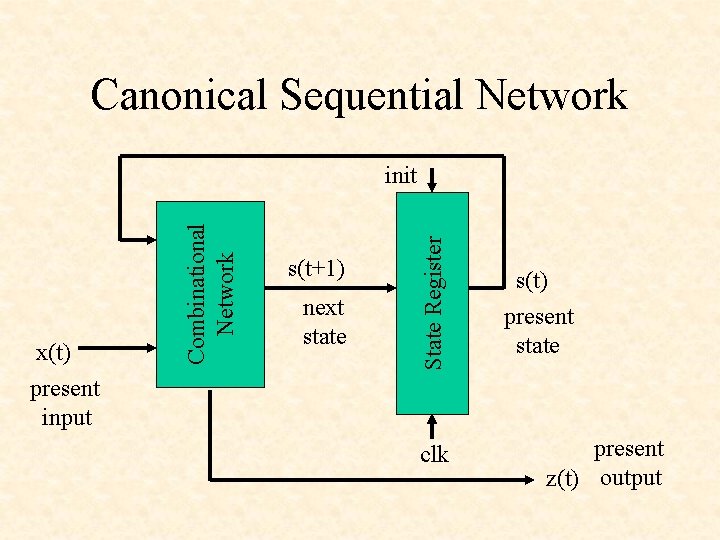

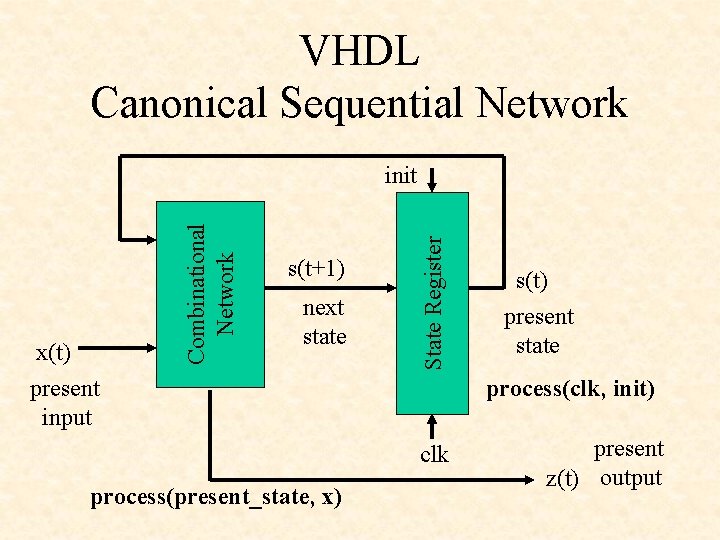

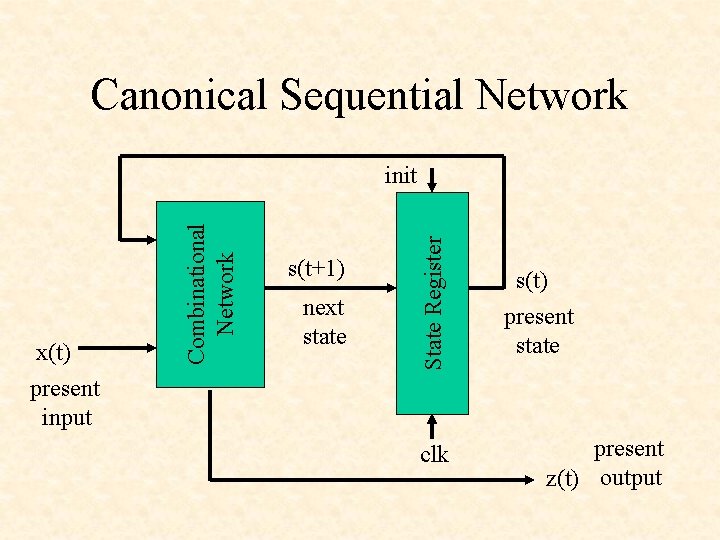

Canonical Sequential Network s(t+1) next state State Register x(t) Combinational Network init s(t) present state present input clk present z(t) output

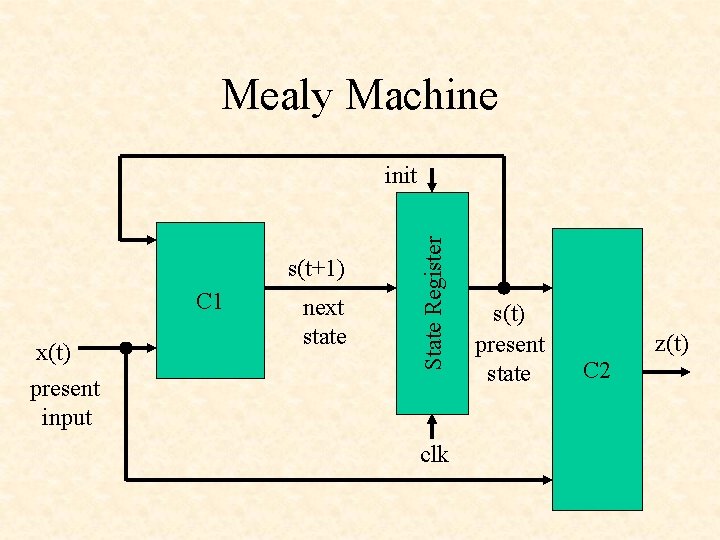

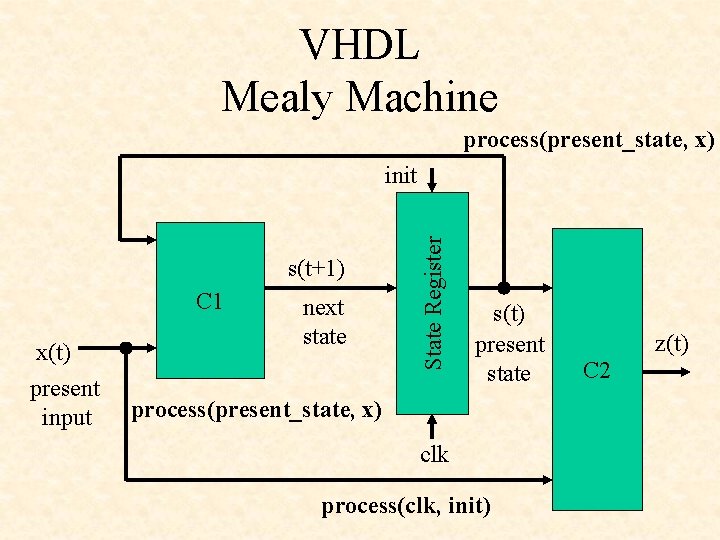

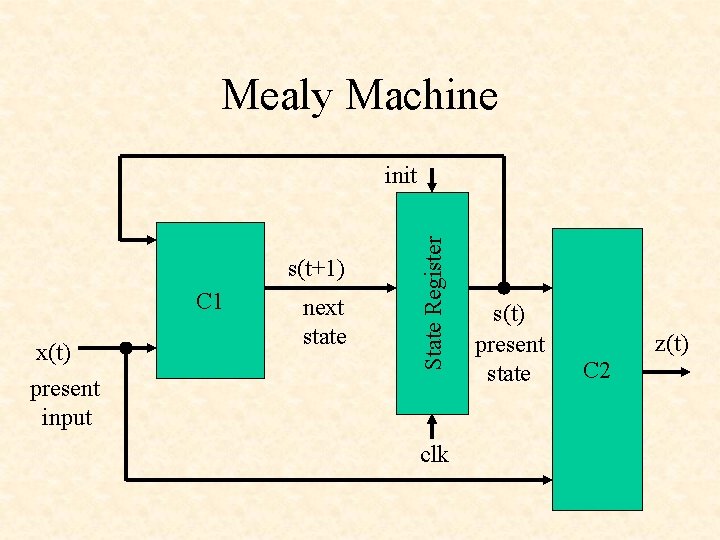

Mealy Machine s(t+1) C 1 x(t) next state State Register init present input clk s(t) present state z(t) C 2

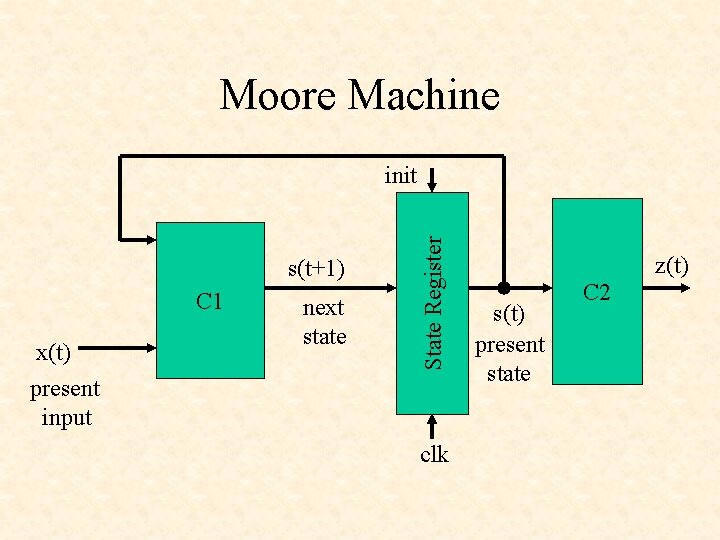

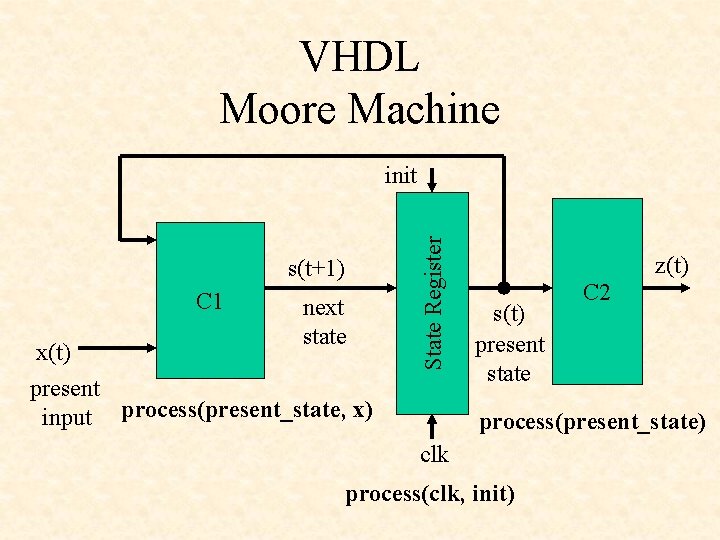

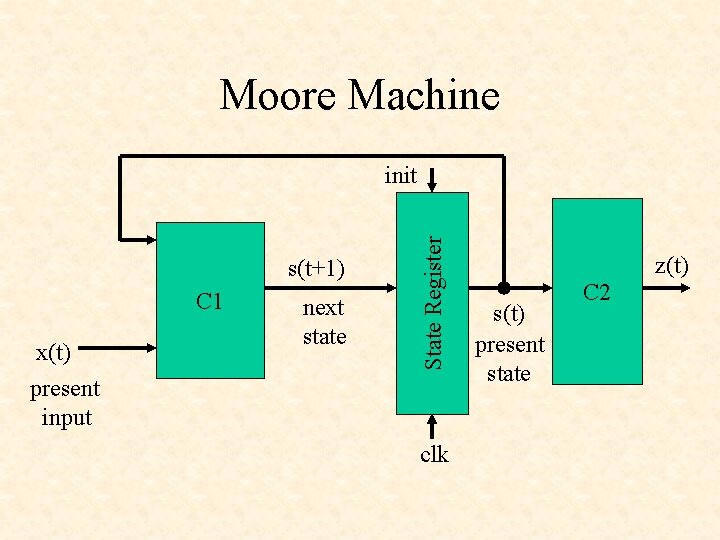

Moore Machine s(t+1) C 1 x(t) next state State Register init present input clk z(t) s(t) present state C 2

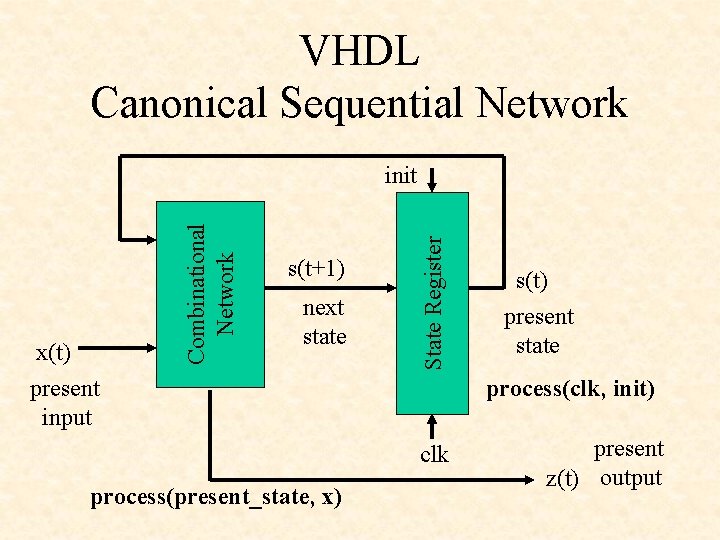

VHDL Canonical Sequential Network s(t+1) next state State Register x(t) present input Combinational Network init process(clk, init) clk process(present_state, x) s(t) present state present z(t) output

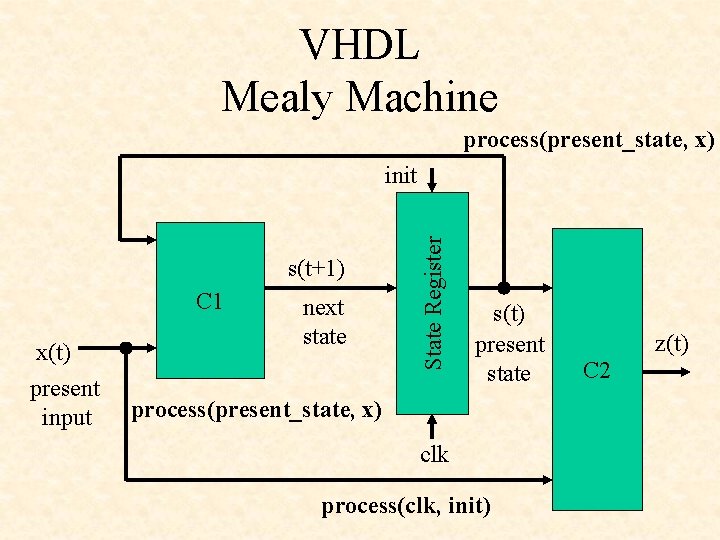

VHDL Mealy Machine process(present_state, x) s(t+1) C 1 x(t) present input next state State Register init s(t) present state process(present_state, x) clk process(clk, init) z(t) C 2

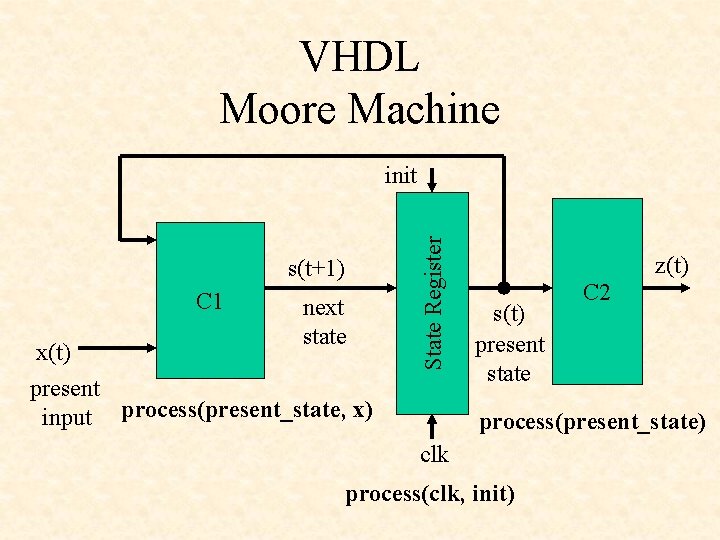

VHDL Moore Machine s(t+1) C 1 next state x(t) present input process(present_state, x) State Register init z(t) s(t) present state C 2 process(present_state) clk process(clk, init)

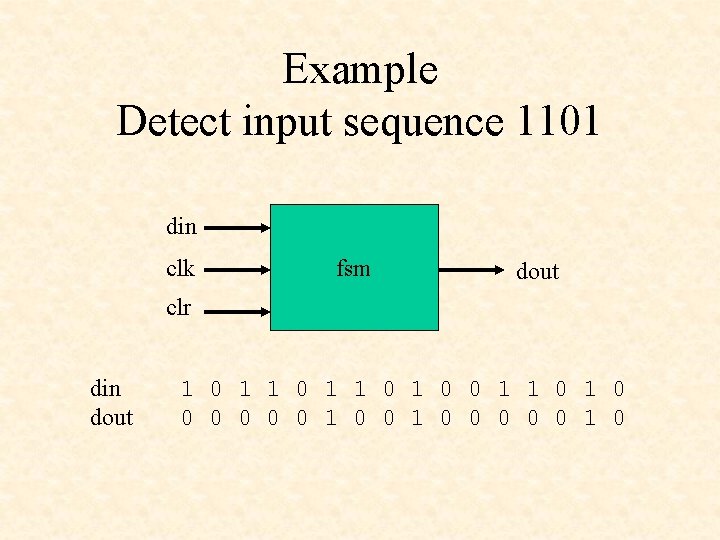

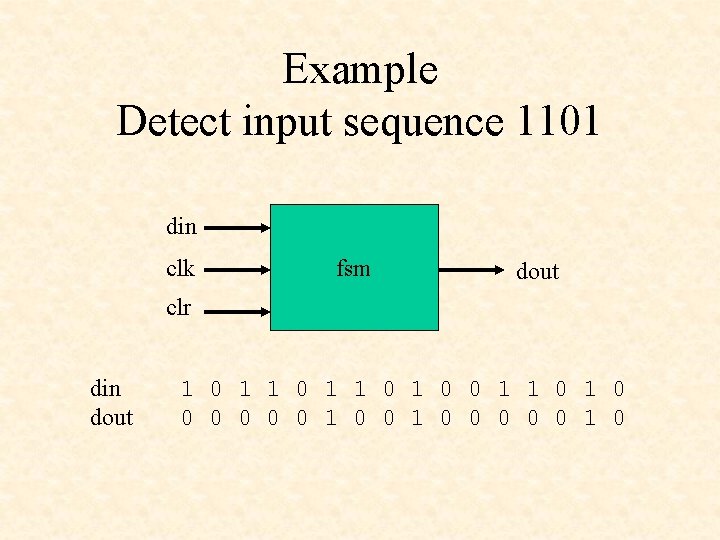

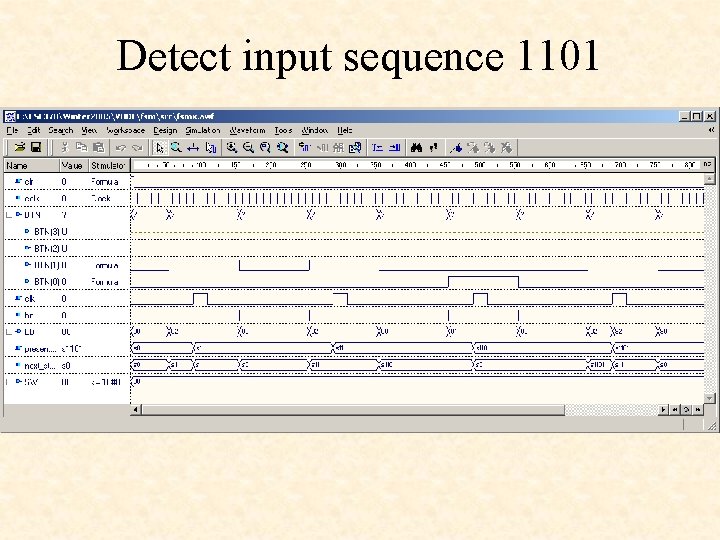

Example Detect input sequence 1101 din clk fsm dout clr din dout 1 0 1 1 0 0 0 0 1 0

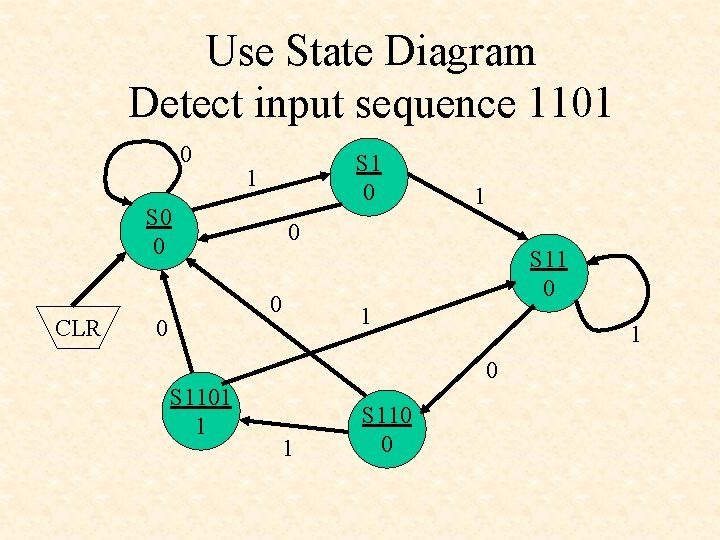

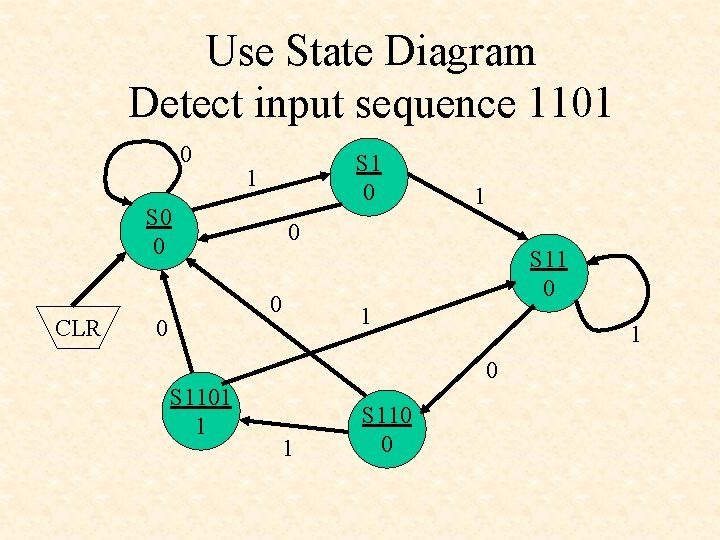

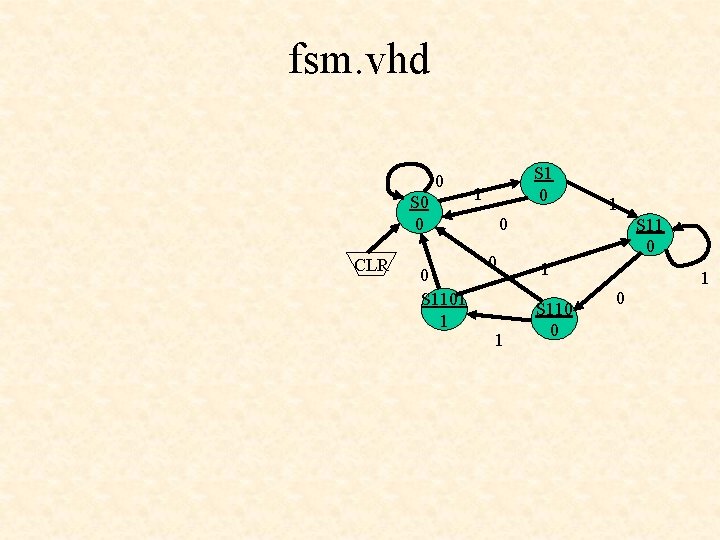

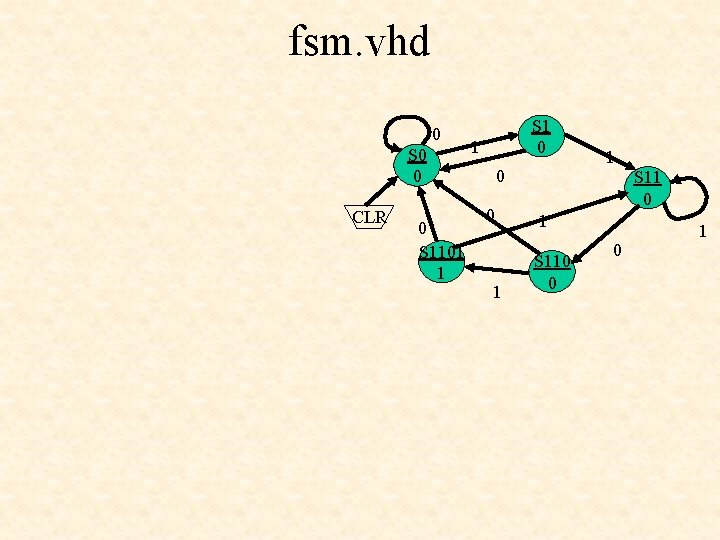

Use State Diagram Detect input sequence 1101 0 S 1 0 1 S 0 0 CLR 0 S 11 0 0 0 1 1 1 0 S 1101 1 1 S 110 0

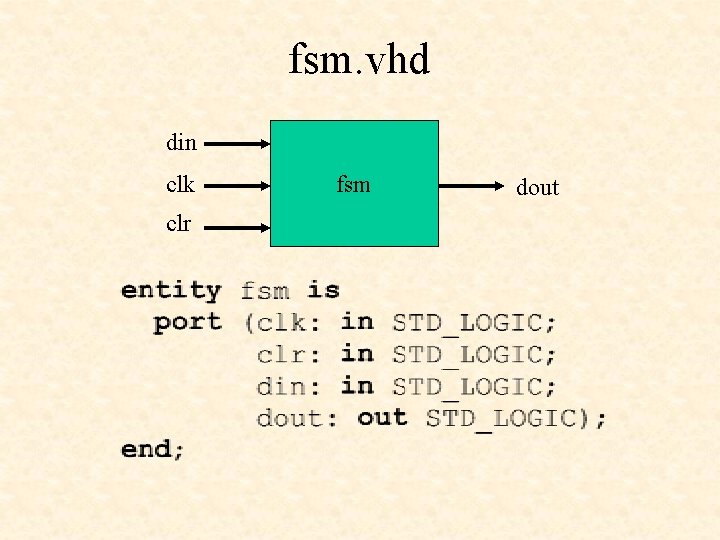

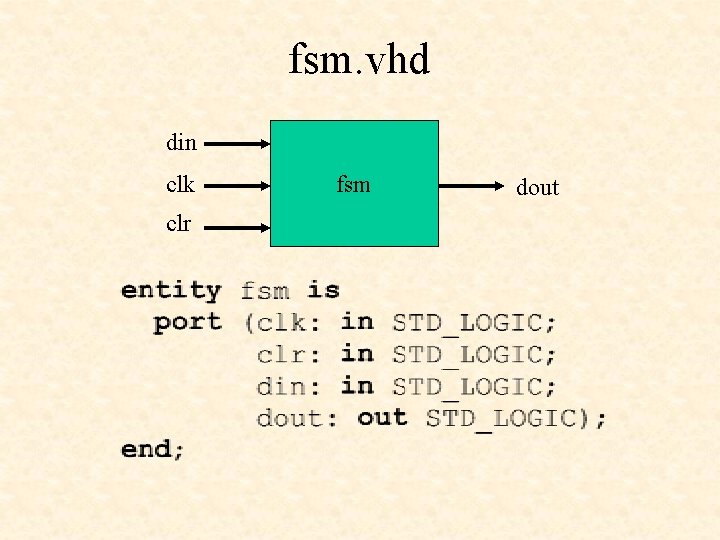

fsm. vhd din clk clr fsm dout

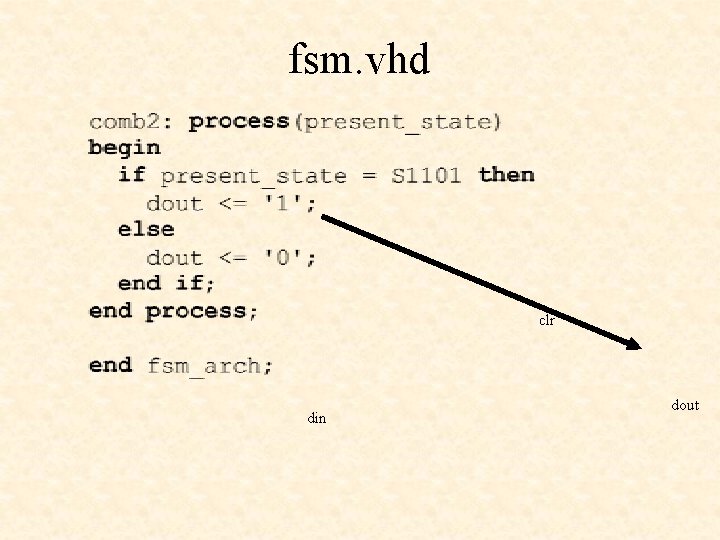

fsm. vhd clr din dout

fsm. vhd clr din dout

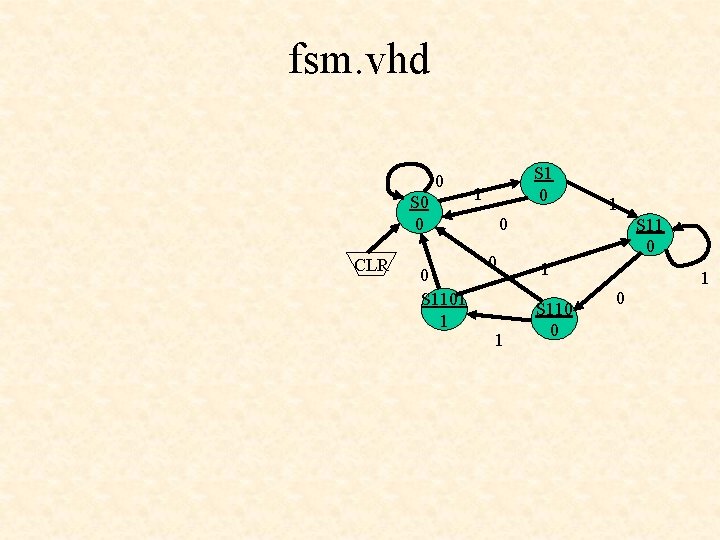

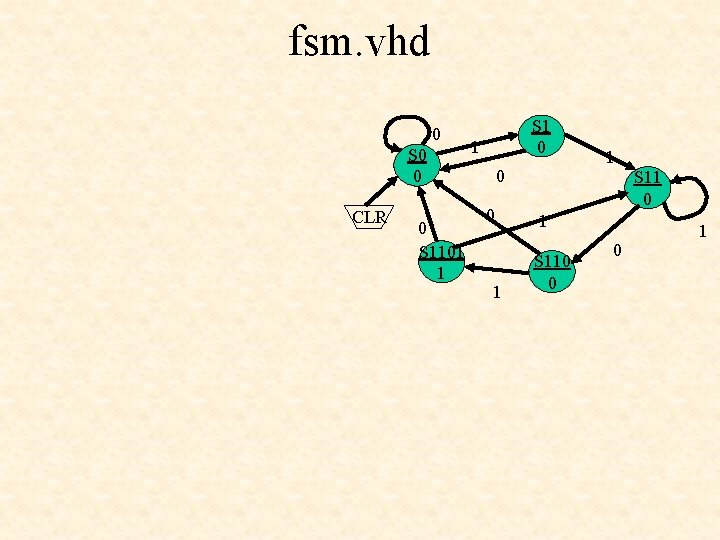

fsm. vhd 0 S 0 0 CLR 0 S 1101 1 S 1 0 0 1 1 S 11 0 1 S 110 0 0 1

fsm. vhd 0 S 0 0 CLR 0 S 1101 1 S 1 0 0 1 1 S 11 0 1 S 110 0 0 1

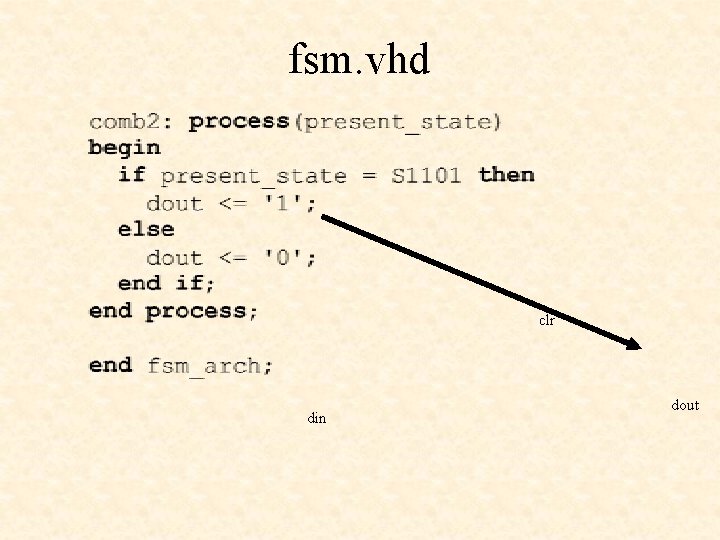

fsm. vhd clr din dout

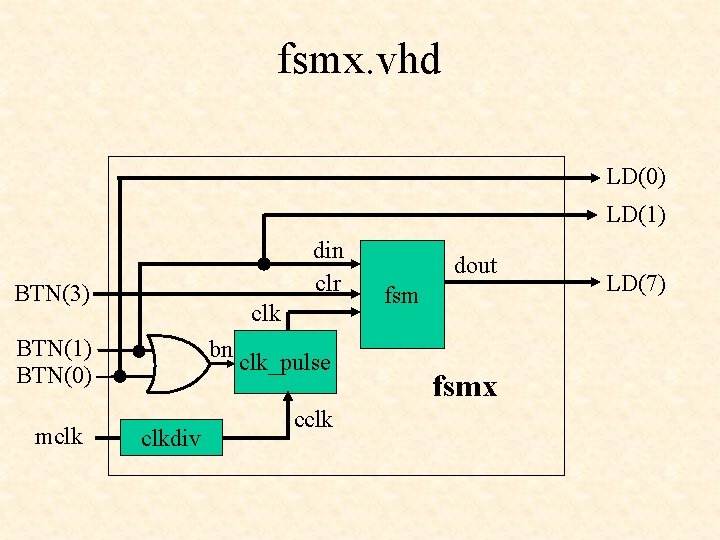

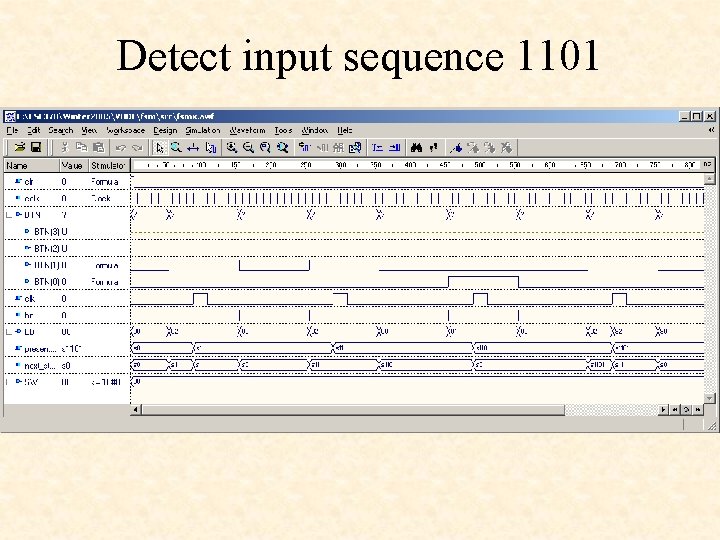

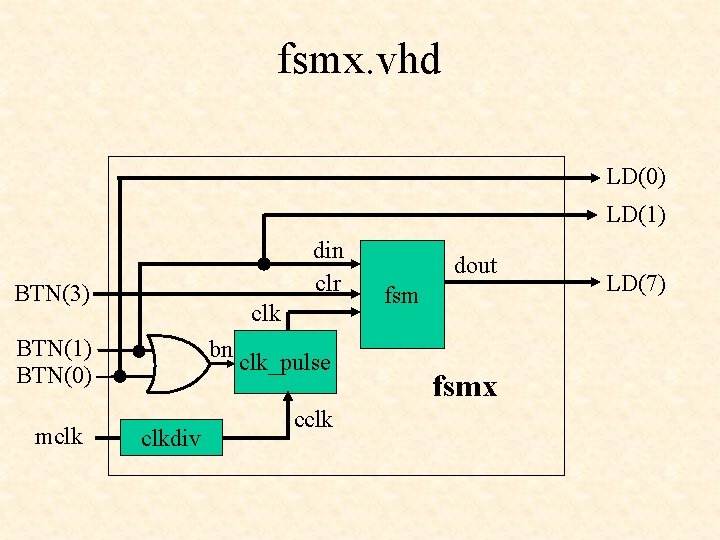

fsmx. vhd LD(0) LD(1) din clr BTN(3) clk BTN(1) BTN(0) mclk bn clkdiv clk_pulse cclk dout fsmx LD(7)

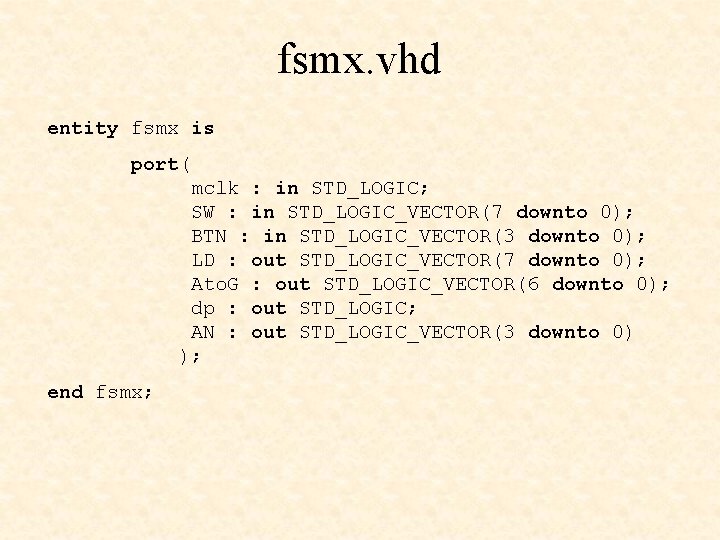

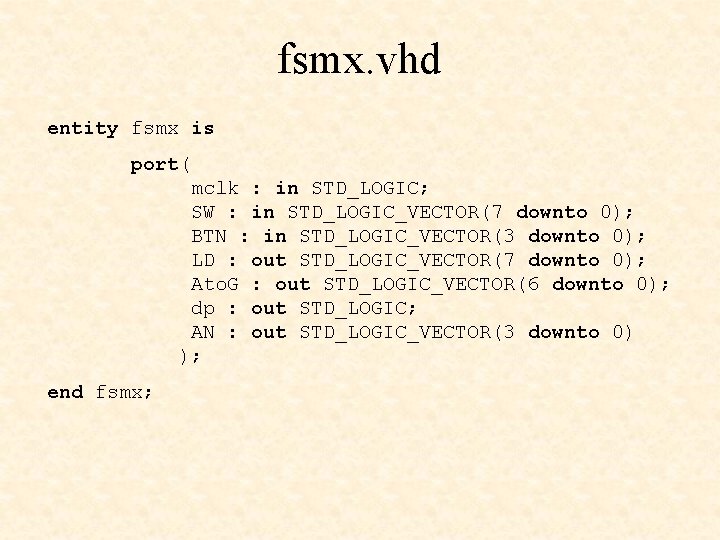

fsmx. vhd entity fsmx is port( mclk : in STD_LOGIC; SW : in STD_LOGIC_VECTOR(7 downto 0); BTN : in STD_LOGIC_VECTOR(3 downto 0); LD : out STD_LOGIC_VECTOR(7 downto 0); Ato. G : out STD_LOGIC_VECTOR(6 downto 0); dp : out STD_LOGIC; AN : out STD_LOGIC_VECTOR(3 downto 0) ); end fsmx;

fsmx. vhd

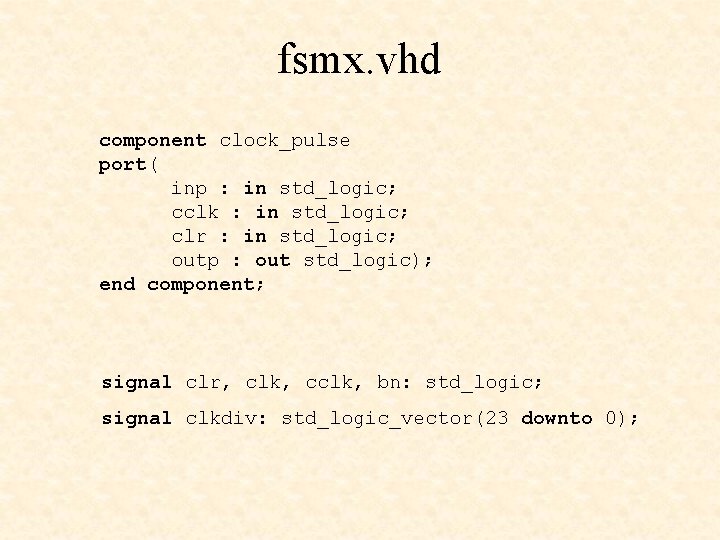

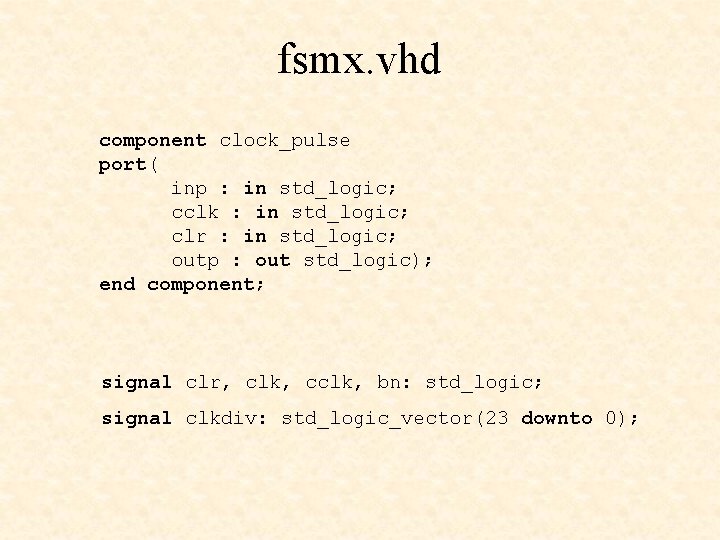

fsmx. vhd component clock_pulse port( inp : in std_logic; cclk : in std_logic; clr : in std_logic; outp : out std_logic); end component; signal clr, clk, cclk, bn: std_logic; signal clkdiv: std_logic_vector(23 downto 0);

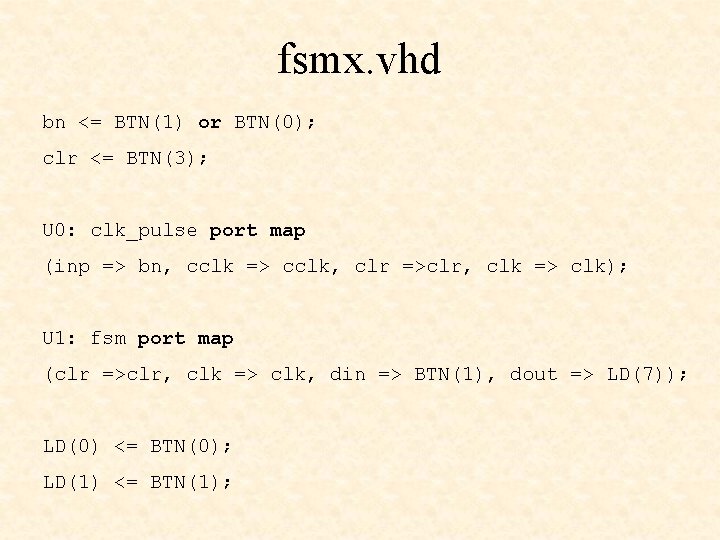

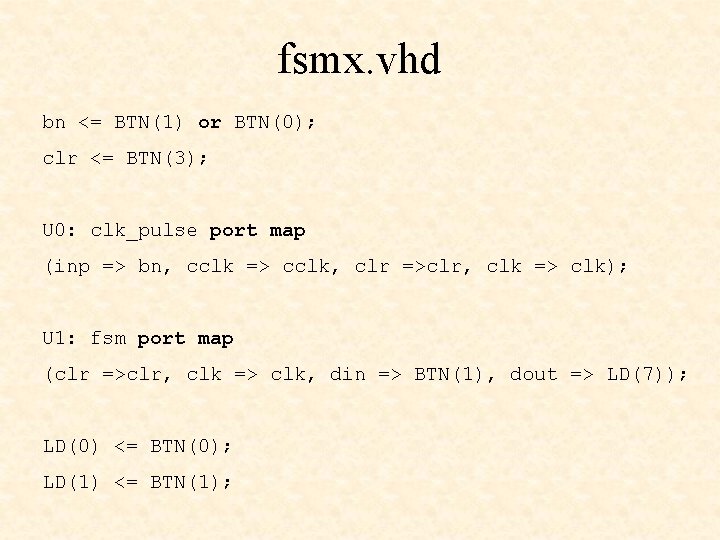

fsmx. vhd bn <= BTN(1) or BTN(0); clr <= BTN(3); U 0: clk_pulse port map (inp => bn, cclk => cclk, clr =>clr, clk => clk); U 1: fsm port map (clr =>clr, clk => clk, din => BTN(1), dout => LD(7)); LD(0) <= BTN(0); LD(1) <= BTN(1);

Detect input sequence 1101