Figure 7 1 Two versions of SETRESET SR

- Slides: 107

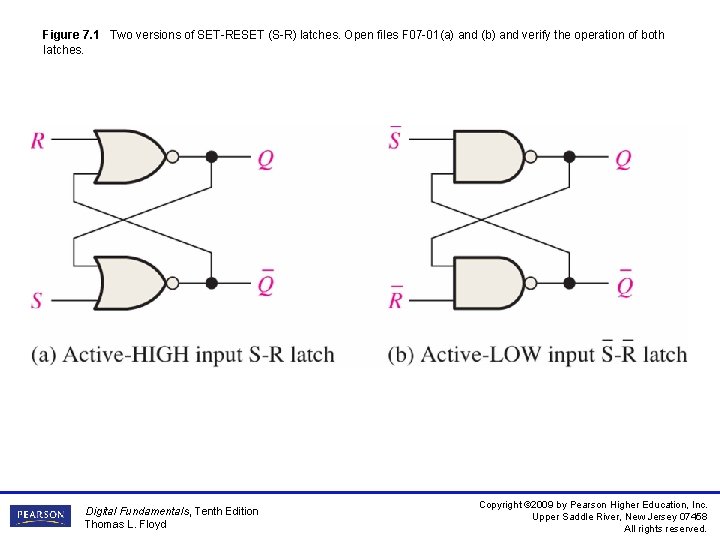

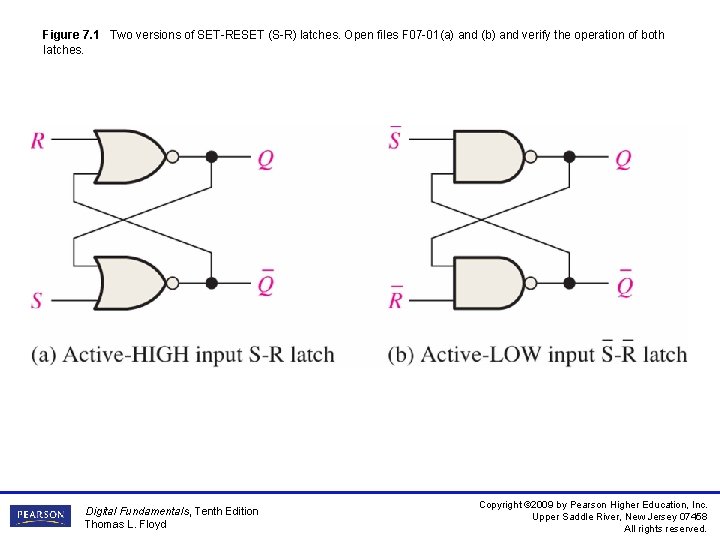

Figure 7. 1 Two versions of SET-RESET (S-R) latches. Open files F 07 -01(a) and (b) and verify the operation of both latches. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

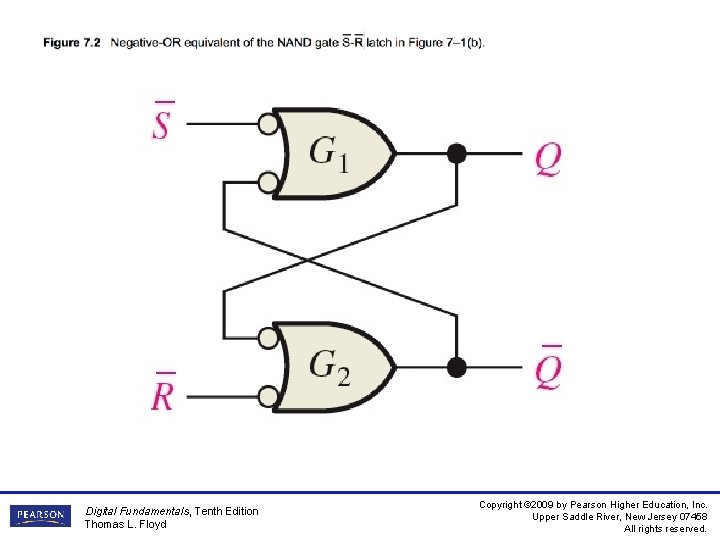

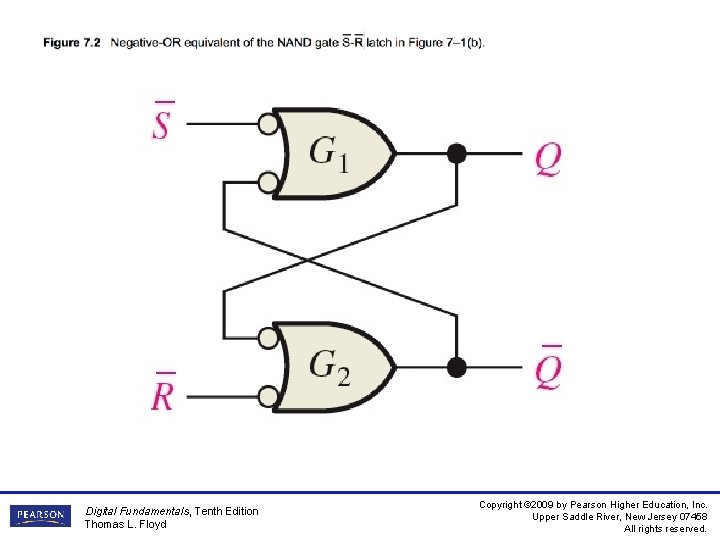

__ Figure 7. 2 Negative-OR equivalent of the NAND gate S-R latch in Figure 7– 1(b). Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

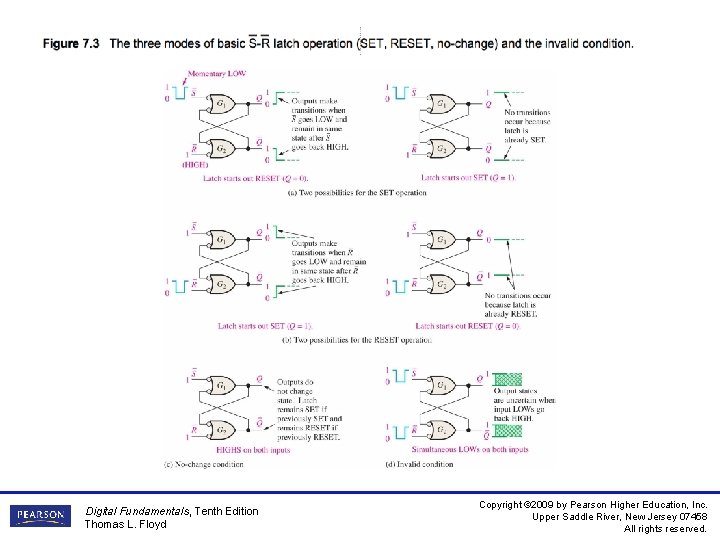

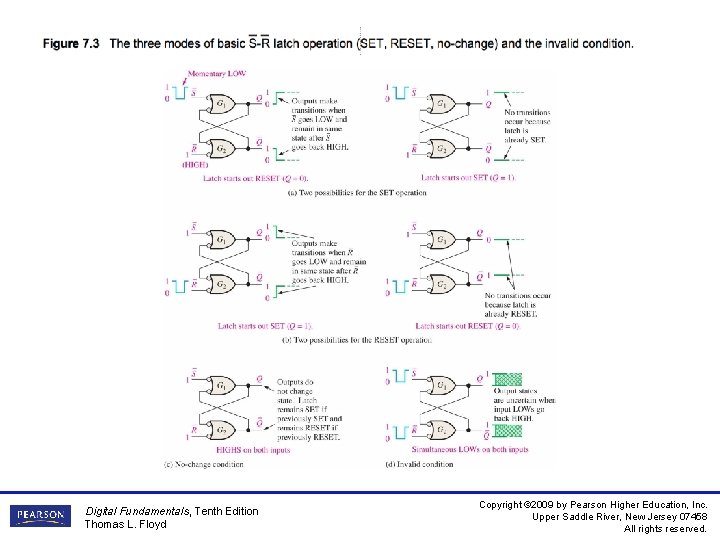

__ Figure 7. 3 The three modes of basic S-R latch operation (SET, RESET, no-change) and the invalid condition. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

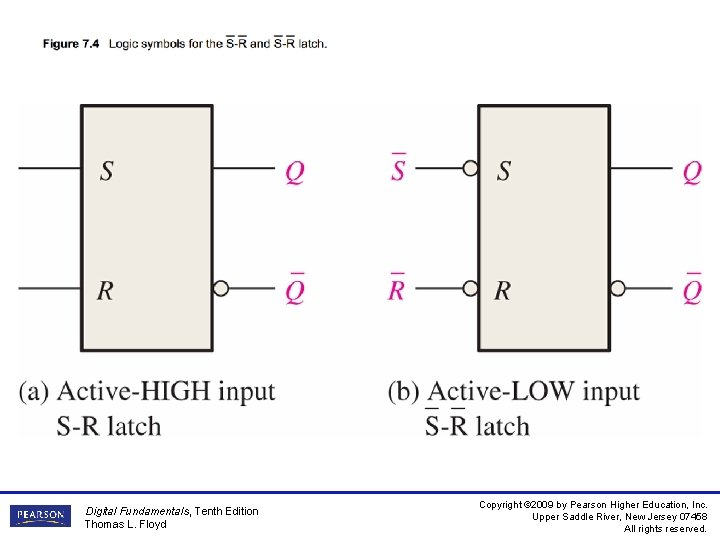

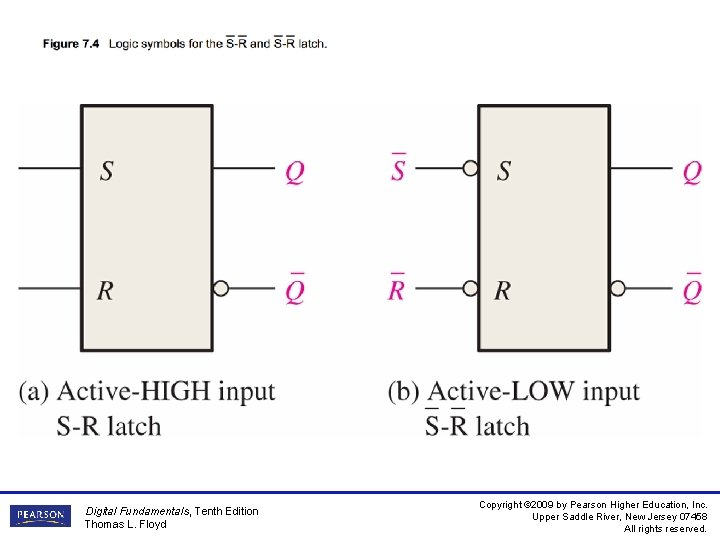

__ __ Figure 7. 4 Logic symbols for the S-R and S-R latch. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

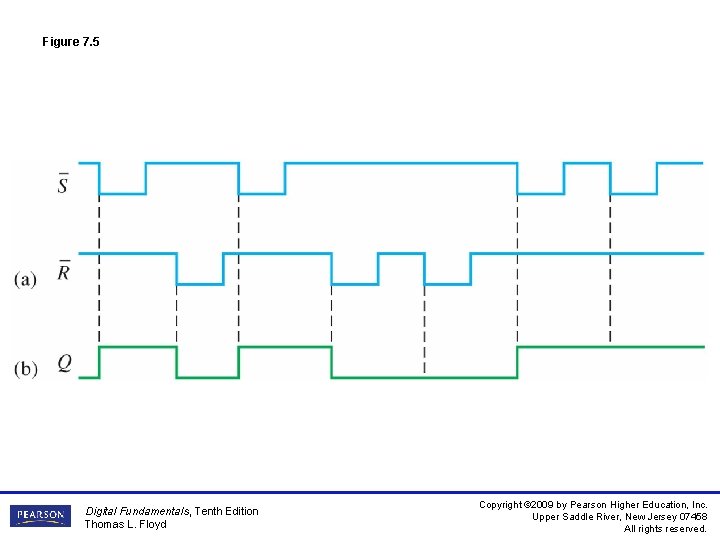

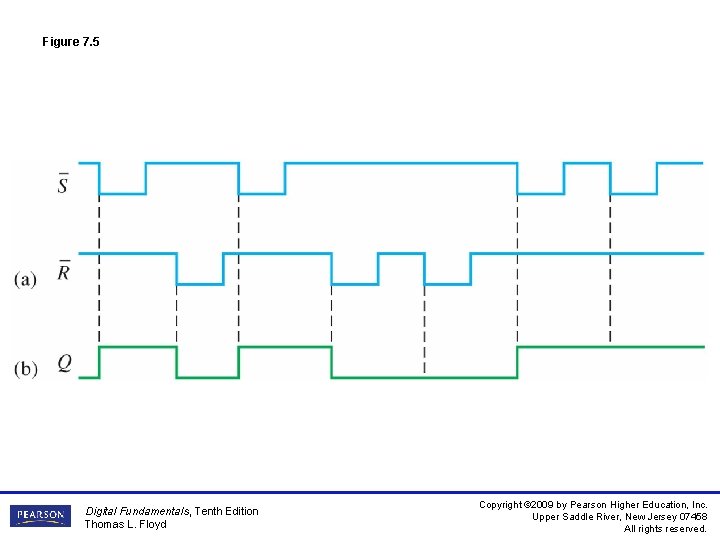

Figure 7. 5 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

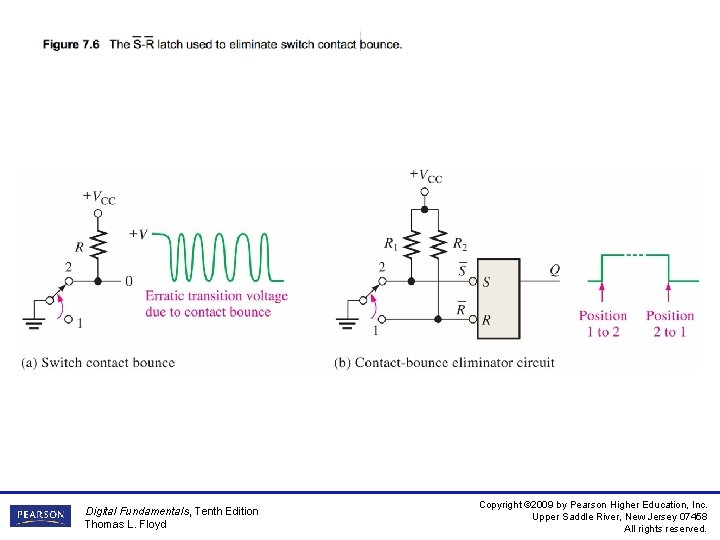

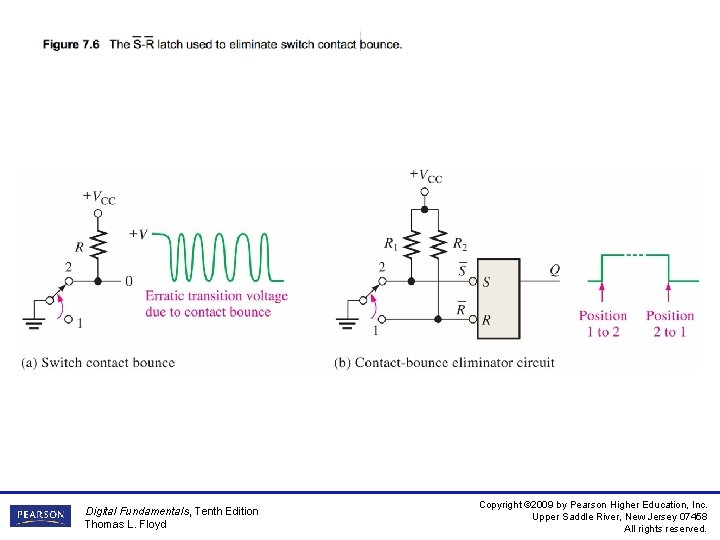

__ Figure 7. 6 The S-R latch used to eliminate switch contact bounce. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

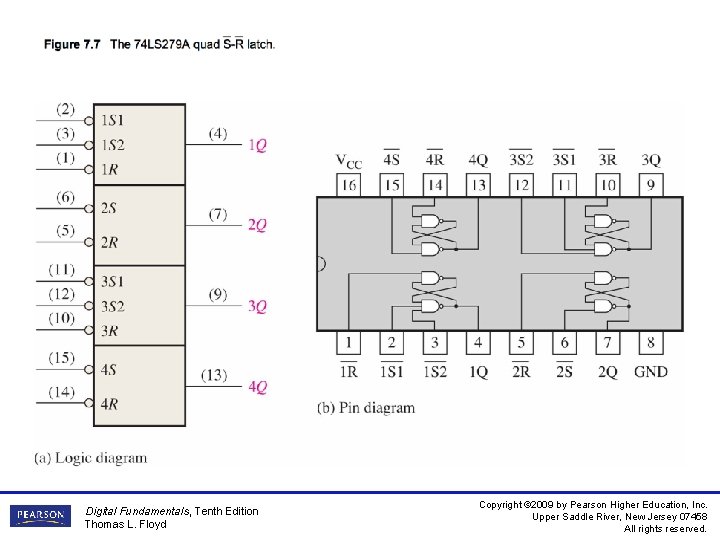

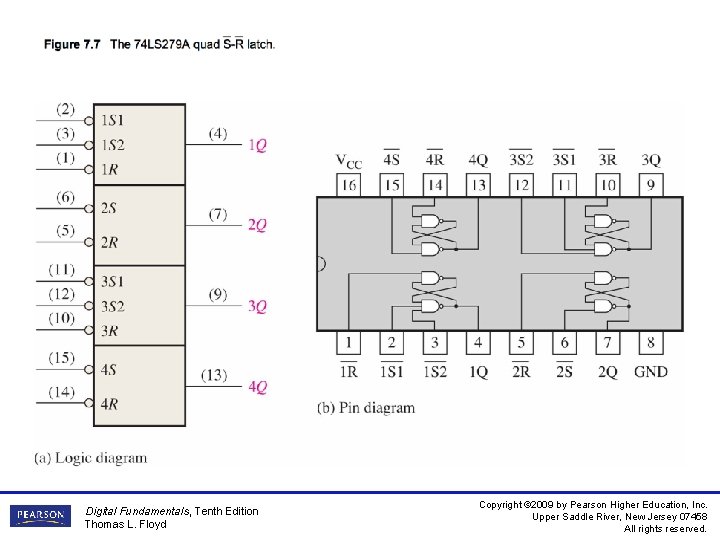

__ Figure 7. 7 The 74 LS 279 A quad S-R latch. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

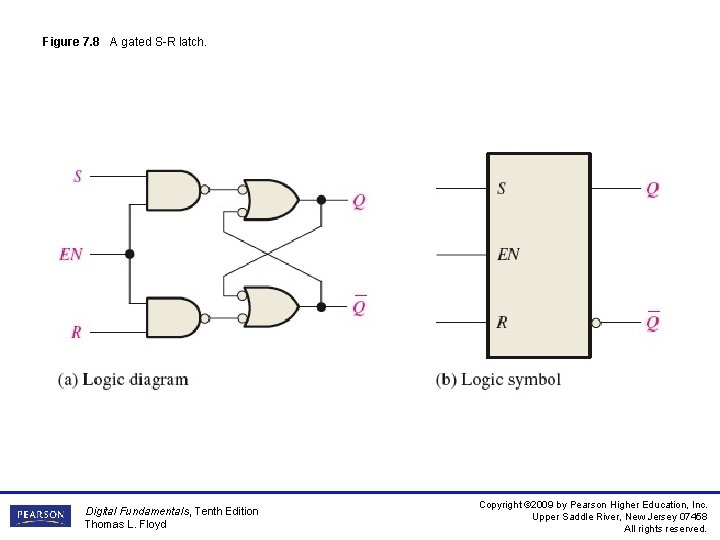

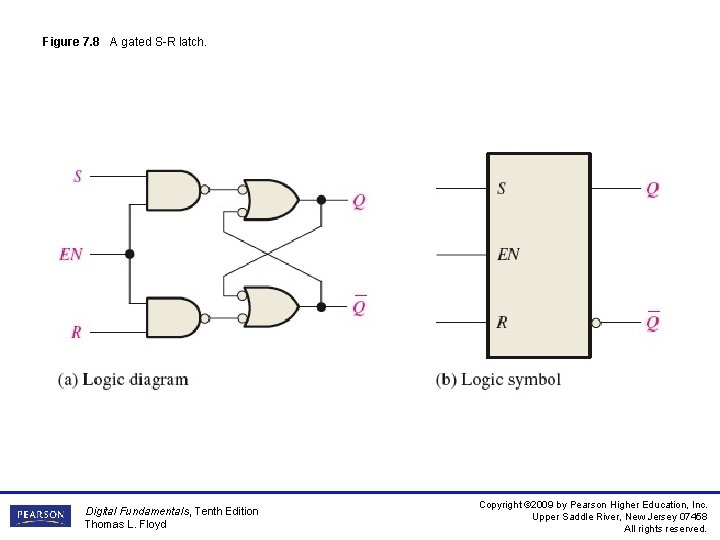

Figure 7. 8 A gated S-R latch. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

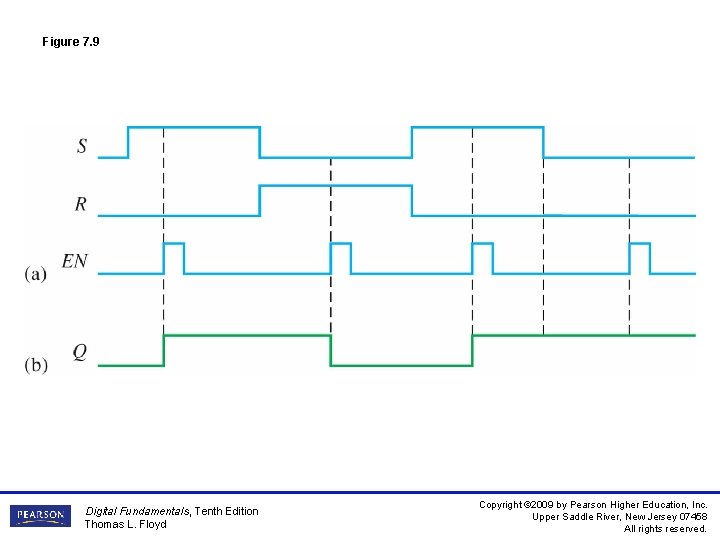

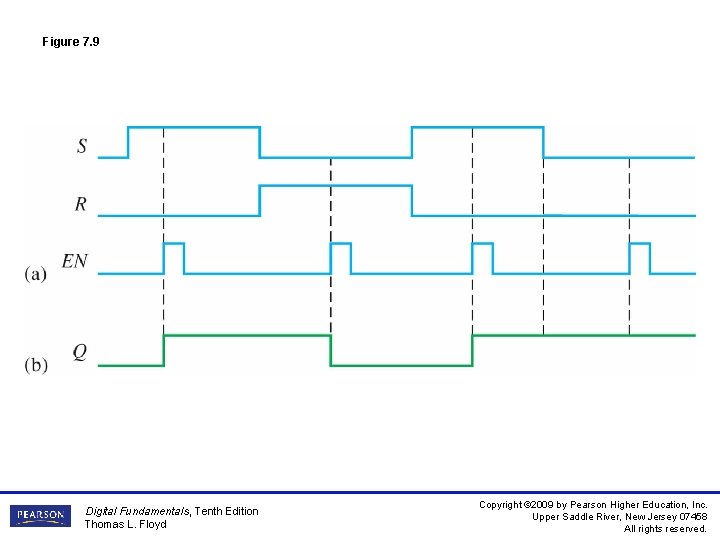

Figure 7. 9 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

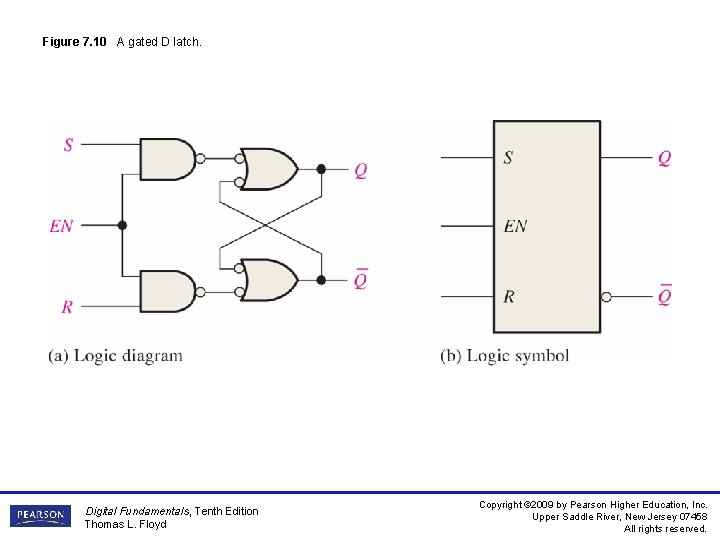

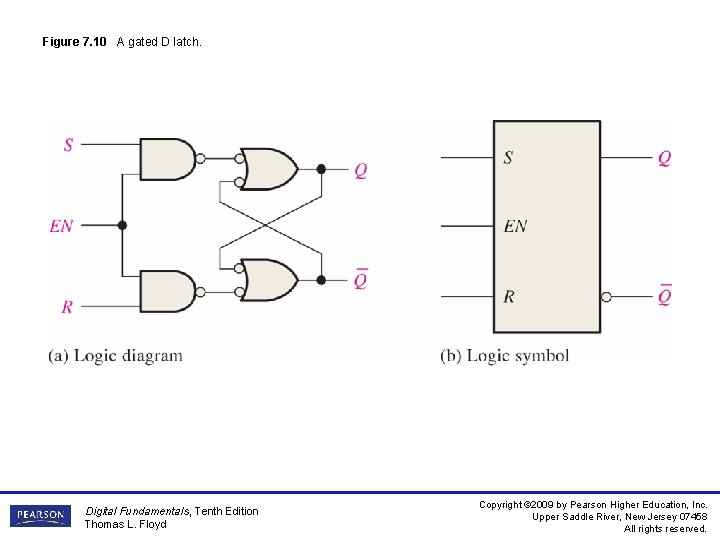

Figure 7. 10 A gated D latch. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

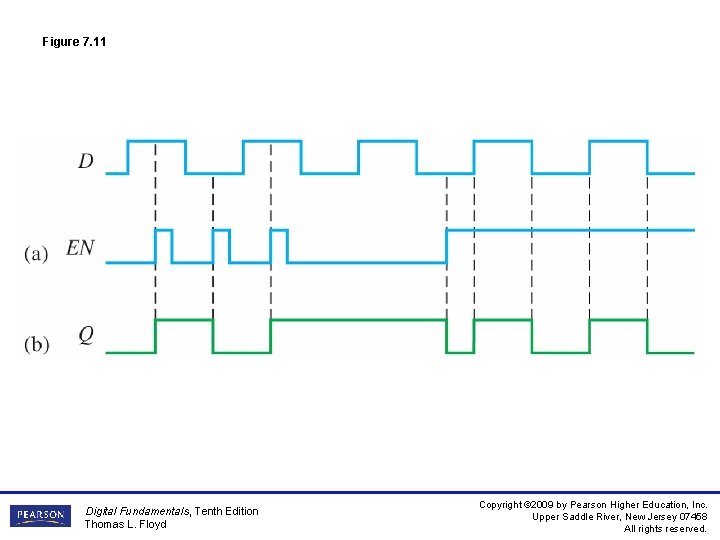

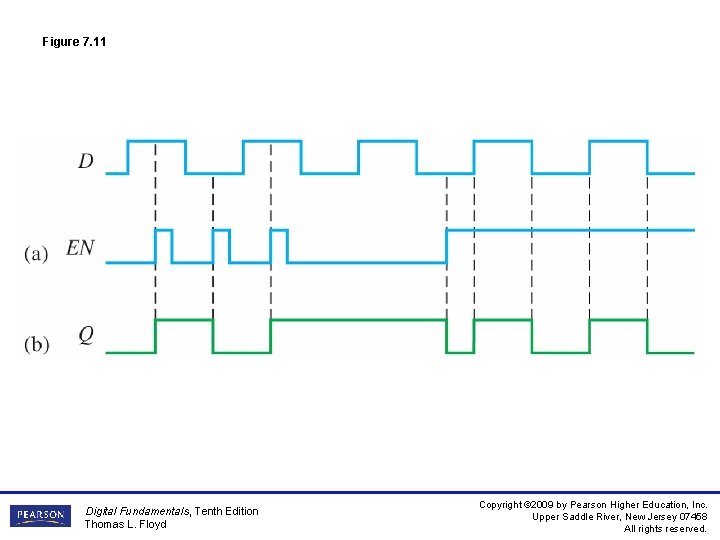

Figure 7. 11 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

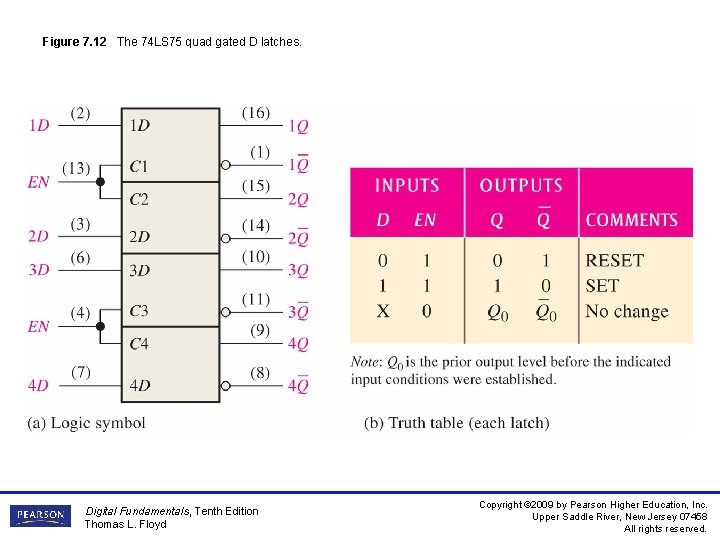

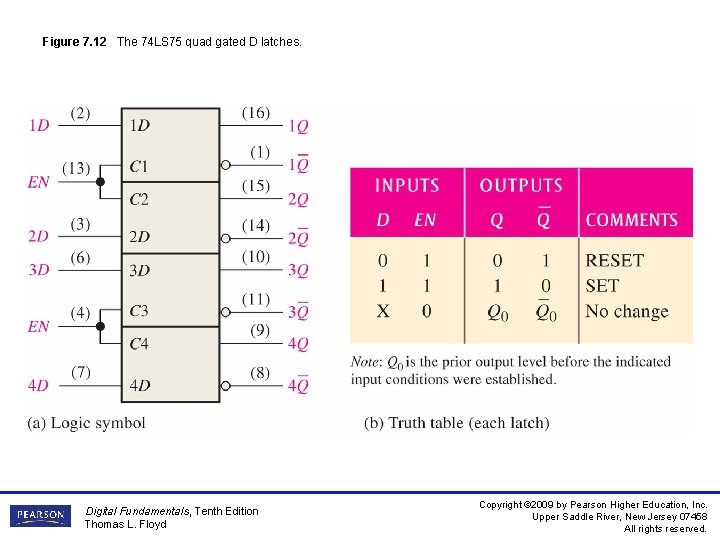

Figure 7. 12 The 74 LS 75 quad gated D latches. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

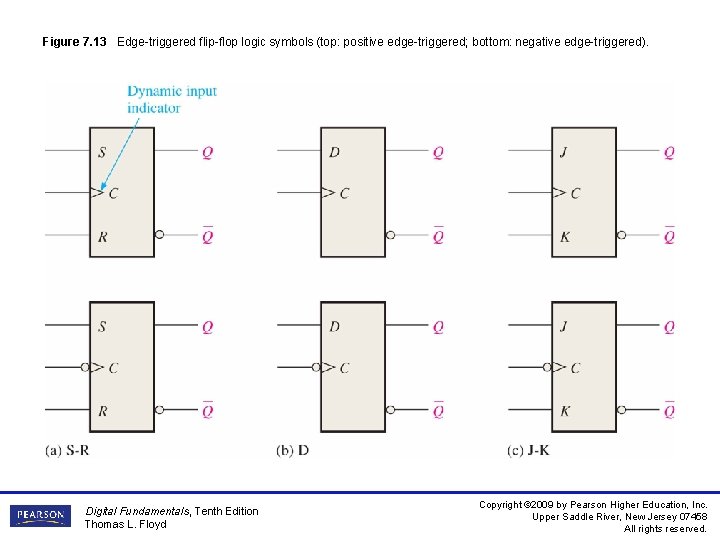

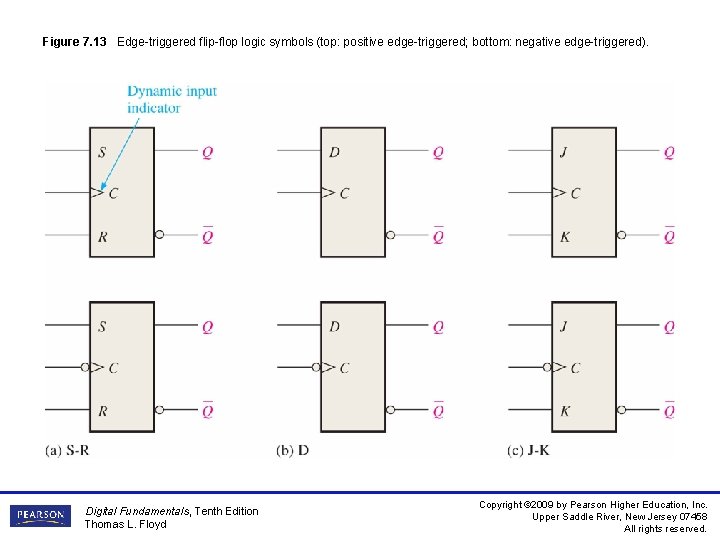

Figure 7. 13 Edge-triggered flip-flop logic symbols (top: positive edge-triggered; bottom: negative edge-triggered). Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

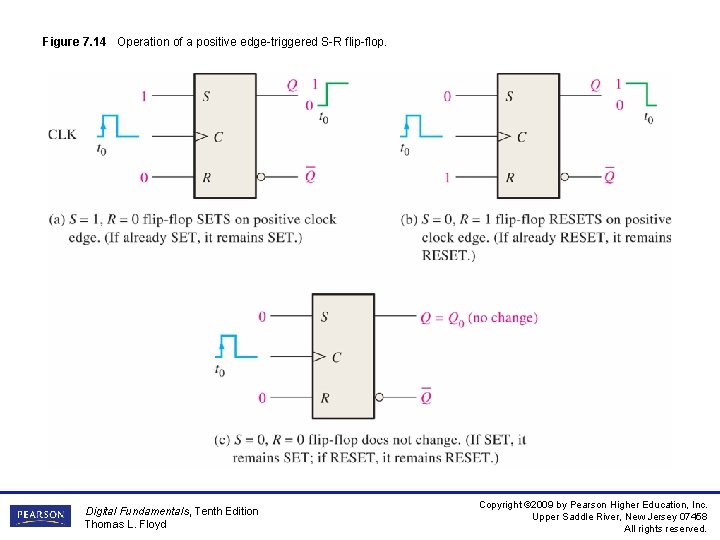

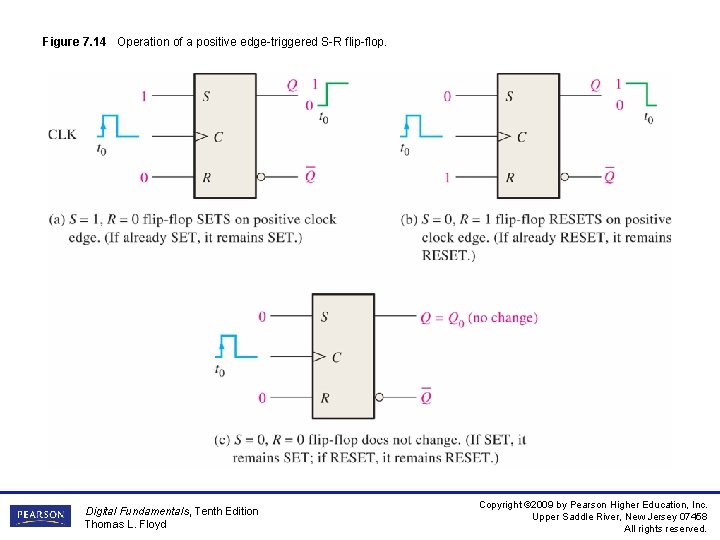

Figure 7. 14 Operation of a positive edge-triggered S-R flip-flop. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

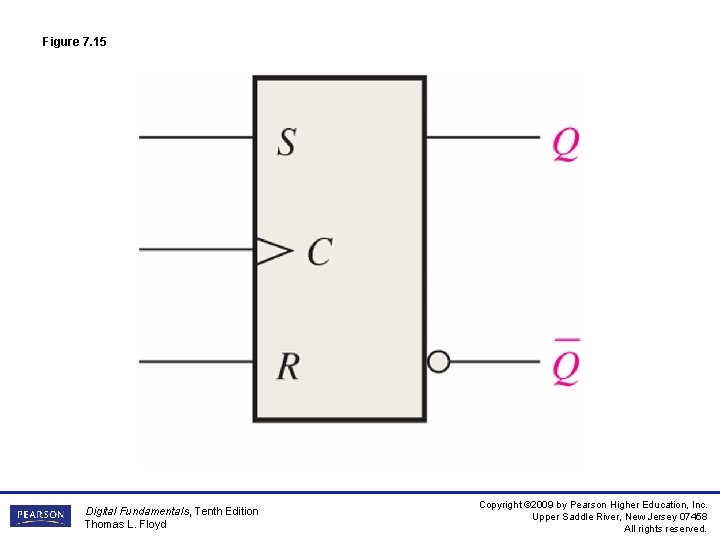

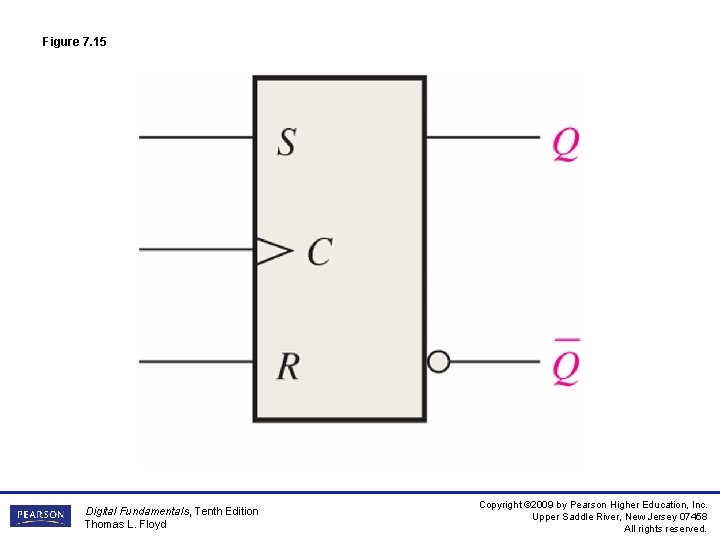

Figure 7. 15 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

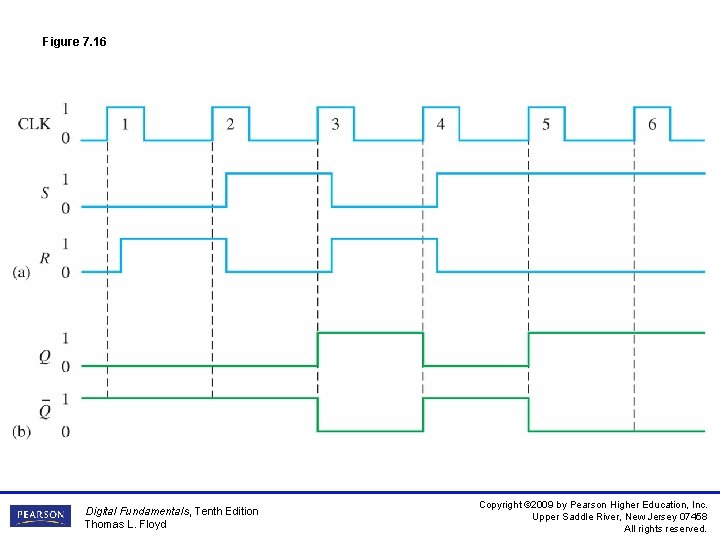

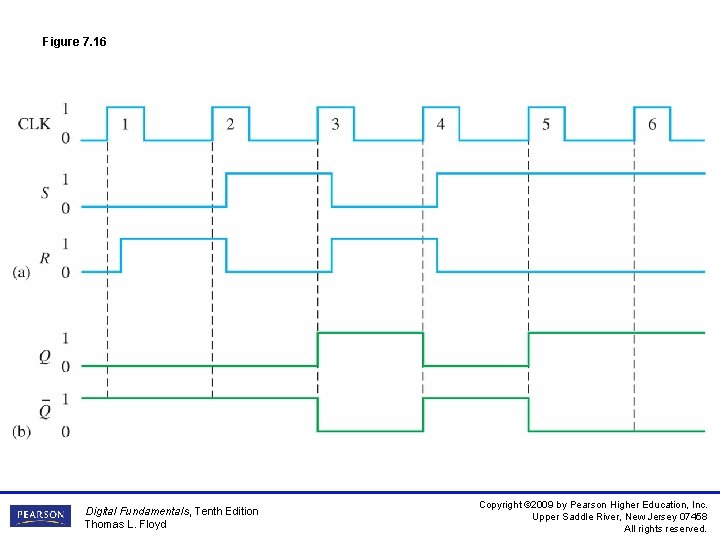

Figure 7. 16 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

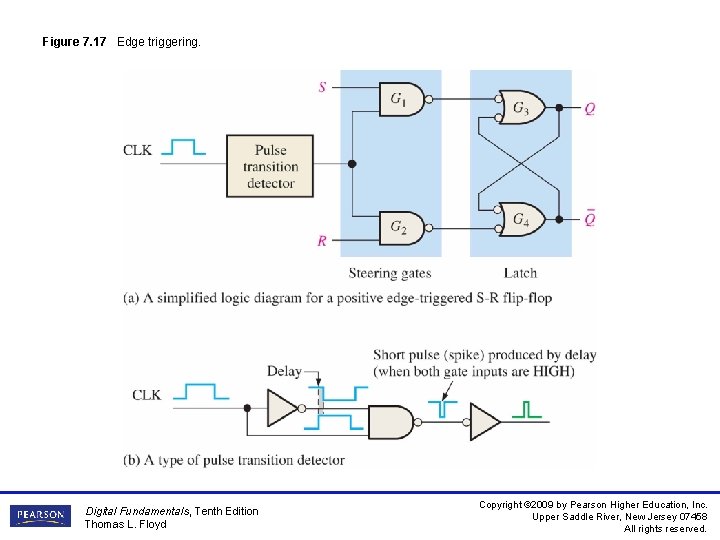

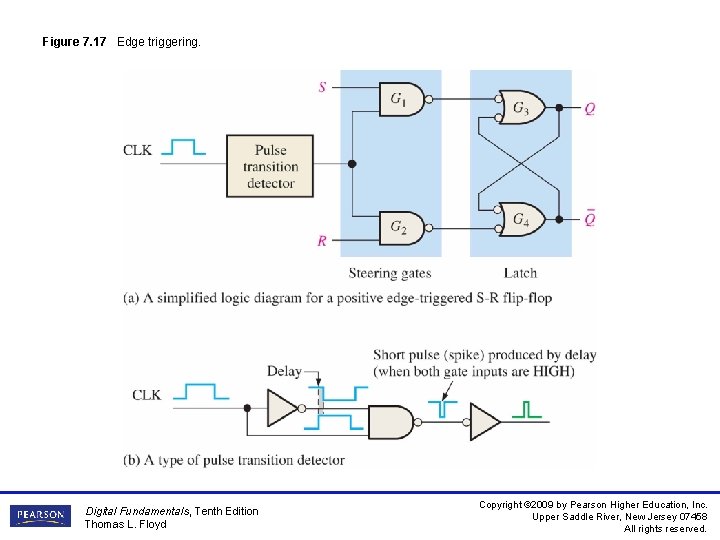

Figure 7. 17 Edge triggering. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

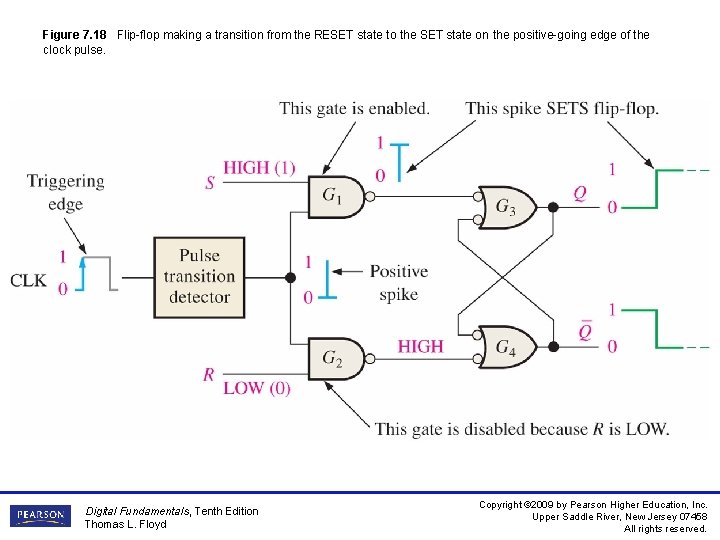

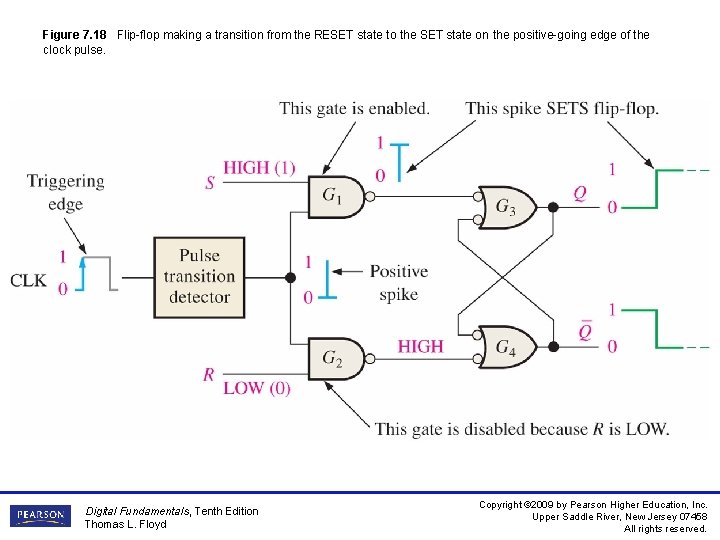

Figure 7. 18 Flip-flop making a transition from the RESET state to the SET state on the positive-going edge of the clock pulse. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

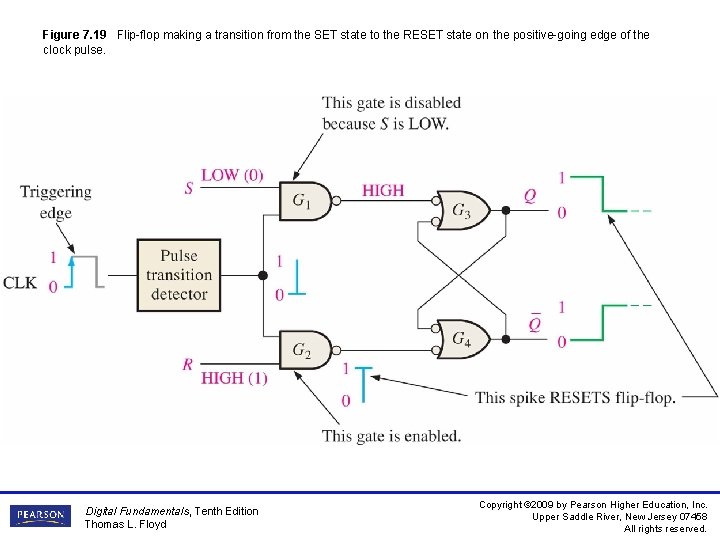

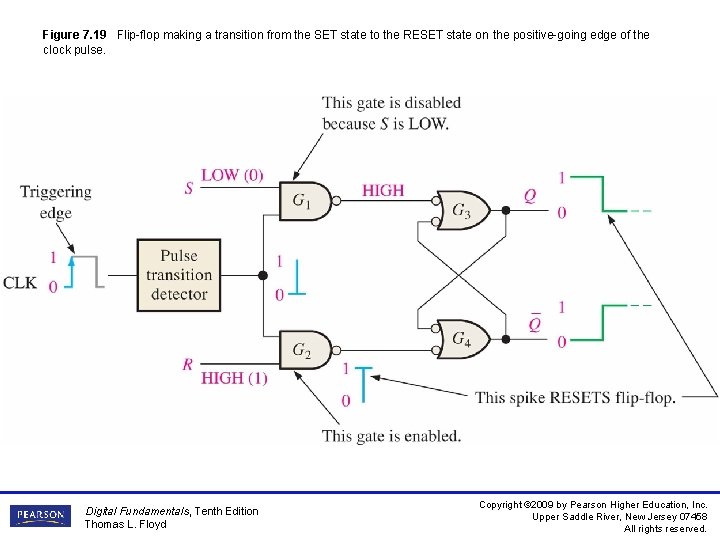

Figure 7. 19 Flip-flop making a transition from the SET state to the RESET state on the positive-going edge of the clock pulse. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

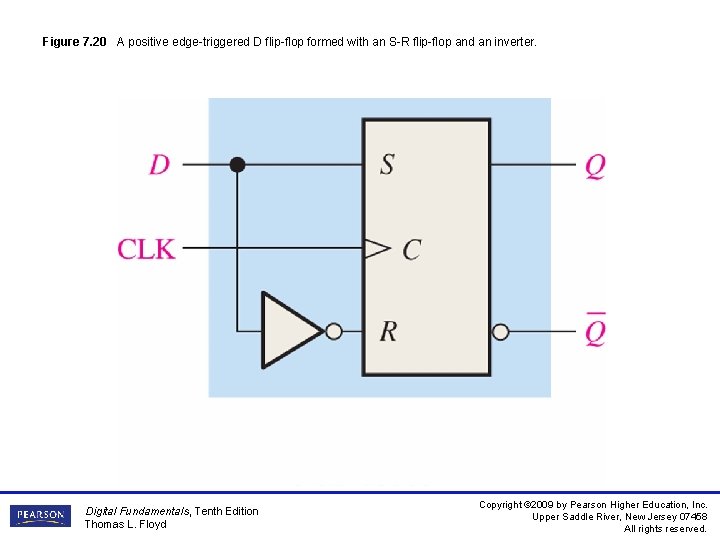

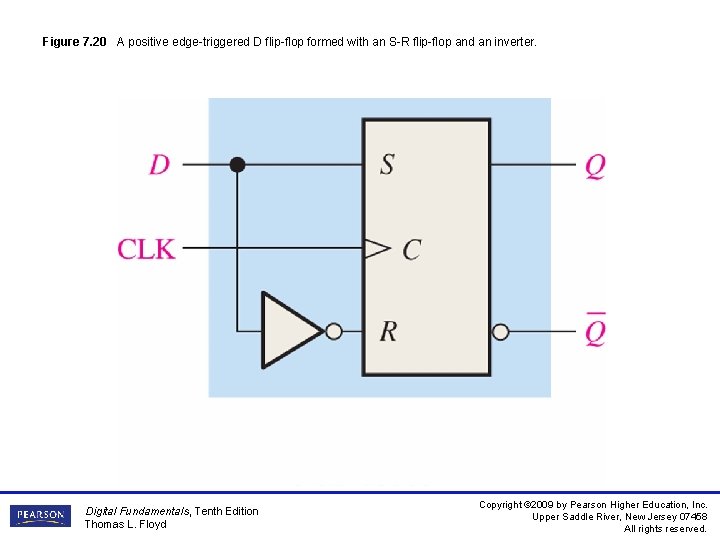

Figure 7. 20 A positive edge-triggered D flip-flop formed with an S-R flip-flop and an inverter. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

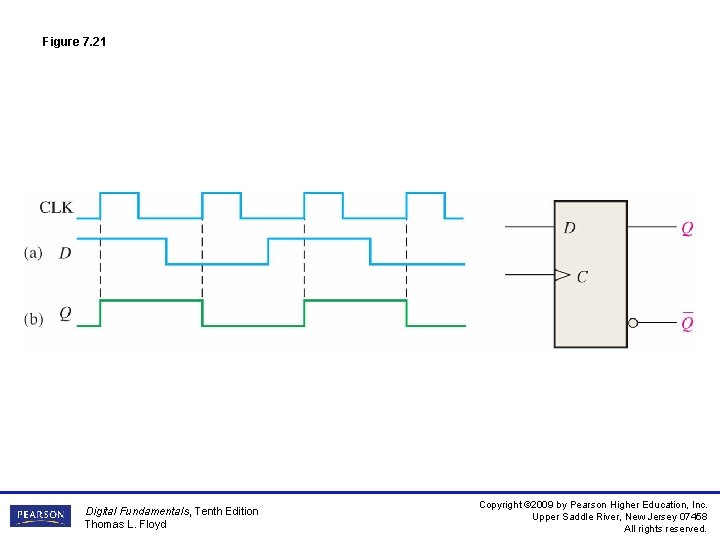

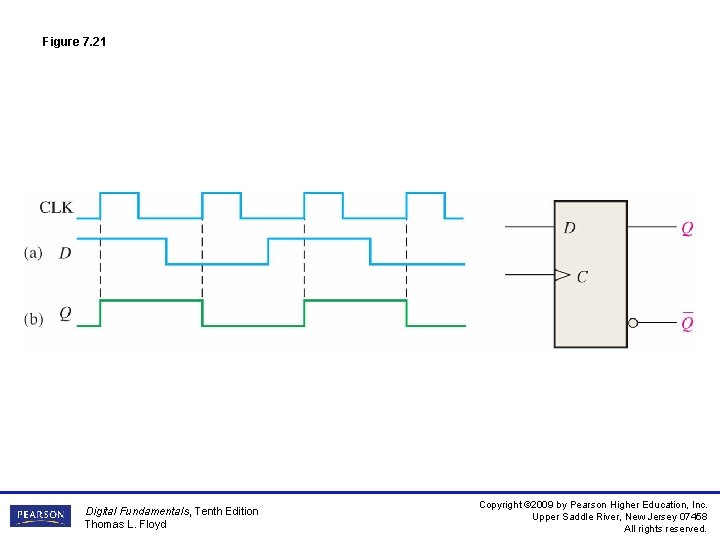

Figure 7. 21 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

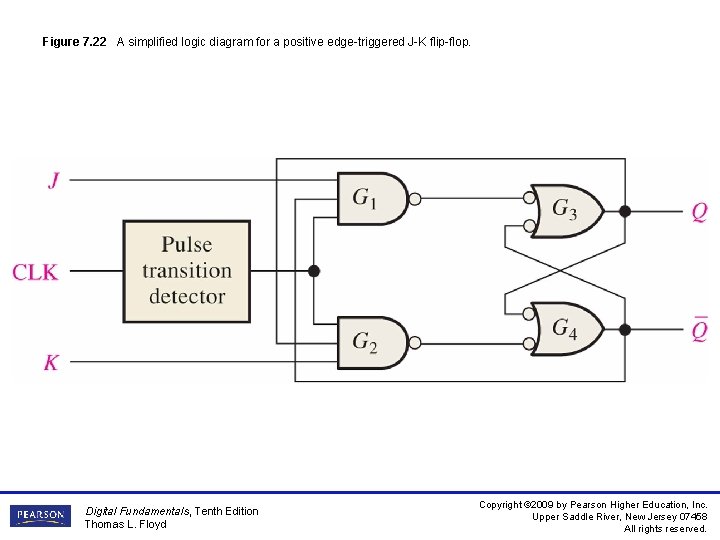

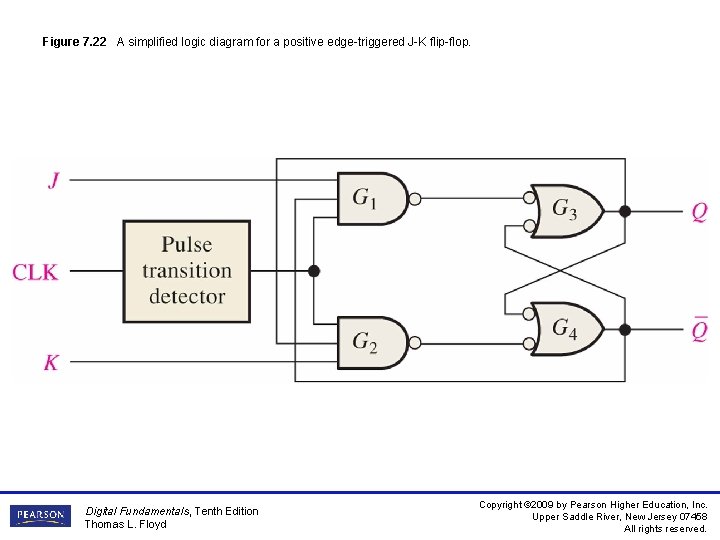

Figure 7. 22 A simplified logic diagram for a positive edge-triggered J-K flip-flop. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

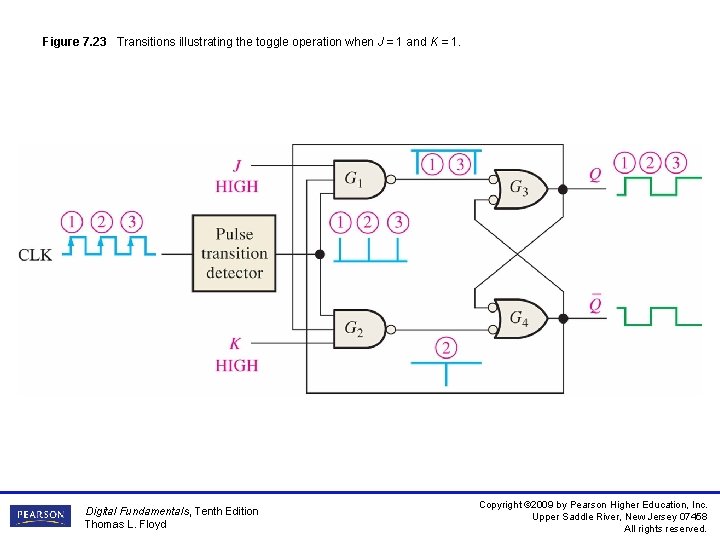

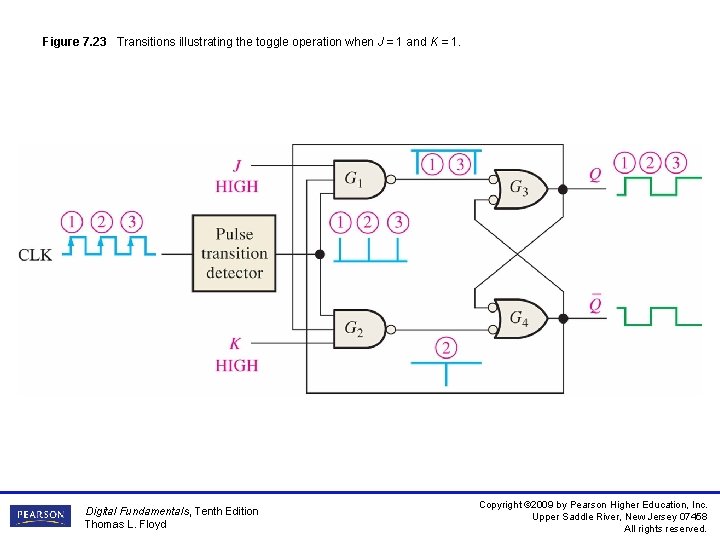

Figure 7. 23 Transitions illustrating the toggle operation when J = 1 and K = 1. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

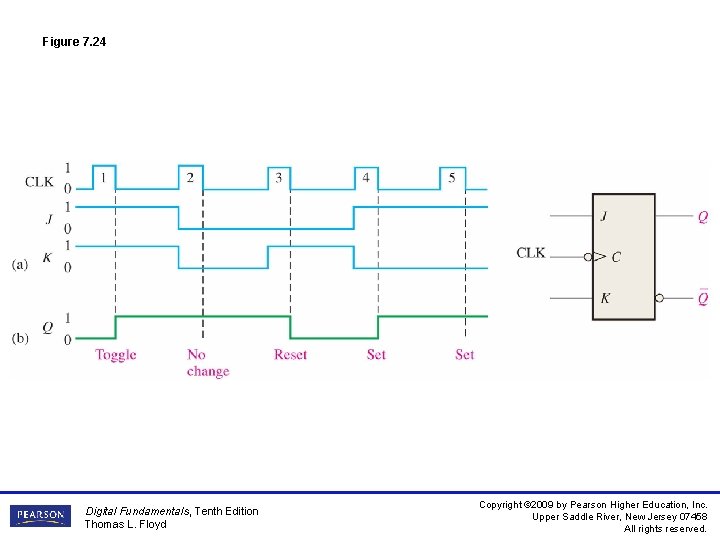

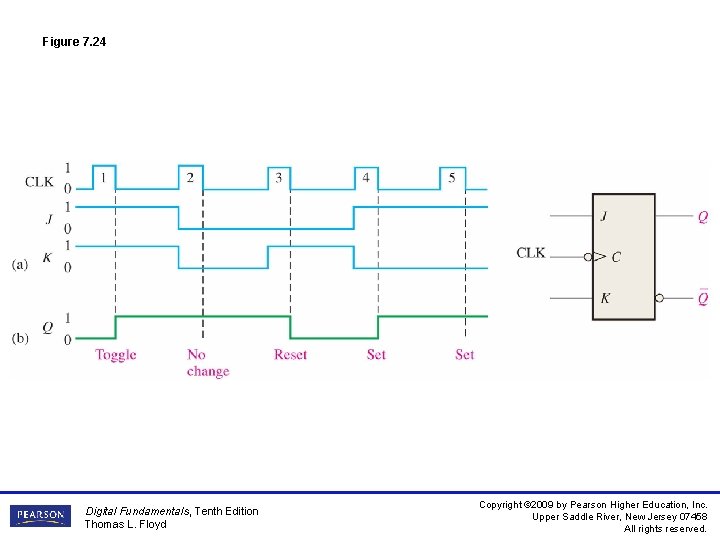

Figure 7. 24 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

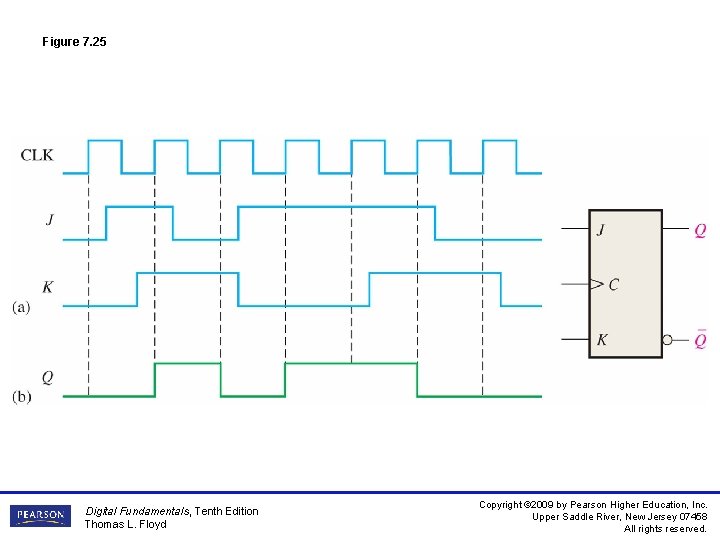

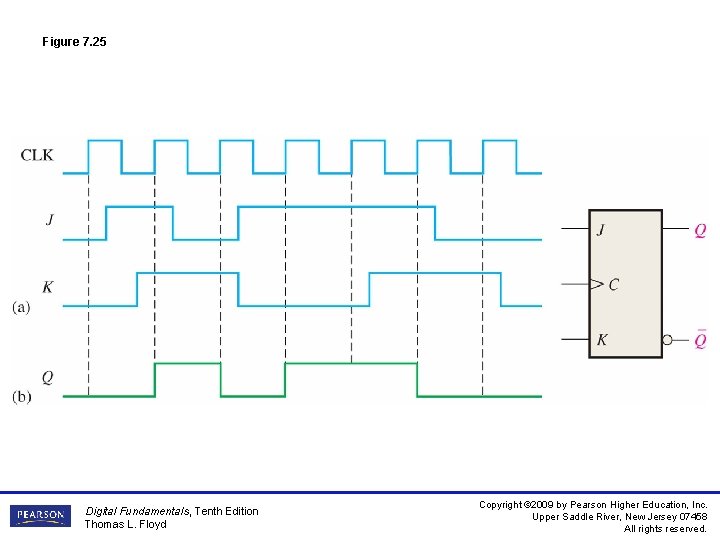

Figure 7. 25 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

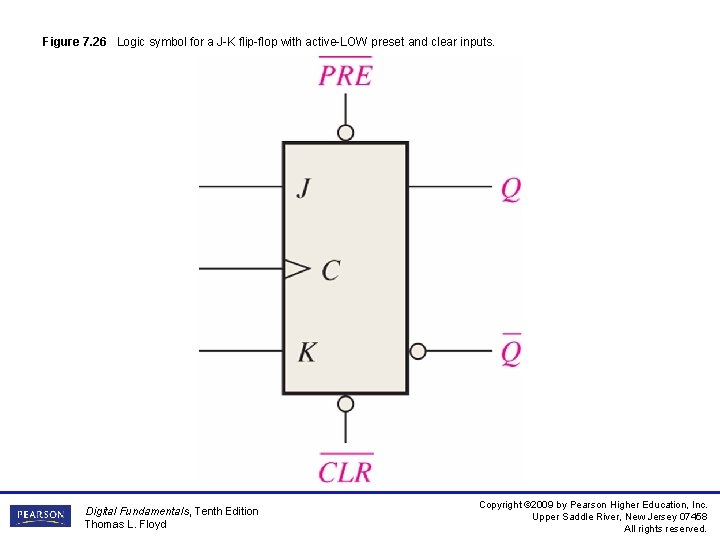

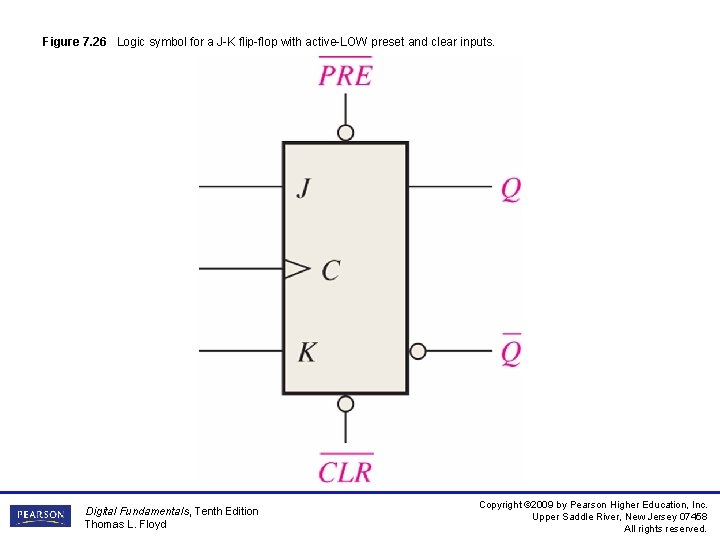

Figure 7. 26 Logic symbol for a J-K flip-flop with active-LOW preset and clear inputs. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

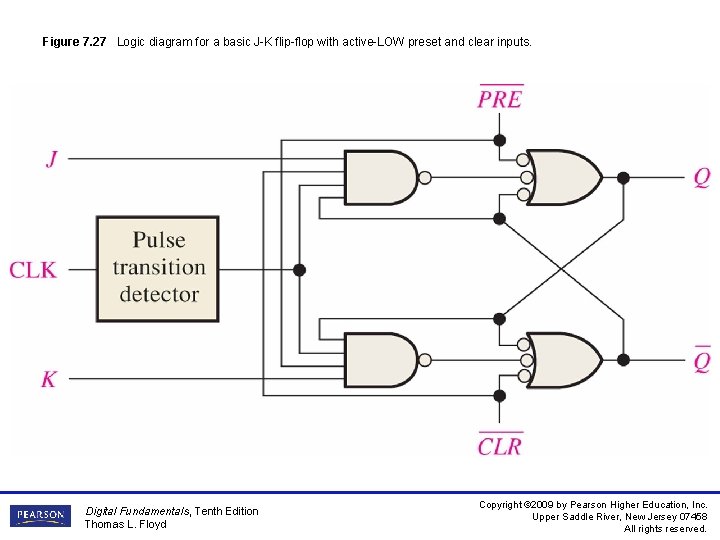

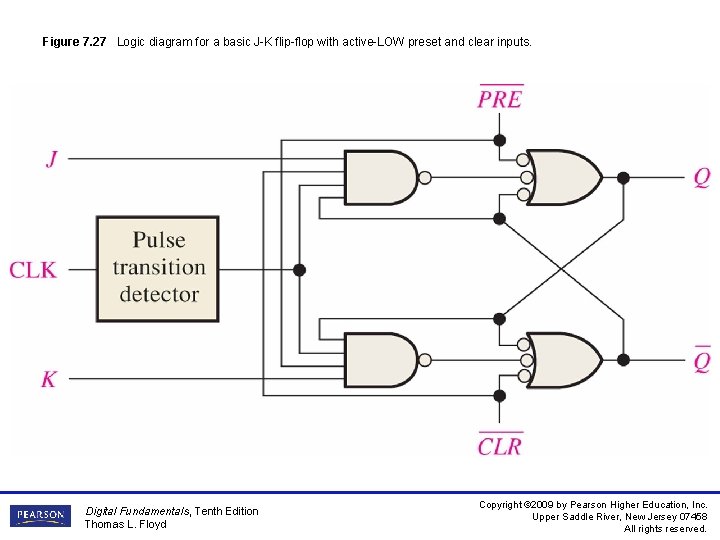

Figure 7. 27 Logic diagram for a basic J-K flip-flop with active-LOW preset and clear inputs. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

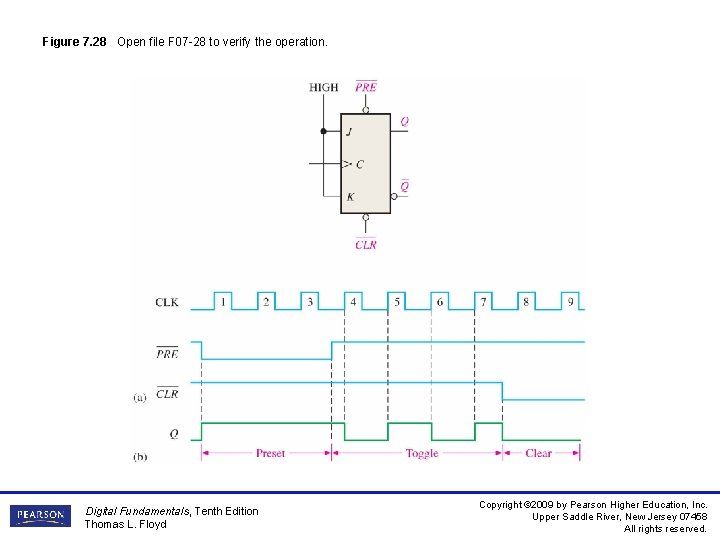

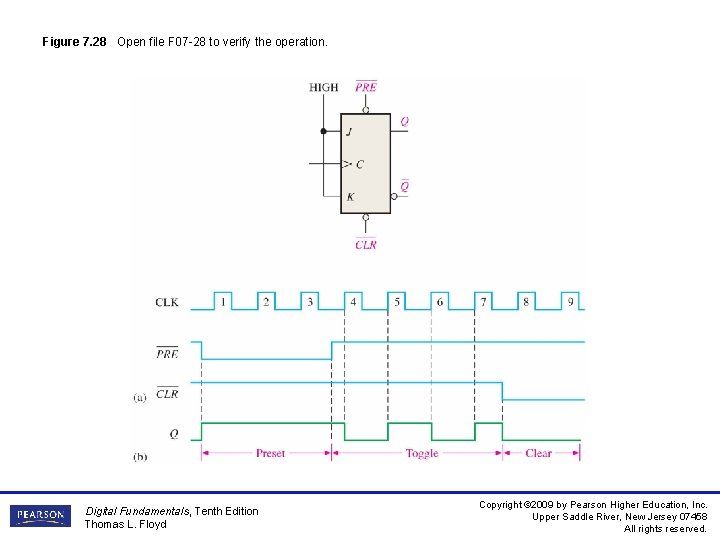

Figure 7. 28 Open file F 07 -28 to verify the operation. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

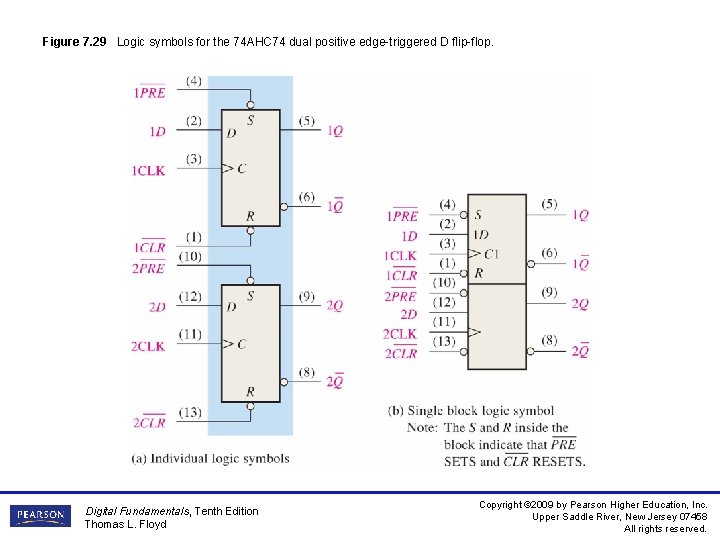

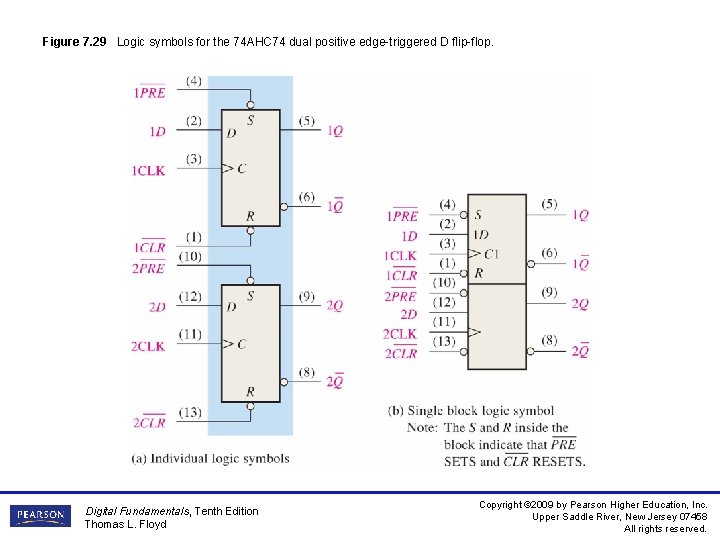

Figure 7. 29 Logic symbols for the 74 AHC 74 dual positive edge-triggered D flip-flop. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

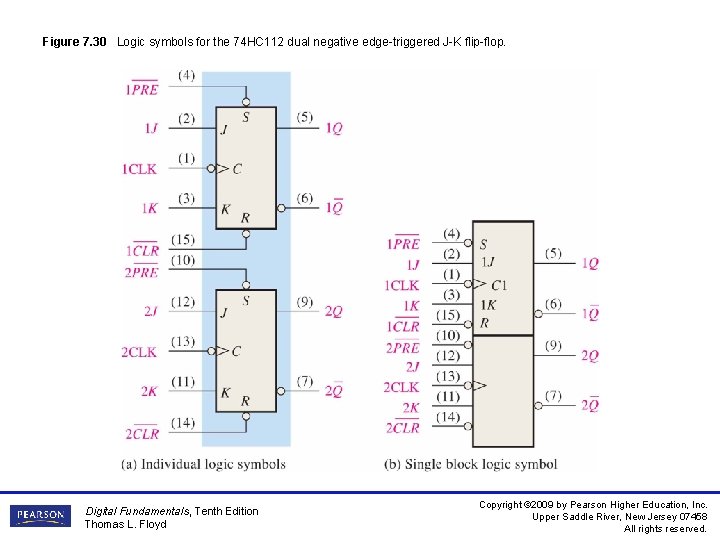

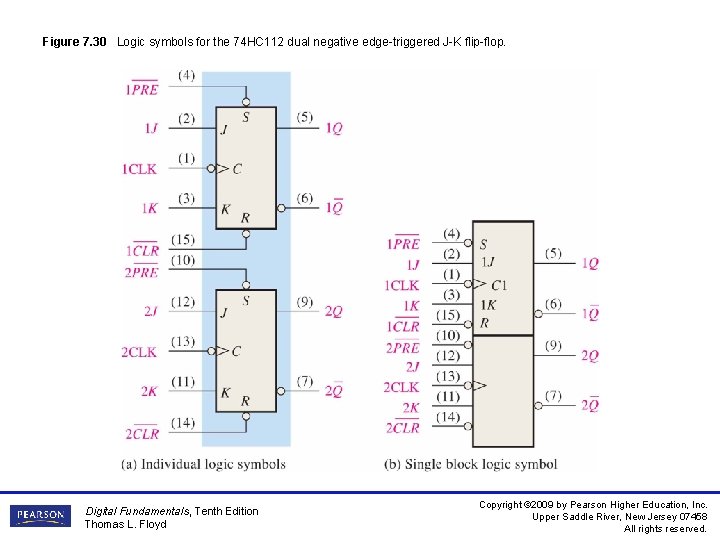

Figure 7. 30 Logic symbols for the 74 HC 112 dual negative edge-triggered J-K flip-flop. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

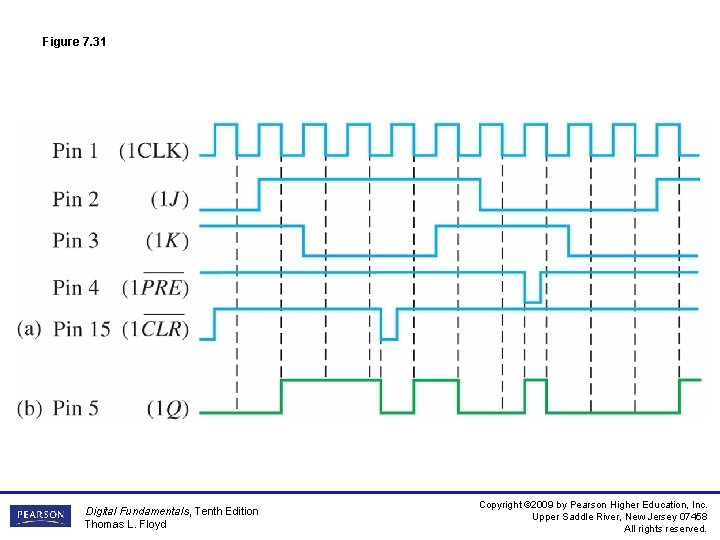

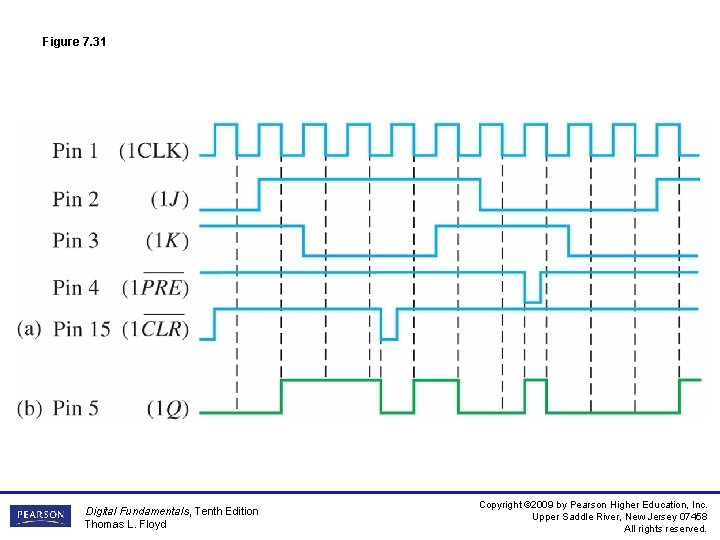

Figure 7. 31 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

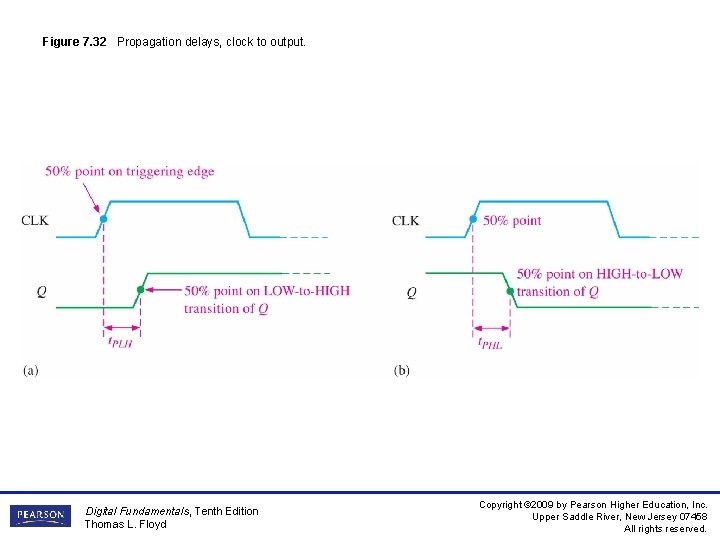

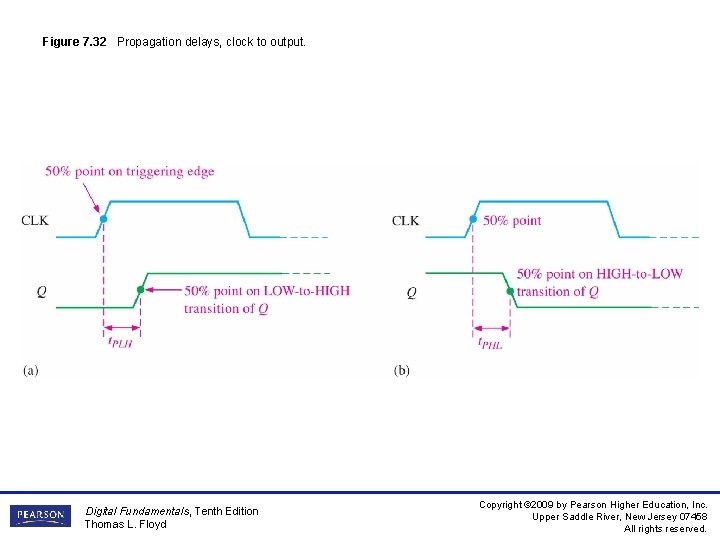

Figure 7. 32 Propagation delays, clock to output. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

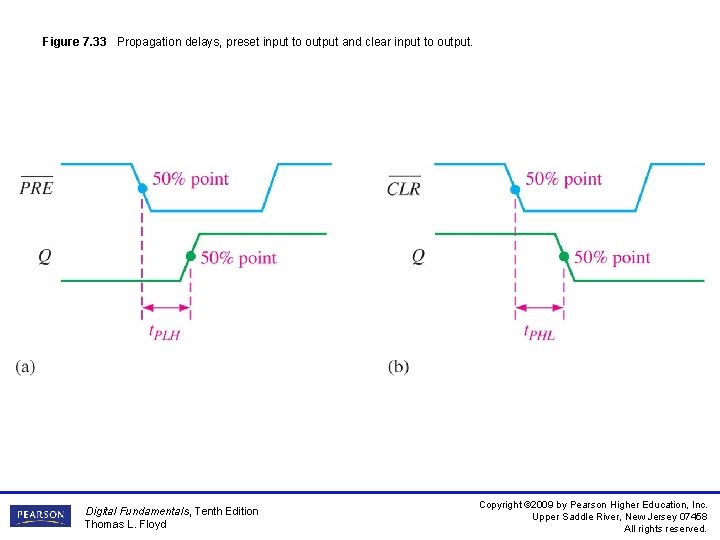

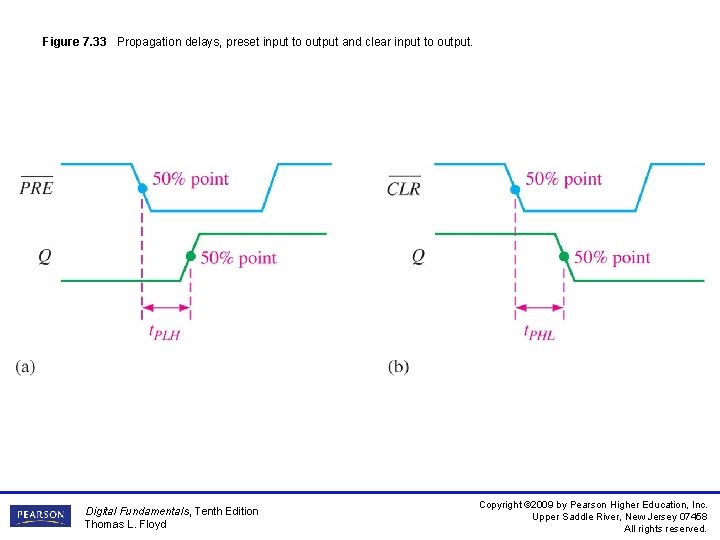

Figure 7. 33 Propagation delays, preset input to output and clear input to output. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

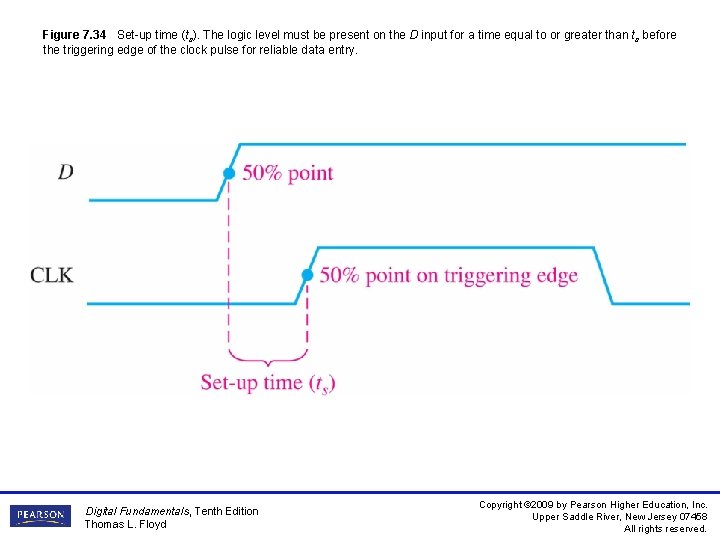

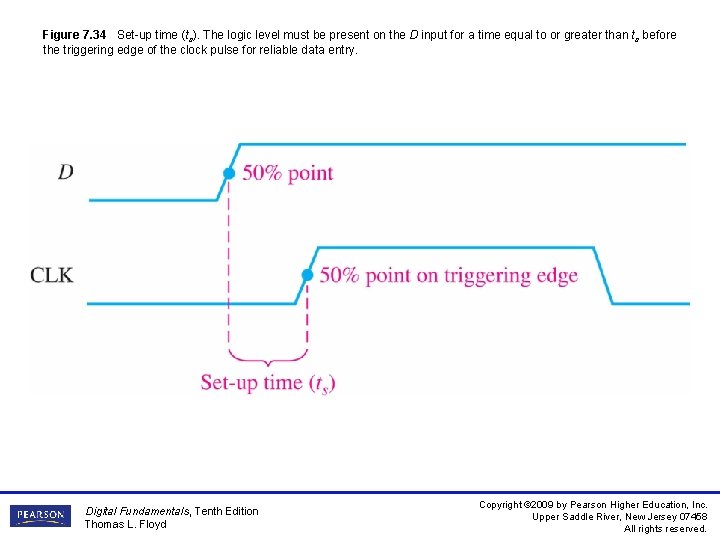

Figure 7. 34 Set-up time (ts). The logic level must be present on the D input for a time equal to or greater than ts before the triggering edge of the clock pulse for reliable data entry. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

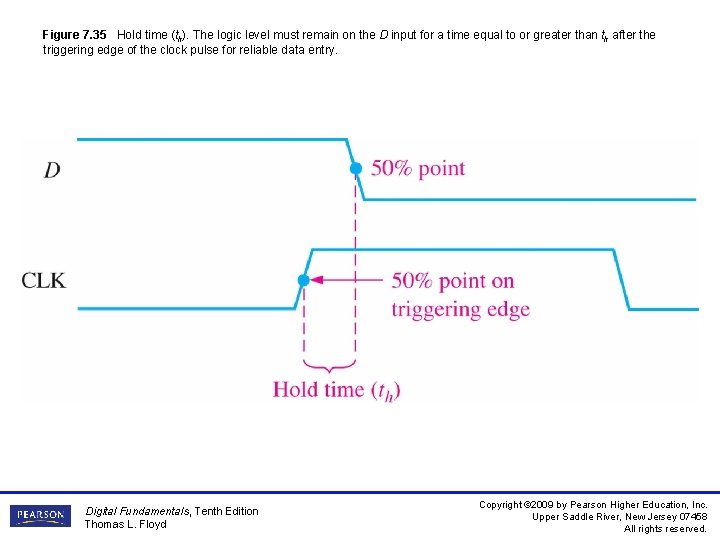

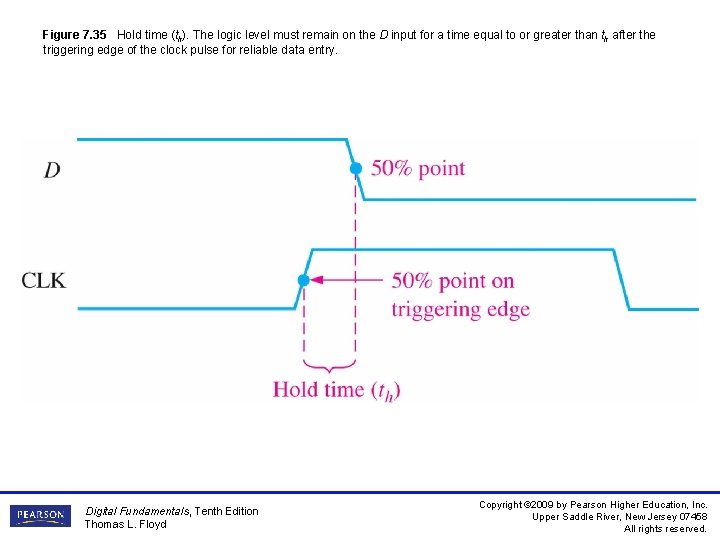

Figure 7. 35 Hold time (th). The logic level must remain on the D input for a time equal to or greater than th after the triggering edge of the clock pulse for reliable data entry. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

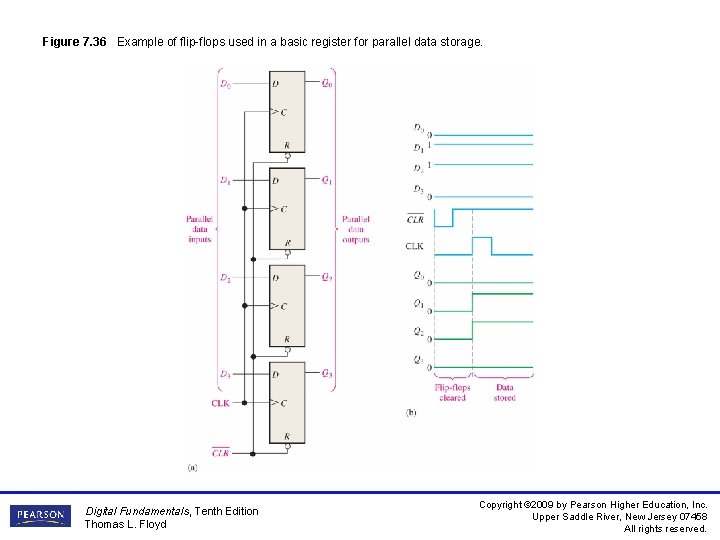

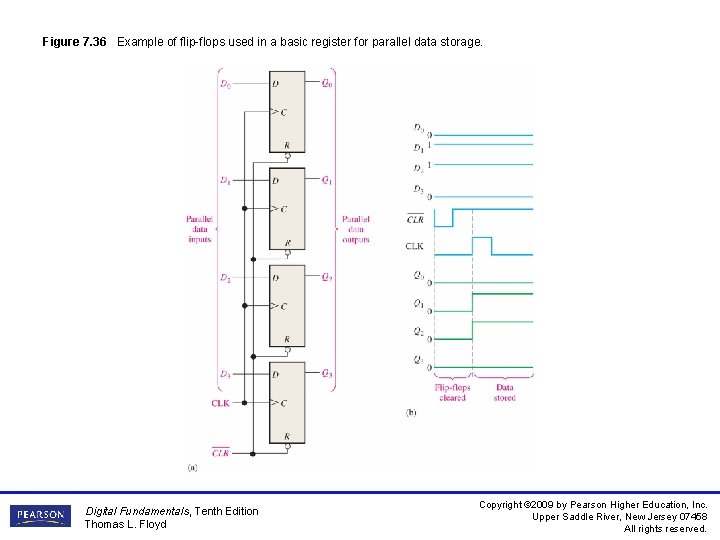

Figure 7. 36 Example of flip-flops used in a basic register for parallel data storage. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

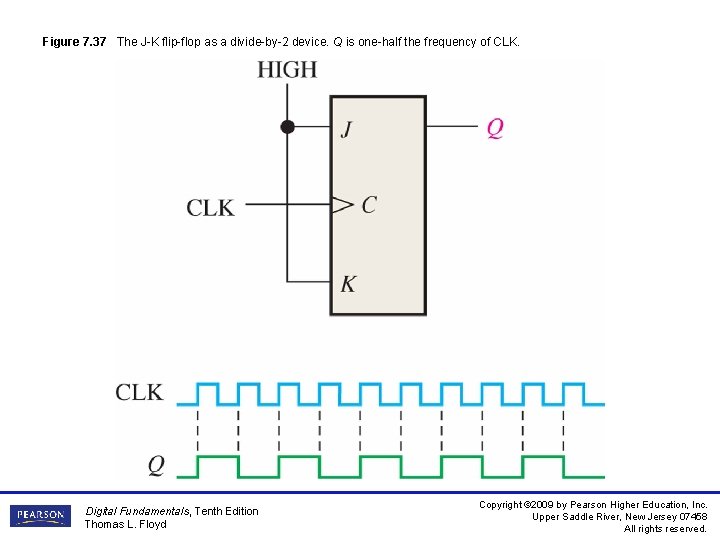

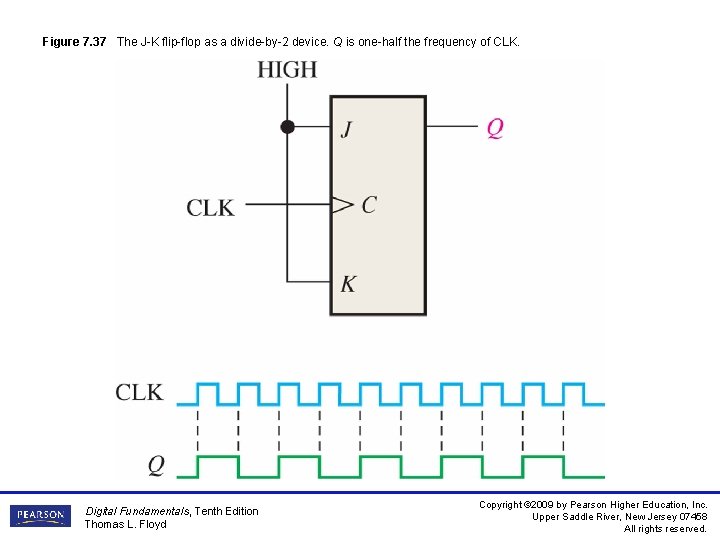

Figure 7. 37 The J-K flip-flop as a divide-by-2 device. Q is one-half the frequency of CLK. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

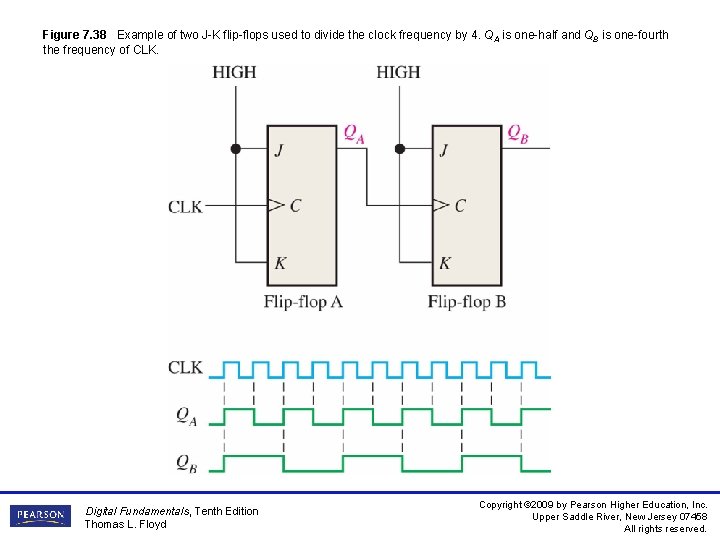

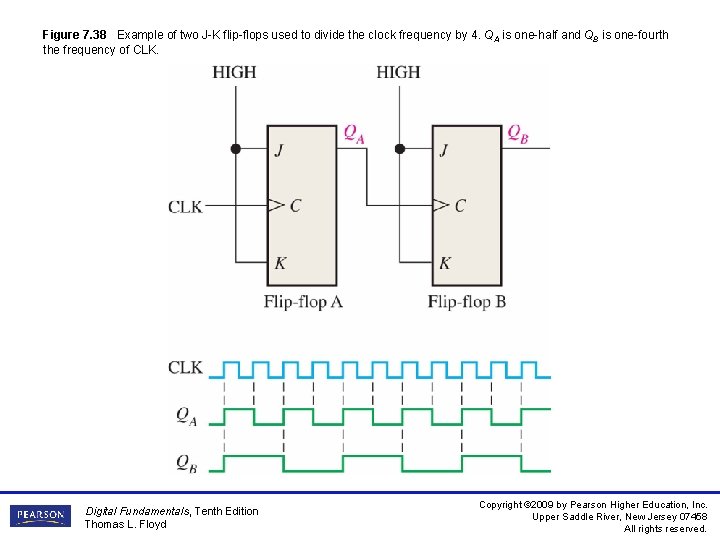

Figure 7. 38 Example of two J-K flip-flops used to divide the clock frequency by 4. QA is one-half and QB is one-fourth the frequency of CLK. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

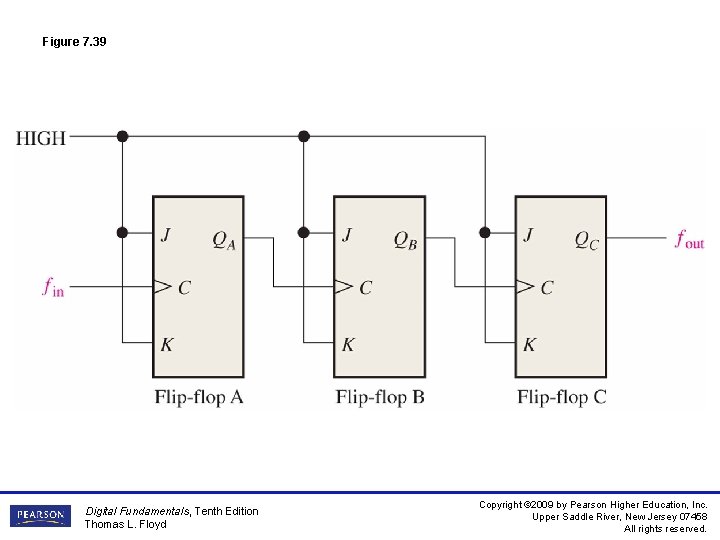

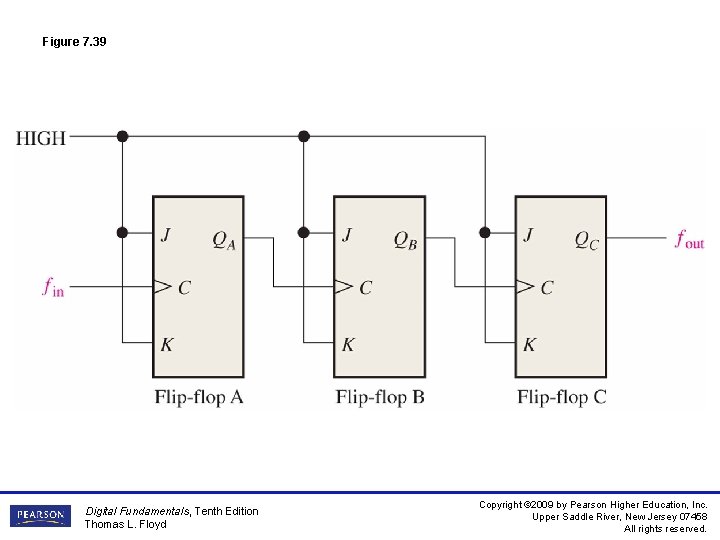

Figure 7. 39 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

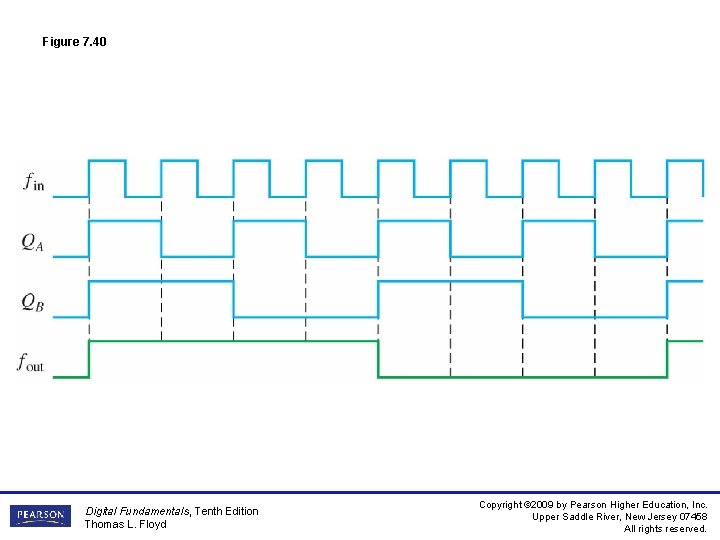

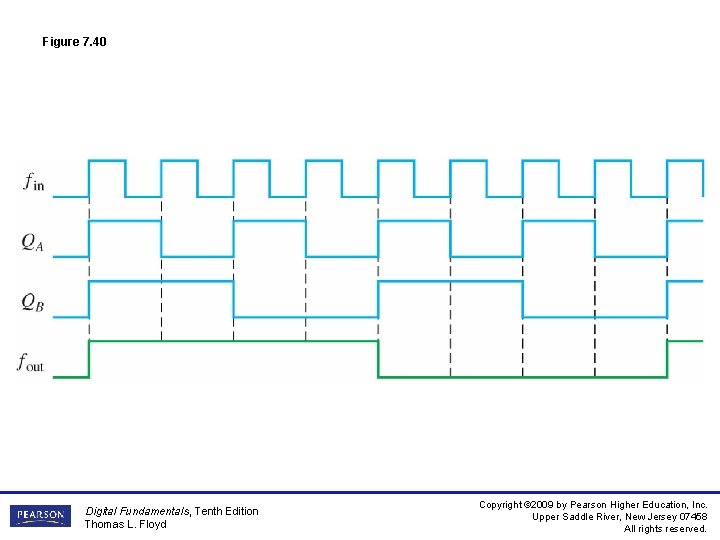

Figure 7. 40 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

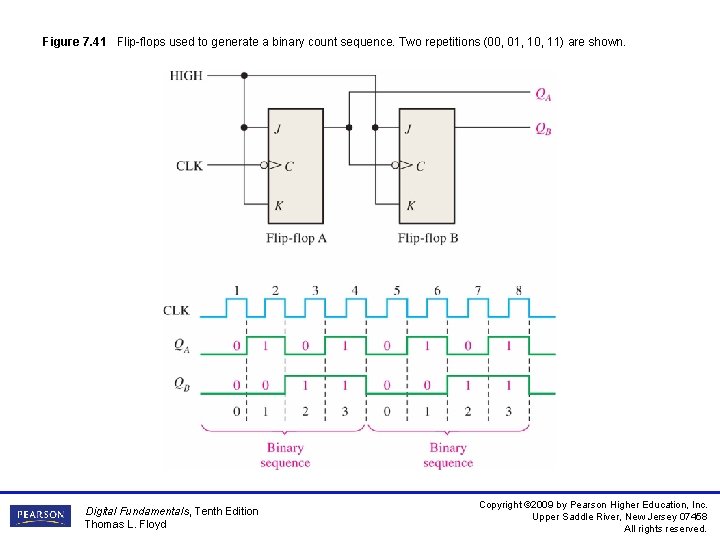

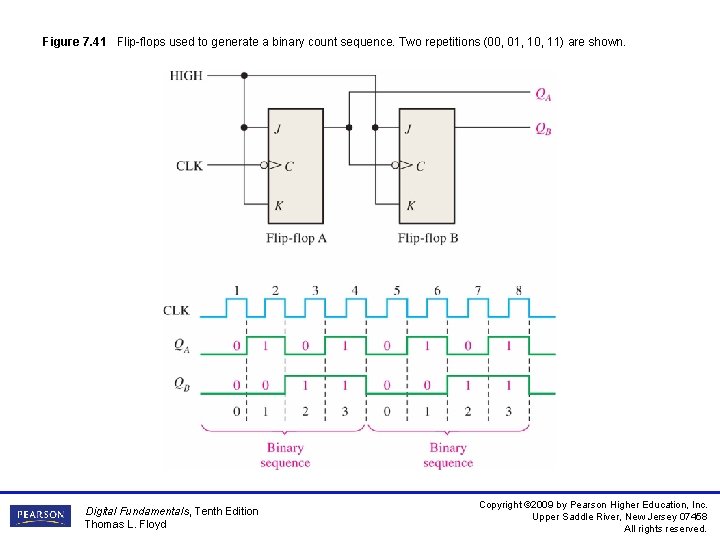

Figure 7. 41 Flip-flops used to generate a binary count sequence. Two repetitions (00, 01, 10, 11) are shown. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

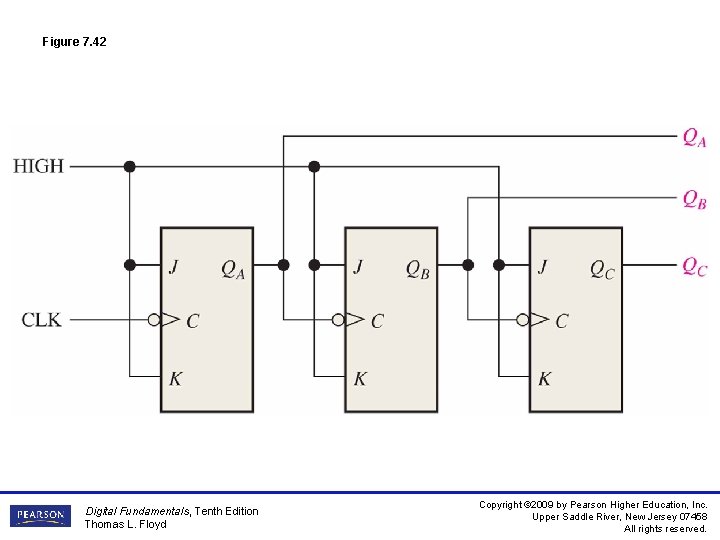

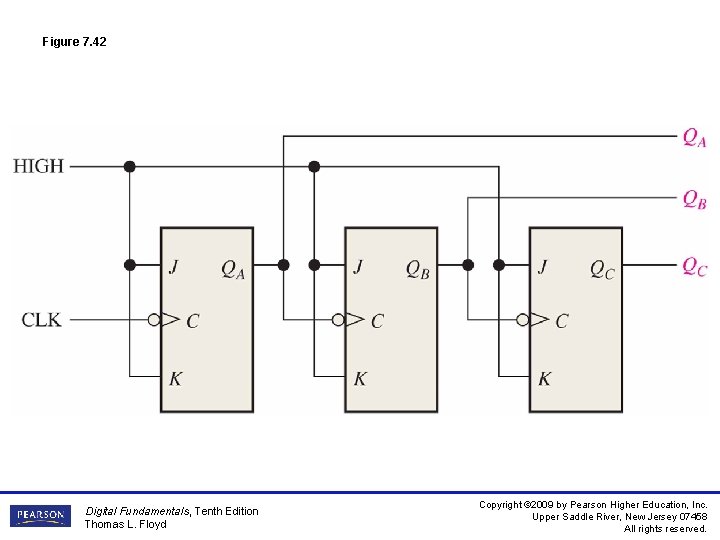

Figure 7. 42 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

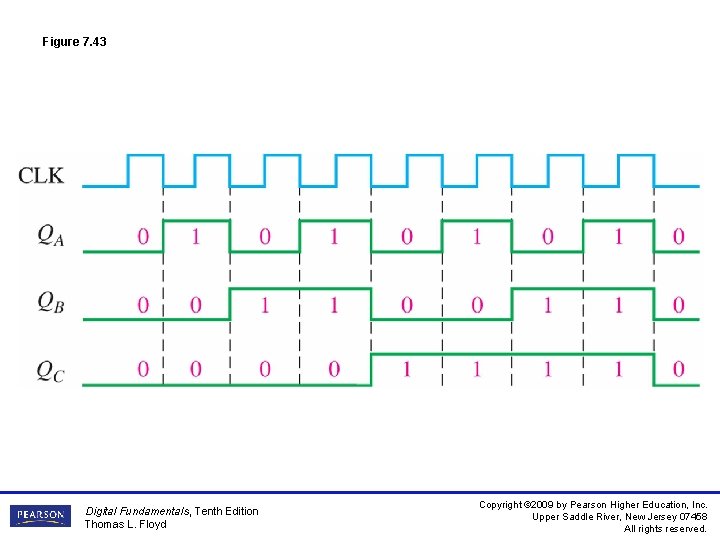

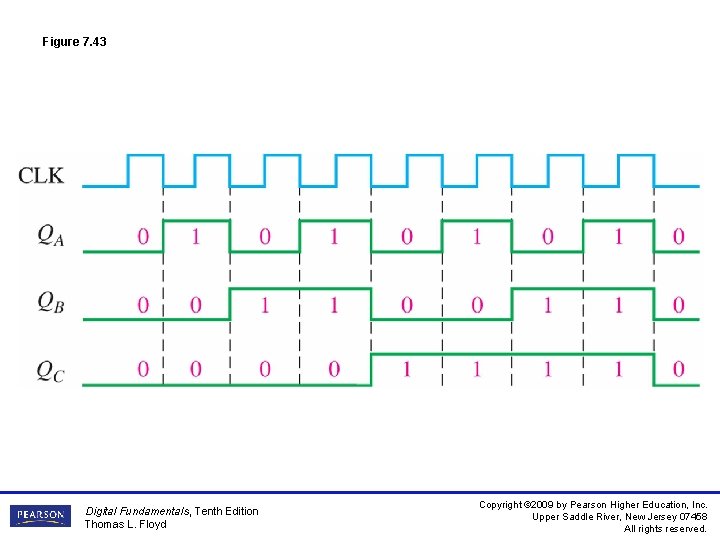

Figure 7. 43 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

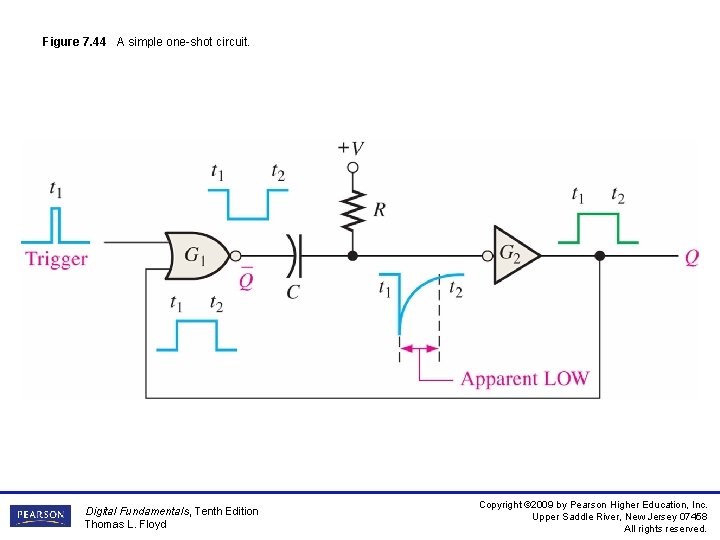

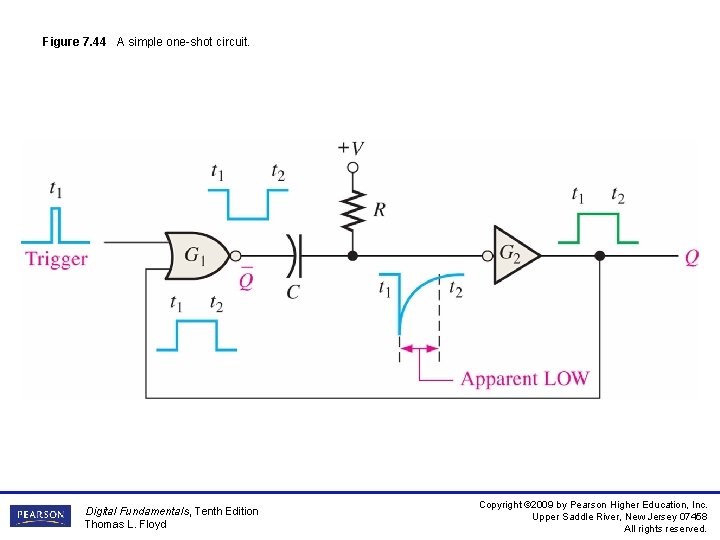

Figure 7. 44 A simple one-shot circuit. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

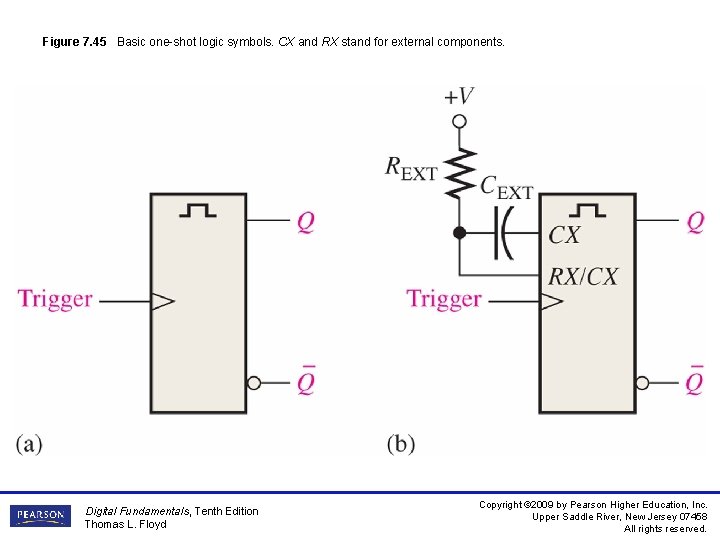

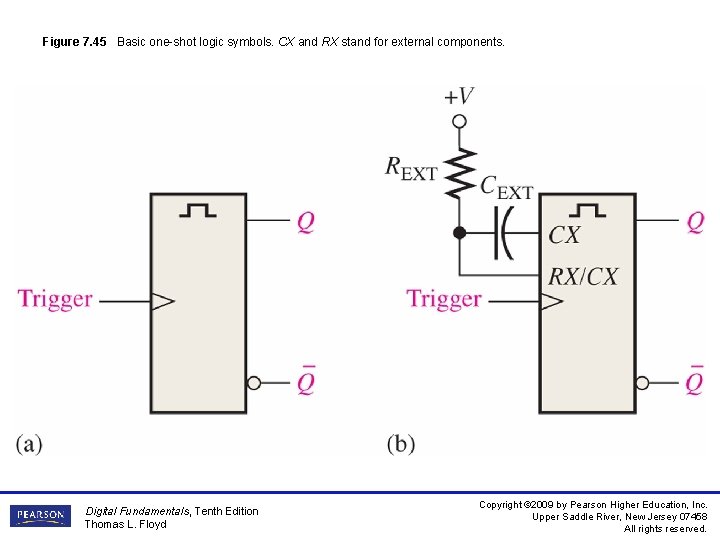

Figure 7. 45 Basic one-shot logic symbols. CX and RX stand for external components. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

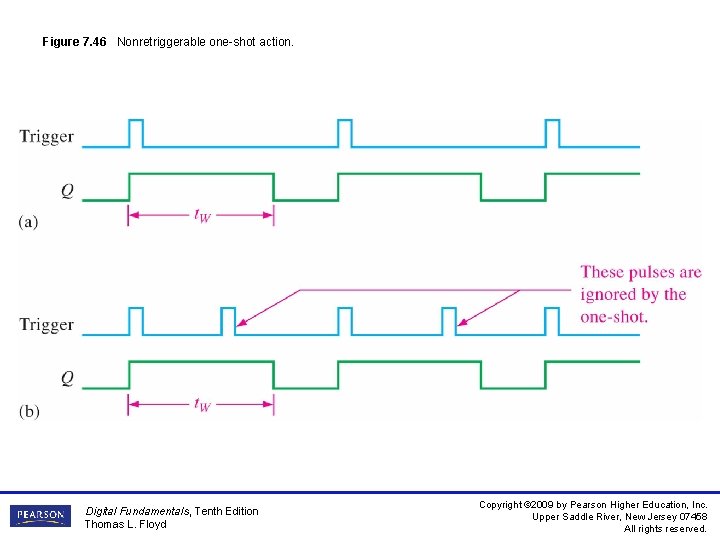

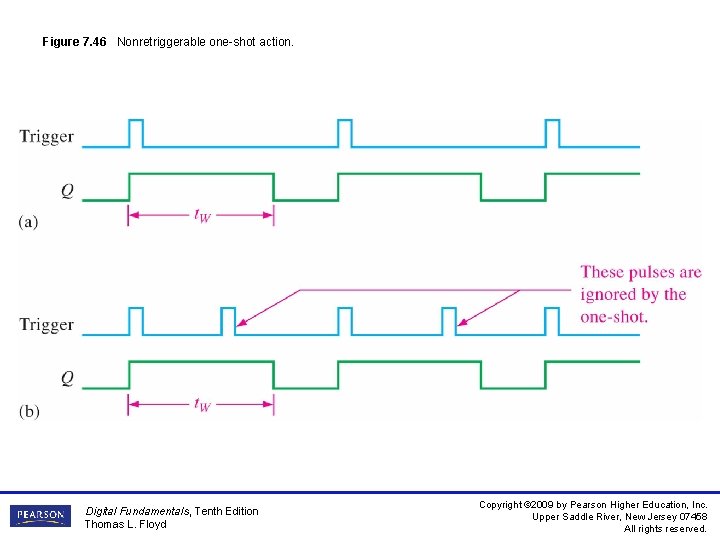

Figure 7. 46 Nonretriggerable one-shot action. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

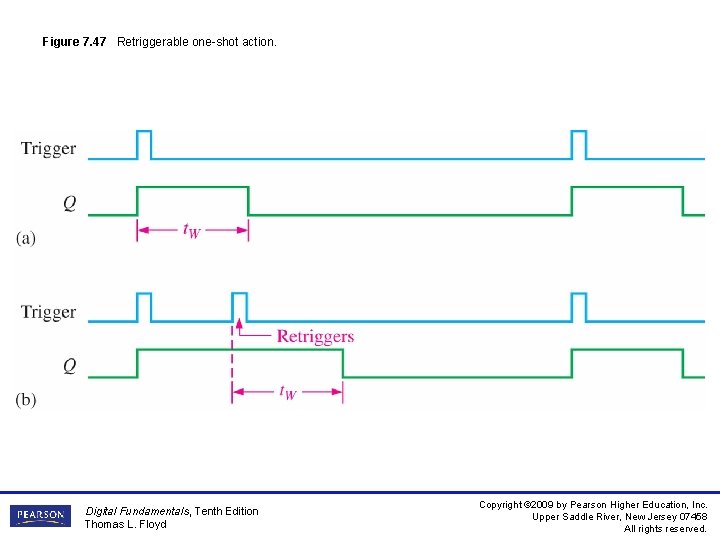

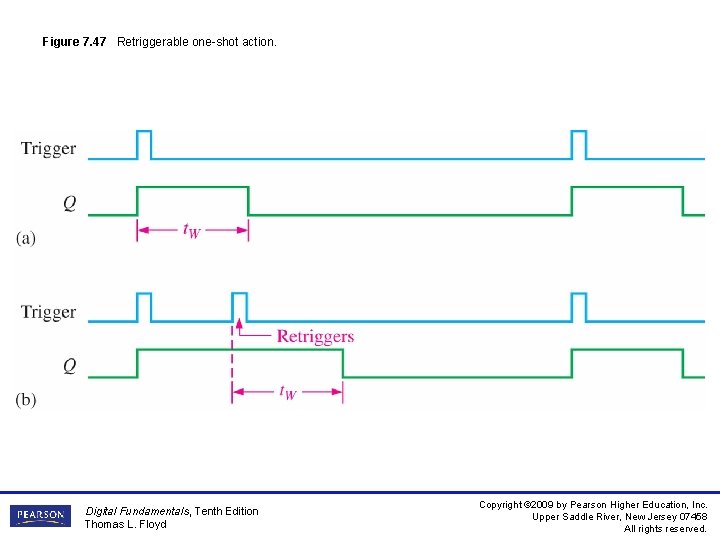

Figure 7. 47 Retriggerable one-shot action. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

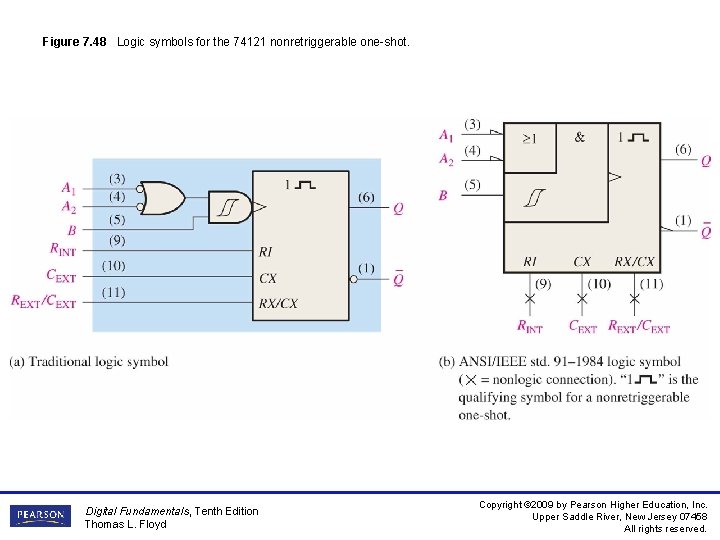

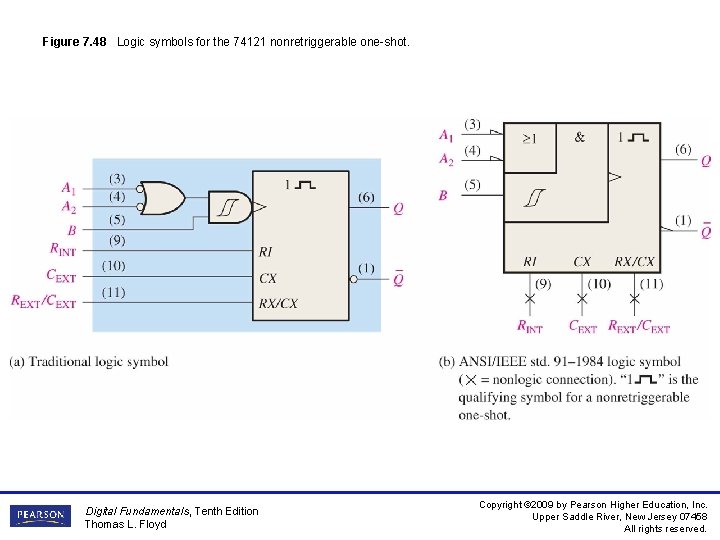

Figure 7. 48 Logic symbols for the 74121 nonretriggerable one-shot. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

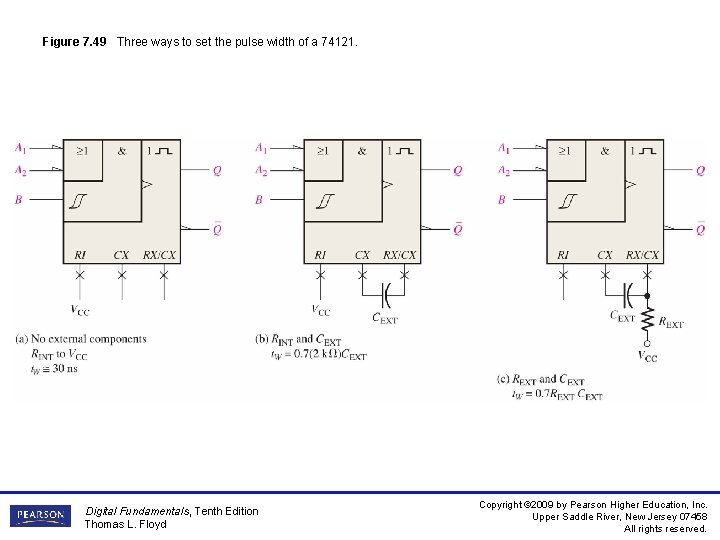

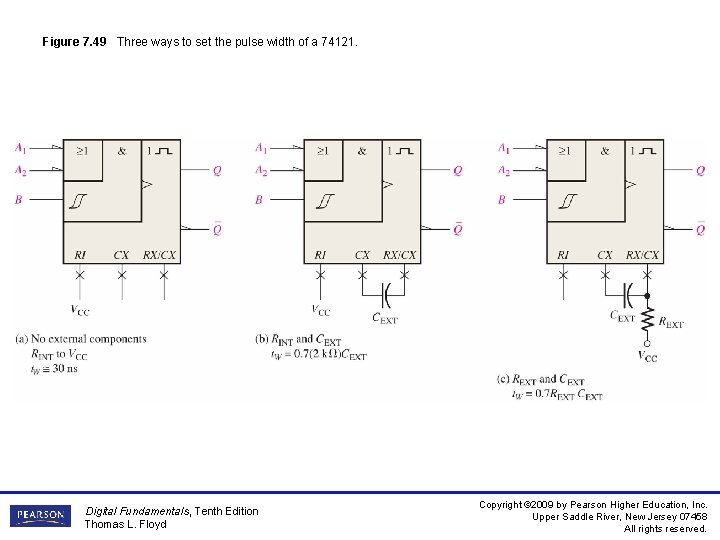

Figure 7. 49 Three ways to set the pulse width of a 74121. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

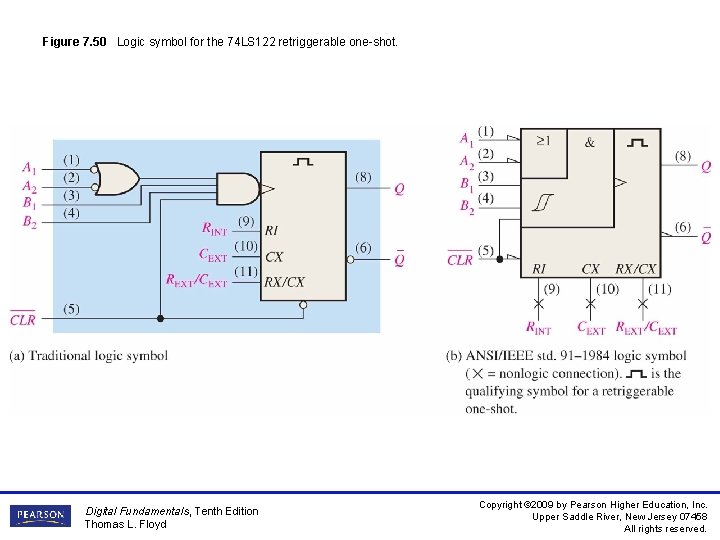

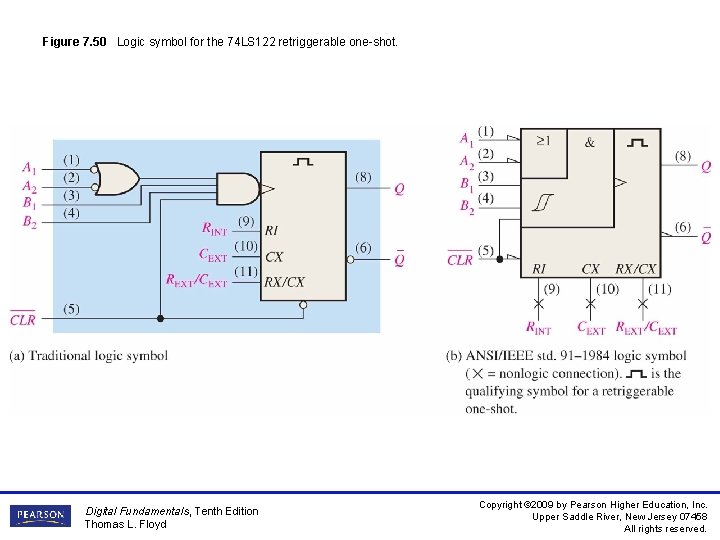

Figure 7. 50 Logic symbol for the 74 LS 122 retriggerable one-shot. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

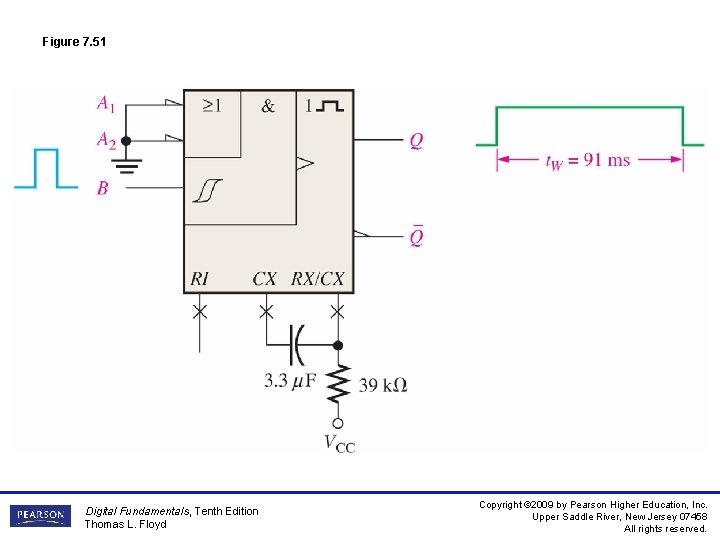

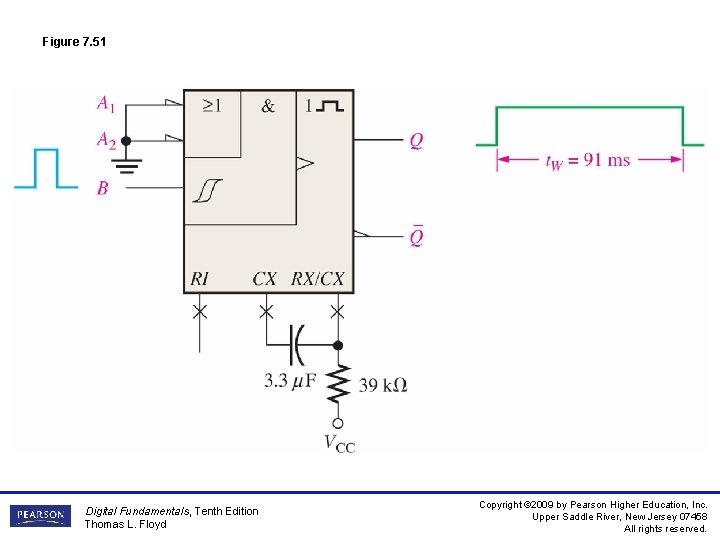

Figure 7. 51 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

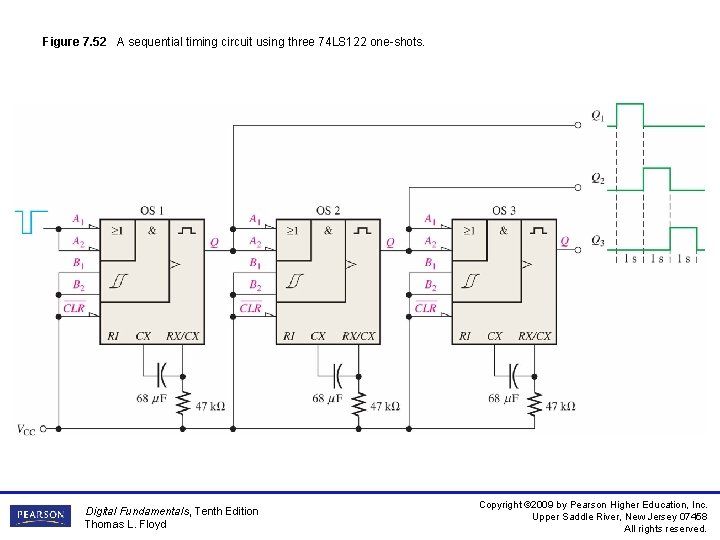

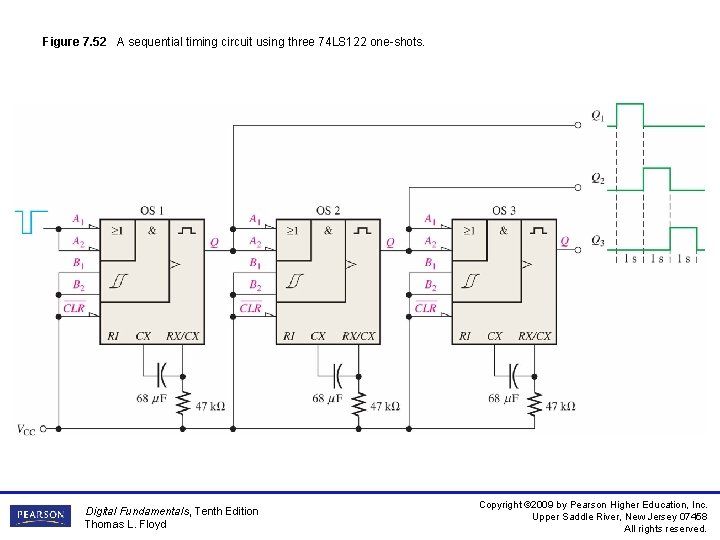

Figure 7. 52 A sequential timing circuit using three 74 LS 122 one-shots. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

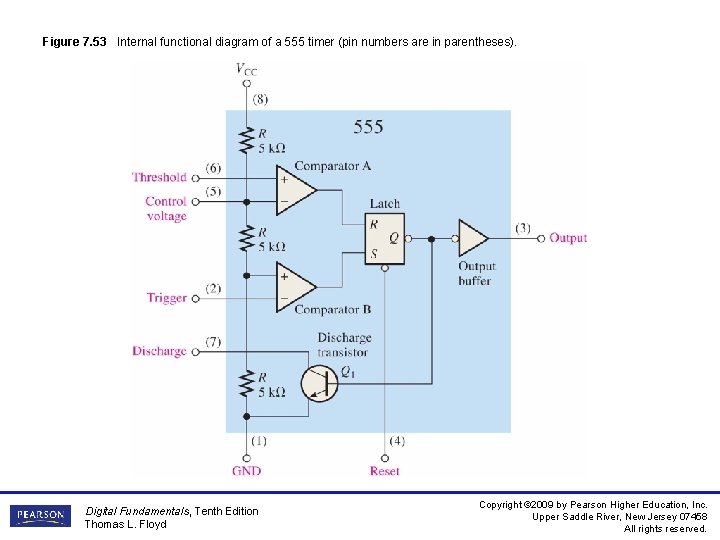

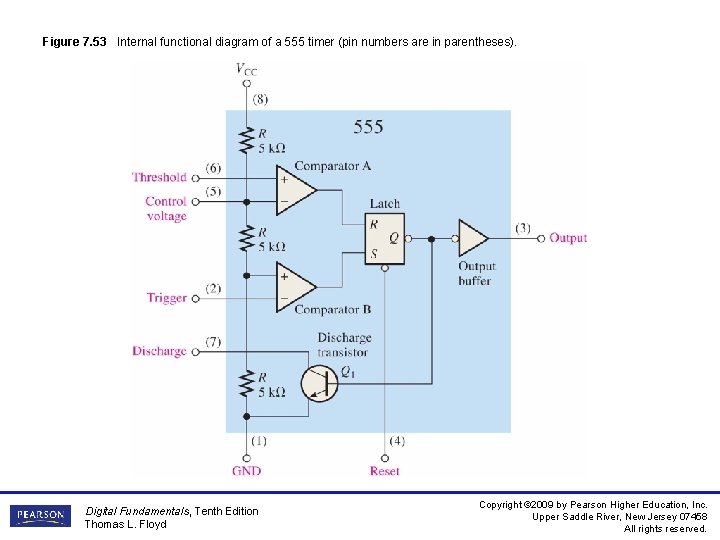

Figure 7. 53 Internal functional diagram of a 555 timer (pin numbers are in parentheses). Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

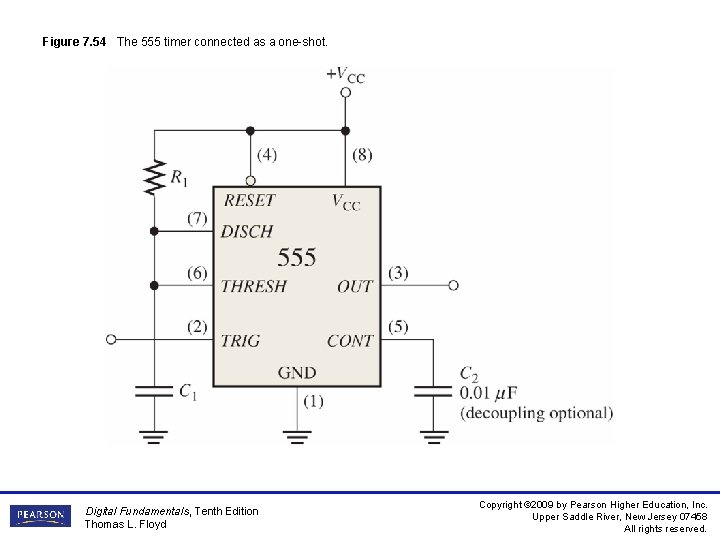

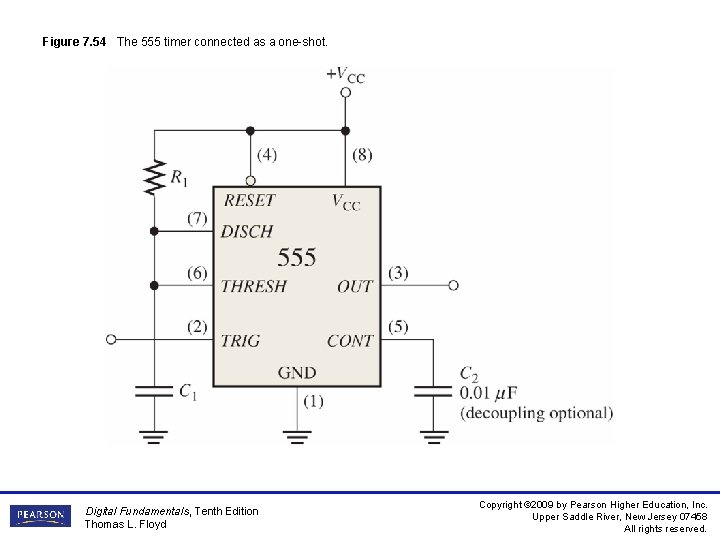

Figure 7. 54 The 555 timer connected as a one-shot. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

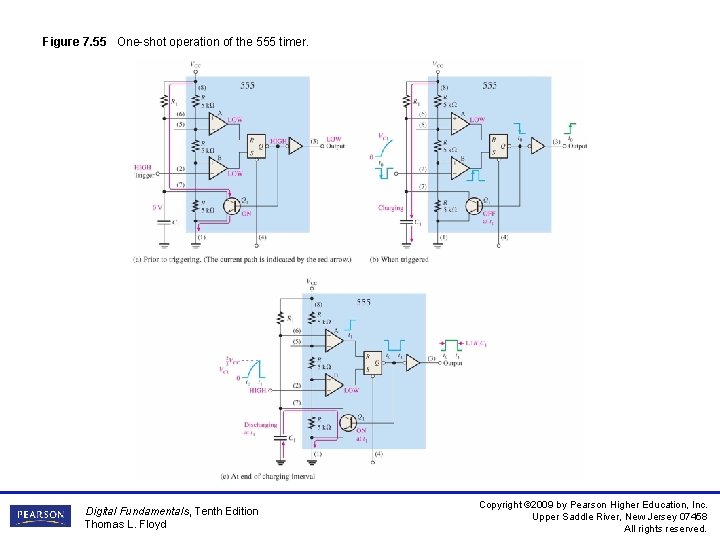

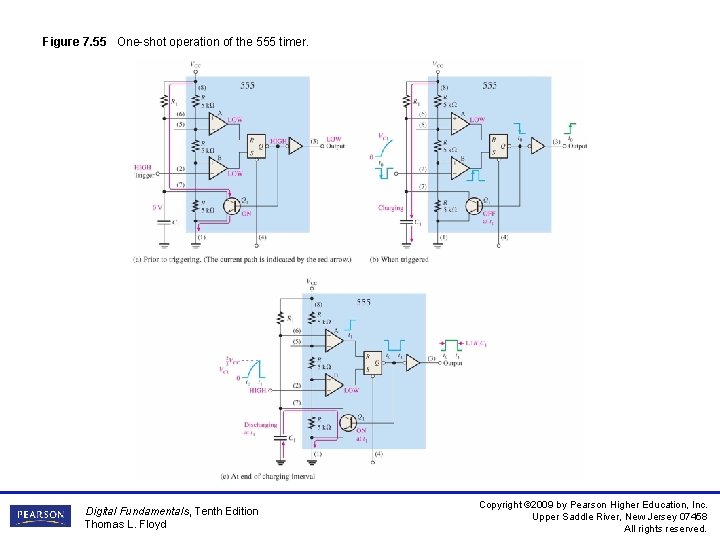

Figure 7. 55 One-shot operation of the 555 timer. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

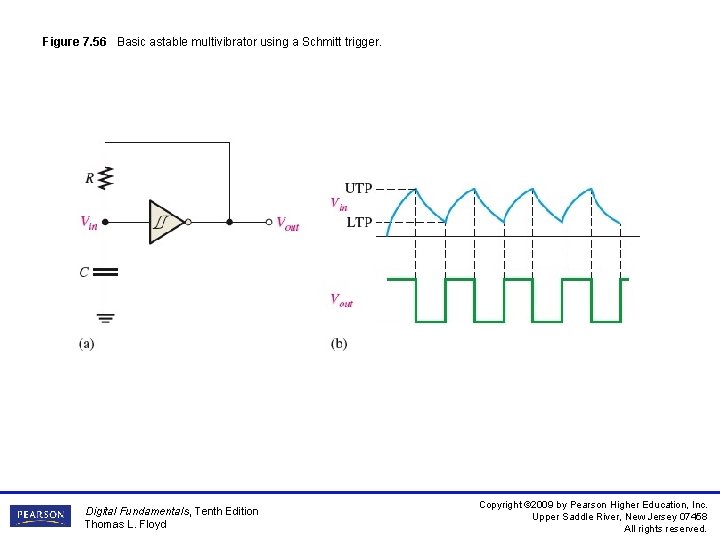

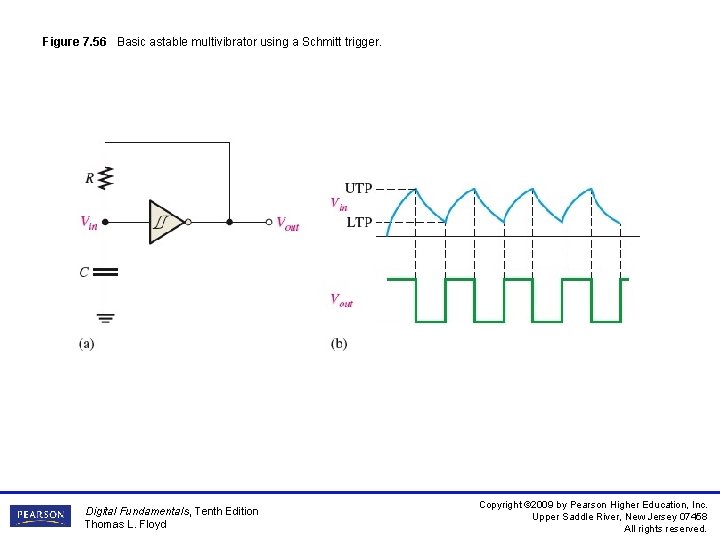

Figure 7. 56 Basic astable multivibrator using a Schmitt trigger. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

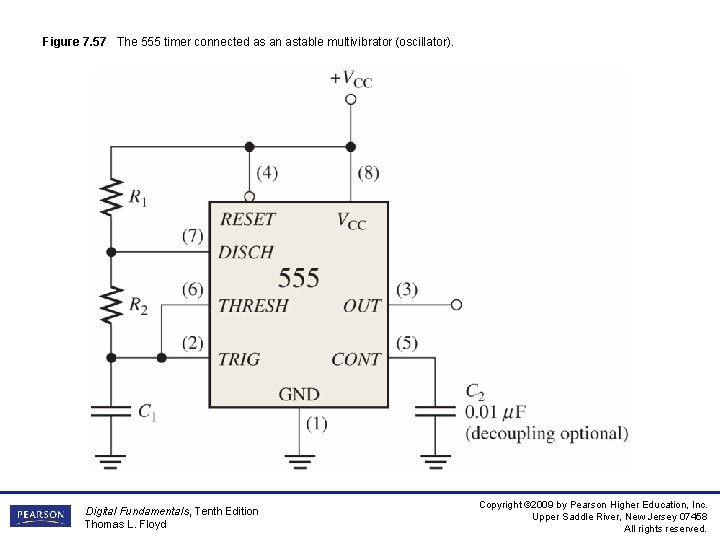

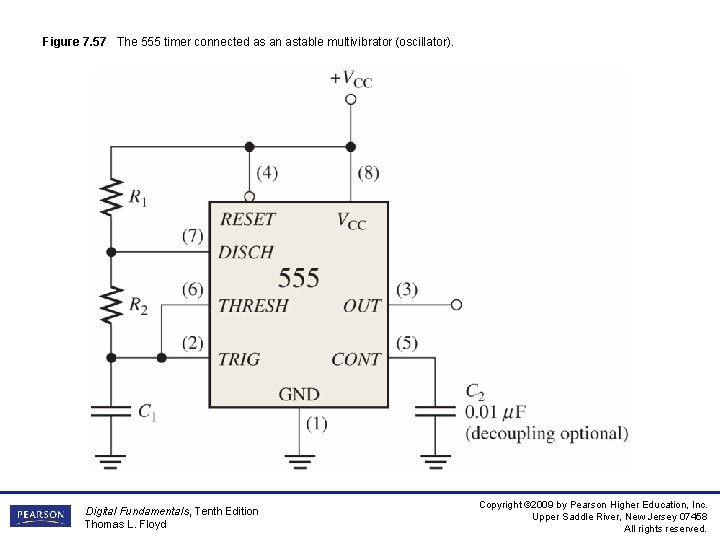

Figure 7. 57 The 555 timer connected as an astable multivibrator (oscillator). Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

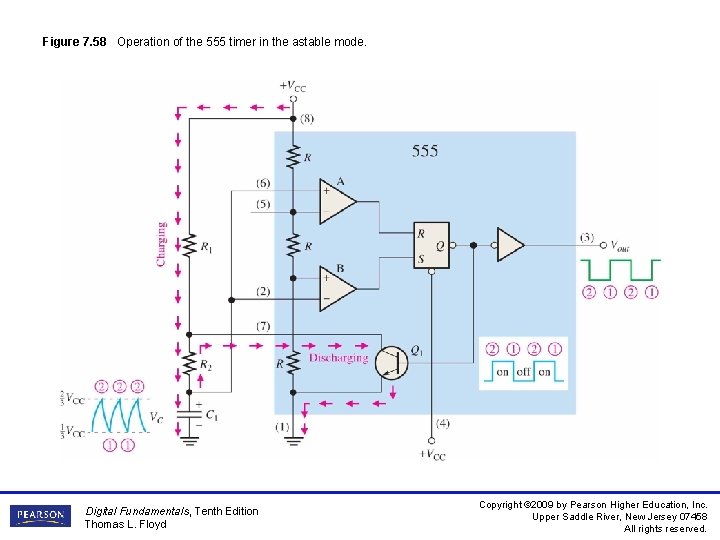

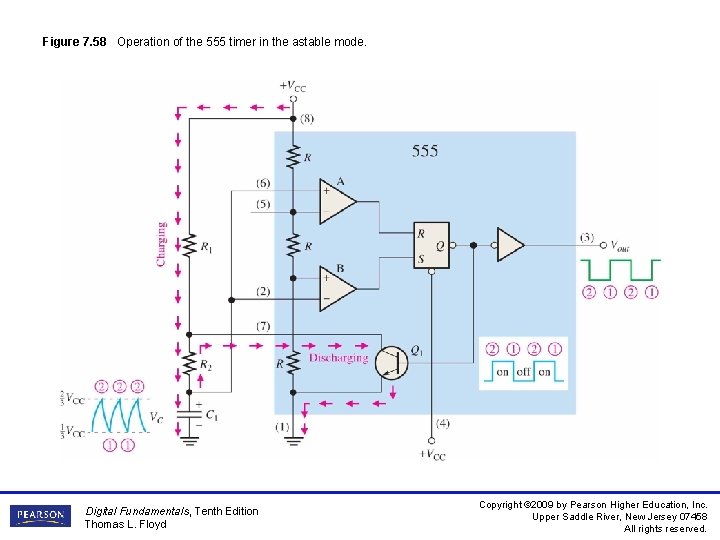

Figure 7. 58 Operation of the 555 timer in the astable mode. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

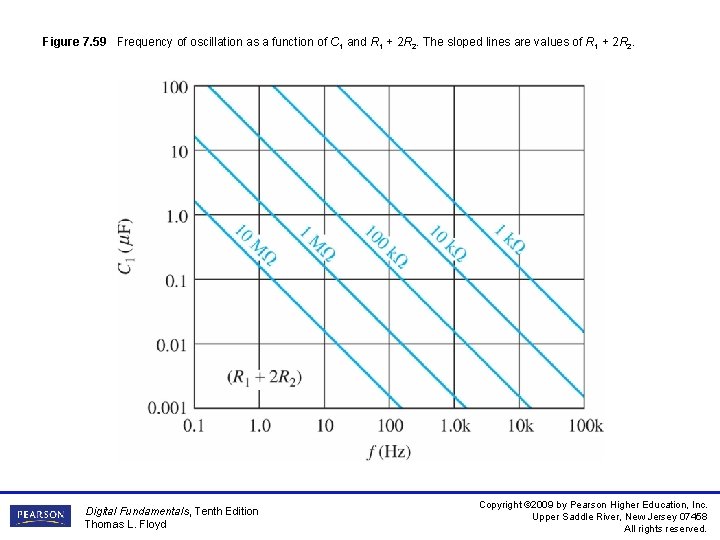

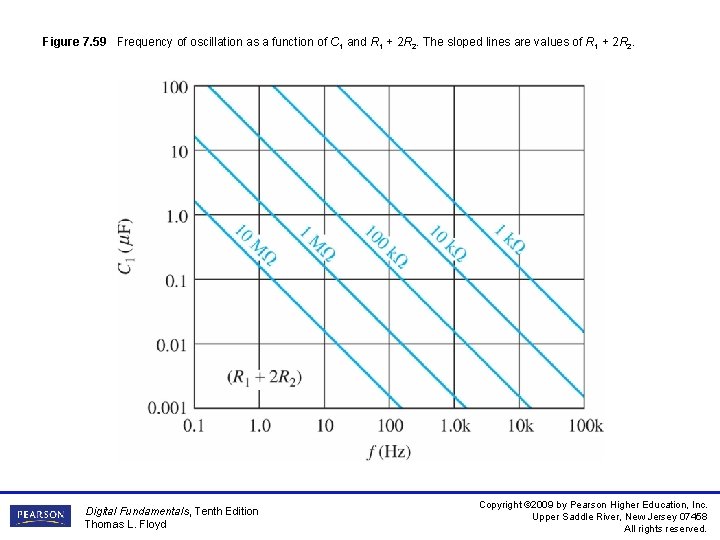

Figure 7. 59 Frequency of oscillation as a function of C 1 and R 1 + 2 R 2. The sloped lines are values of R 1 + 2 R 2. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

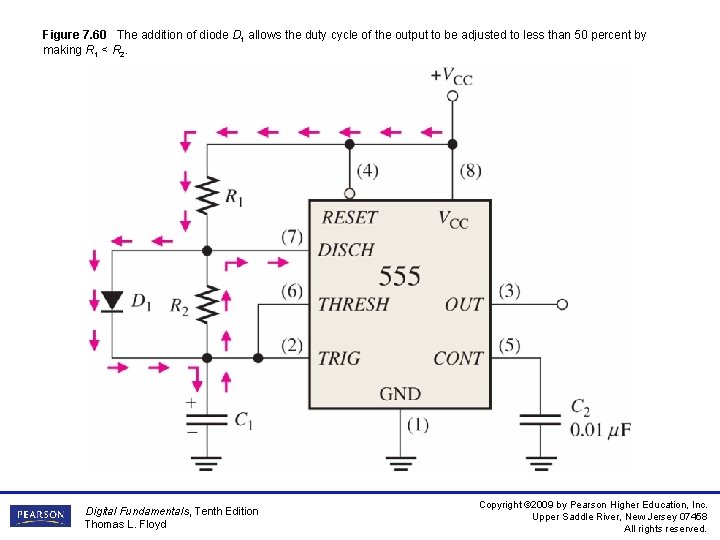

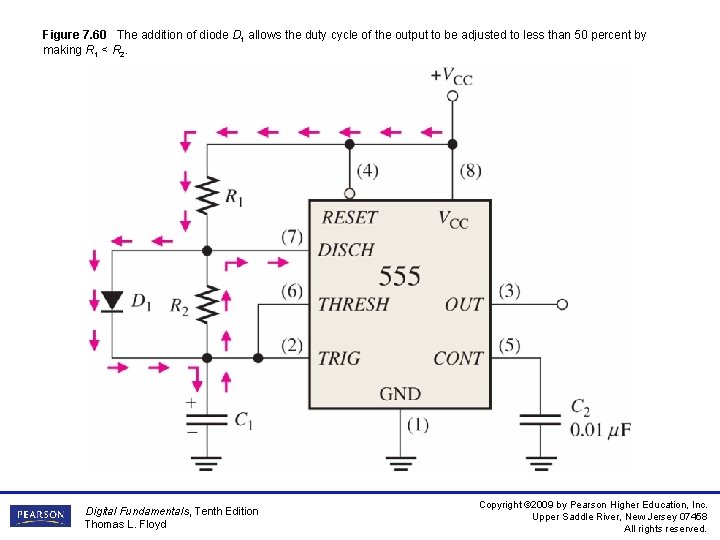

Figure 7. 60 The addition of diode D 1 allows the duty cycle of the output to be adjusted to less than 50 percent by making R 1 < R 2. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

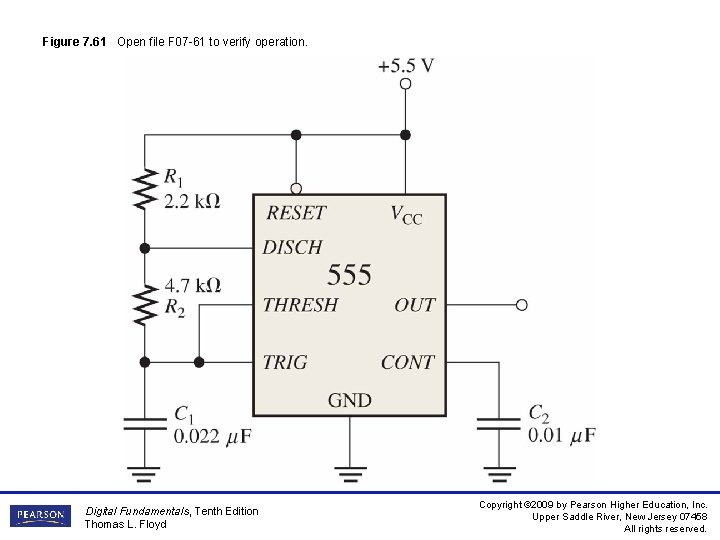

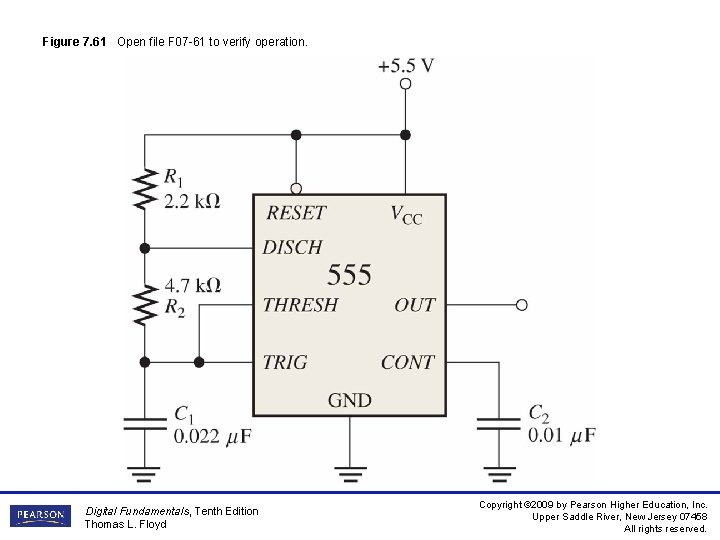

Figure 7. 61 Open file F 07 -61 to verify operation. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

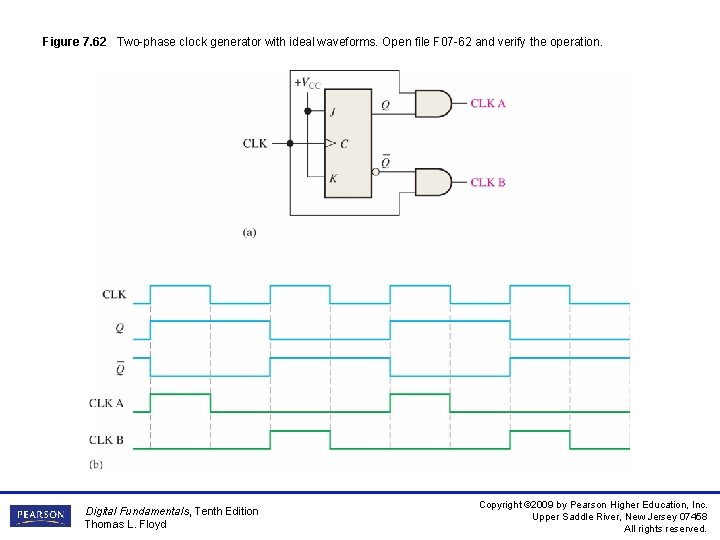

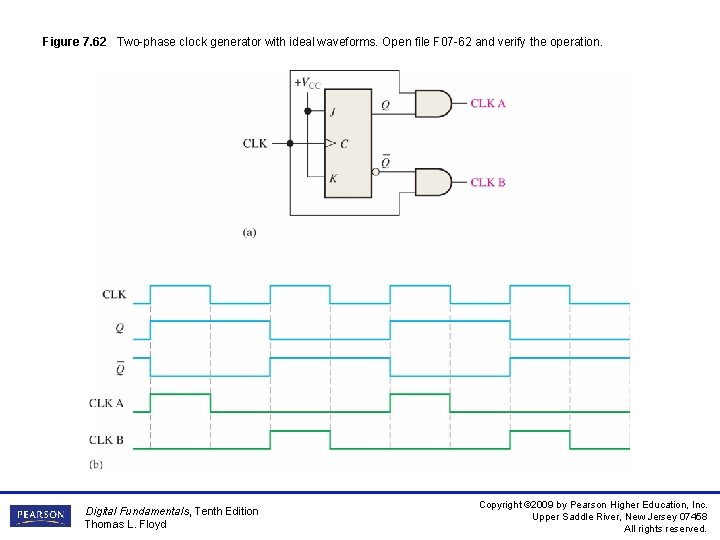

Figure 7. 62 Two-phase clock generator with ideal waveforms. Open file F 07 -62 and verify the operation. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

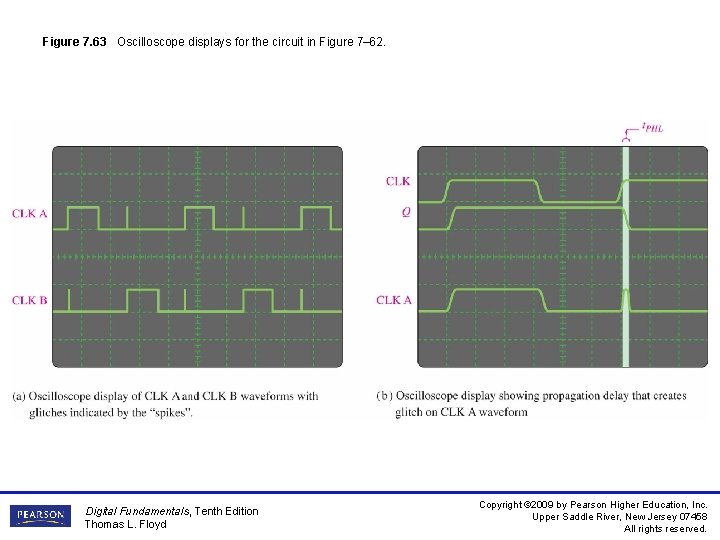

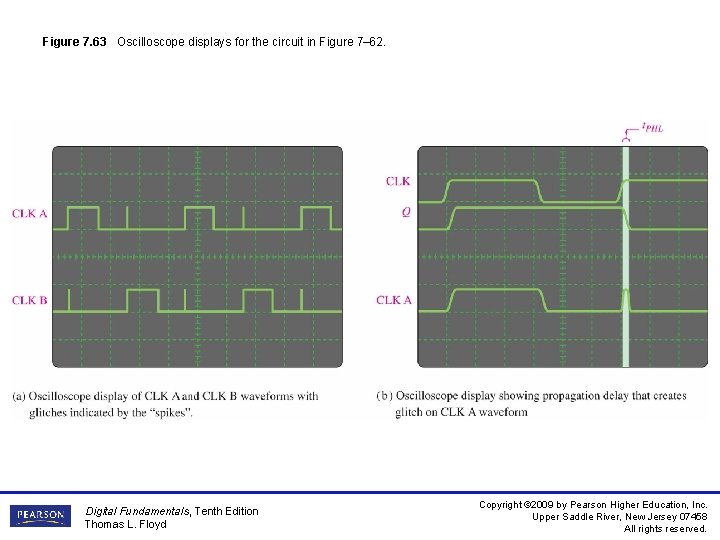

Figure 7. 63 Oscilloscope displays for the circuit in Figure 7– 62. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

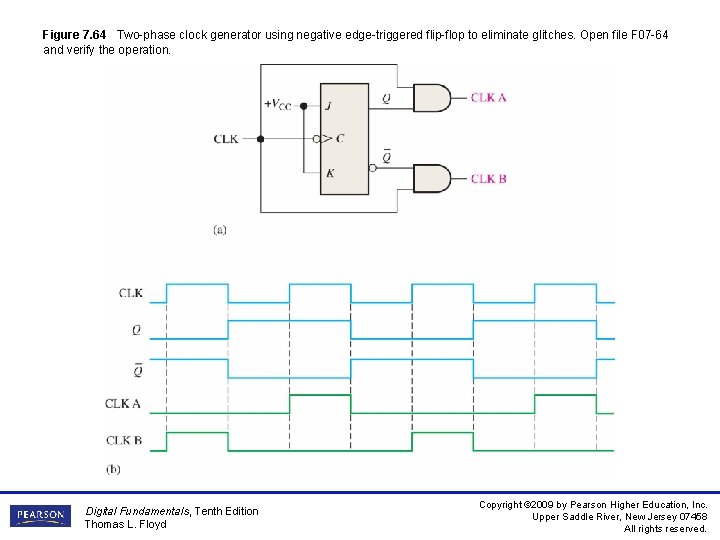

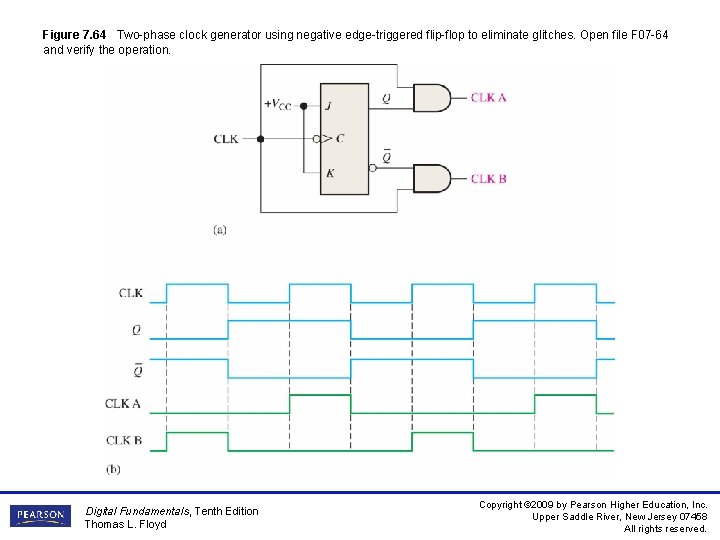

Figure 7. 64 Two-phase clock generator using negative edge-triggered flip-flop to eliminate glitches. Open file F 07 -64 and verify the operation. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 7. 65 Block diagram of the traffic signal control system. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

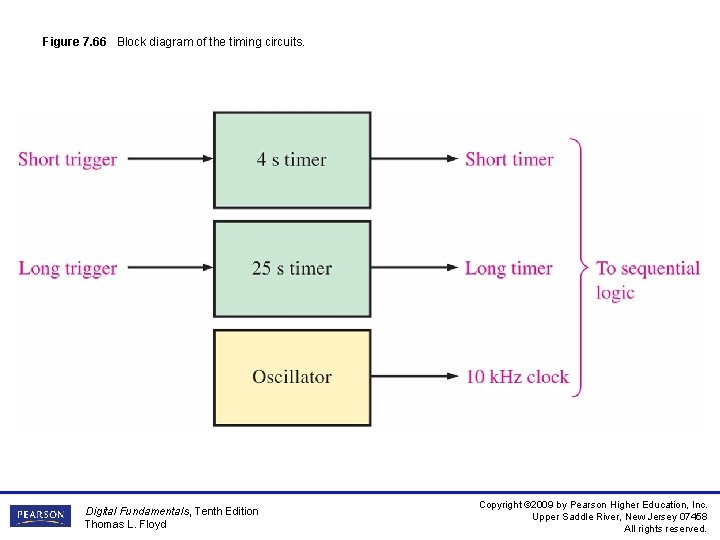

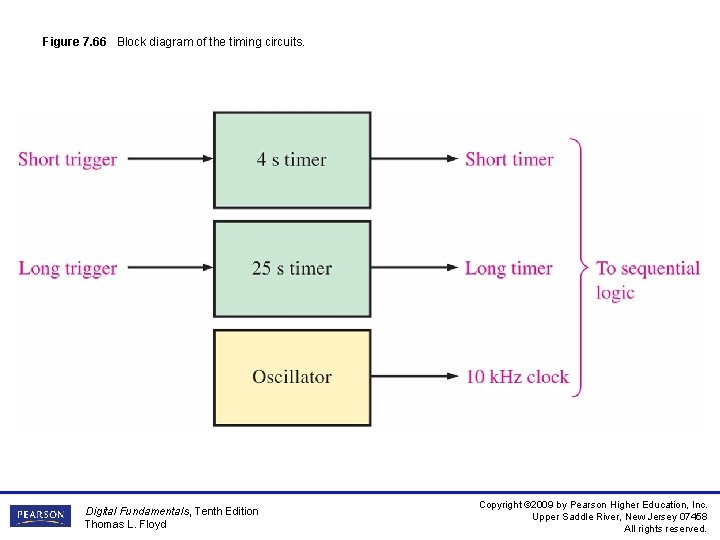

Figure 7. 66 Block diagram of the timing circuits. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

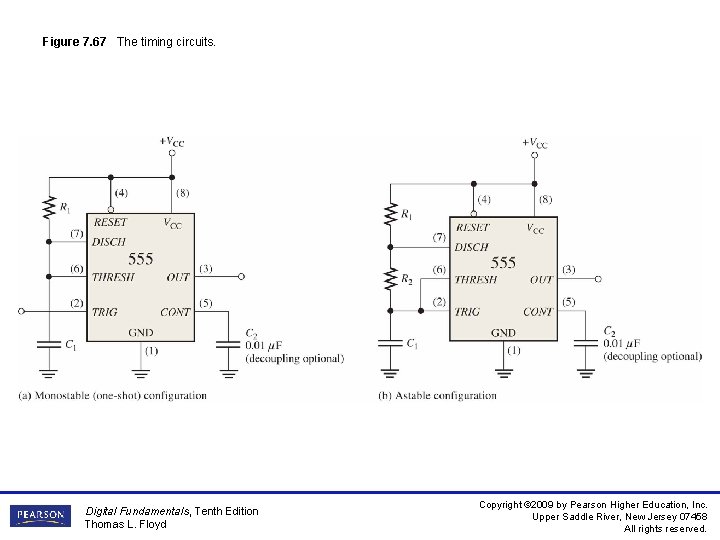

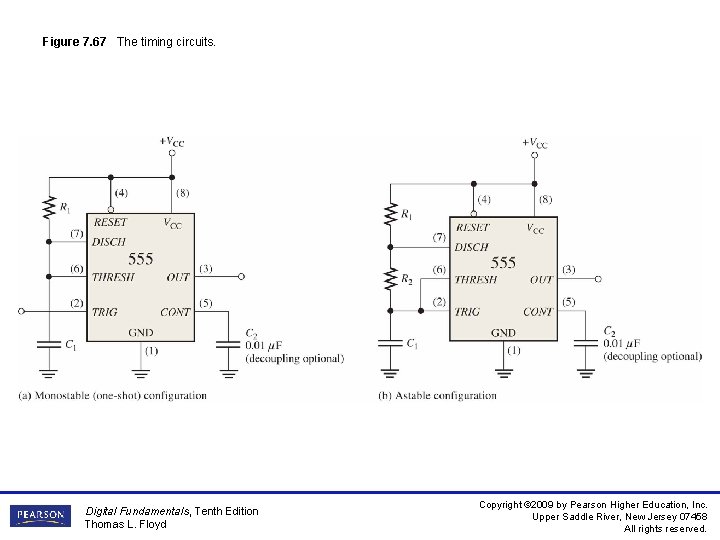

Figure 7. 67 The timing circuits. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 7. 68 Multisim screen for the timing circuits. The switches are for test purposes only. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

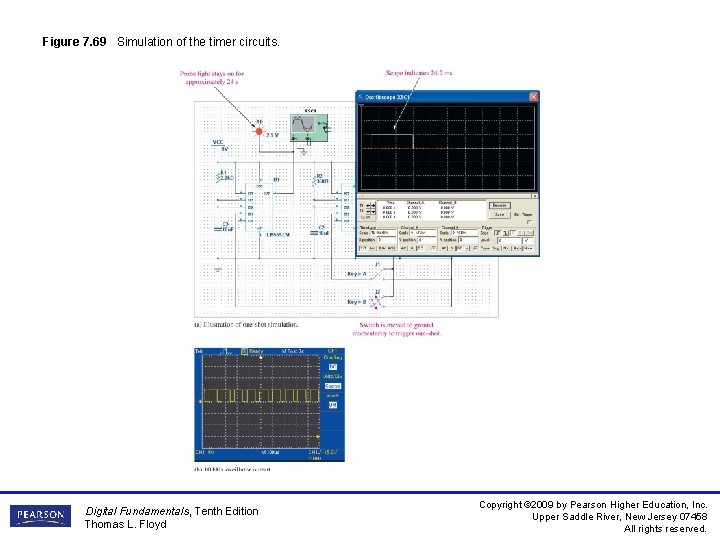

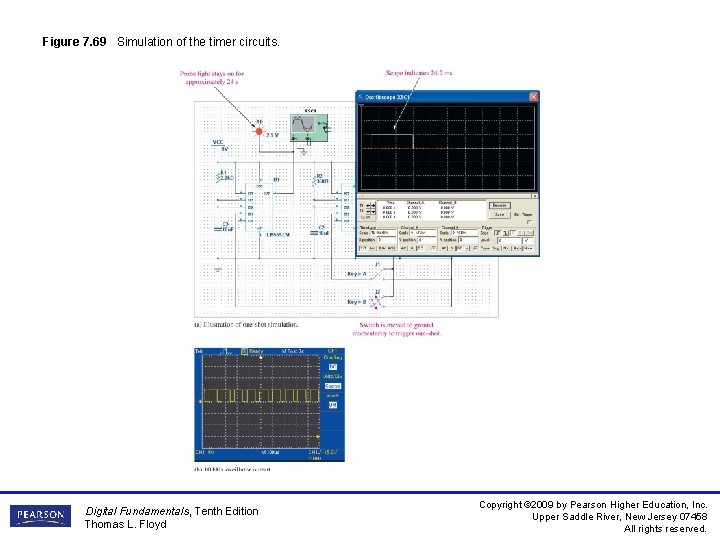

Figure 7. 69 Simulation of the timer circuits. Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

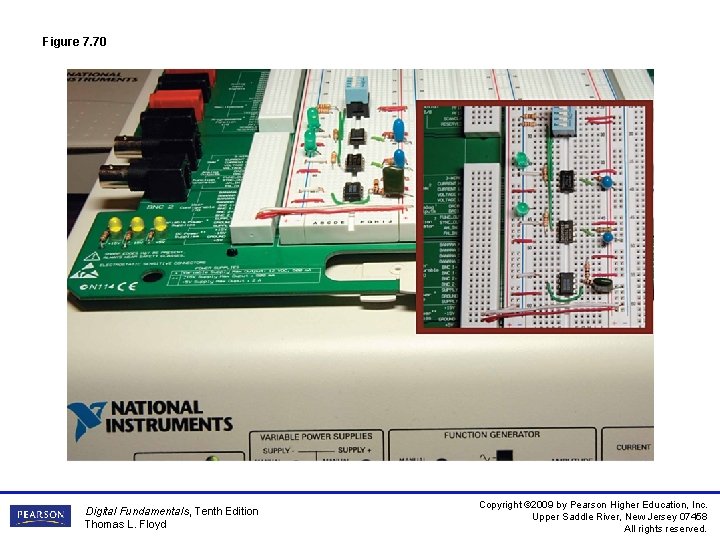

Figure 7. 70 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

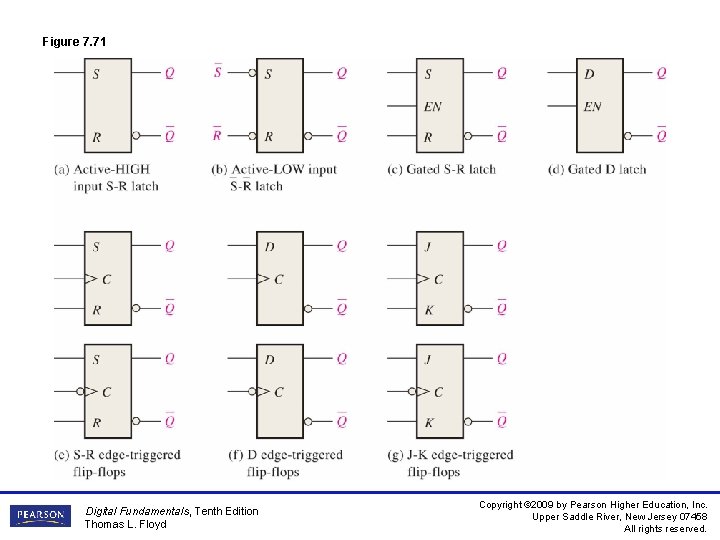

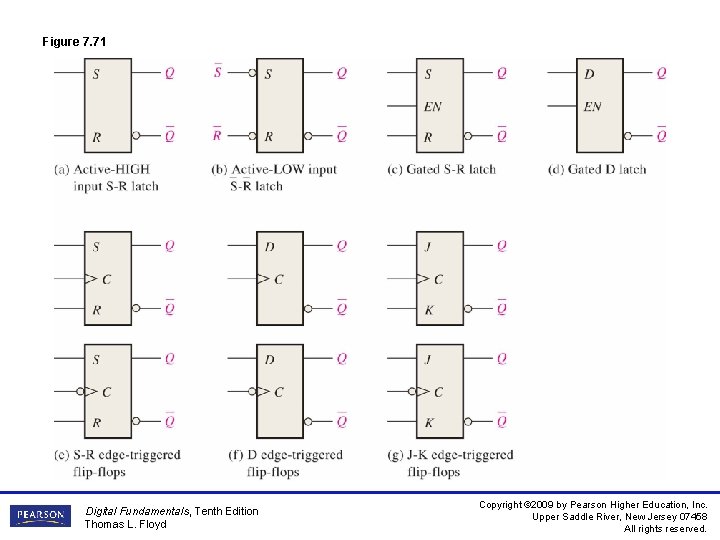

Figure 7. 71 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

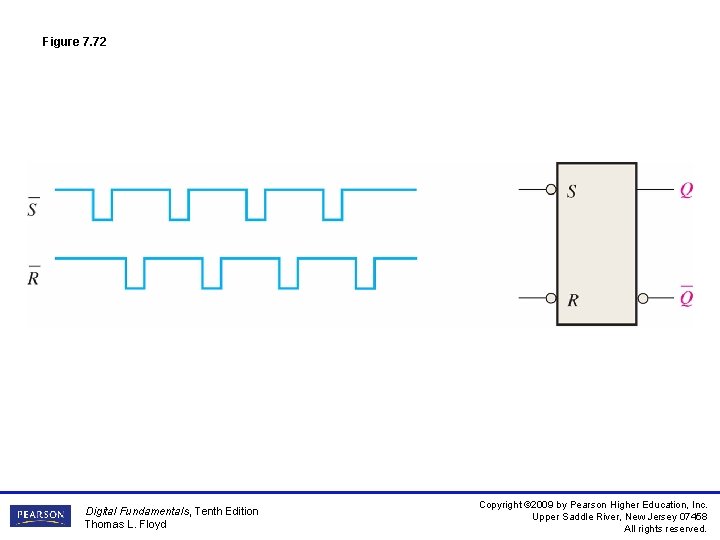

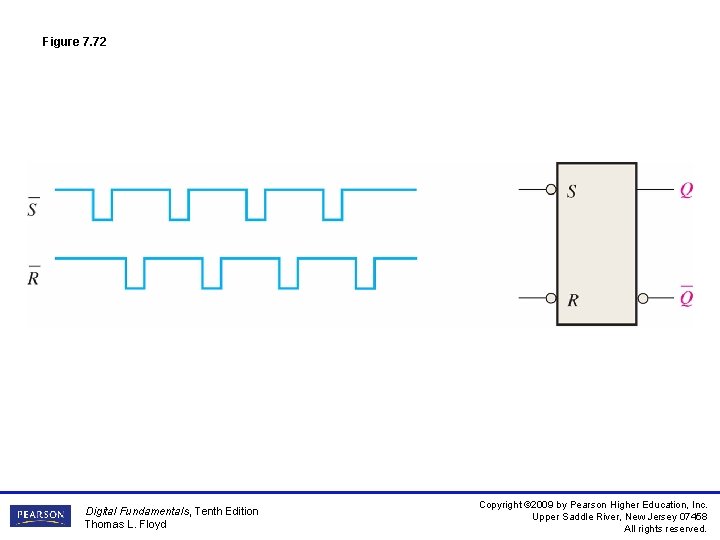

Figure 7. 72 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

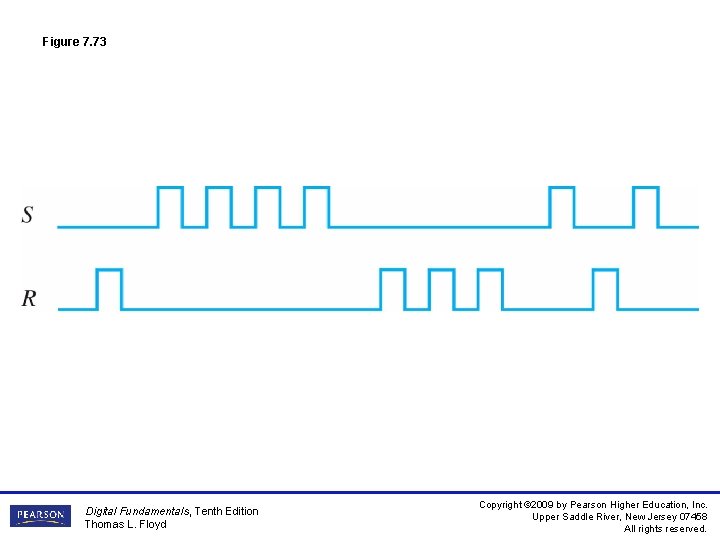

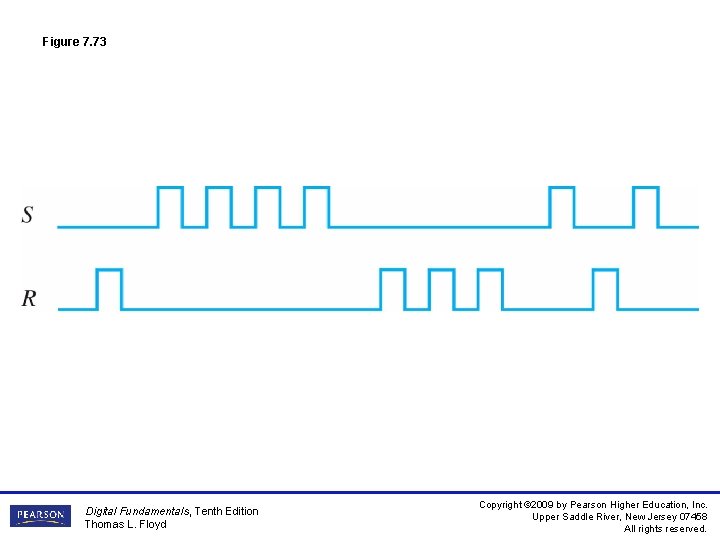

Figure 7. 73 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

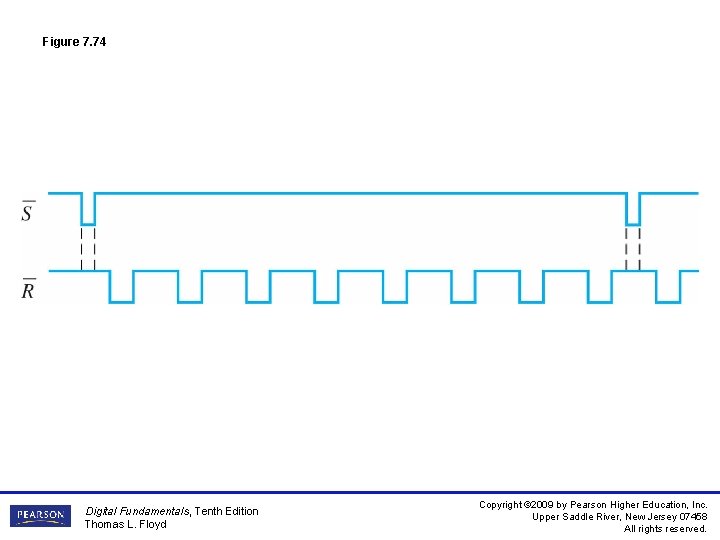

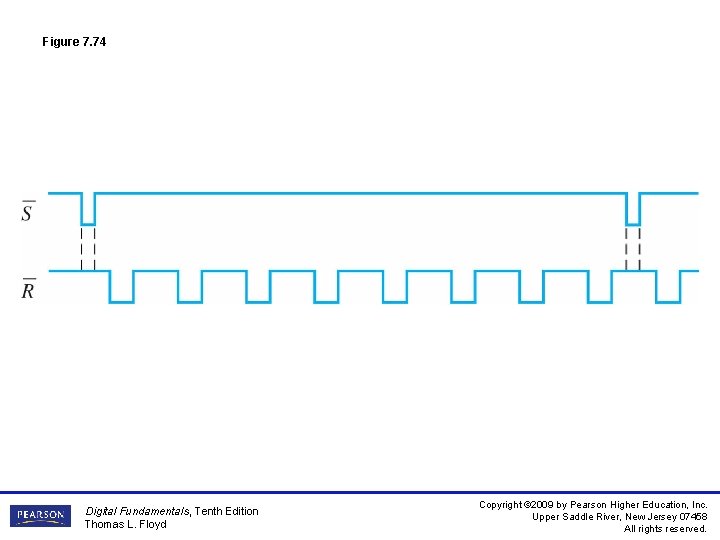

Figure 7. 74 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

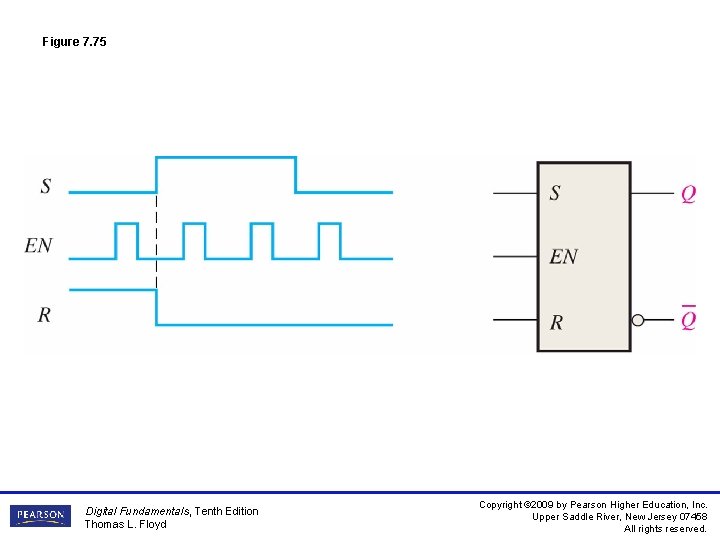

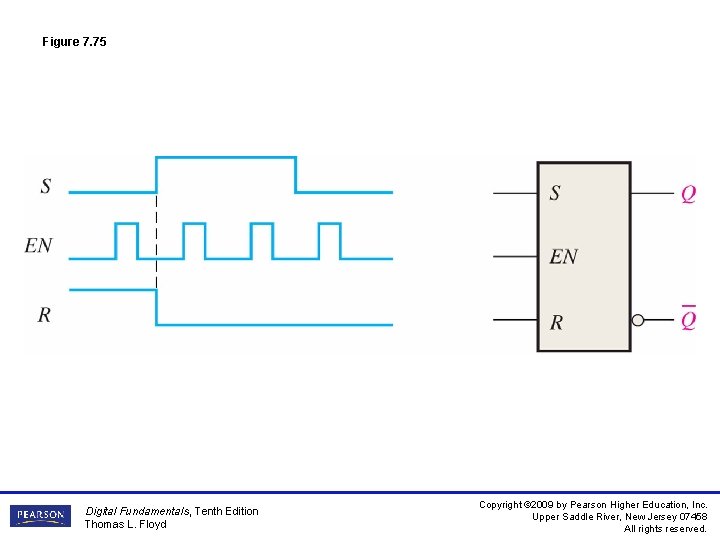

Figure 7. 75 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

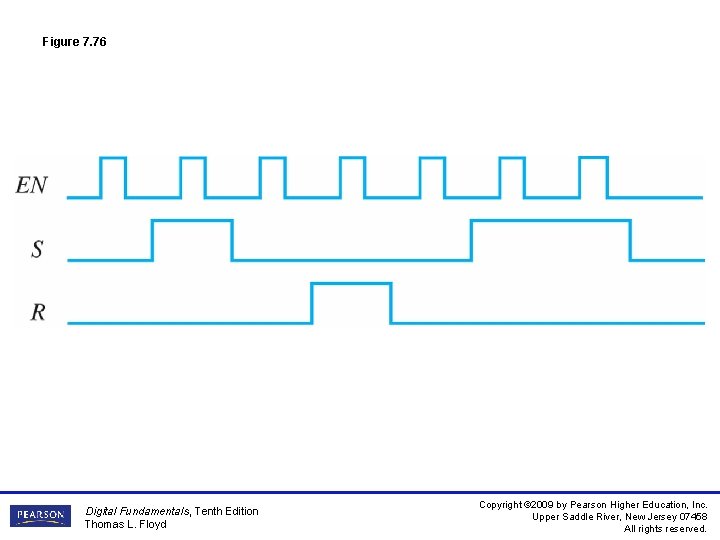

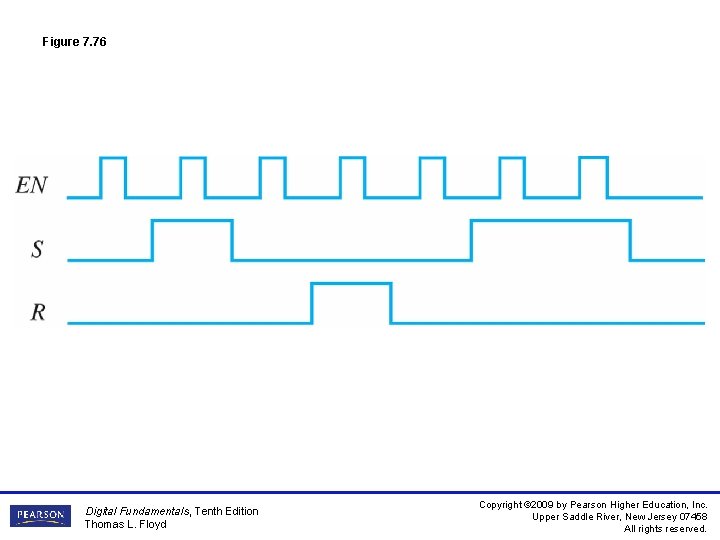

Figure 7. 76 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

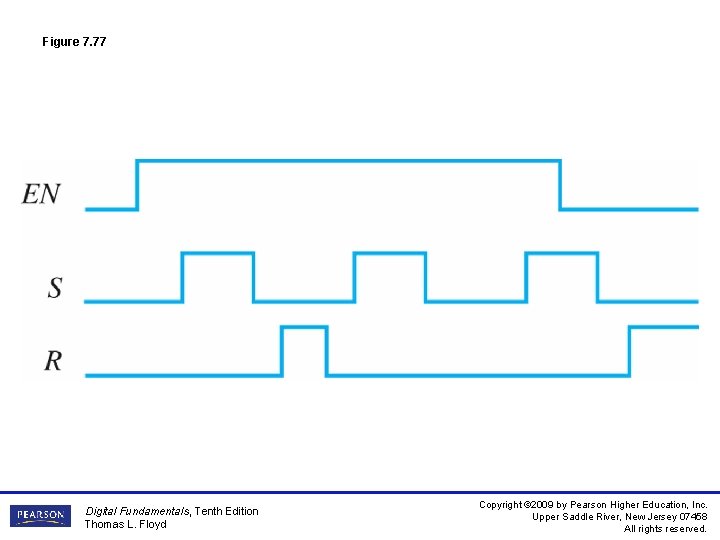

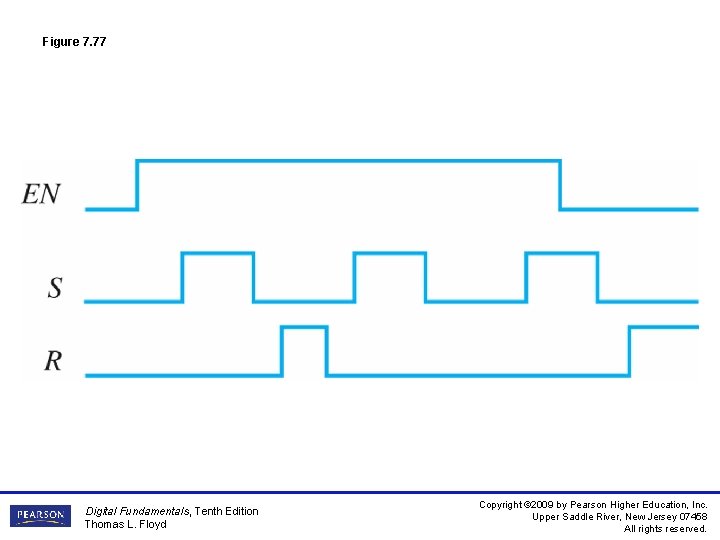

Figure 7. 77 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

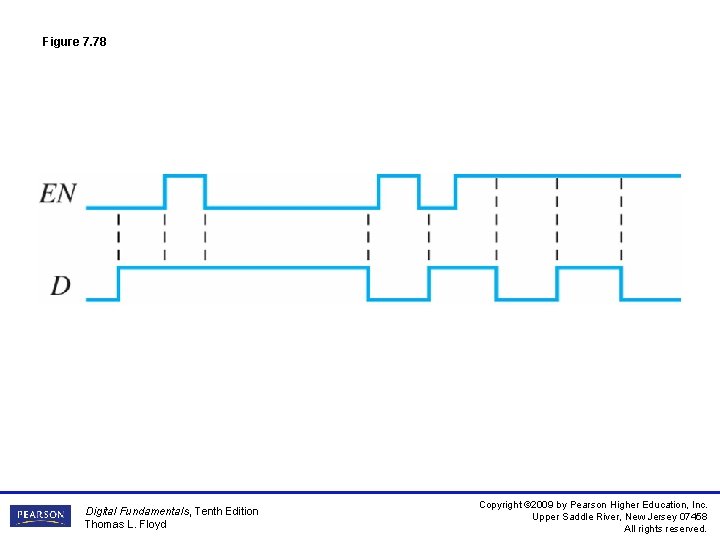

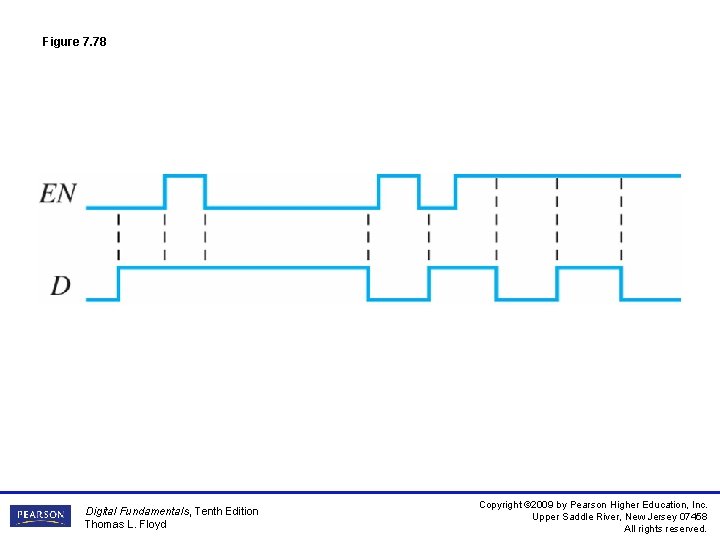

Figure 7. 78 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

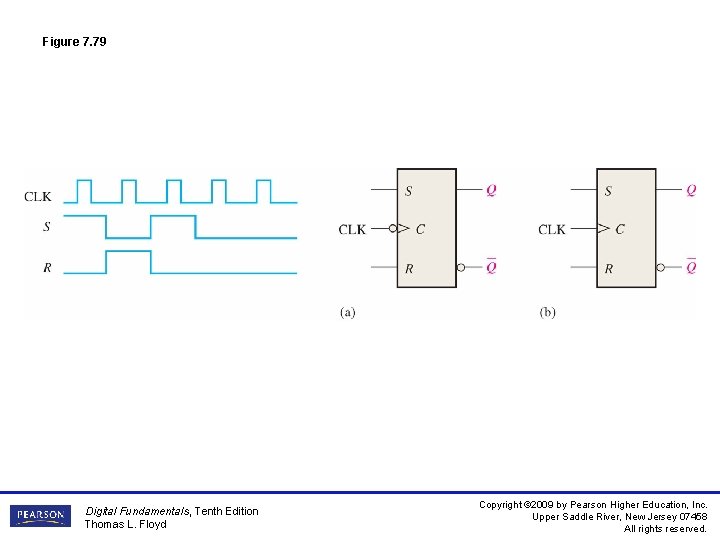

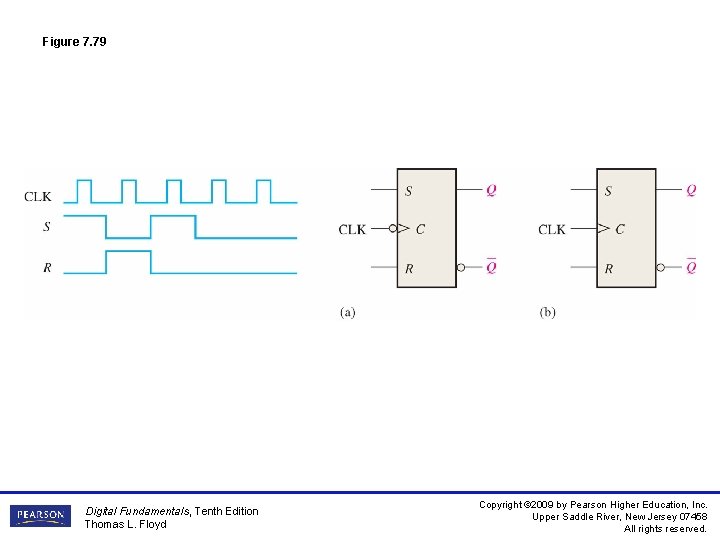

Figure 7. 79 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

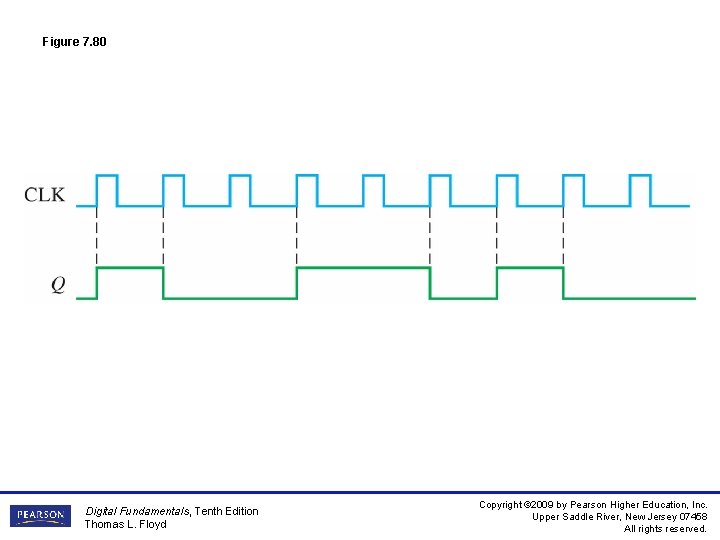

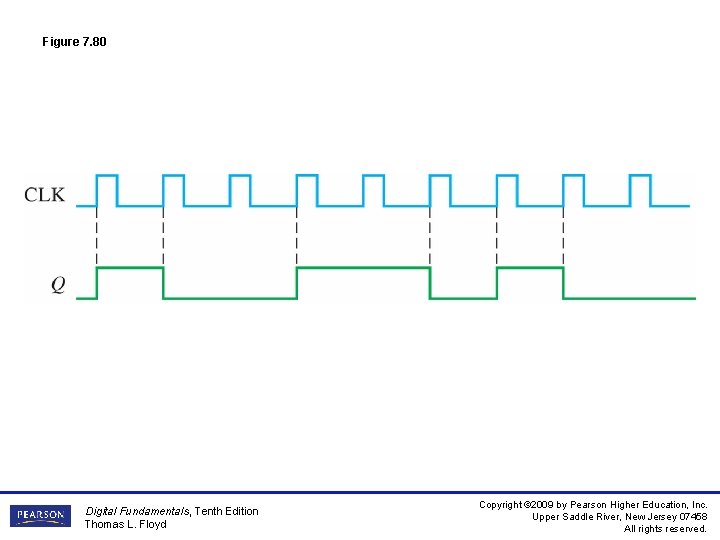

Figure 7. 80 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

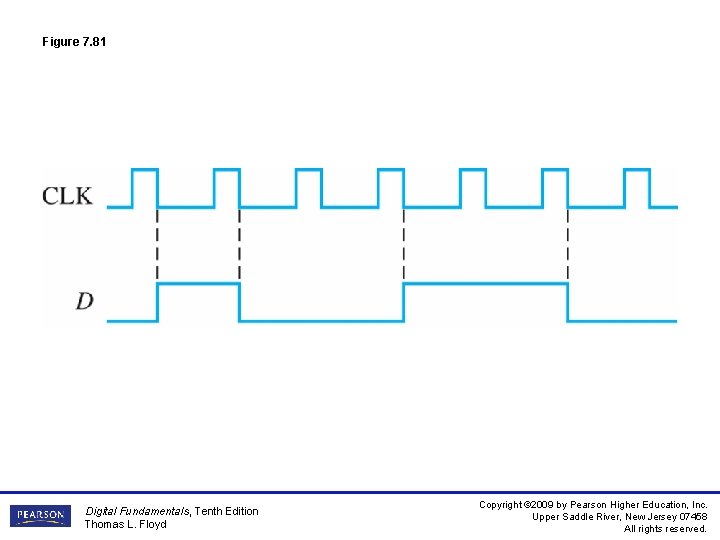

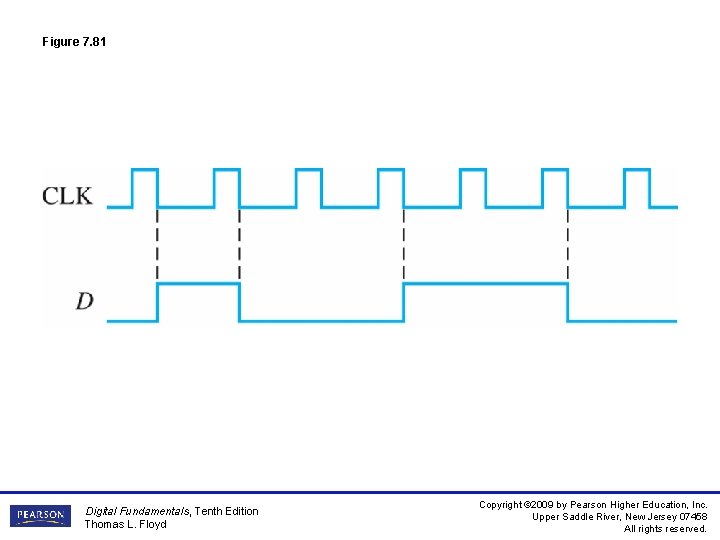

Figure 7. 81 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

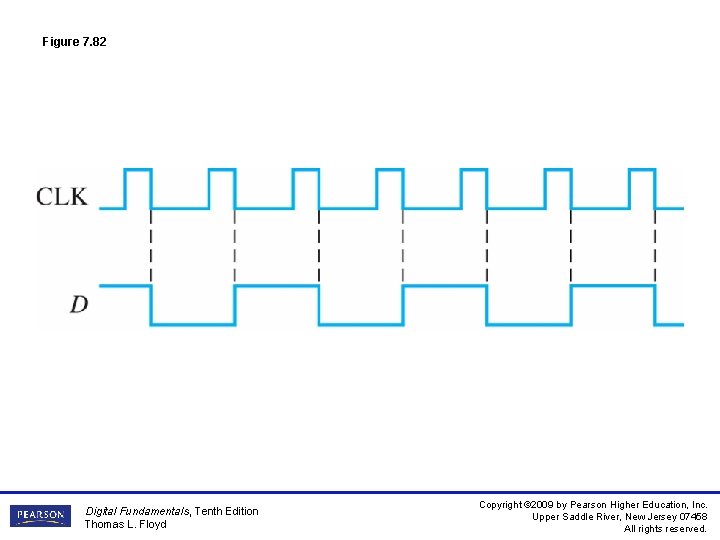

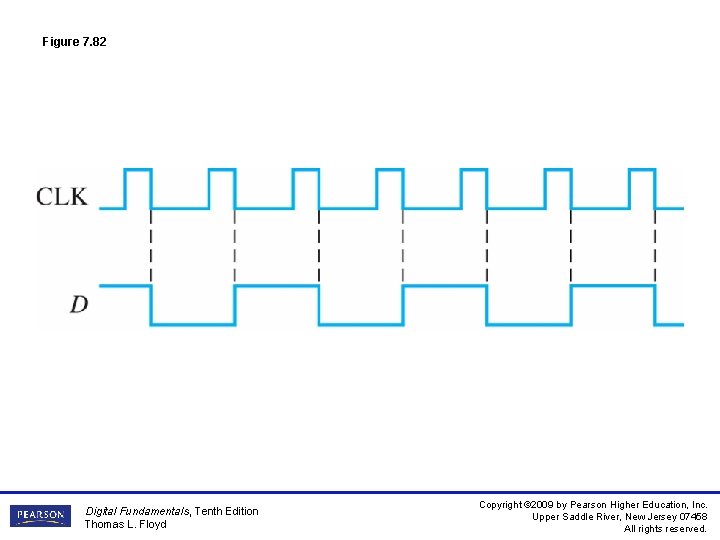

Figure 7. 82 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

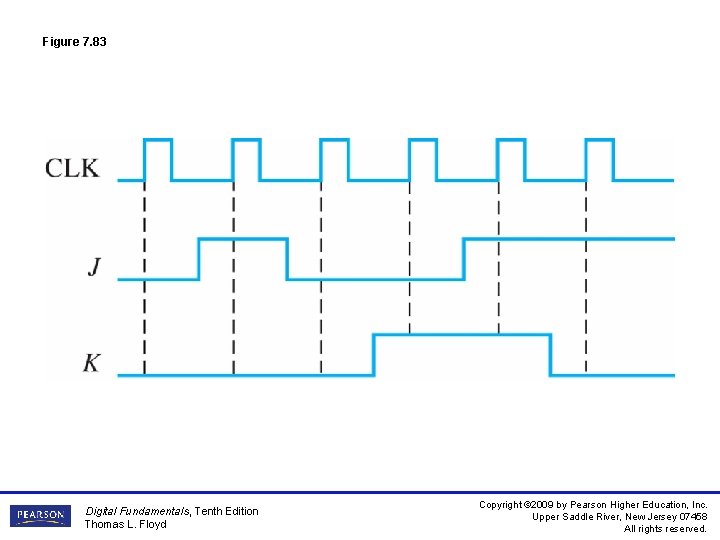

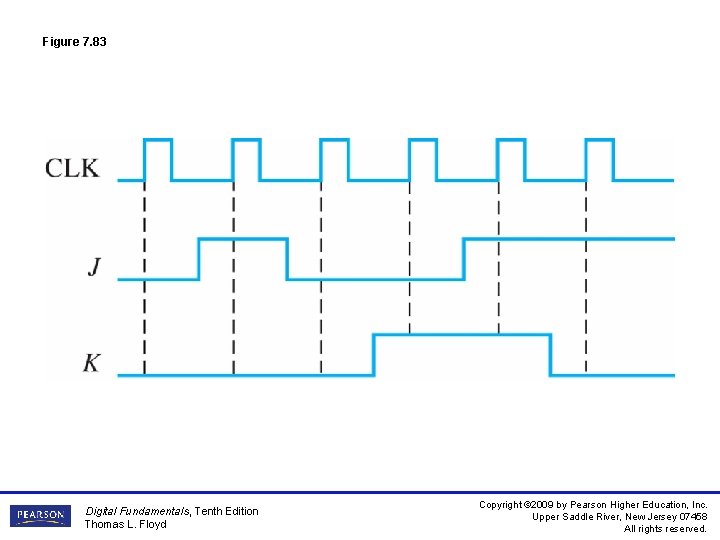

Figure 7. 83 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

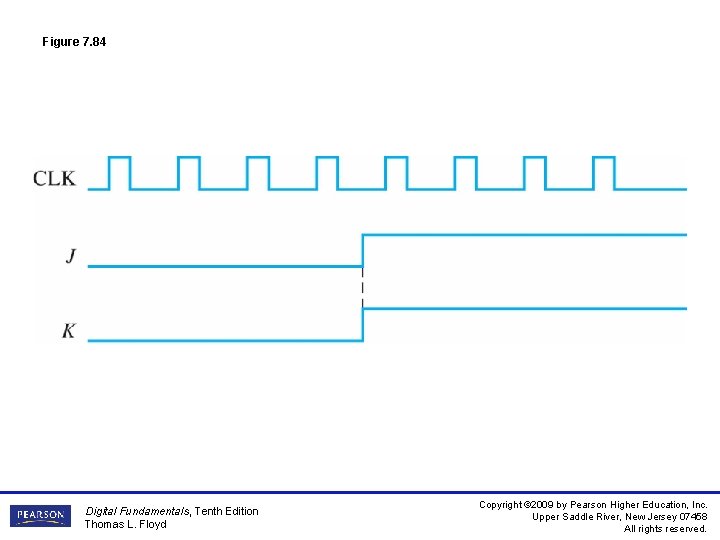

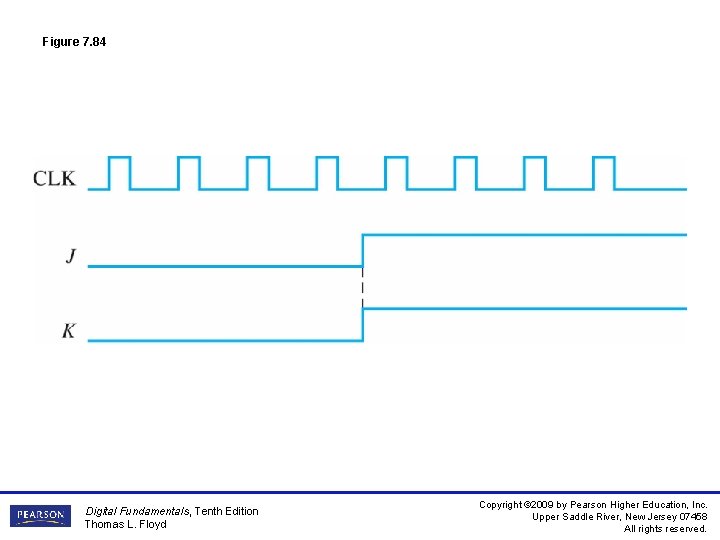

Figure 7. 84 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

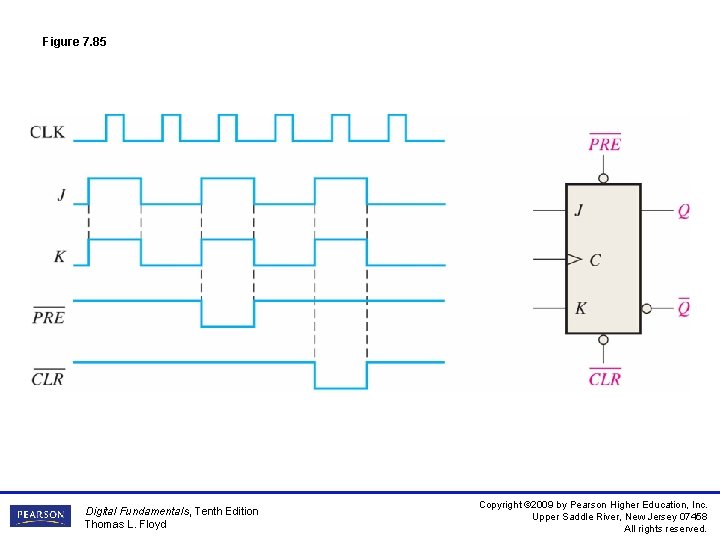

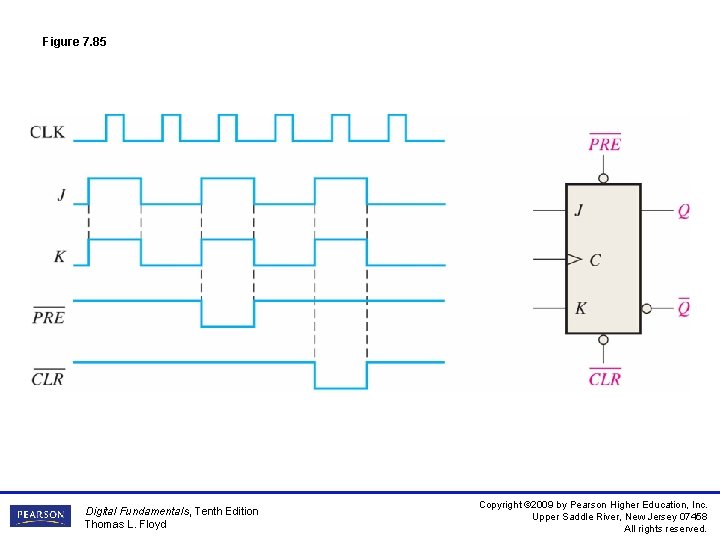

Figure 7. 85 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

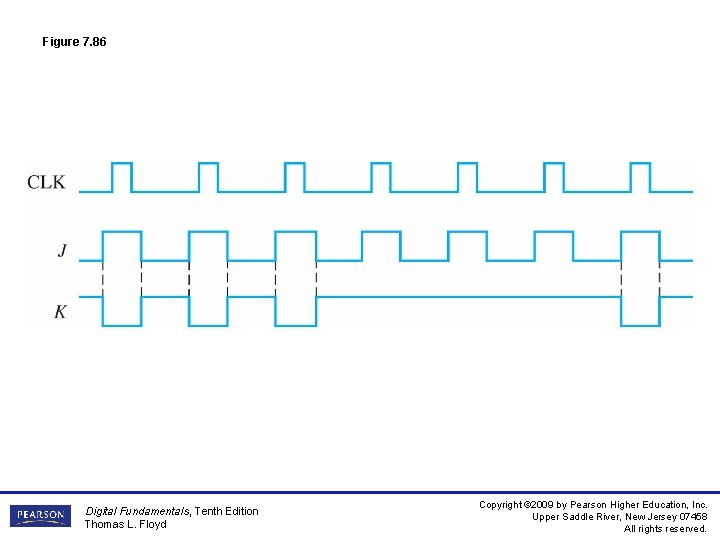

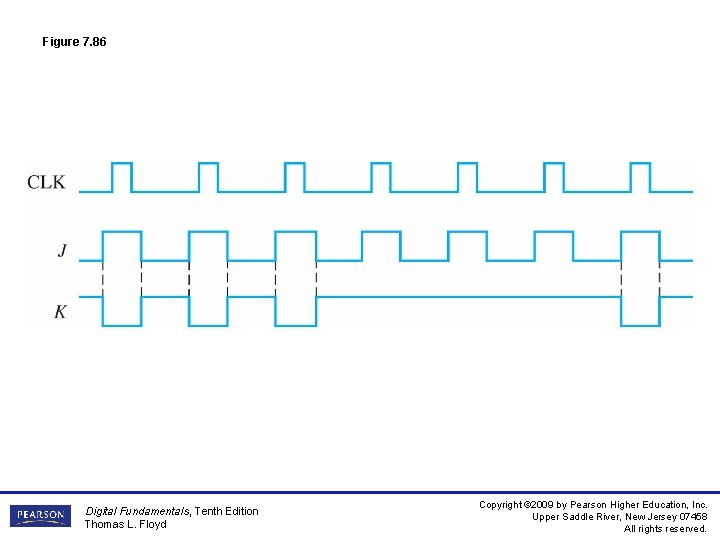

Figure 7. 86 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

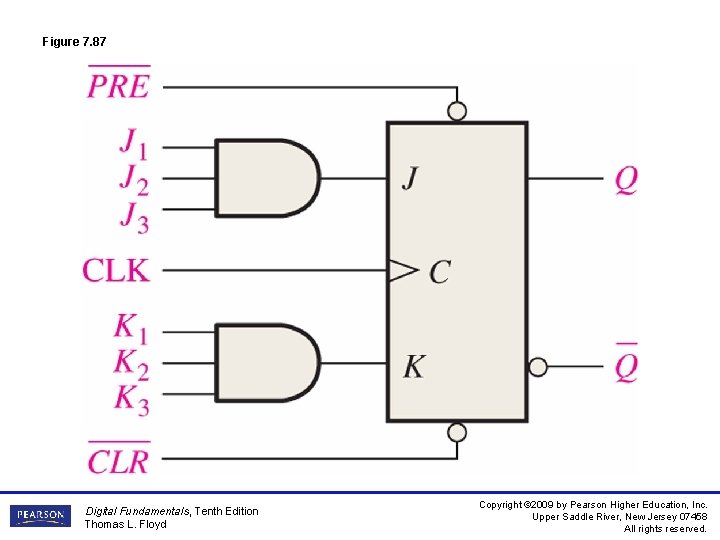

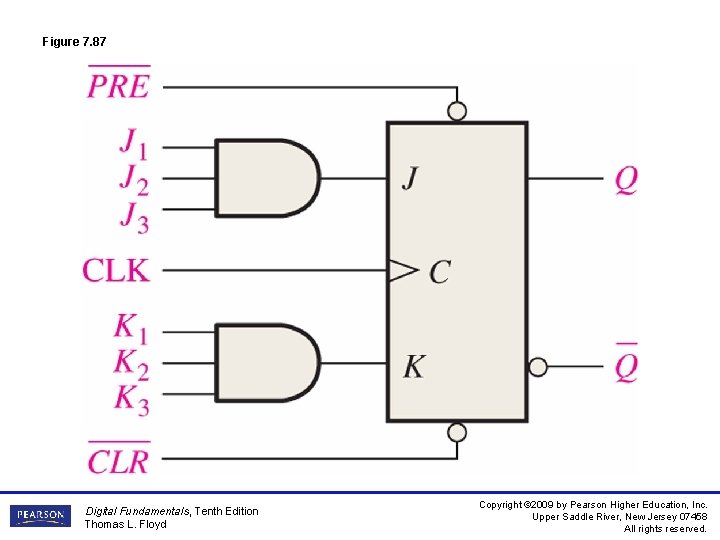

Figure 7. 87 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

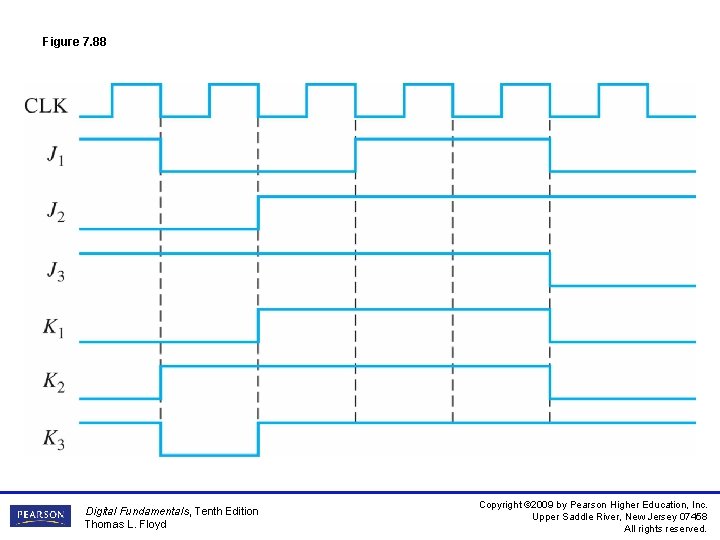

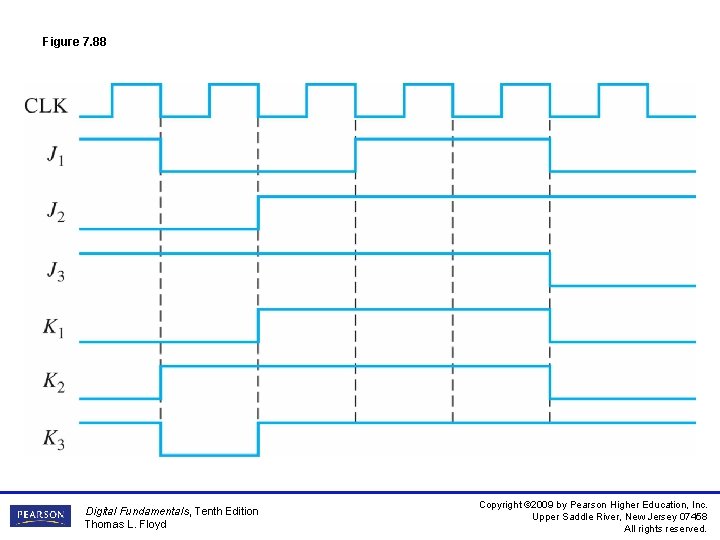

Figure 7. 88 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

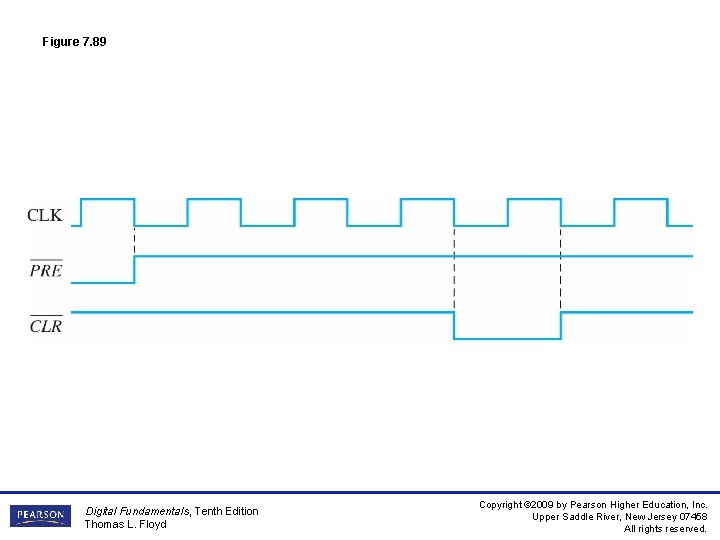

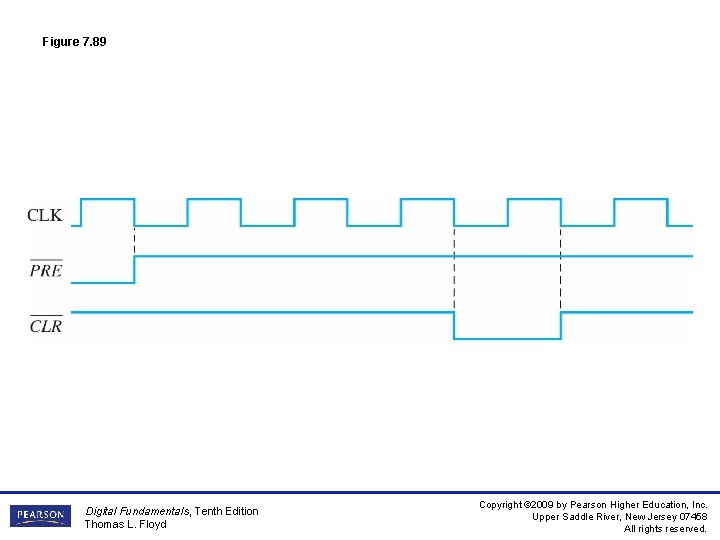

Figure 7. 89 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

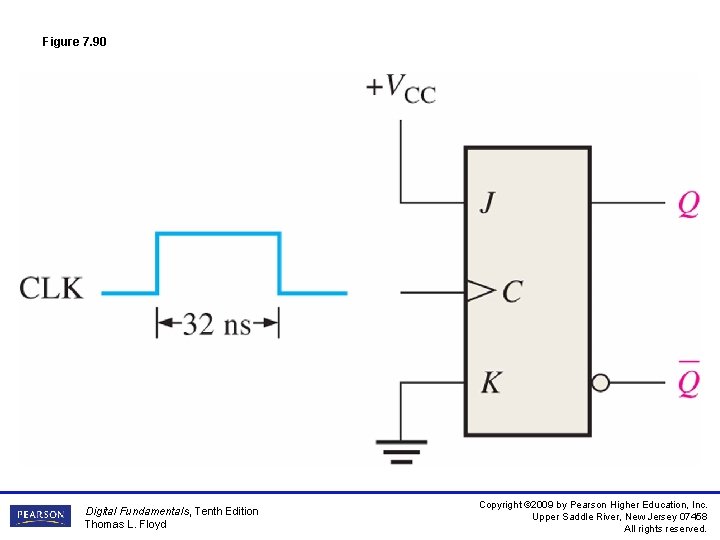

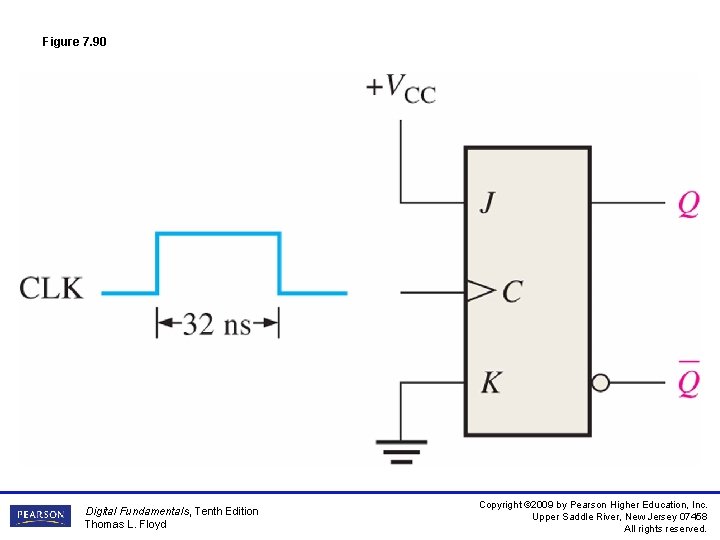

Figure 7. 90 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

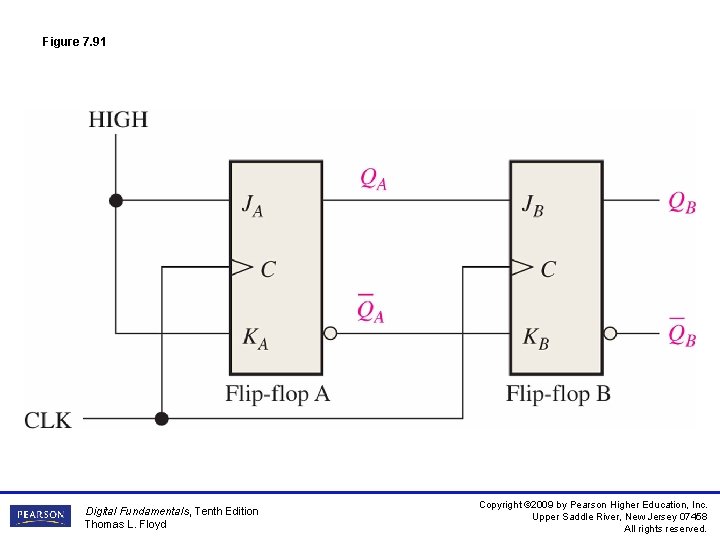

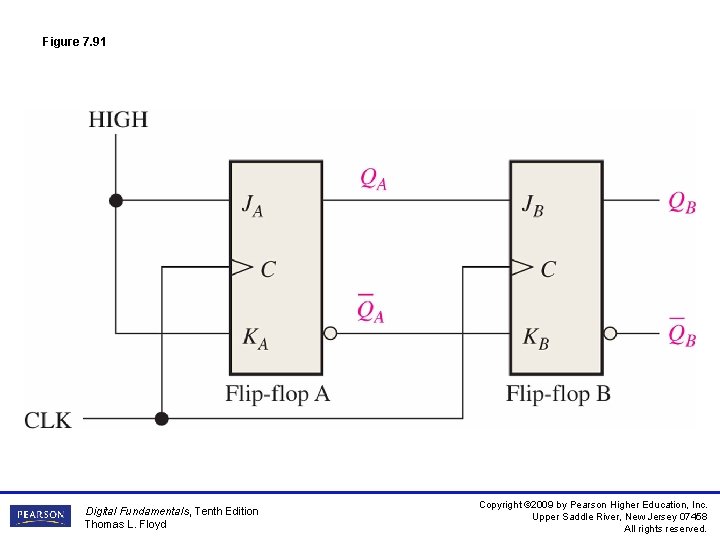

Figure 7. 91 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

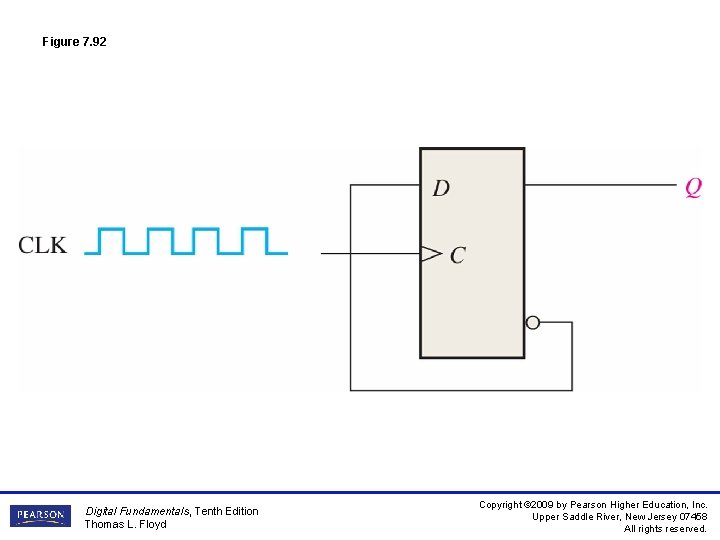

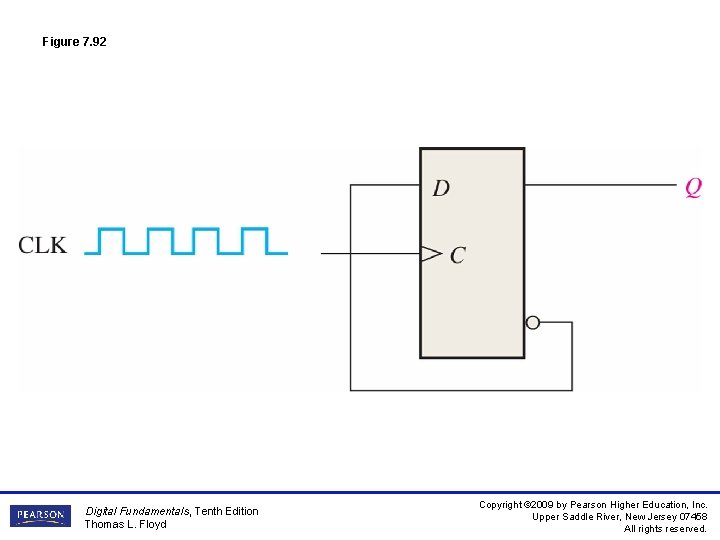

Figure 7. 92 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

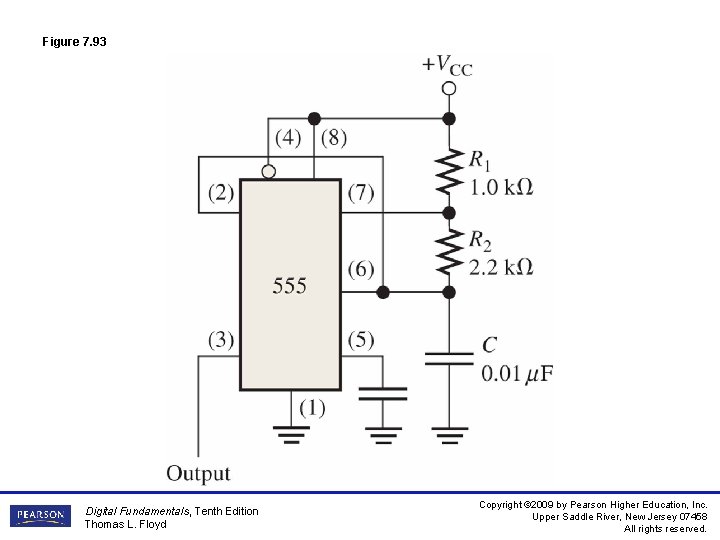

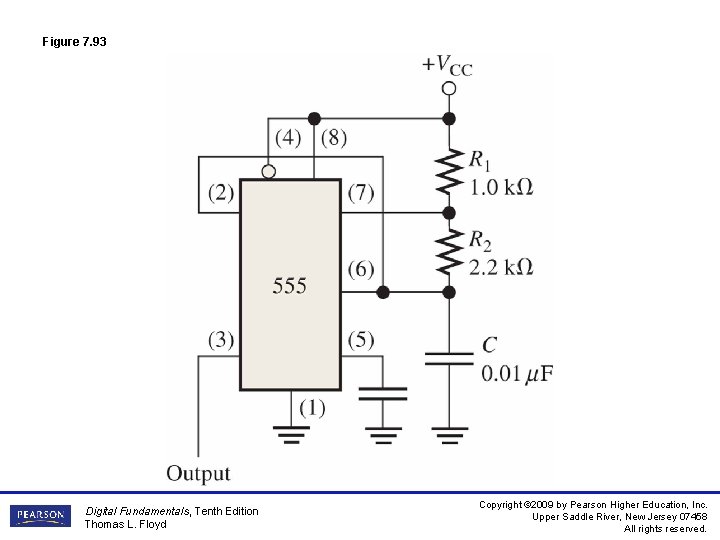

Figure 7. 93 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

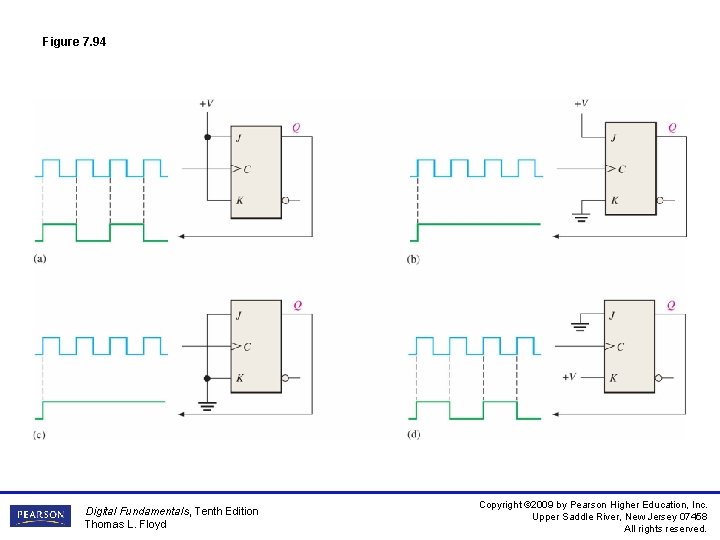

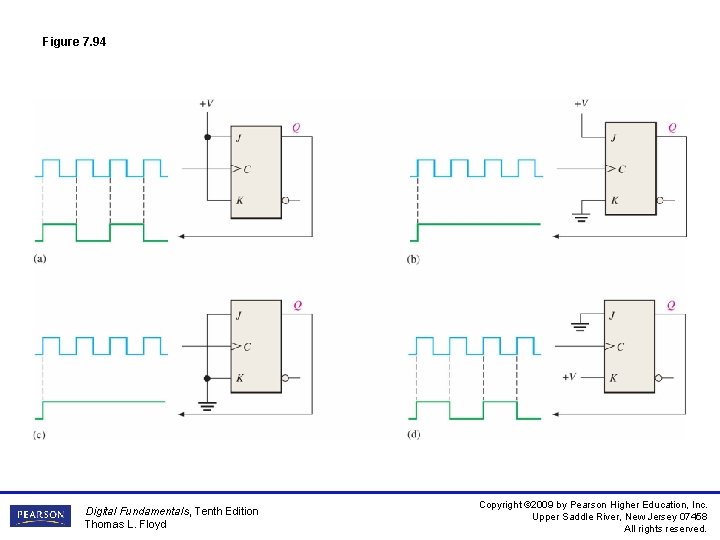

Figure 7. 94 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

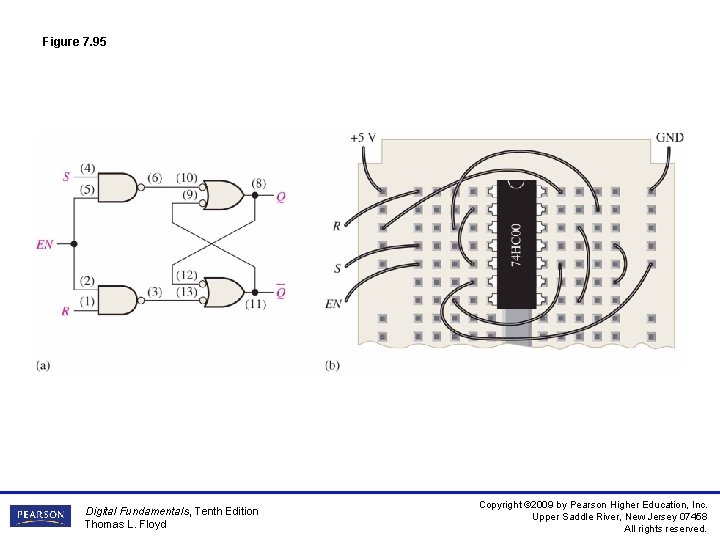

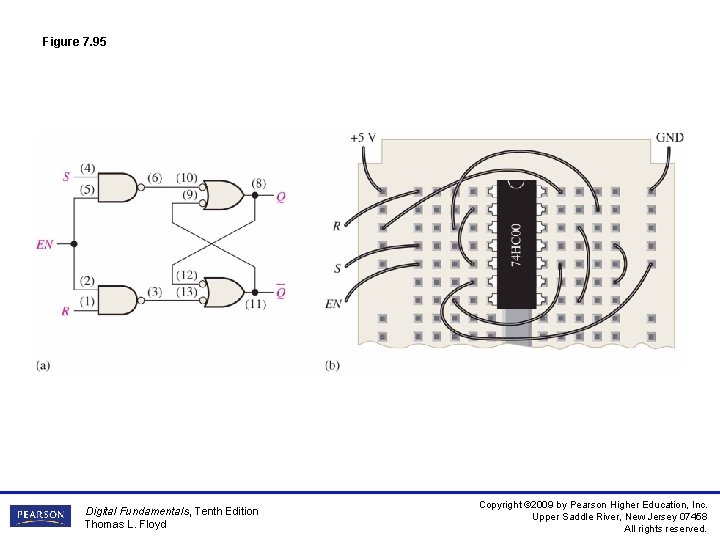

Figure 7. 95 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

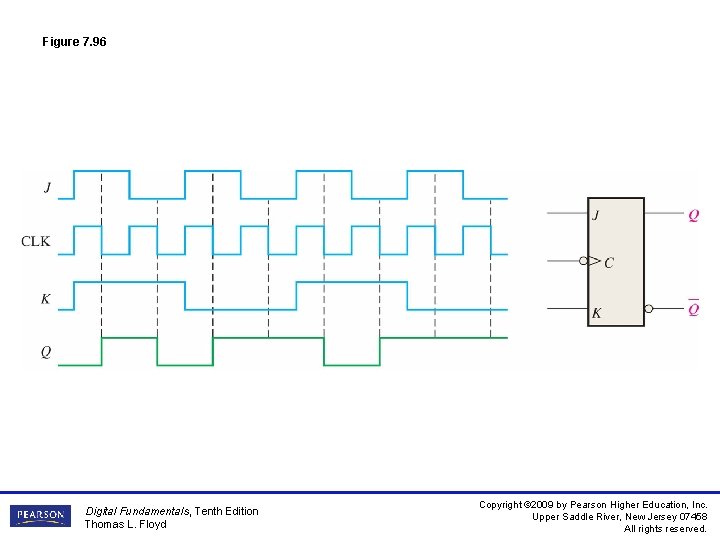

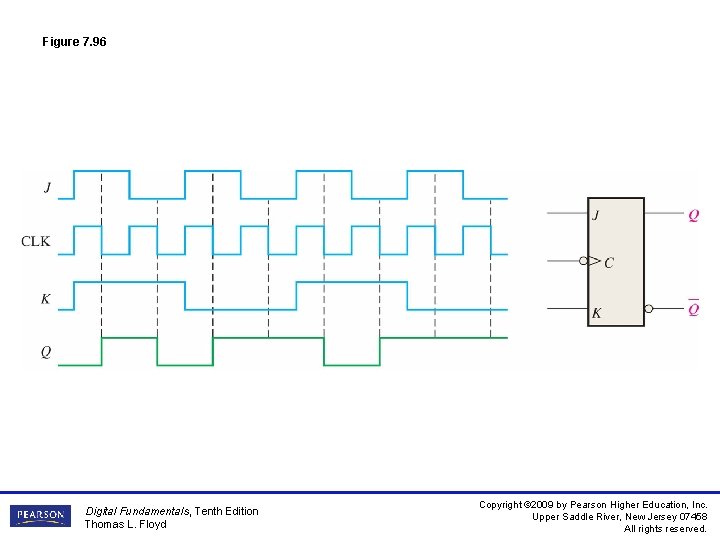

Figure 7. 96 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

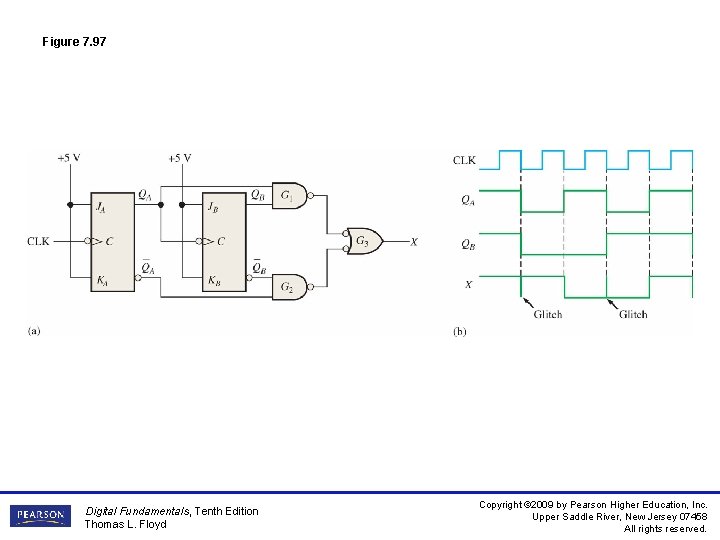

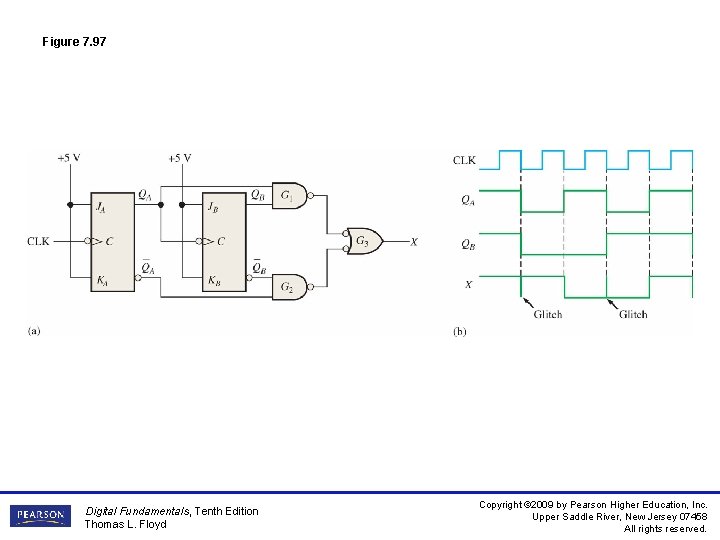

Figure 7. 97 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

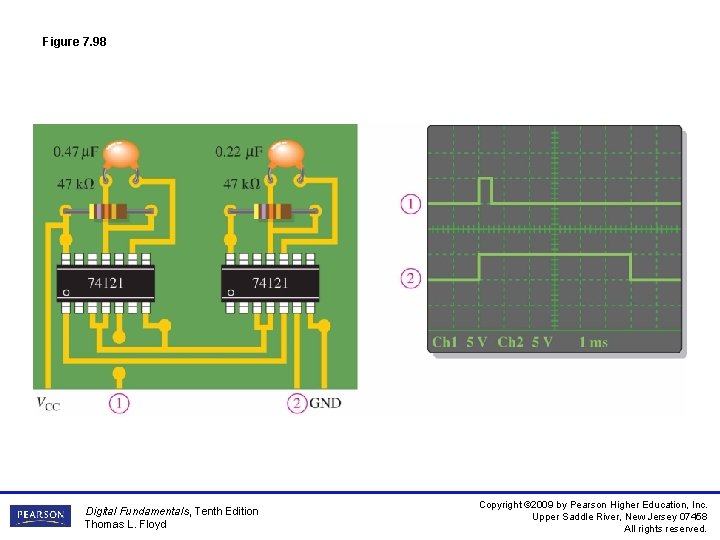

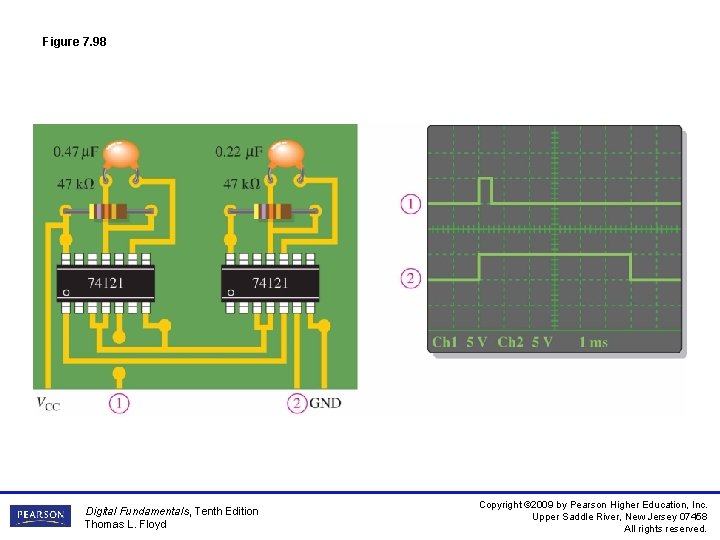

Figure 7. 98 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

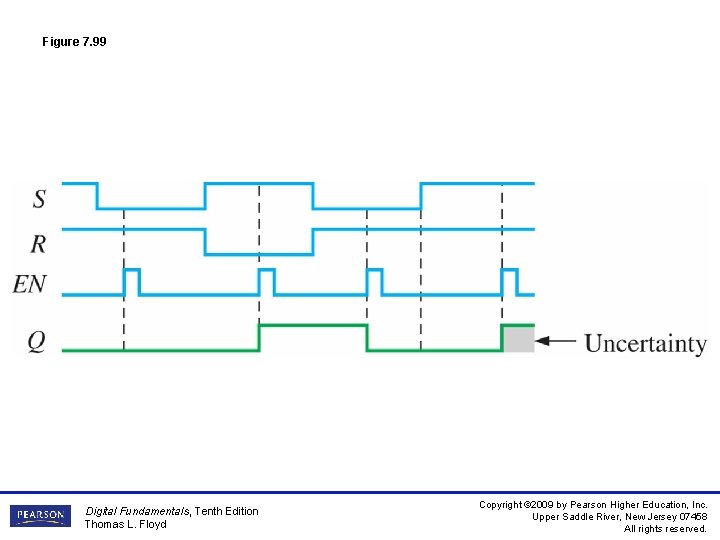

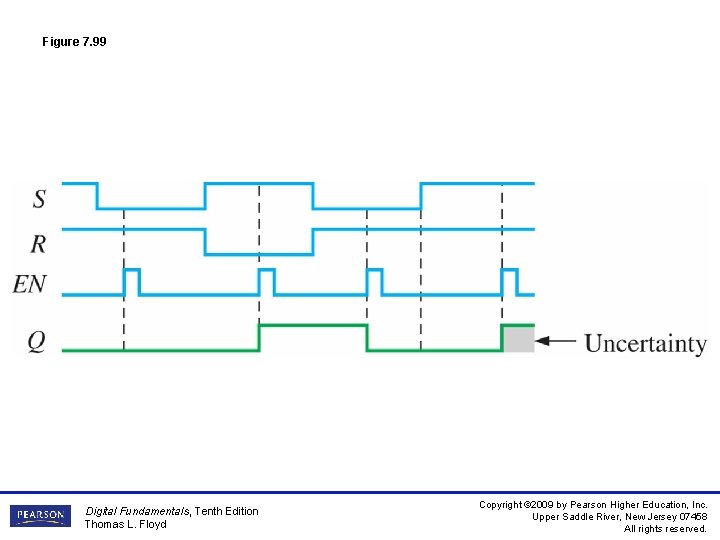

Figure 7. 99 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

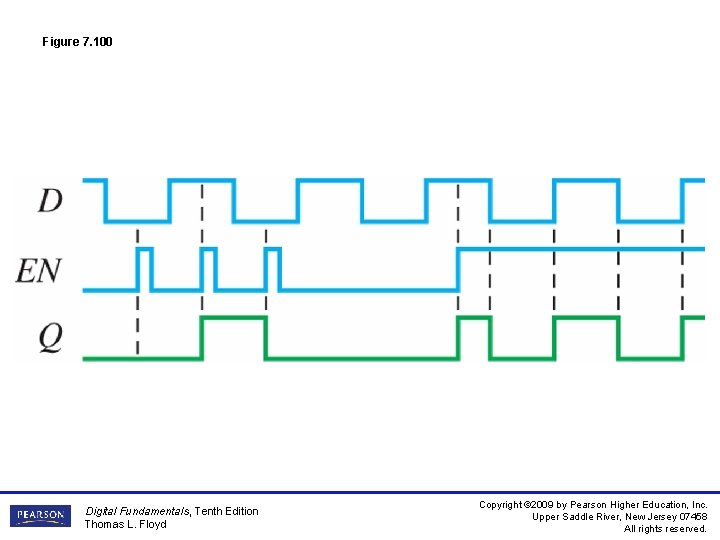

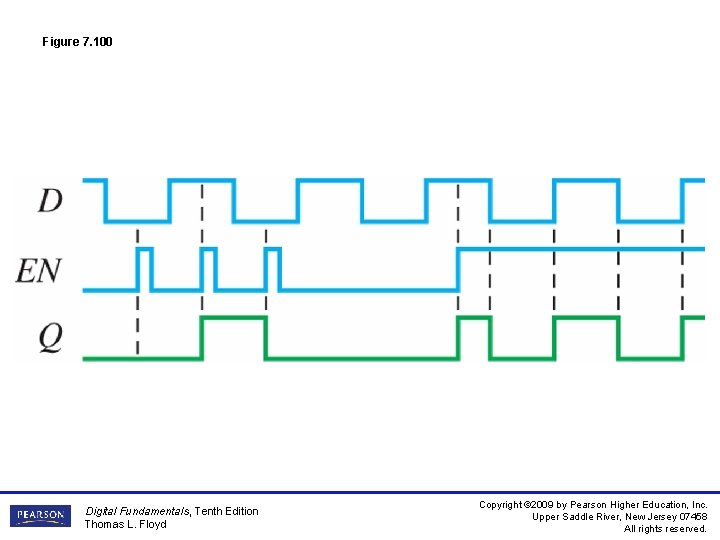

Figure 7. 100 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

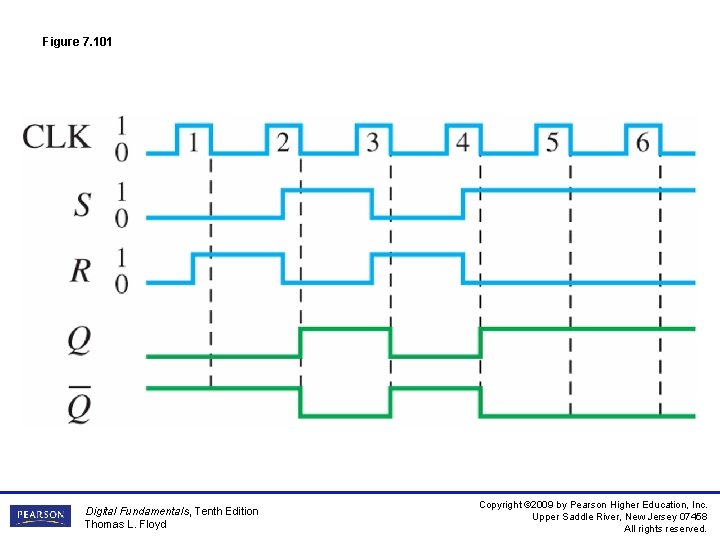

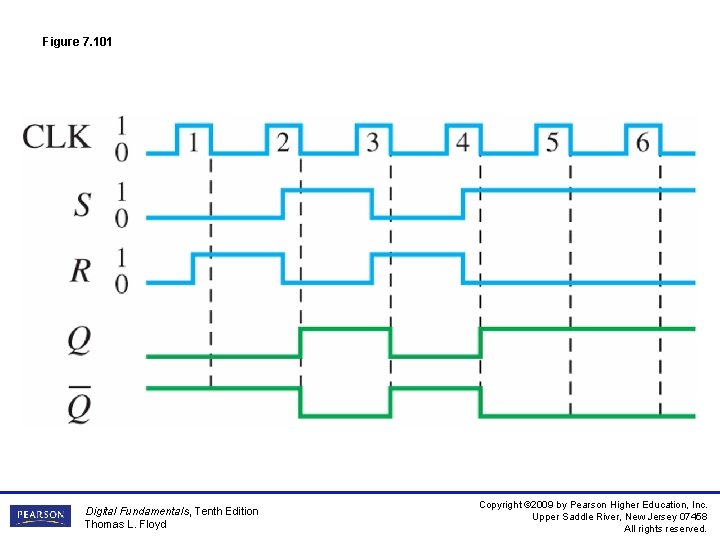

Figure 7. 101 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

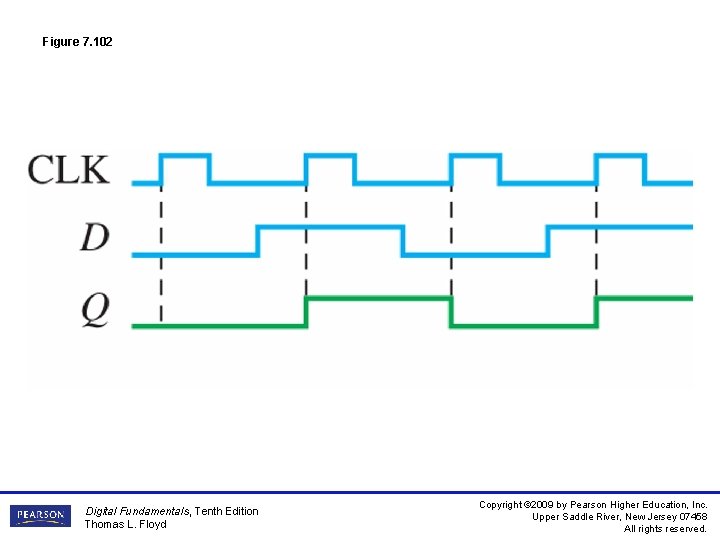

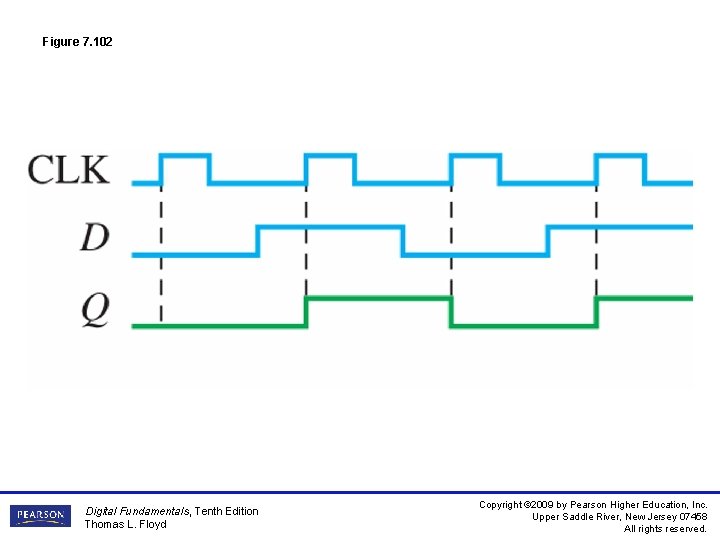

Figure 7. 102 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

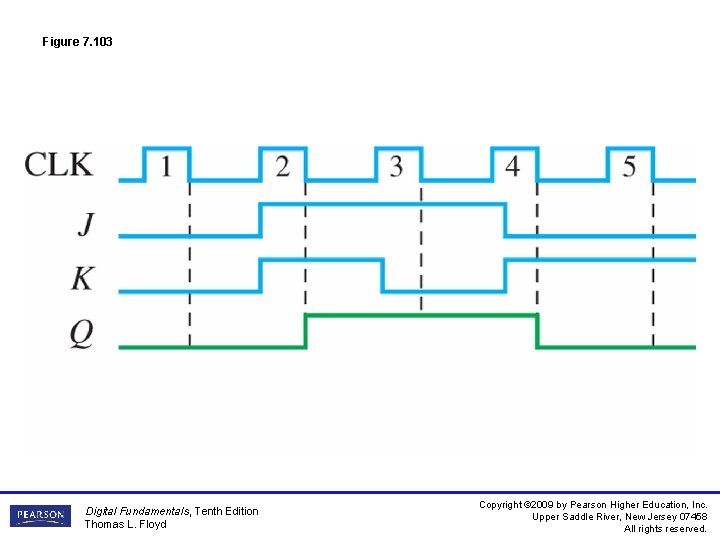

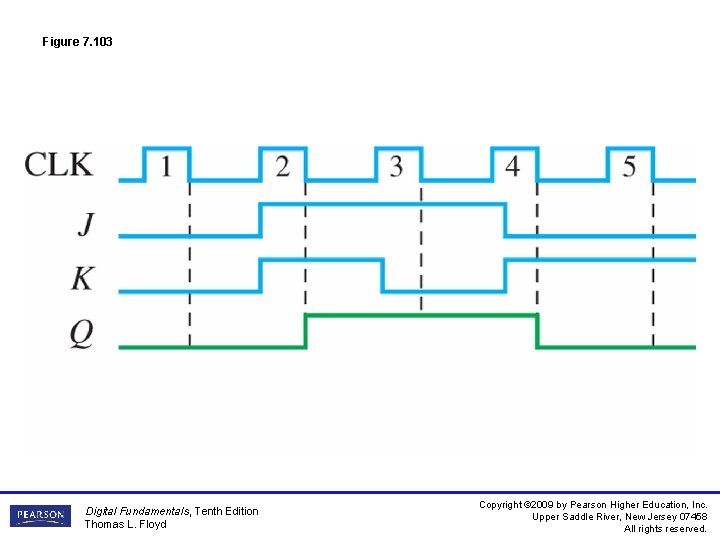

Figure 7. 103 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

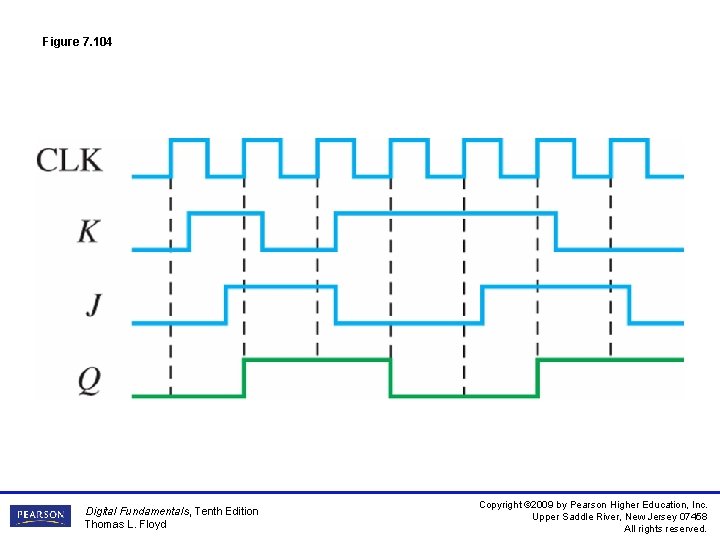

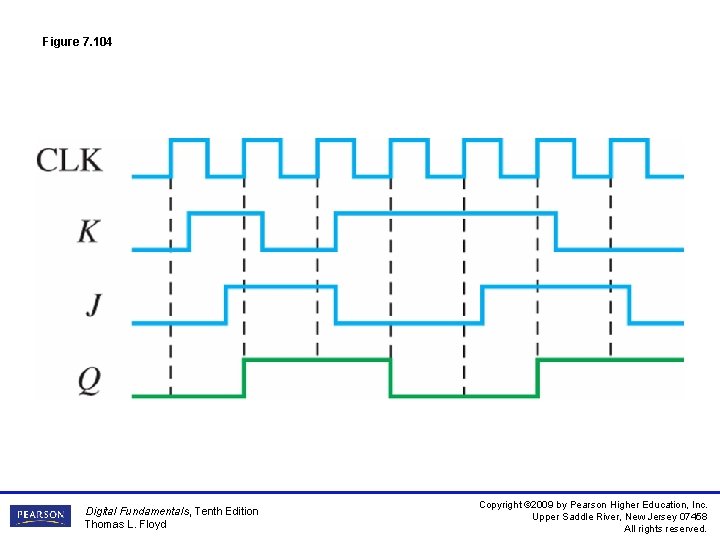

Figure 7. 104 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

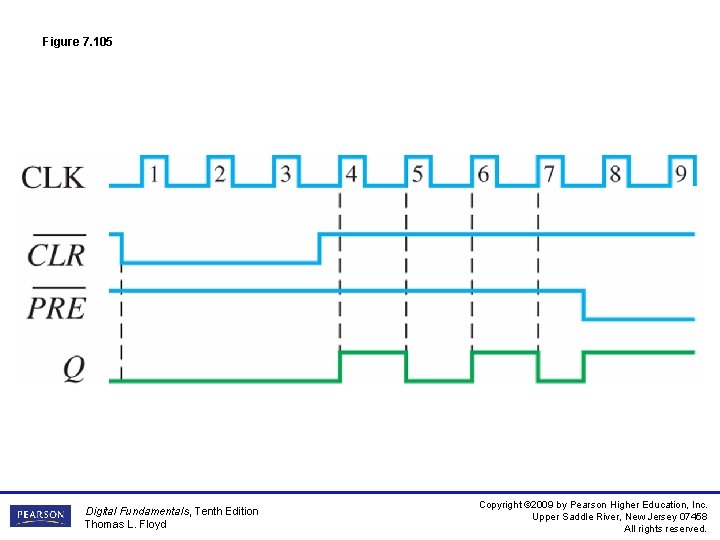

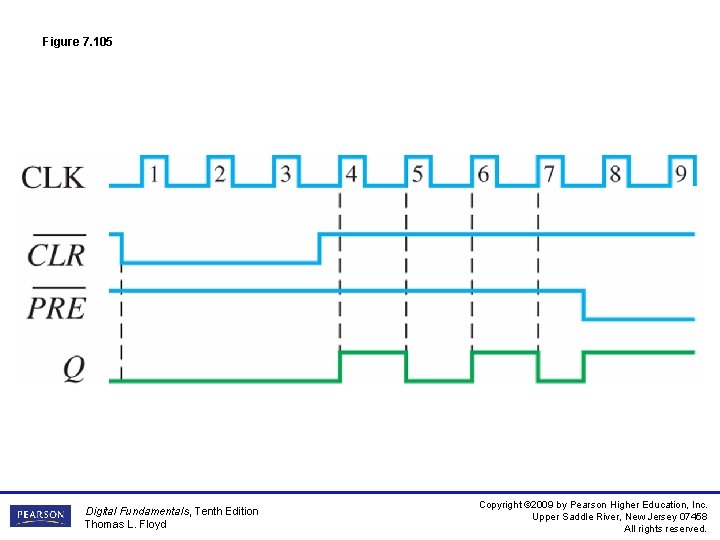

Figure 7. 105 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

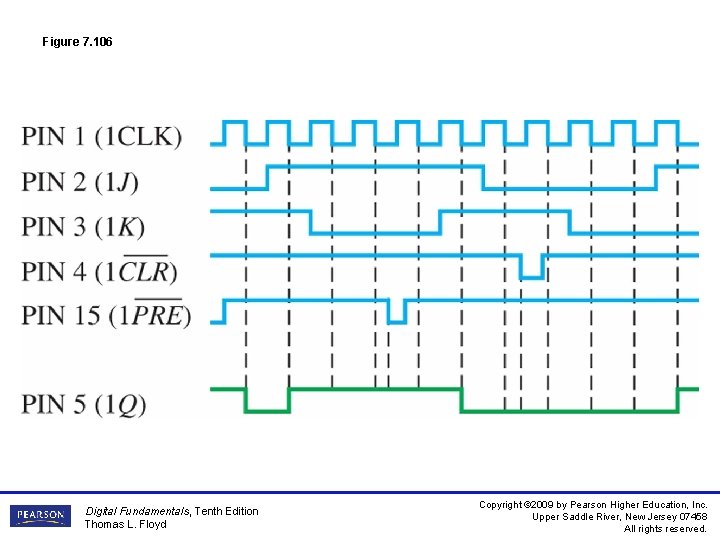

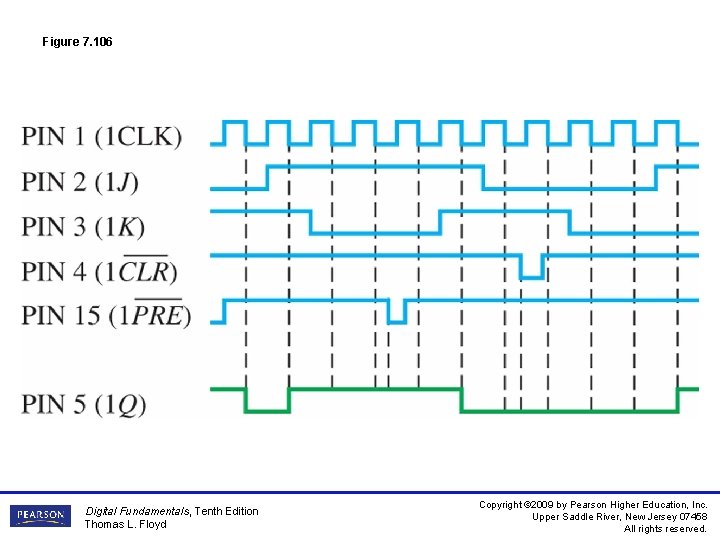

Figure 7. 106 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

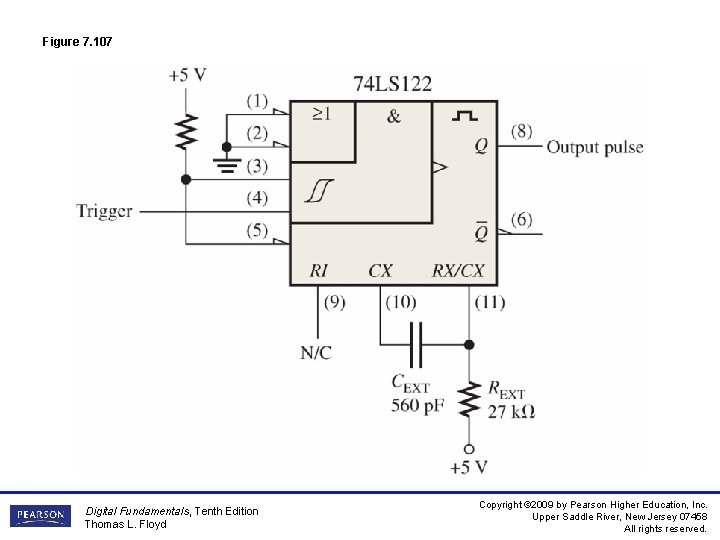

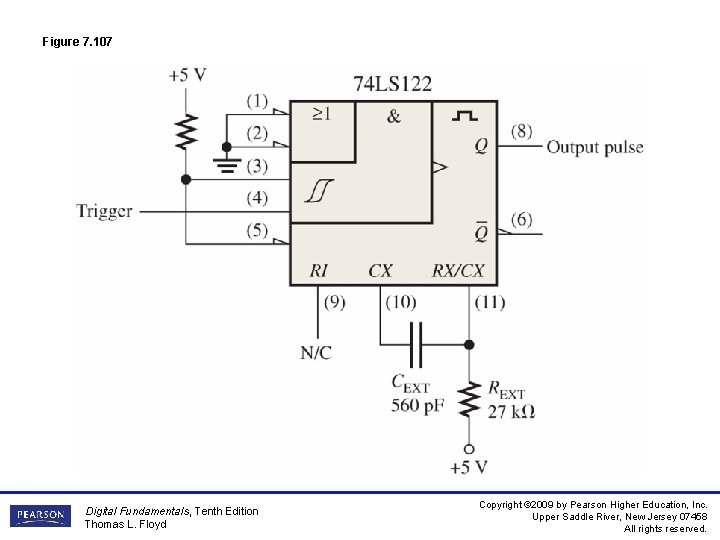

Figure 7. 107 Digital Fundamentals, Tenth Edition Thomas L. Floyd Copyright © 2009 by Pearson Higher Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.