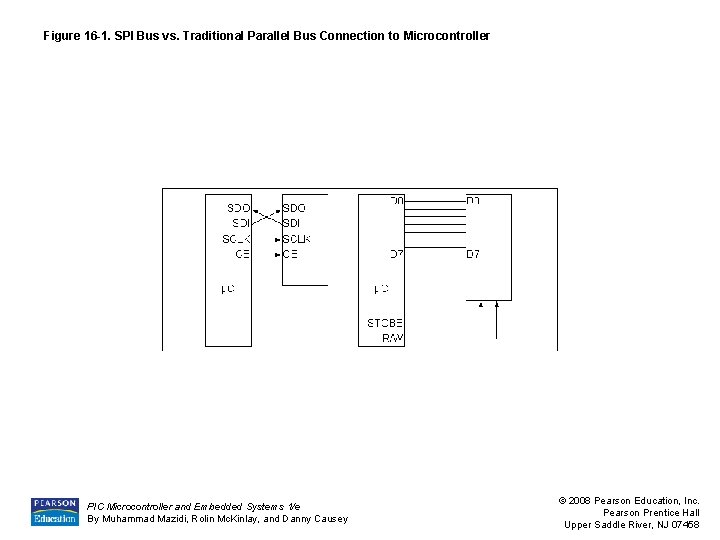

Figure 16 1 SPI Bus vs Traditional Parallel

Figure 16 -1. SPI Bus vs. Traditional Parallel Bus Connection to Microcontroller PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

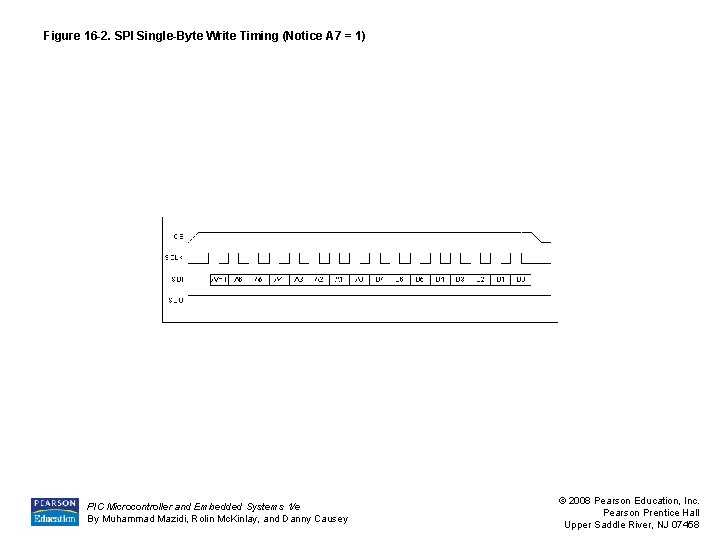

Figure 16 -2. SPI Single-Byte Write Timing (Notice A 7 = 1) PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

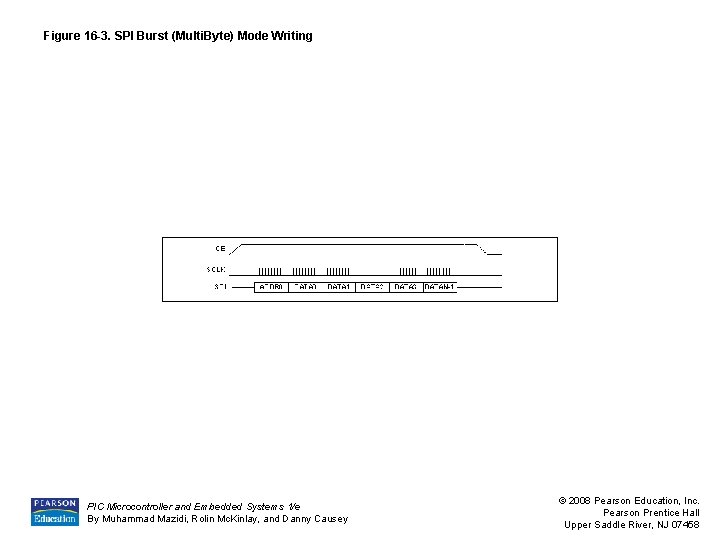

Figure 16 -3. SPI Burst (Multi. Byte) Mode Writing PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

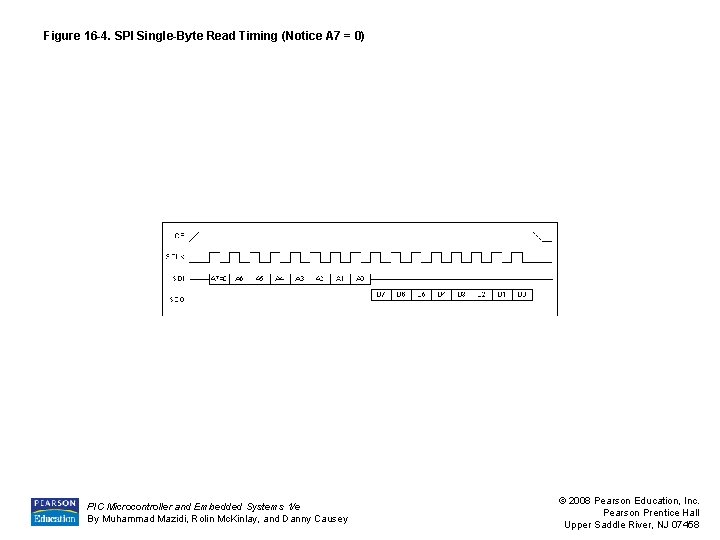

Figure 16 -4. SPI Single-Byte Read Timing (Notice A 7 = 0) PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

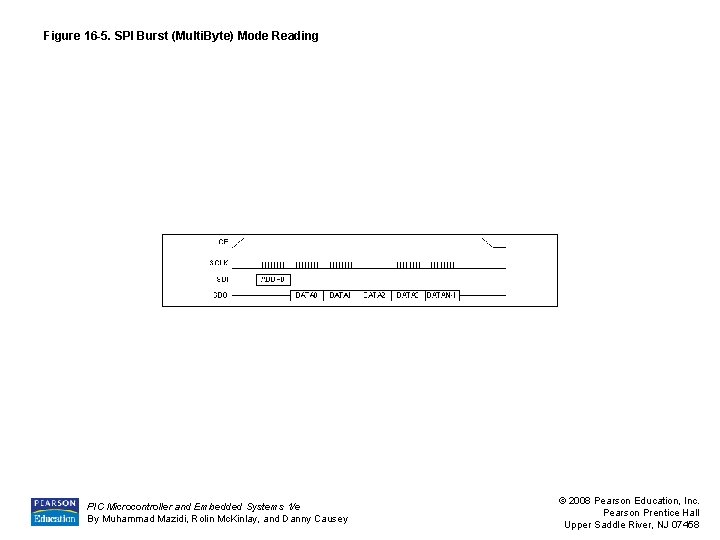

Figure 16 -5. SPI Burst (Multi. Byte) Mode Reading PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

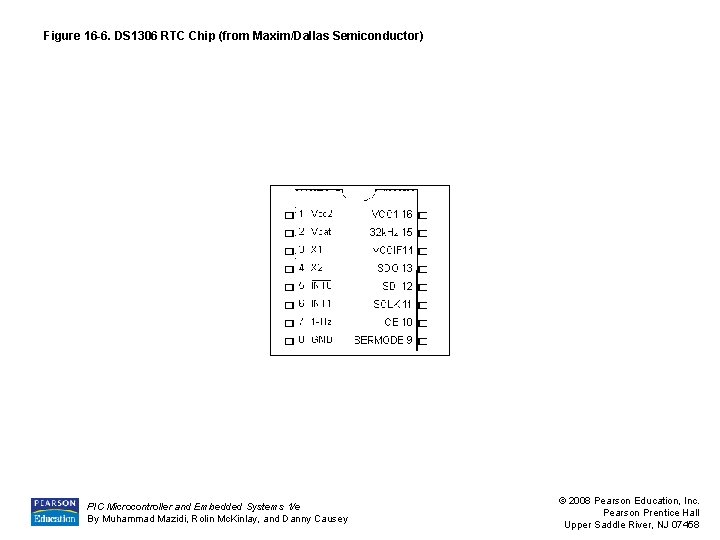

Figure 16 -6. DS 1306 RTC Chip (from Maxim/Dallas Semiconductor) PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

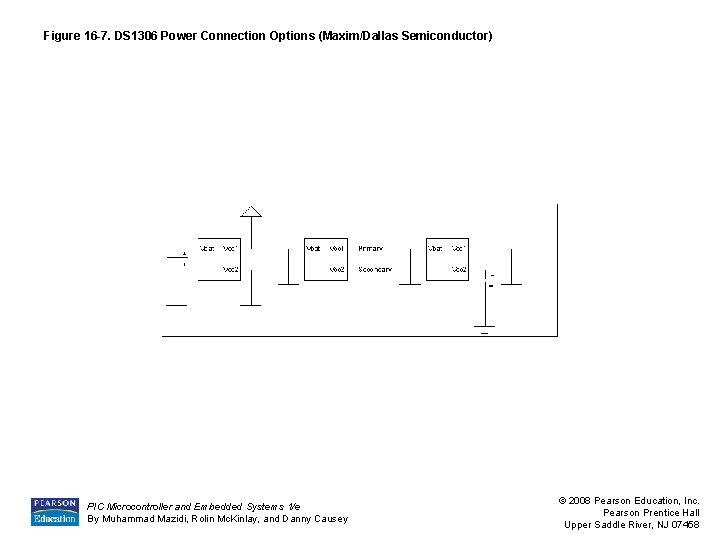

Figure 16 -7. DS 1306 Power Connection Options (Maxim/Dallas Semiconductor) PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

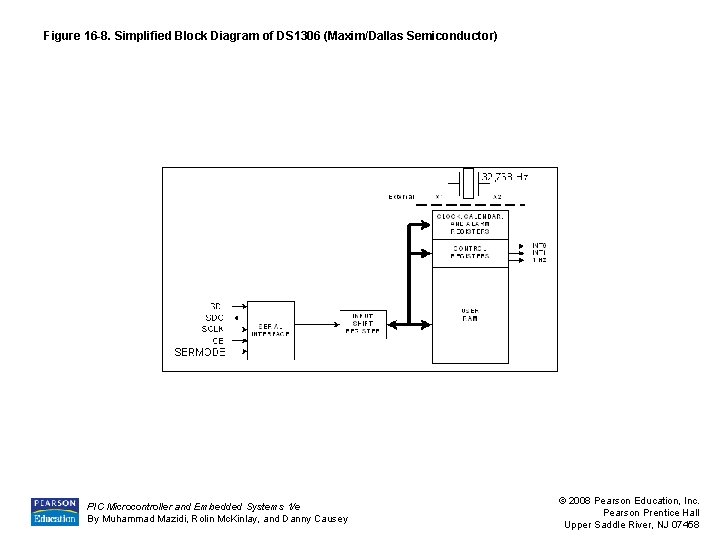

Figure 16 -8. Simplified Block Diagram of DS 1306 (Maxim/Dallas Semiconductor) PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

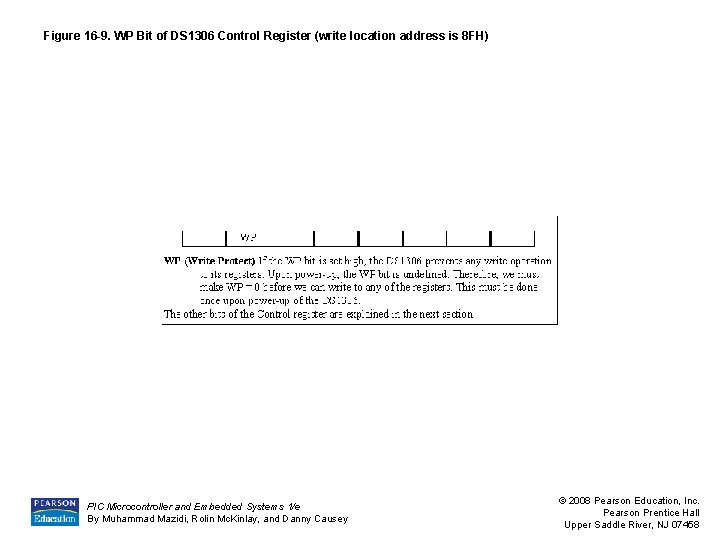

Figure 16 -9. WP Bit of DS 1306 Control Register (write location address is 8 FH) PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

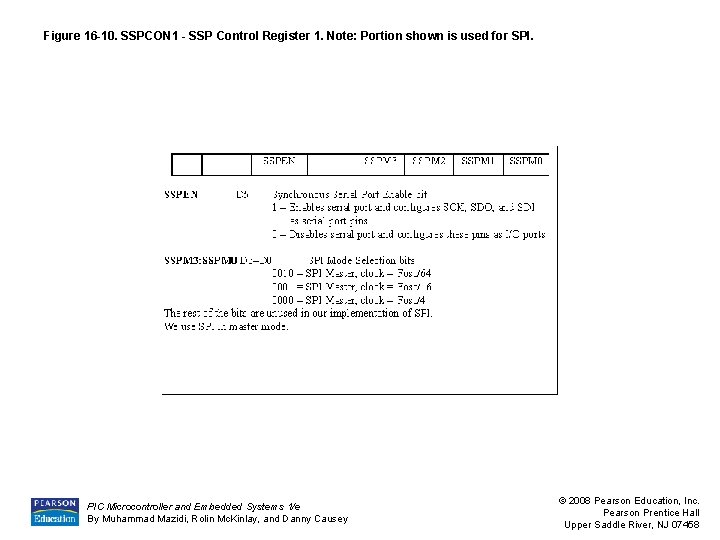

Figure 16 -10. SSPCON 1 - SSP Control Register 1. Note: Portion shown is used for SPI. PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

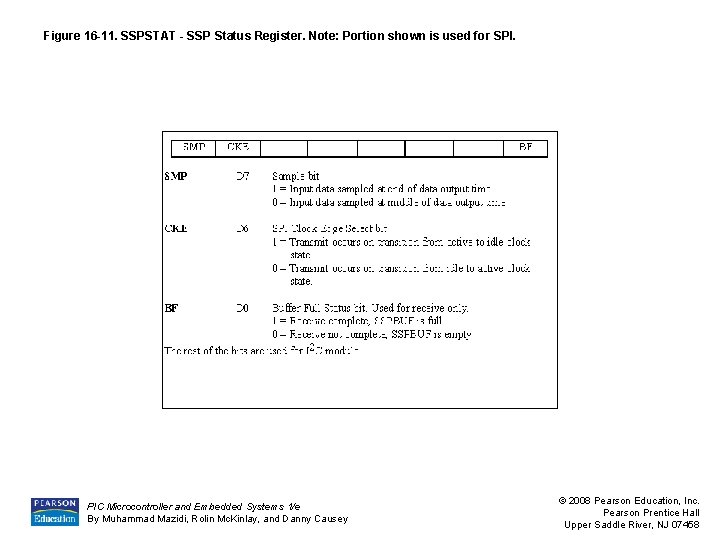

Figure 16 -11. SSPSTAT - SSP Status Register. Note: Portion shown is used for SPI. PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

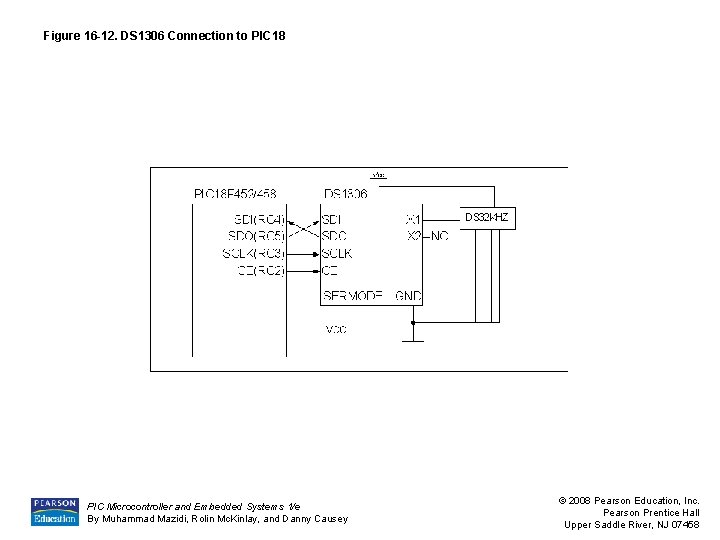

Figure 16 -12. DS 1306 Connection to PIC 18 PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

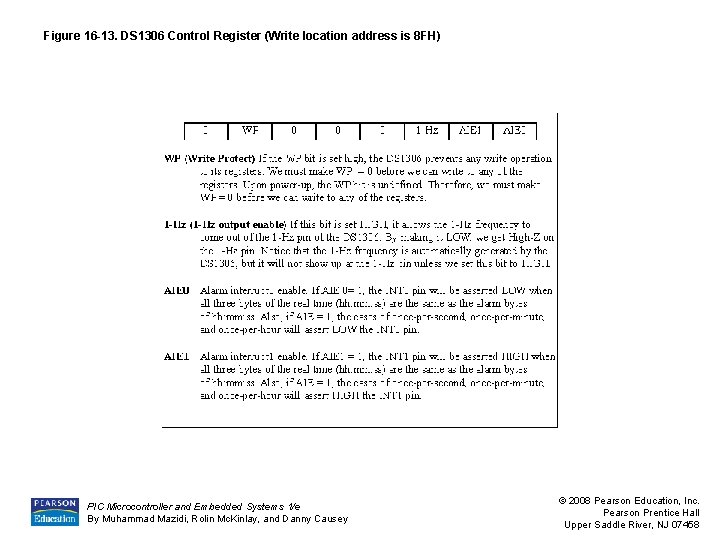

Figure 16 -13. DS 1306 Control Register (Write location address is 8 FH) PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

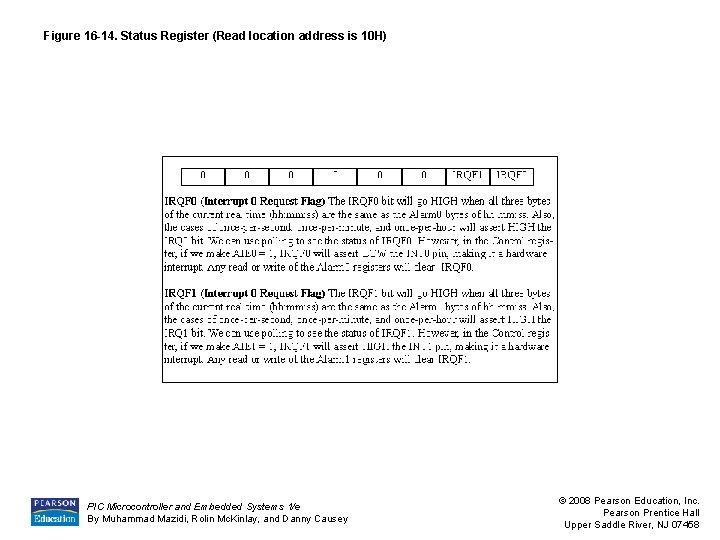

Figure 16 -14. Status Register (Read location address is 10 H) PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

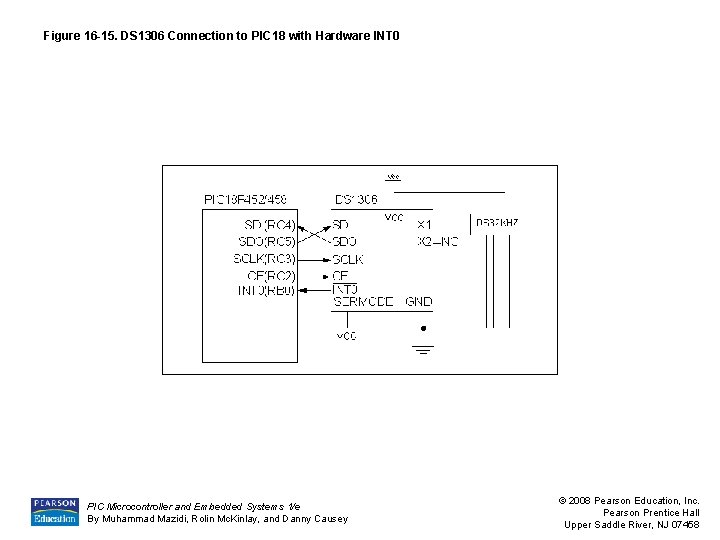

Figure 16 -15. DS 1306 Connection to PIC 18 with Hardware INT 0 PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

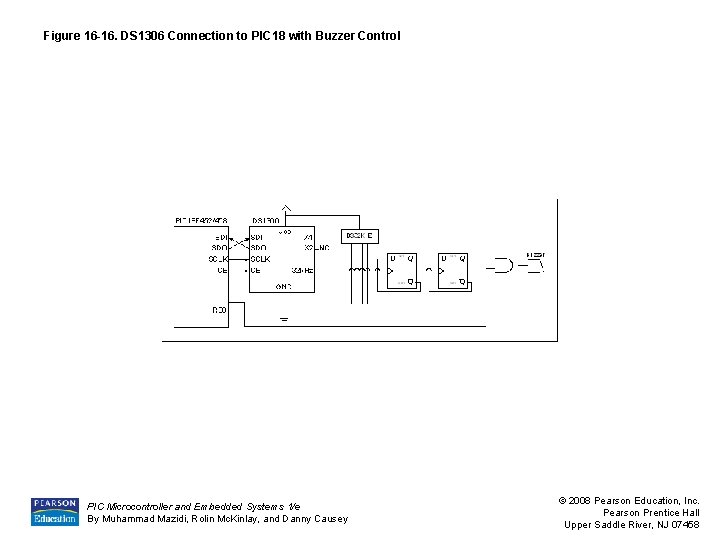

Figure 16 -16. DS 1306 Connection to PIC 18 with Buzzer Control PIC Microcontroller and Embedded Systems 1/e By Muhammad Mazidi, Rolin Mc. Kinlay, and Danny Causey © 2008 Pearson Education, Inc. Pearson Prentice Hall Upper Saddle River, NJ 07458

- Slides: 16