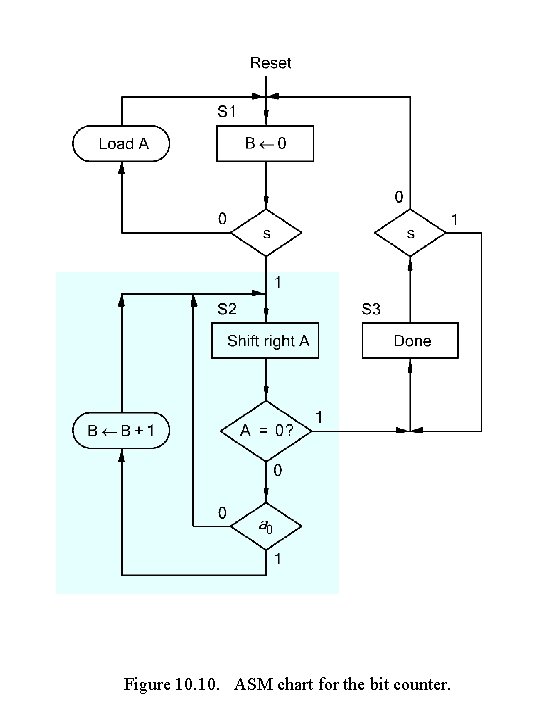

Figure 10 ASM chart for the bit counter

Figure 10. ASM chart for the bit counter.

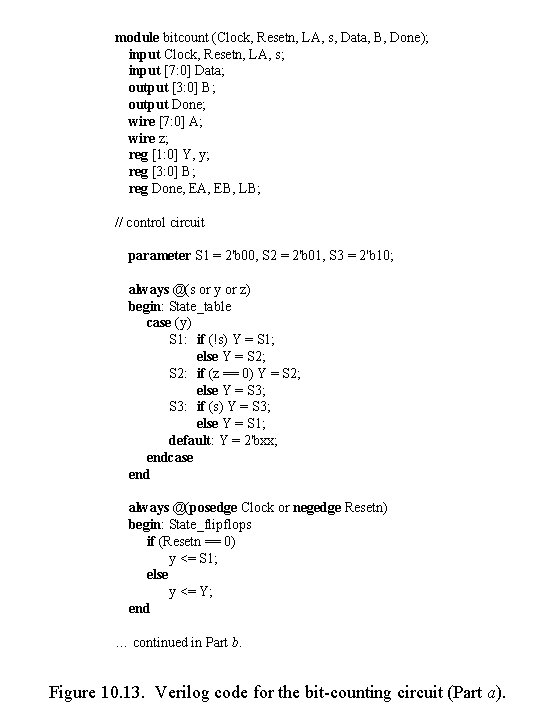

module bitcount (Clock, Resetn, LA, s, Data, B, Done); input Clock, Resetn, LA, s; input [7: 0] Data; output [3: 0] B; output Done; wire [7: 0] A; wire z; reg [1: 0] Y, y; reg [3: 0] B; reg Done, EA, EB, LB; // control circuit parameter S 1 = 2'b 00, S 2 = 2'b 01, S 3 = 2'b 10; always @(s or y or z) begin: State_table case (y) S 1: if (!s) Y = S 1; else Y = S 2; S 2: if (z == 0) Y = S 2; else Y = S 3; S 3: if (s) Y = S 3; else Y = S 1; default: Y = 2'bxx; endcase end always @(posedge Clock or negedge Resetn) begin: State_flipflops if (Resetn == 0) y <= S 1; else y <= Y; end … continued in Part b. Figure 10. 13. Verilog code for the bit-counting circuit (Part a).

![always @(y or A[0]) begin: FSM_outputs // defaults EA = 0; LB = 0; always @(y or A[0]) begin: FSM_outputs // defaults EA = 0; LB = 0;](http://slidetodoc.com/presentation_image_h/27cf973cffa3b1f3c3de6d0725d3776e/image-3.jpg)

always @(y or A[0]) begin: FSM_outputs // defaults EA = 0; LB = 0; EB = 0; Done = 0; case (y) S 1: LB = 1; S 2: begin EA = 1; if (A[0]) EB = 1; else EB = 0; end S 3: Done = 1; endcase end // datapath circuit // counter B always @(negedge Resetn or posedge Clock) if (!Resetn) B <= 0; else if (LB) B <= 0; else if (EB) B <= B + 1; shiftrne Shift. A (Data, LA, EA, 0, Clock, A); assign z = ~| A; endmodule Figure 10. 13. Verilog code for the bit-counting circuit (Part b).

Figure 10. 16. ASM chart for the multiplier.

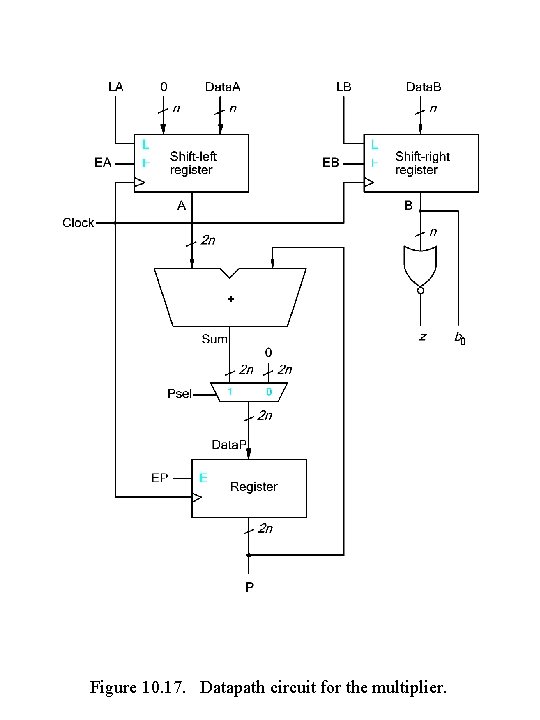

Figure 10. 17. Datapath circuit for the multiplier.

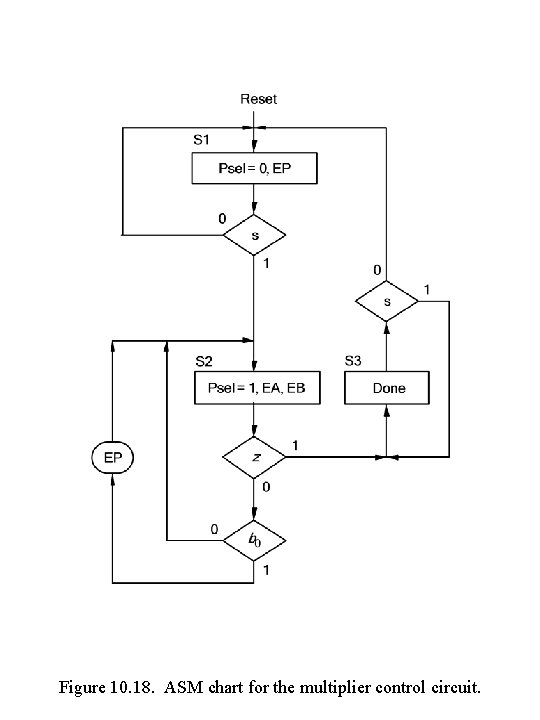

Figure 10. 18. ASM chart for the multiplier control circuit.

module multiply (Clock, Resetn, LA, LB, s, Data. A, Data. B, P, Done); parameter n = 8; input Clock, Resetn, LA, LB, s; input [n-1: 0] Data. A, Data. B; output [n+n-1: 0] P; output Done; wire z; reg [n+n-1: 0] A, Data. P; wire [n+n-1: 0] Sum; reg [1: 0] y, Y; reg [n-1: 0] B; reg Done, EA, EB, EP, Psel; integer k; // control circuit parameter S 1 = 2'b 00, S 2 = 2'b 01, S 3 = 2'b 10; always @(s or y or z) begin: State_table case (y) S 1: if (s == 0) Y = S 1; else Y = S 2; S 2: if (z == 0) Y = S 2; else Y = S 3; S 3: if (s == 1) Y = S 3; else Y = S 1; default: Y = 2'bxx; endcase end always @(posedge Clock or negedge Resetn) begin: State_flipflops if (Resetn == 0) y <= S 1; else y <= Y; end … continued in Part b. Figure 10. 19. Verilog code for the multiplier circuit (Part a).

![always @(s or y or B[0]) begin: FSM_outputs // defaults EA = 0; EB always @(s or y or B[0]) begin: FSM_outputs // defaults EA = 0; EB](http://slidetodoc.com/presentation_image_h/27cf973cffa3b1f3c3de6d0725d3776e/image-8.jpg)

always @(s or y or B[0]) begin: FSM_outputs // defaults EA = 0; EB = 0; EP = 0; Done = 0; Psel = 0; case (y) S 1: EP = 1; S 2: begin EA = 1; EB = 1; Psel = 1; if (B[0]) EP = 1; else EP = 0; end S 3: Done = 1; endcase end //datapath circuit shiftrne Shift. B (Data. B, LB, EB, 0, Clock, B); defparam Shift. B. n = 8; shiftlne Shift. A ({{n{1'b 0}}, Data. A}, LA, EA, 0, Clock, A); defparam Shift. A. n = 16; assign z = (B == 0); assign Sum = A + P; // define the 2 n 2 -to-1 multiplexers always @(Psel or Sum) for (k = 0; k < n+n; k = k+1) Data. P[k] = Psel ? Sum[k] : 0; regne Reg. P (Data. P, Clock, Resetn, EP, P); defparam Reg. P. n = 16; endmodule Figure 10. 19. Verilog code for the multiplier circuit (Part b).

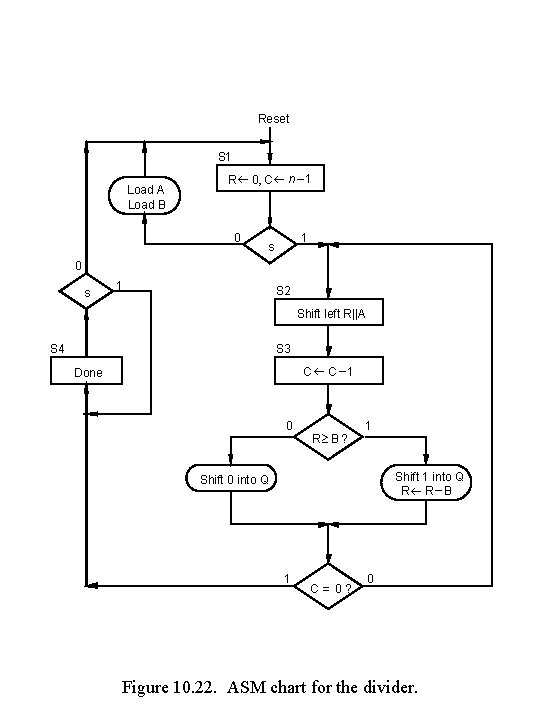

Reset S 1 Load A Load B R ¬ 0, C ¬ n – 1 0 1 s 0 s 1 S 2 Shift left R||A S 4 S 3 C¬ C – 1 Done 0 R³ B? 1 Shift 1 into Q R ¬ R– B Shift 0 into Q 1 C = 0? 0 Figure 10. 22. ASM chart for the divider.

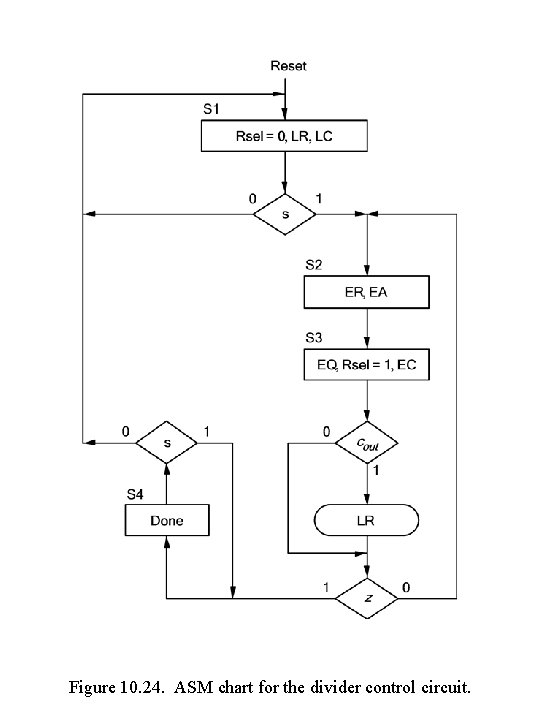

Figure 10. 24. ASM chart for the divider control circuit.

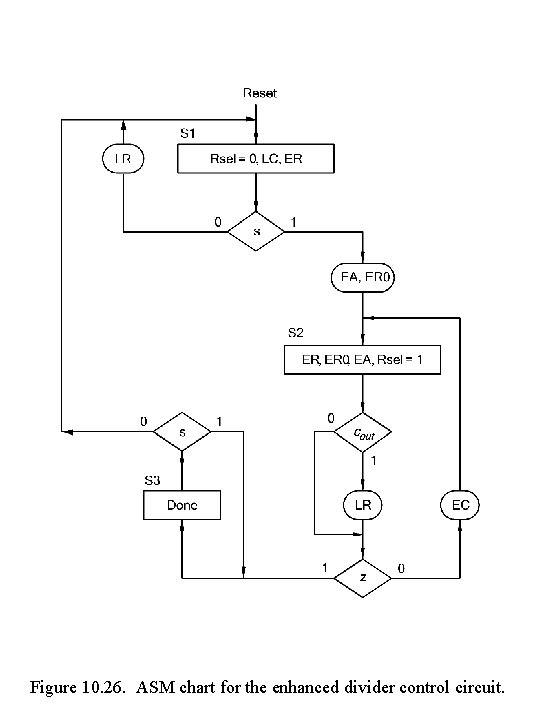

Figure 10. 26. ASM chart for the enhanced divider control circuit.

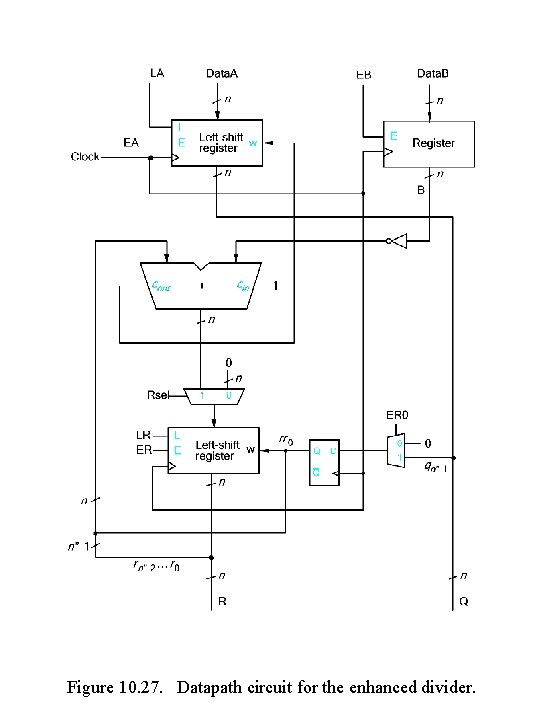

Figure 10. 27. Datapath circuit for the enhanced divider.

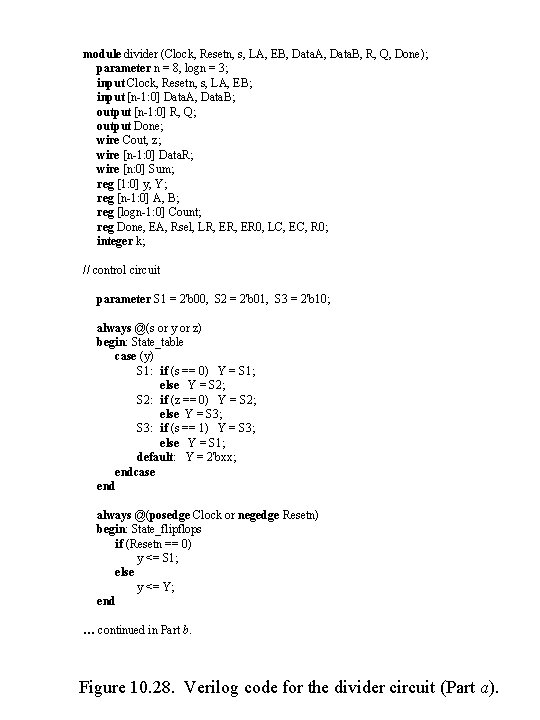

module divider (Clock, Resetn, s, LA, EB, Data. A, Data. B, R, Q, Done); parameter n = 8, logn = 3; input Clock, Resetn, s, LA, EB; input [n-1: 0] Data. A, Data. B; output [n-1: 0] R, Q; output Done; wire Cout, z; wire [n-1: 0] Data. R; wire [n: 0] Sum; reg [1: 0] y, Y; reg [n-1: 0] A, B; reg [logn-1: 0] Count; reg Done, EA, Rsel, LR, ER 0, LC, EC, R 0; integer k; // control circuit parameter S 1 = 2'b 00, S 2 = 2'b 01, S 3 = 2'b 10; always @(s or y or z) begin: State_table case (y) S 1: if (s == 0) Y = S 1; else Y = S 2; S 2: if (z == 0) Y = S 2; else Y = S 3; S 3: if (s == 1) Y = S 3; else Y = S 1; default: Y = 2'bxx; endcase end always @(posedge Clock or negedge Resetn) begin: State_flipflops if (Resetn == 0) y <= S 1; else y <= Y; end … continued in Part b. Figure 10. 28. Verilog code for the divider circuit (Part a).

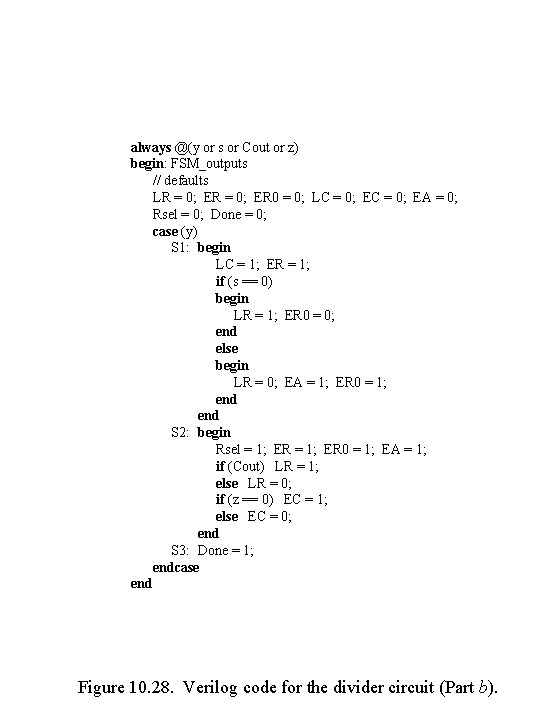

always @(y or s or Cout or z) begin: FSM_outputs // defaults LR = 0; ER 0 = 0; LC = 0; EA = 0; Rsel = 0; Done = 0; case (y) S 1: begin LC = 1; ER = 1; if (s == 0) begin LR = 1; ER 0 = 0; end else begin LR = 0; EA = 1; ER 0 = 1; end S 2: begin Rsel = 1; ER 0 = 1; EA = 1; if (Cout) LR = 1; else LR = 0; if (z == 0) EC = 1; else EC = 0; end S 3: Done = 1; endcase end Figure 10. 28. Verilog code for the divider circuit (Part b).

//datapath circuit regne Reg. B (Data. B, Clock, Resetn, EB, B); defparam Reg. B. n = n; shiftlne Shift. R (Data. R, LR, ER, R 0, Clock, R); defparam Shift. R. n = n; muxdff FF_R 0 (0, A[n-1], ER 0, Clock, R 0); shiftlne Shift. A (Data. A, LA, EA, Cout, Clock, A); defparam Shift. A. n = n; assign Q = A; downcount Counter (Clock, EC, LC, Count); defparam Counter. n = logn; assign z = (Count == 0); assign Sum = {R, R 0} + (~B + 1); assign Cout = Sum[n]; // define the n 2 -to-1 multiplexers assign Data. R = Rsel ? Sum : 0; endmodule Figure 10. 28. Verilog code for the divider circuit (Part c).

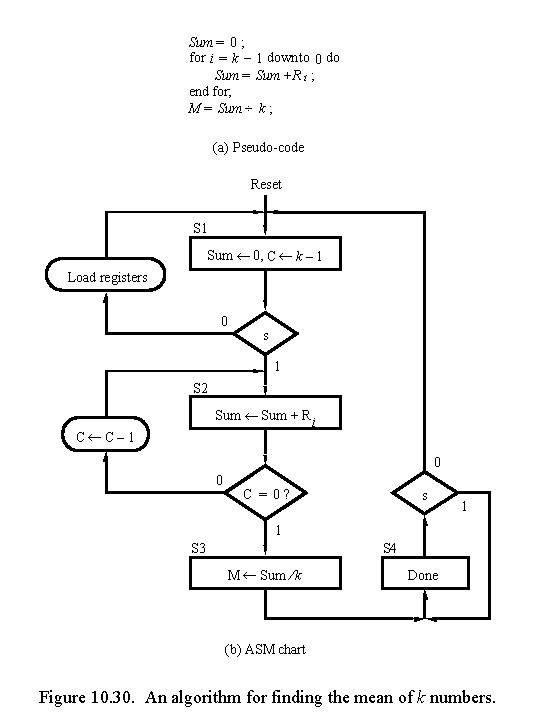

Sum = 0 ; for i = k – 1 downto 0 do Sum = Sum +R i ; end for; M = Sum ÷ k ; (a) Pseudo-code Reset S 1 Sum ¬ 0 , C ¬ k – 1 Load registers 0 s 1 S 2 Sum ¬ Sum + R i C ¬ C – 1 0 0 C = 0 ? s 1 1 S 3 S 4 M ¬ Sum ¤ k Done (b) ASM chart Figure 10. 30. An algorithm for finding the mean of k numbers.

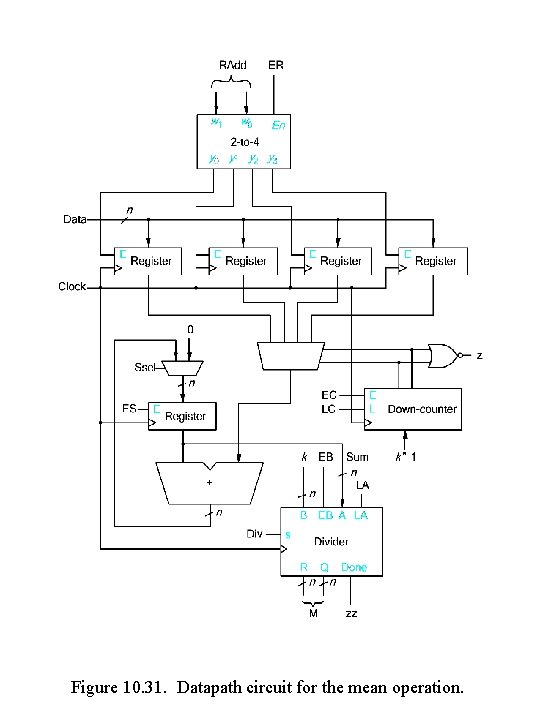

Figure 10. 31. Datapath circuit for the mean operation.

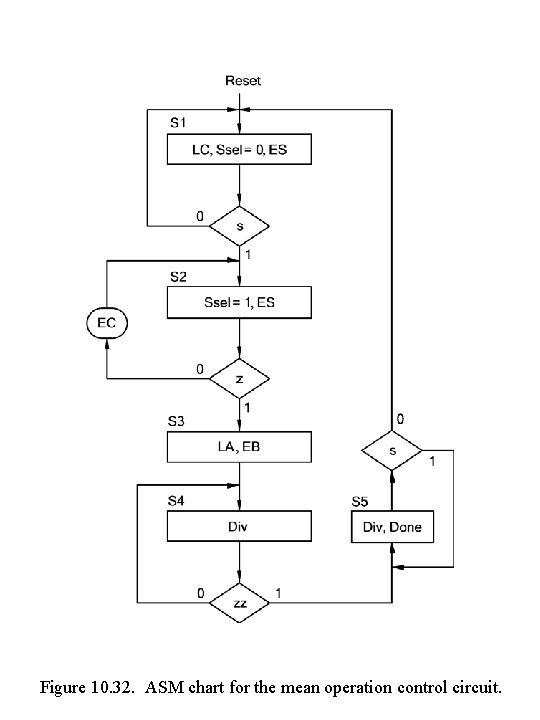

Figure 10. 32. ASM chart for the mean operation control circuit.

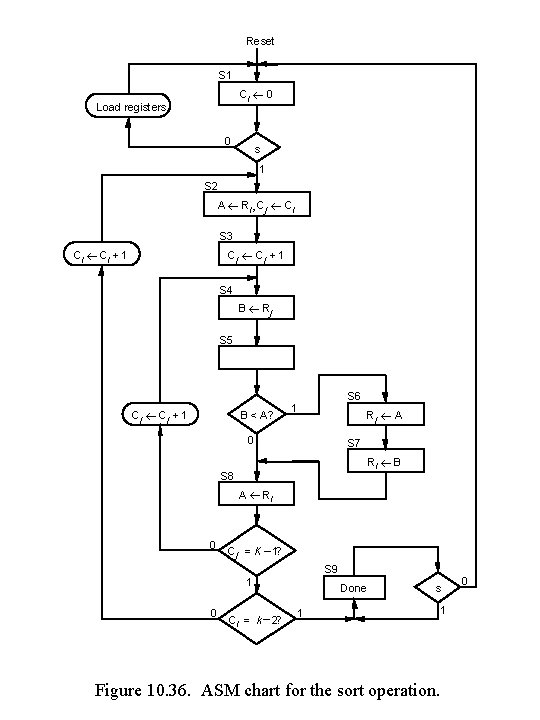

Reset S 1 Ci ¬ 0 Load registers 0 s 1 S 2 A ¬ Ri , C j ¬ Ci S 3 Ci ¬ Ci + 1 Cj ¬ Cj + 1 S 4 B ¬ Rj S 5 Cj ¬ Cj + 1 B < A? S 6 1 Rj ¬ A 0 S 7 Ri ¬ B S 8 A ¬ Ri 0 C j = K – 1? S 9 1 0 Ci = k – 2? Done s 1 Figure 10. 36. ASM chart for the sort operation. 1 0

Figure 10. 39. ASM chart for the control circuit.

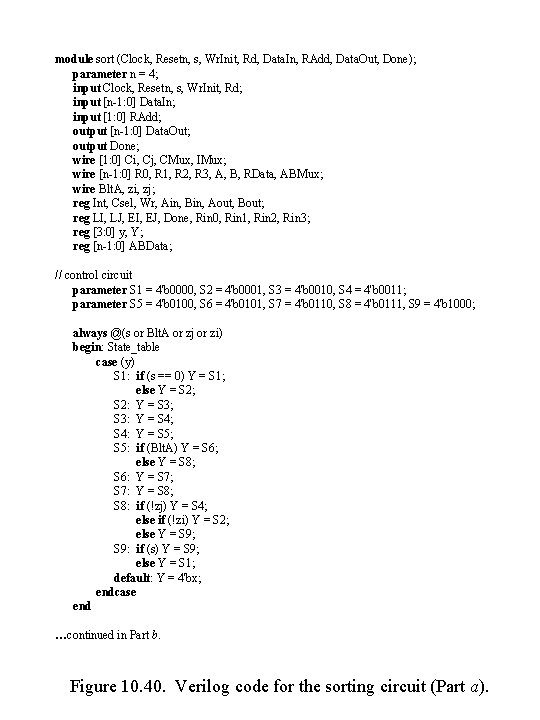

module sort (Clock, Resetn, s, Wr. Init, Rd, Data. In, RAdd, Data. Out, Done); parameter n = 4; input Clock, Resetn, s, Wr. Init, Rd; input [n-1: 0] Data. In; input [1: 0] RAdd; output [n-1: 0] Data. Out; output Done; wire [1: 0] Ci, Cj, CMux, IMux; wire [n-1: 0] R 0, R 1, R 2, R 3, A, B, RData, ABMux; wire Blt. A, zi, zj; reg Int, Csel, Wr, Ain, Bin, Aout, Bout; reg LI, LJ, EI, EJ, Done, Rin 0, Rin 1, Rin 2, Rin 3; reg [3: 0] y, Y; reg [n-1: 0] ABData; // control circuit parameter S 1 = 4'b 0000, S 2 = 4'b 0001, S 3 = 4'b 0010, S 4 = 4'b 0011; parameter S 5 = 4'b 0100, S 6 = 4'b 0101, S 7 = 4'b 0110, S 8 = 4'b 0111, S 9 = 4'b 1000; always @(s or Blt. A or zj or zi) begin: State_table case (y) S 1: if (s == 0) Y = S 1; else Y = S 2; S 2: Y = S 3; S 3: Y = S 4; S 4: Y = S 5; S 5: if (Blt. A) Y = S 6; else Y = S 8; S 6: Y = S 7; S 7: Y = S 8; S 8: if (!zj) Y = S 4; else if (!zi) Y = S 2; else Y = S 9; S 9: if (s) Y = S 9; else Y = S 1; default: Y = 4'bx; endcase end …continued in Part b. Figure 10. 40. Verilog code for the sorting circuit (Part a).

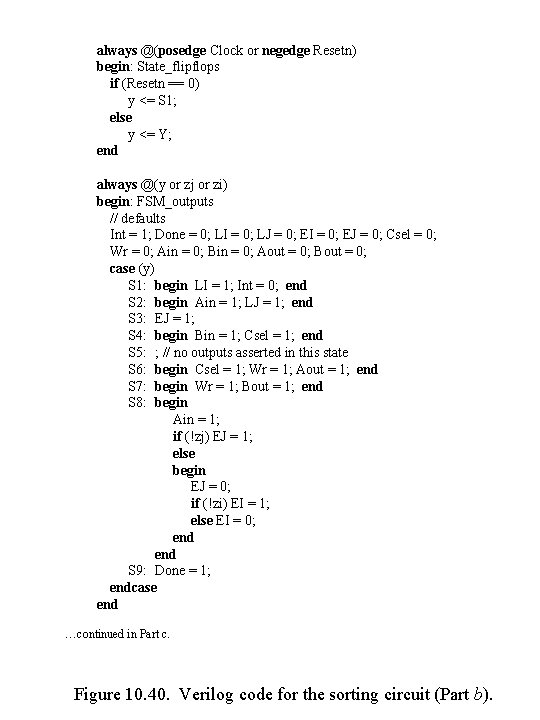

always @(posedge Clock or negedge Resetn) begin: State_flipflops if (Resetn == 0) y <= S 1; else y <= Y; end always @(y or zj or zi) begin: FSM_outputs // defaults Int = 1; Done = 0; LI = 0; LJ = 0; EI = 0; EJ = 0; Csel = 0; Wr = 0; Ain = 0; Bin = 0; Aout = 0; Bout = 0; case (y) S 1: begin LI = 1; Int = 0; end S 2: begin Ain = 1; LJ = 1; end S 3: EJ = 1; S 4: begin Bin = 1; Csel = 1; end S 5: ; // no outputs asserted in this state S 6: begin Csel = 1; Wr = 1; Aout = 1; end S 7: begin Wr = 1; Bout = 1; end S 8: begin Ain = 1; if (!zj) EJ = 1; else begin EJ = 0; if (!zi) EI = 1; else EI = 0; end S 9: Done = 1; endcase end …continued in Part c. Figure 10. 40. Verilog code for the sorting circuit (Part b).

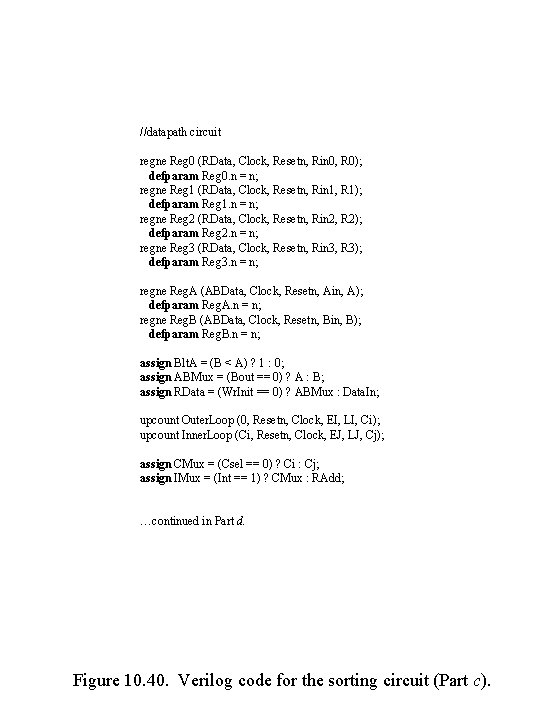

//datapath circuit regne Reg 0 (RData, Clock, Resetn, Rin 0, R 0); defparam Reg 0. n = n; regne Reg 1 (RData, Clock, Resetn, Rin 1, R 1); defparam Reg 1. n = n; regne Reg 2 (RData, Clock, Resetn, Rin 2, R 2); defparam Reg 2. n = n; regne Reg 3 (RData, Clock, Resetn, Rin 3, R 3); defparam Reg 3. n = n; regne Reg. A (ABData, Clock, Resetn, Ain, A); defparam Reg. A. n = n; regne Reg. B (ABData, Clock, Resetn, Bin, B); defparam Reg. B. n = n; assign Blt. A = (B < A) ? 1 : 0; assign ABMux = (Bout == 0) ? A : B; assign RData = (Wr. Init == 0) ? ABMux : Data. In; upcount Outer. Loop (0, Resetn, Clock, EI, LI, Ci); upcount Inner. Loop (Ci, Resetn, Clock, EJ, LJ, Cj); assign CMux = (Csel == 0) ? Ci : Cj; assign IMux = (Int == 1) ? CMux : RAdd; …continued in Part d. Figure 10. 40. Verilog code for the sorting circuit (Part c).

always @(Wr. Init or Wr or IMux) begin case (IMux) 0: ABData = R 0; 1: ABData = R 1; 2: ABData = R 2; 3: ABData = R 3; endcase if (Wr. Init || Wr) case (IMux) 0: {Rin 3, Rin 2, Rin 1, Rin 0} = 4'b 0001; 1: {Rin 3, Rin 2, Rin 1, Rin 0} = 4'b 0010; 2: {Rin 3, Rin 2, Rin 1, Rin 0} = 4'b 0100; 3: {Rin 3, Rin 2, Rin 1, Rin 0} = 4'b 1000; endcase else {Rin 3, Rin 2, Rin 1, Rin 0} = 4'b 0000; end assign zi = (Ci == 2); assign zj = (Cj == 3); assign Data. Out = (Rd == 0) ? 'bz : ABData; endmodule Figure 10. 40. Verilog code for the sorting circuit (Part d).

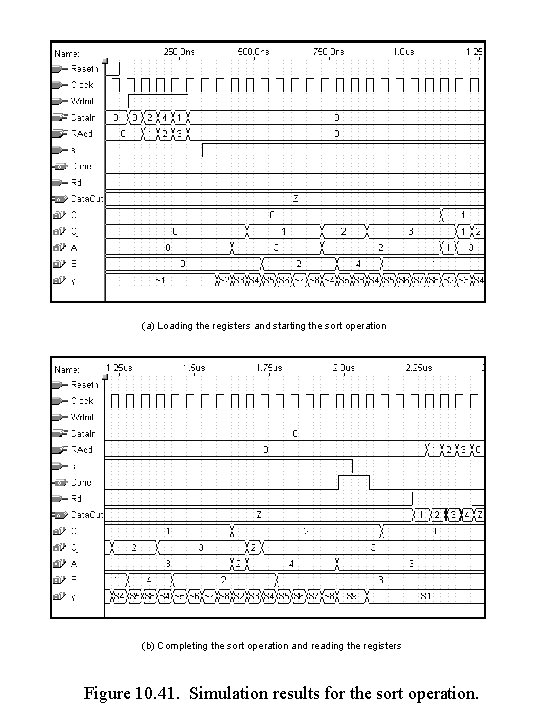

(a) Loading the registers and starting the sort operation (b) Completing the sort operation and reading the registers Figure 10. 41. Simulation results for the sort operation.

- Slides: 25