Figure 1 12 An amplifier that requires two

- Slides: 49

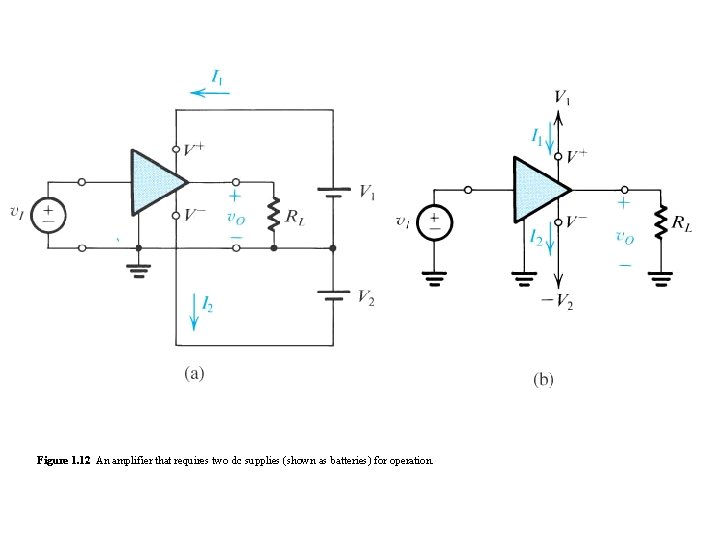

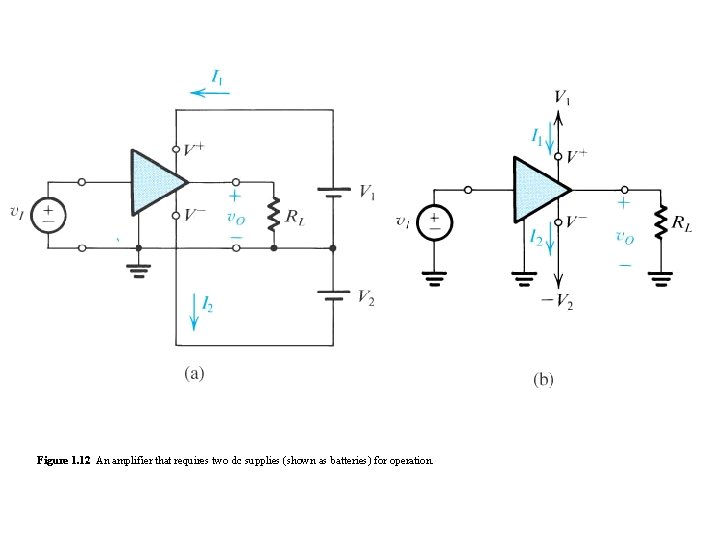

Figure 1. 12 An amplifier that requires two dc supplies (shown as batteries) for operation.

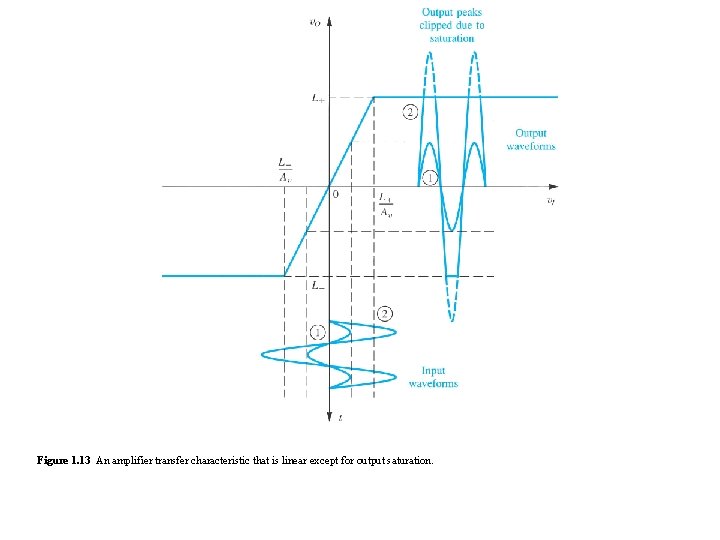

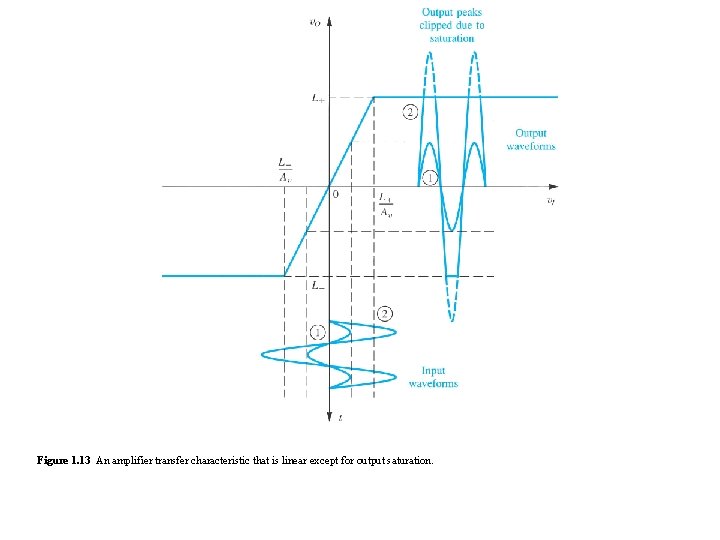

Figure 1. 13 An amplifier transfer characteristic that is linear except for output saturation.

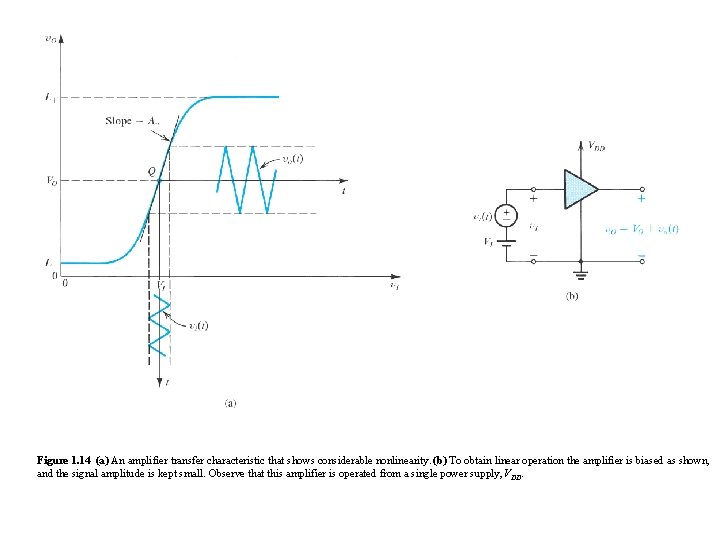

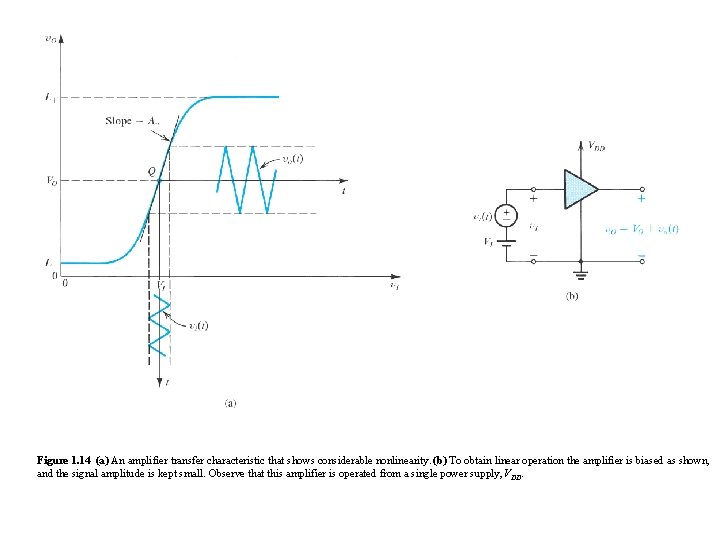

Figure 1. 14 (a) An amplifier transfer characteristic that shows considerable nonlinearity. (b) To obtain linear operation the amplifier is biased as shown, and the signal amplitude is kept small. Observe that this amplifier is operated from a single power supply, VDD.

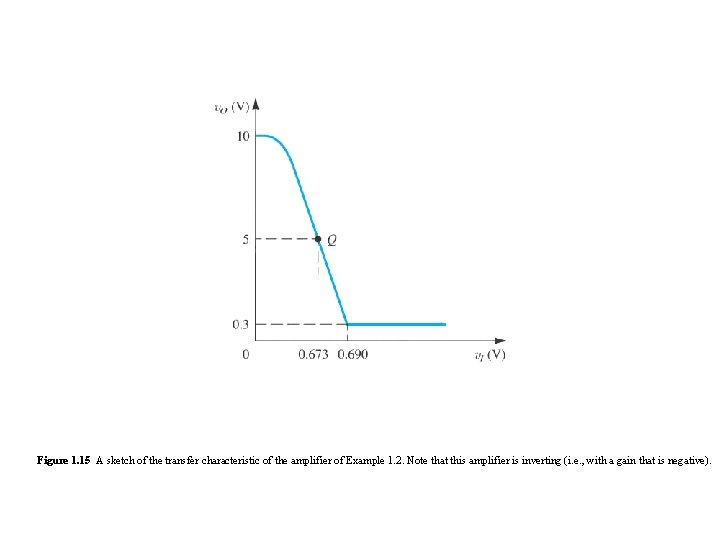

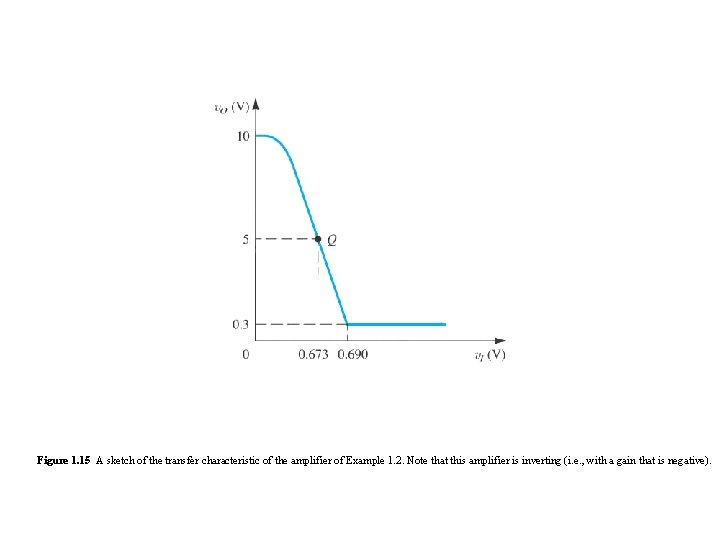

Figure 1. 15 A sketch of the transfer characteristic of the amplifier of Example 1. 2. Note that this amplifier is inverting (i. e. , with a gain that is negative).

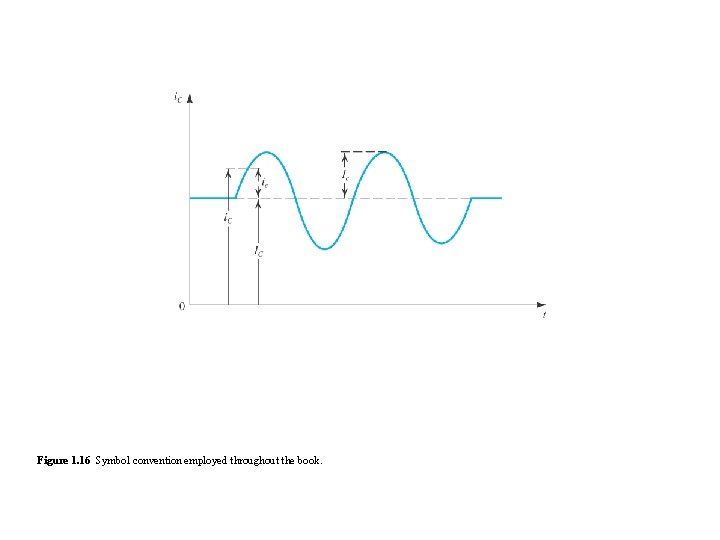

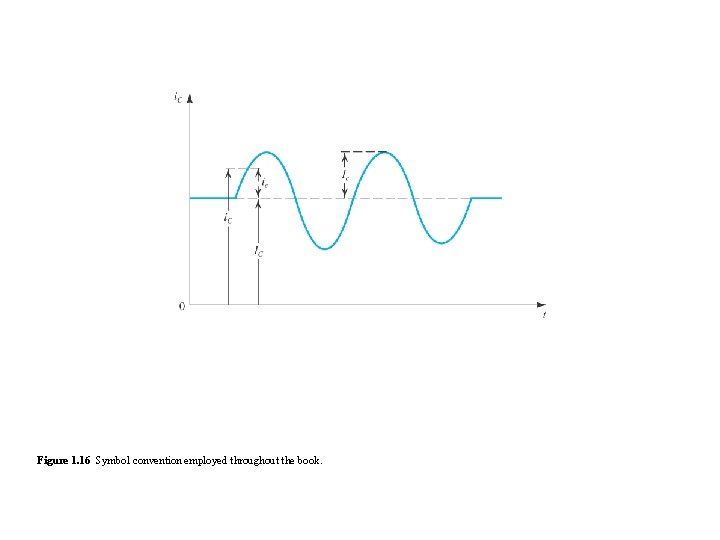

Figure 1. 16 Symbol convention employed throughout the book.

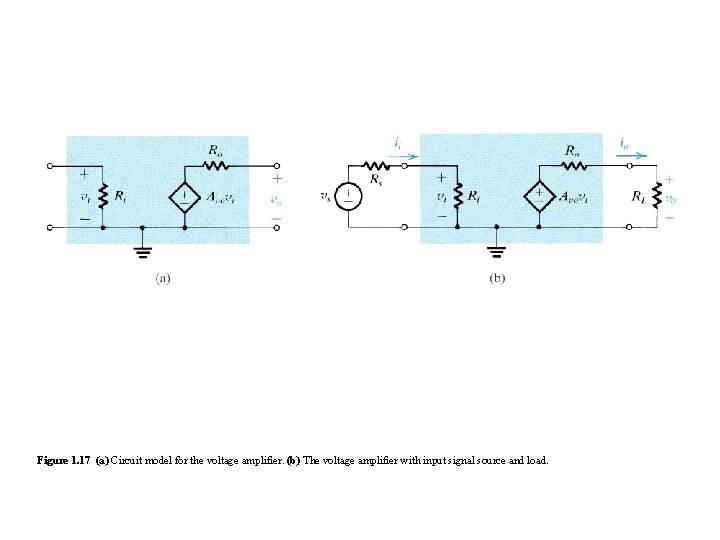

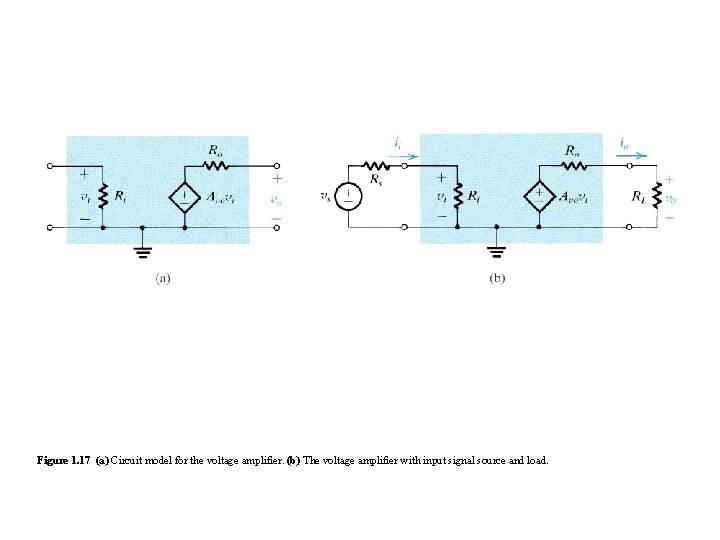

Figure 1. 17 (a) Circuit model for the voltage amplifier. (b) The voltage amplifier with input signal source and load.

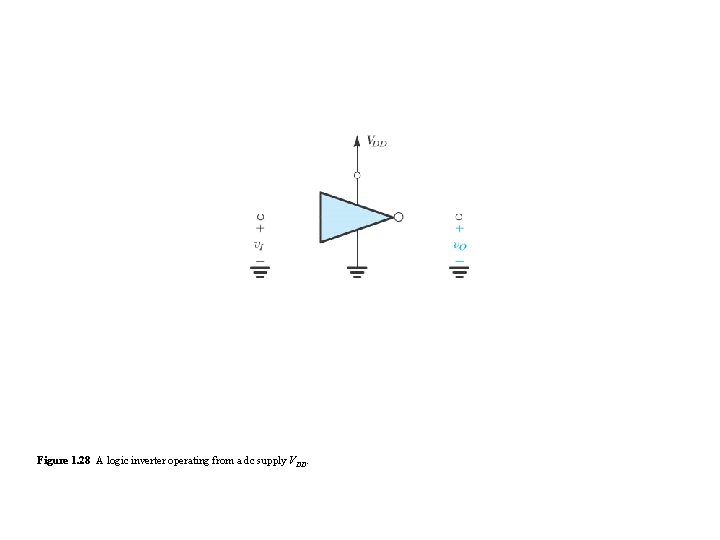

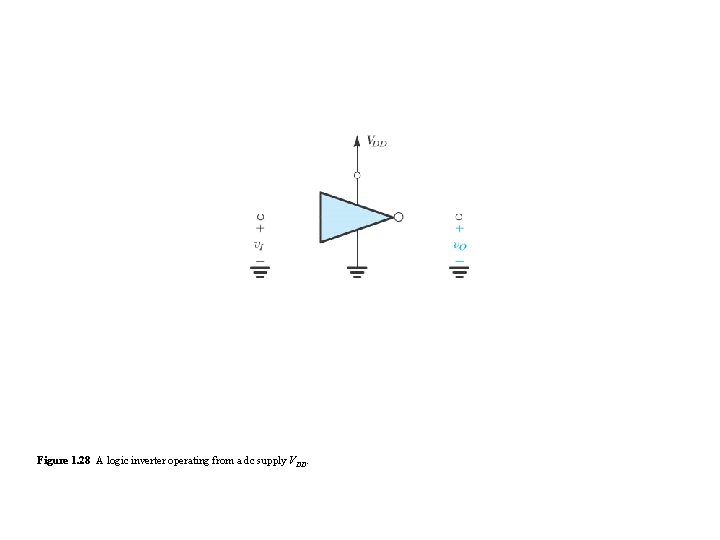

Figure 1. 28 A logic inverter operating from a dc supply VDD.

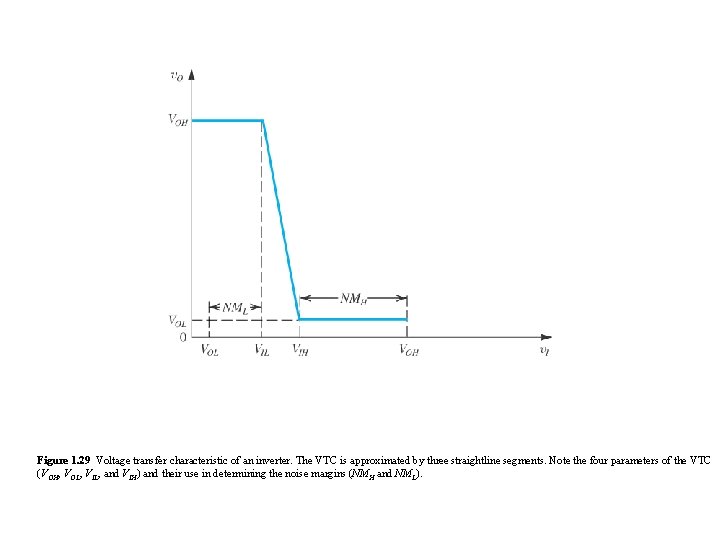

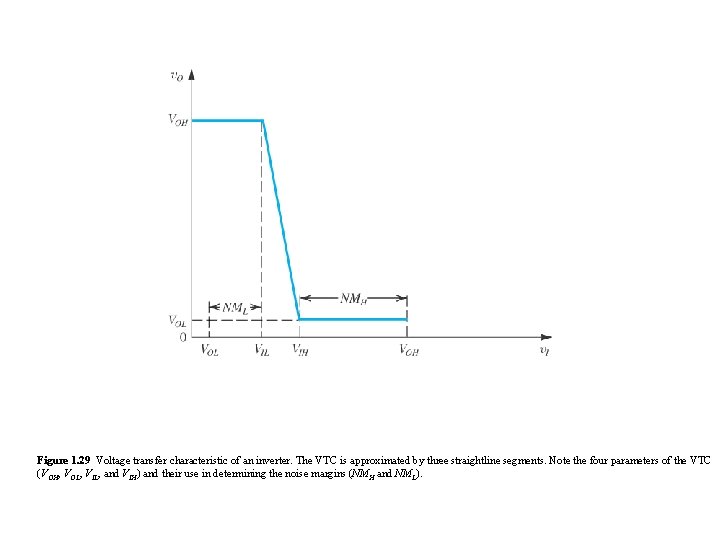

Figure 1. 29 Voltage transfer characteristic of an inverter. The VTC is approximated by three straightline segments. Note the four parameters of the VTC (VOH, VOL, VIL, and VIH) and their use in determining the noise margins (NMH and NML).

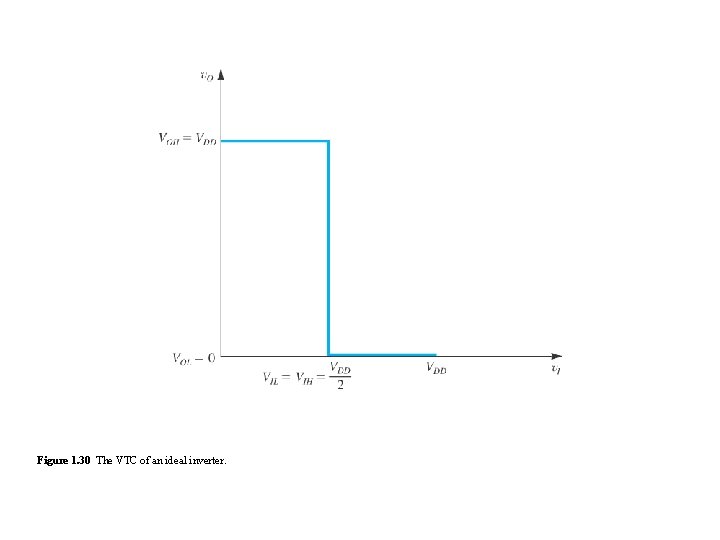

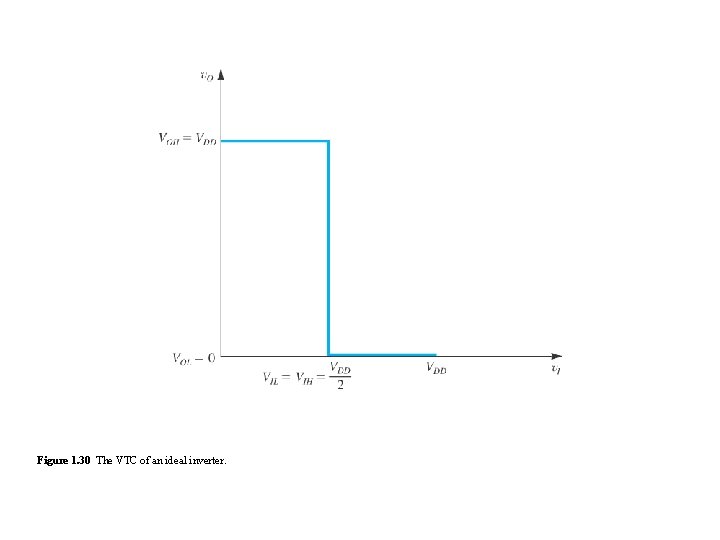

Figure 1. 30 The VTC of an ideal inverter.

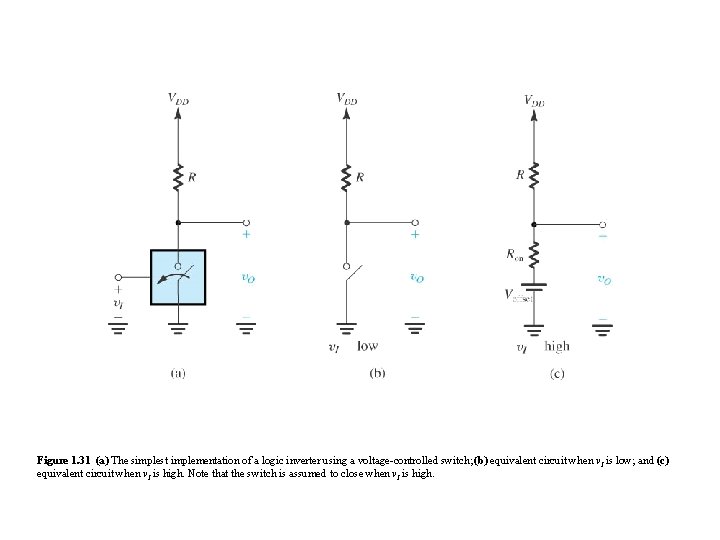

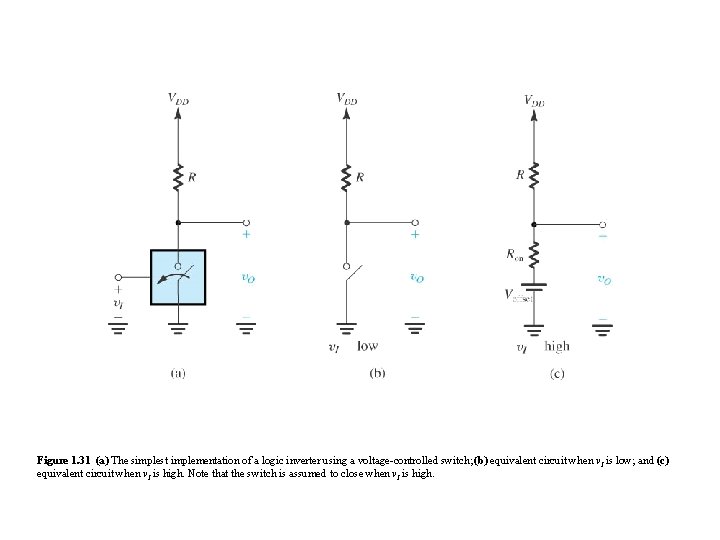

Figure 1. 31 (a) The simplest implementation of a logic inverter using a voltage-controlled switch; (b) equivalent circuit when v. I is low; and (c) equivalent circuit when v. I is high. Note that the switch is assumed to close when v. I is high.

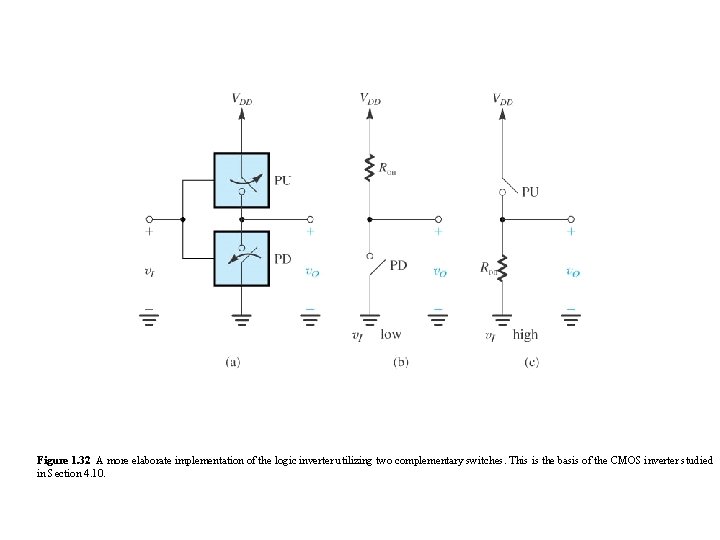

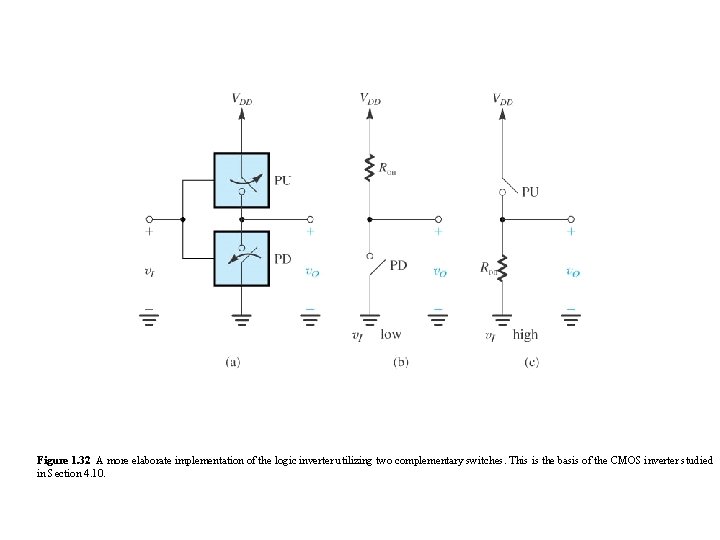

Figure 1. 32 A more elaborate implementation of the logic inverter utilizing two complementary switches. This is the basis of the CMOS inverter studied in Section 4. 10.

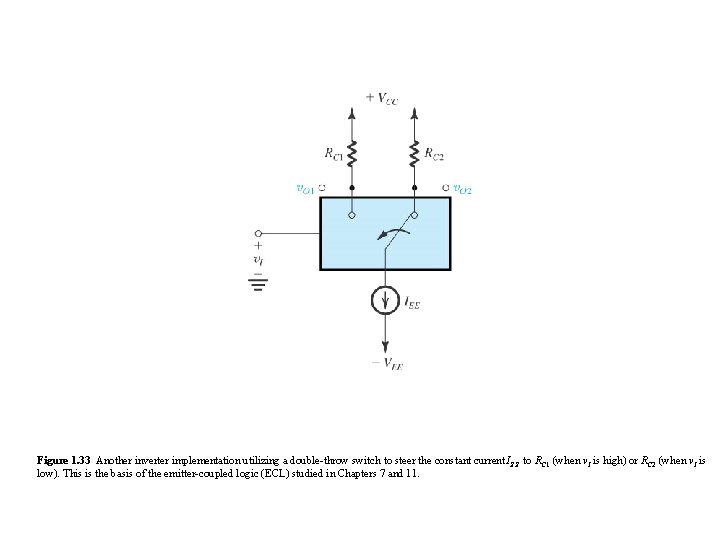

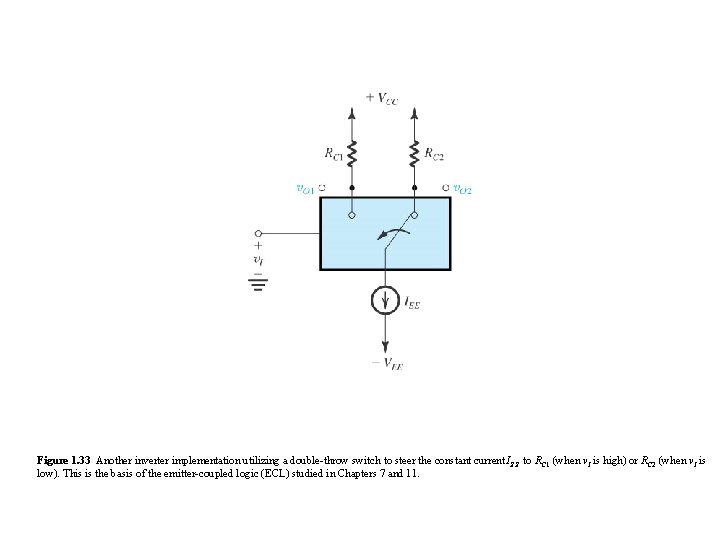

Figure 1. 33 Another inverter implementation utilizing a double-throw switch to steer the constant current IEE to RC 1 (when v. I is high) or RC 2 (when v. I is low). This is the basis of the emitter-coupled logic (ECL) studied in Chapters 7 and 11.

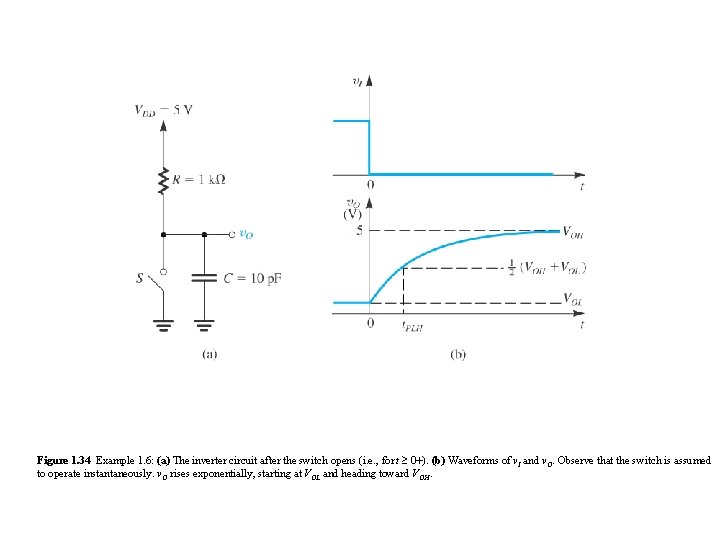

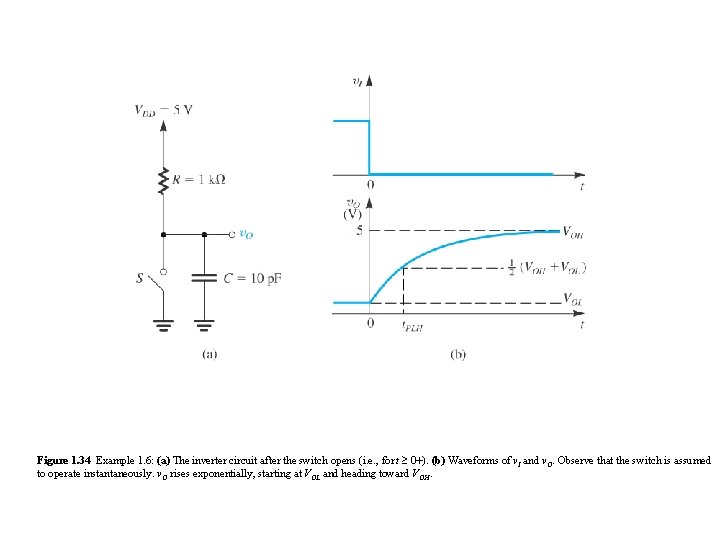

Figure 1. 34 Example 1. 6: (a) The inverter circuit after the switch opens (i. e. , for t 0 ). (b) Waveforms of v. I and v. O. Observe that the switch is assumed to operate instantaneously. v. O rises exponentially, starting at VOL and heading toward VOH.

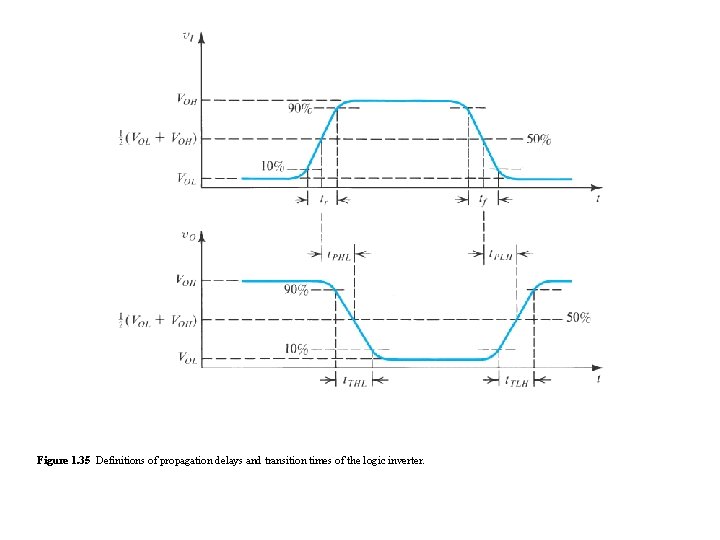

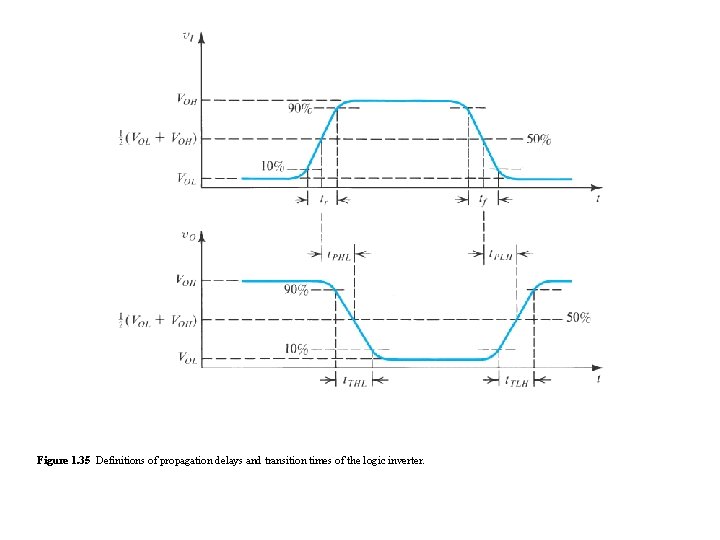

Figure 1. 35 Definitions of propagation delays and transition times of the logic inverter.

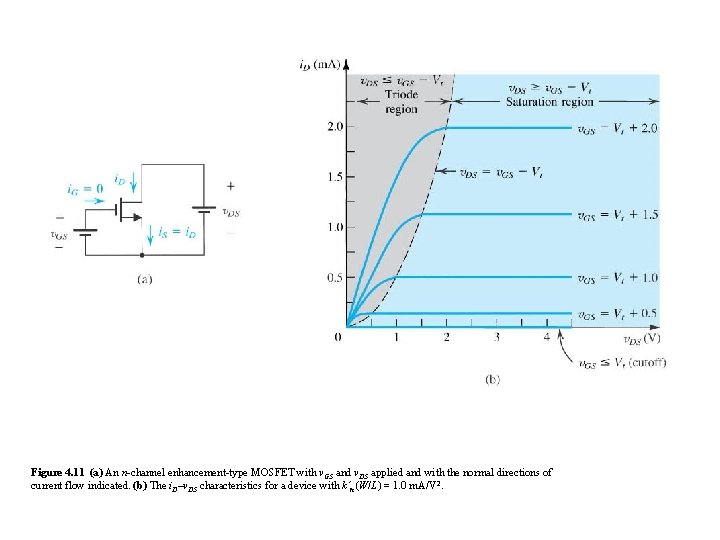

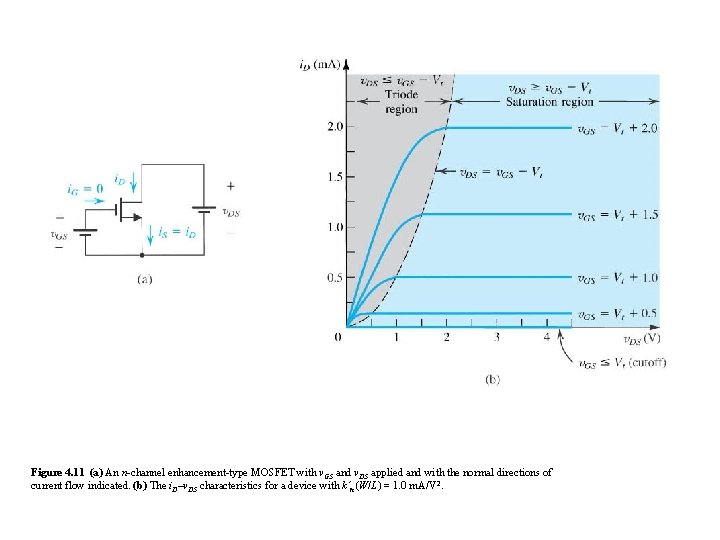

Figure 4. 11 (a) An n-channel enhancement-type MOSFET with v. GS and v. DS applied and with the normal directions of current flow indicated. (b) The i. D–v. DS characteristics for a device with k’n (W/L) = 1. 0 m. A/V 2.

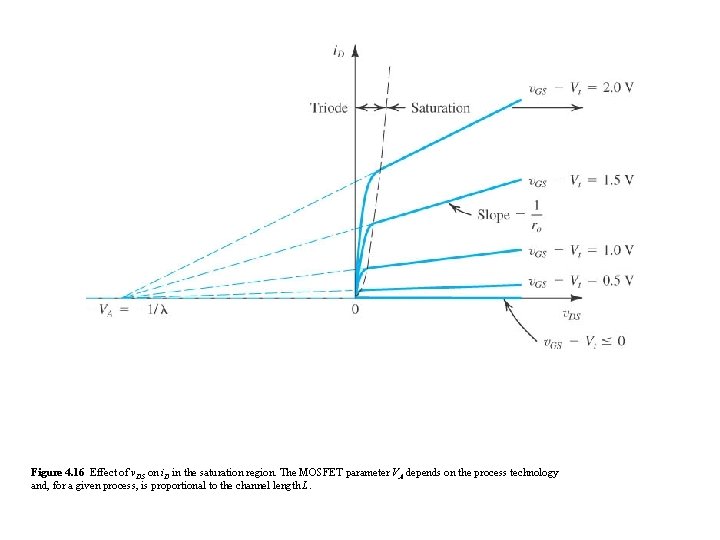

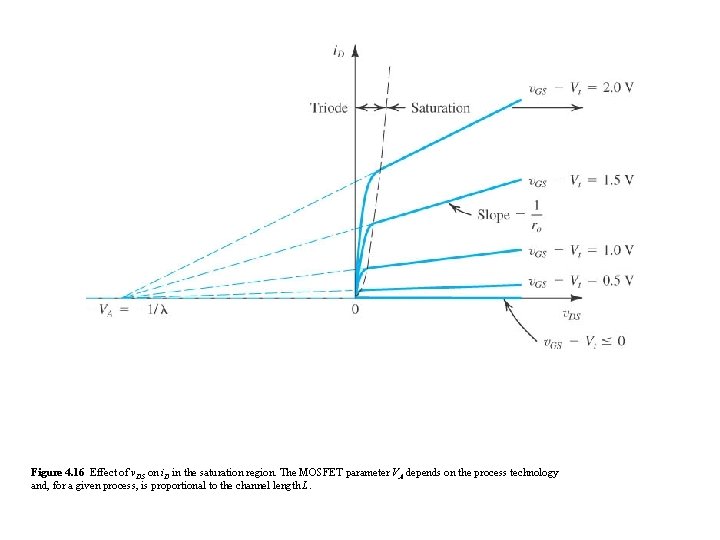

Figure 4. 16 Effect of v. DS on i. D in the saturation region. The MOSFET parameter VA depends on the process technology and, for a given process, is proportional to the channel length L.

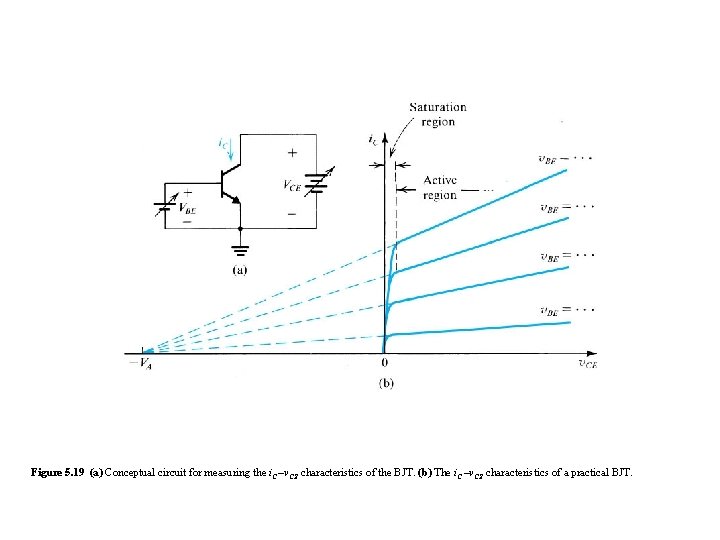

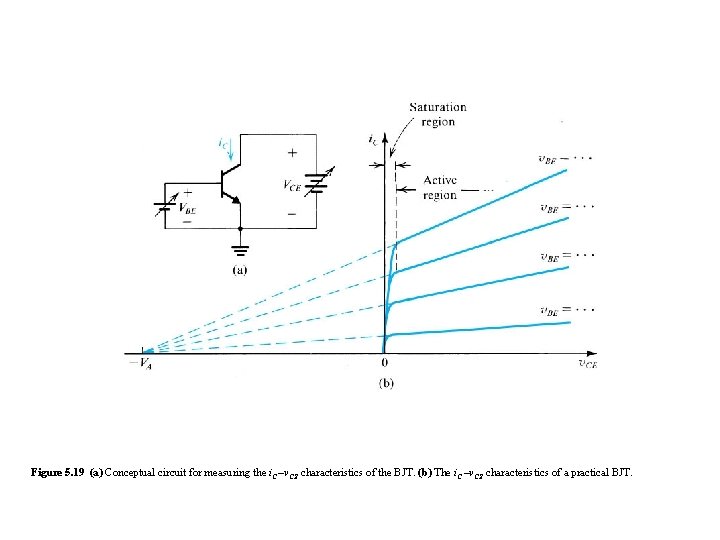

Figure 5. 19 (a) Conceptual circuit for measuring the i. C –v. CE characteristics of the BJT. (b) The i. C –v. CE characteristics of a practical BJT.

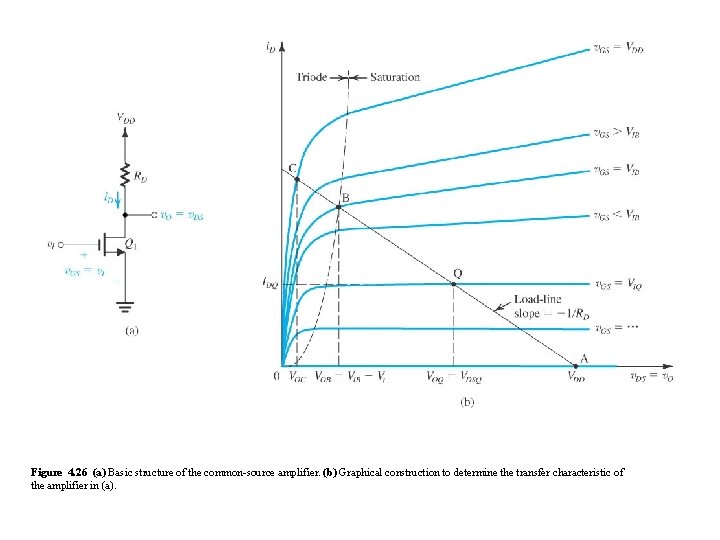

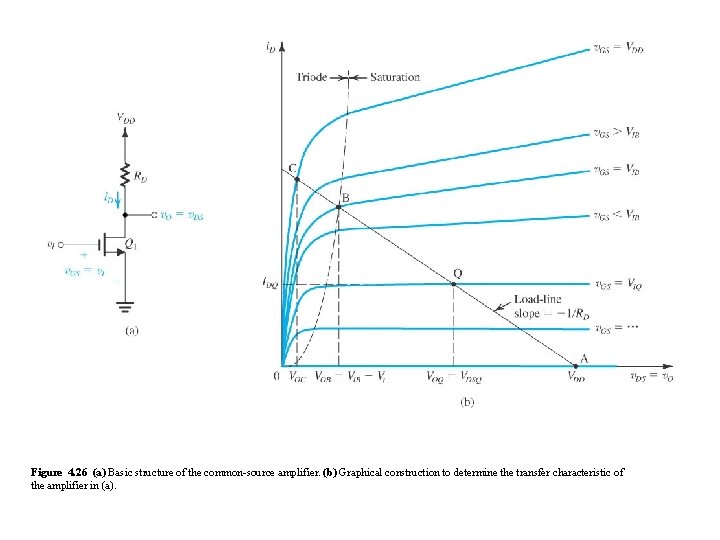

Figure 4. 26 (a) Basic structure of the common-source amplifier. (b) Graphical construction to determine the transfer characteristic of the amplifier in (a).

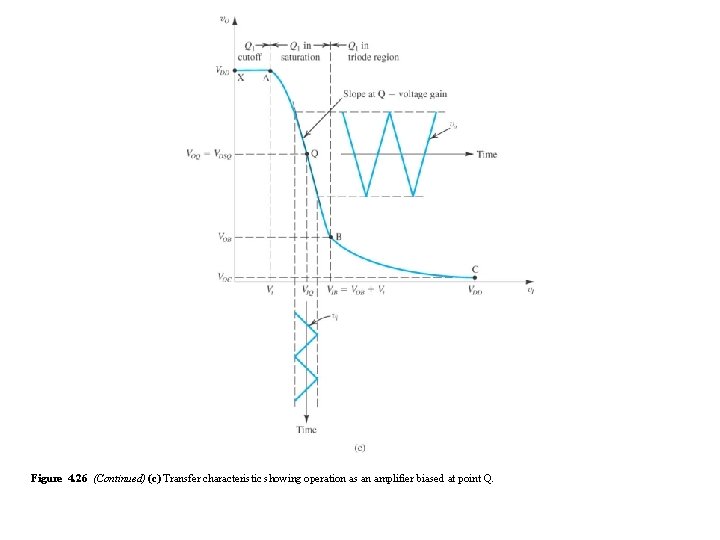

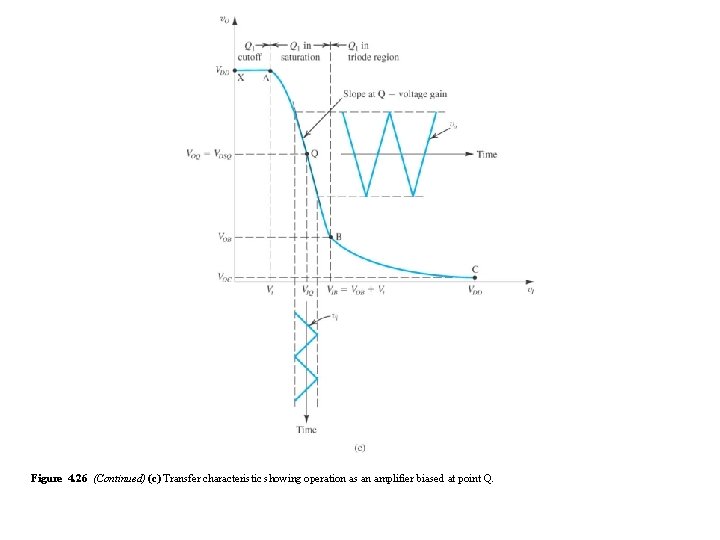

Figure 4. 26 (Continued) (c) Transfer characteristic showing operation as an amplifier biased at point Q.

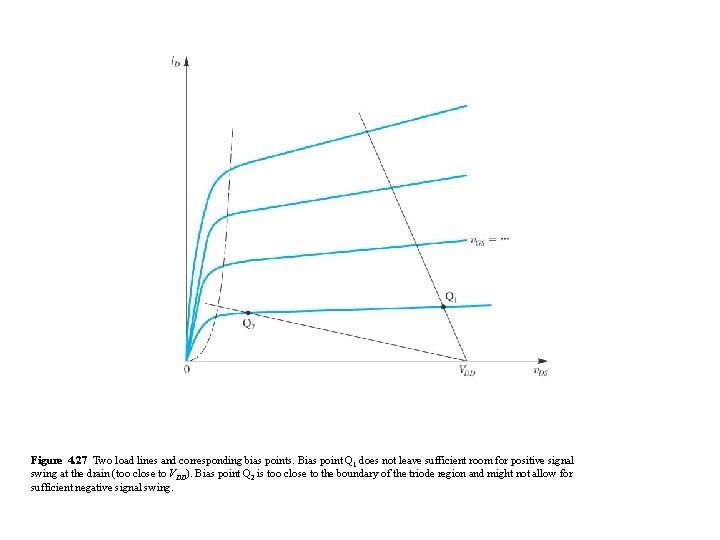

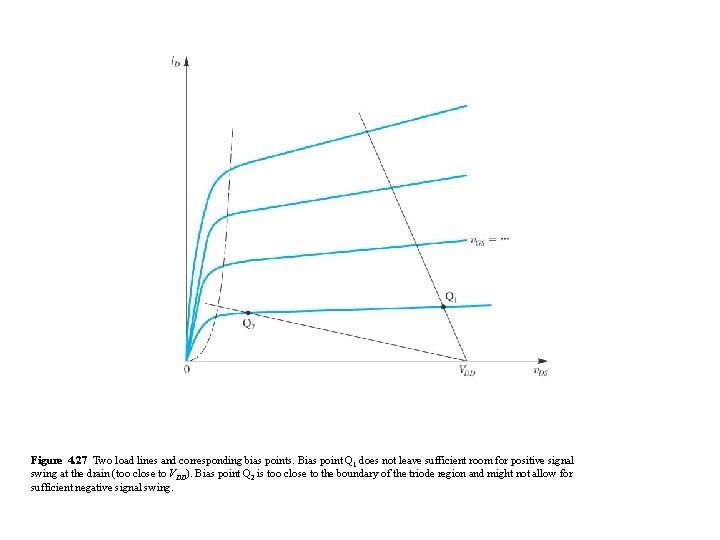

Figure 4. 27 Two load lines and corresponding bias points. Bias point Q 1 does not leave sufficient room for positive signal swing at the drain (too close to VDD). Bias point Q 2 is too close to the boundary of the triode region and might not allow for sufficient negative signal swing.

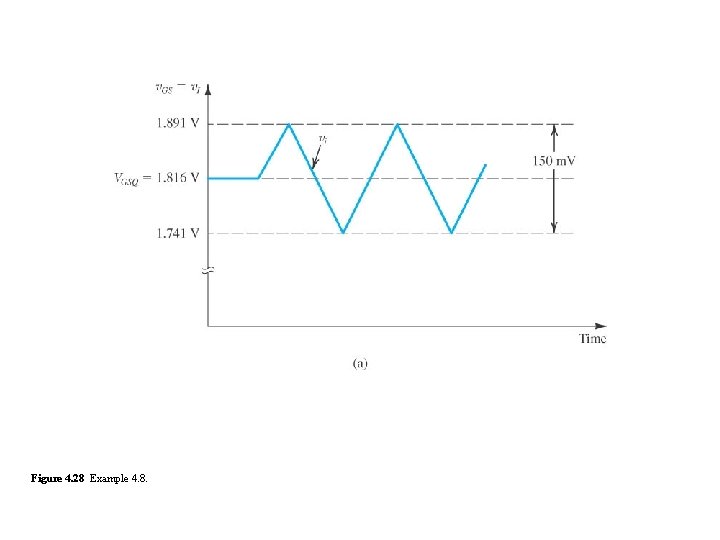

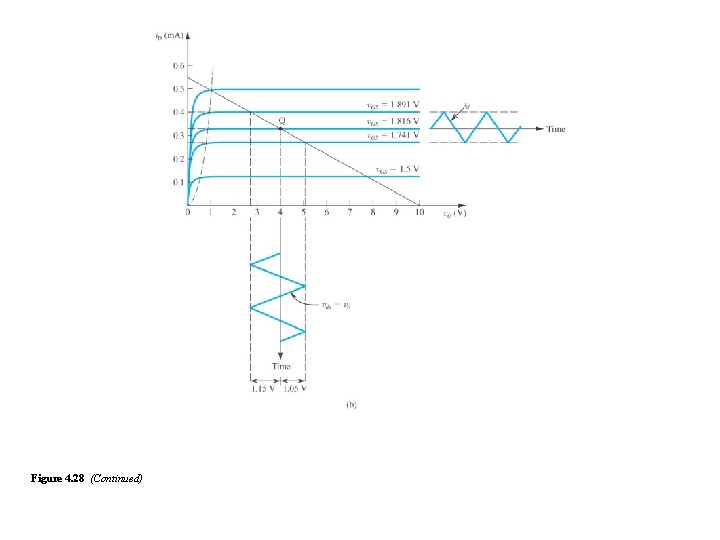

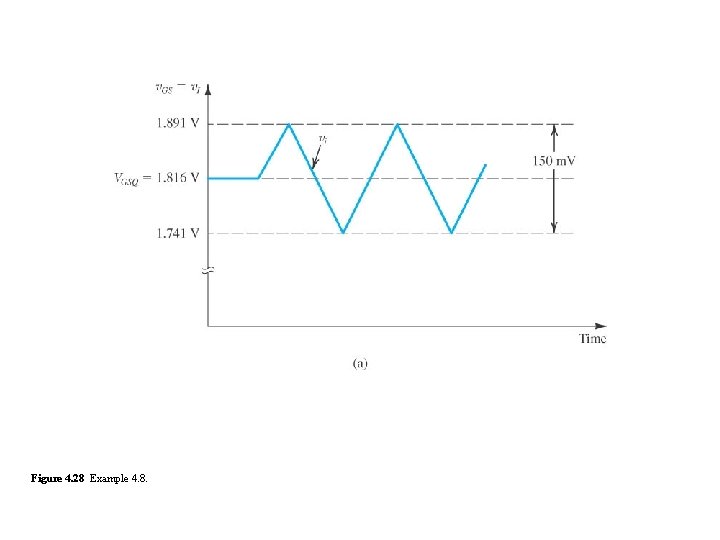

Figure 4. 28 Example 4. 8.

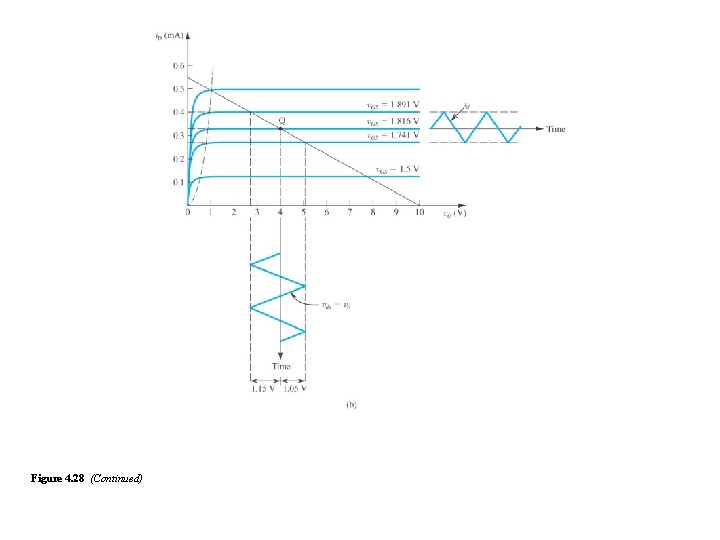

Figure 4. 28 (Continued)

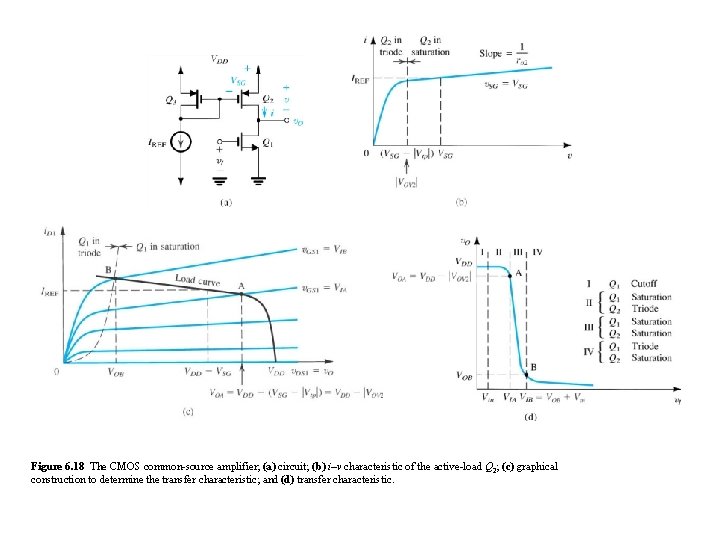

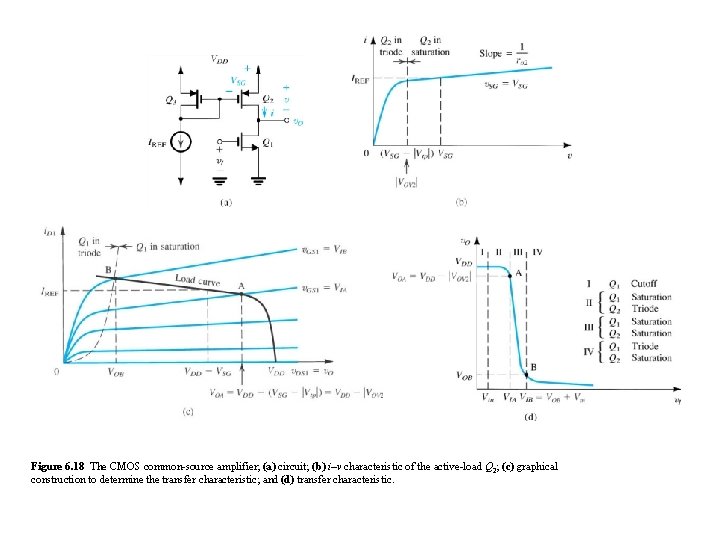

Figure 6. 18 The CMOS common-source amplifier; (a) circuit; (b) i–v characteristic of the active-load Q 2; (c) graphical construction to determine the transfer characteristic; and (d) transfer characteristic.

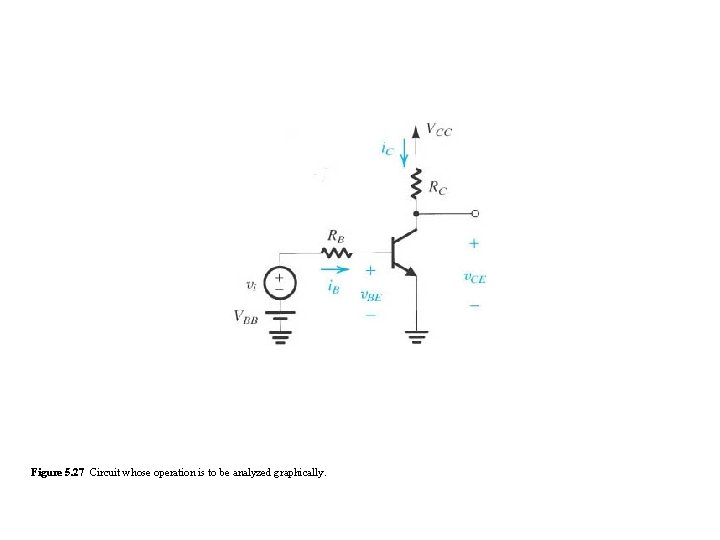

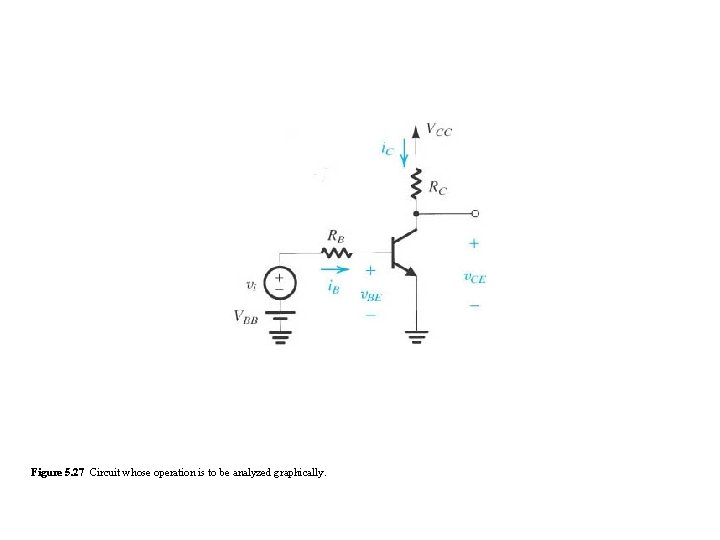

Figure 5. 27 Circuit whose operation is to be analyzed graphically.

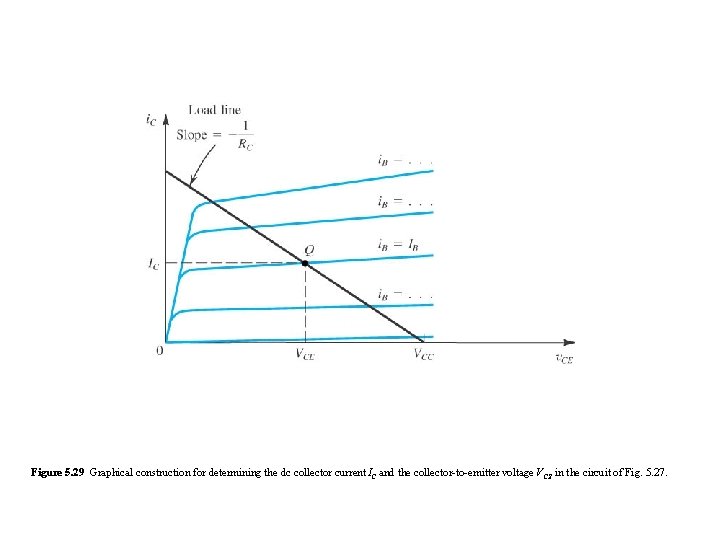

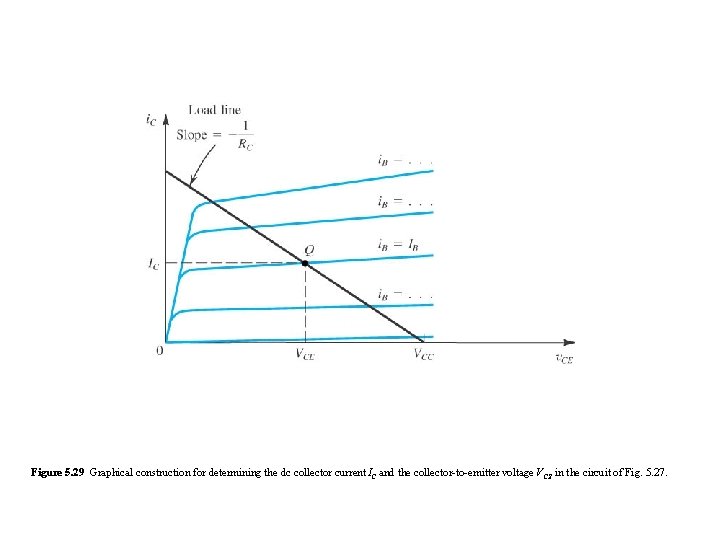

Figure 5. 29 Graphical construction for determining the dc collector current IC and the collector-to-emitter voltage VCE in the circuit of Fig. 5. 27.

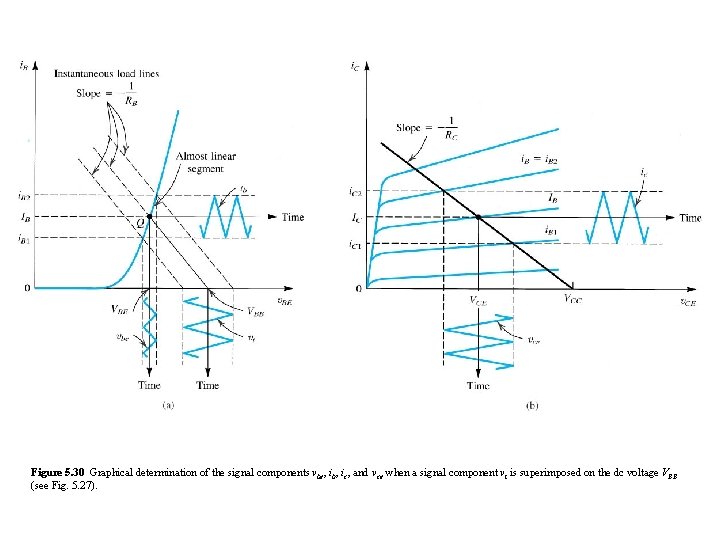

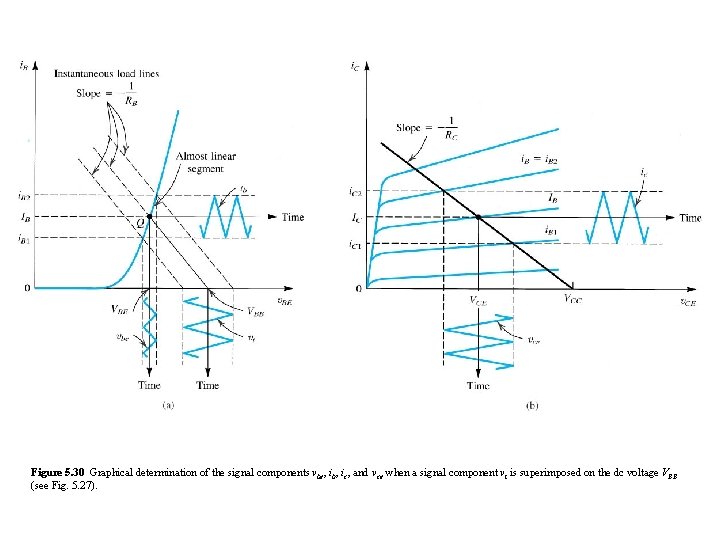

Figure 5. 30 Graphical determination of the signal components vbe, ib, ic, and vce when a signal component vi is superimposed on the dc voltage VBB (see Fig. 5. 27).

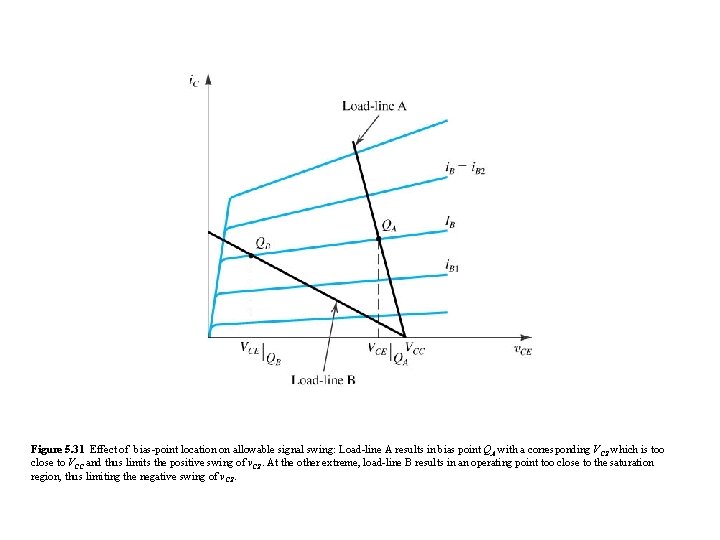

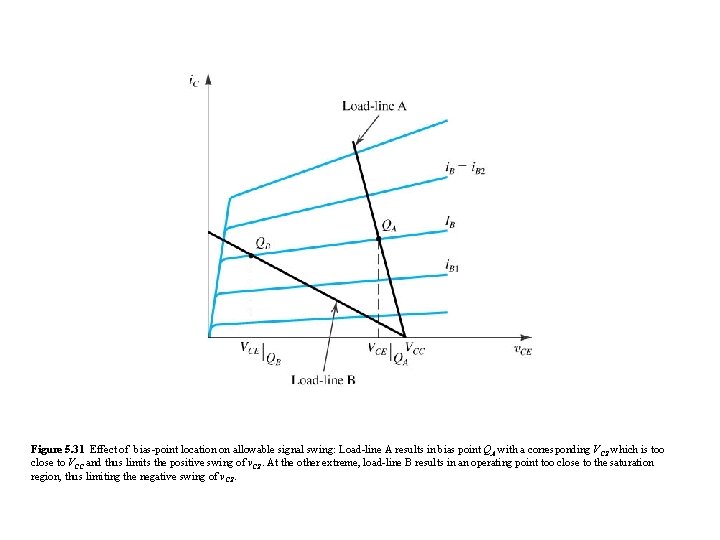

Figure 5. 31 Effect of bias-point location on allowable signal swing: Load-line A results in bias point QA with a corresponding VCE which is too close to VCC and thus limits the positive swing of v. CE. At the other extreme, load-line B results in an operating point too close to the saturation region, thus limiting the negative swing of v. CE.

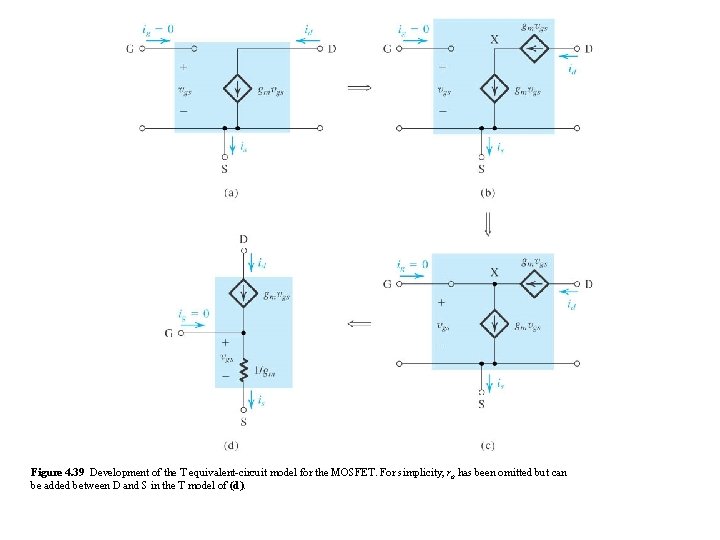

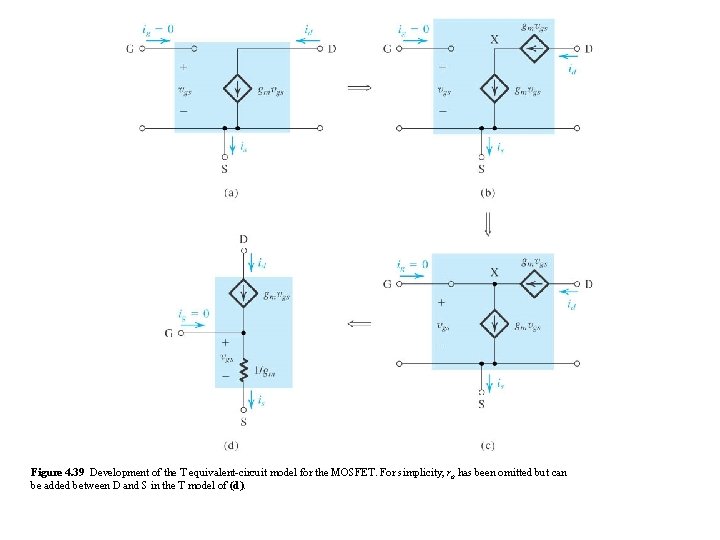

Figure 4. 39 Development of the T equivalent-circuit model for the MOSFET. For simplicity, ro has been omitted but can be added between D and S in the T model of (d).

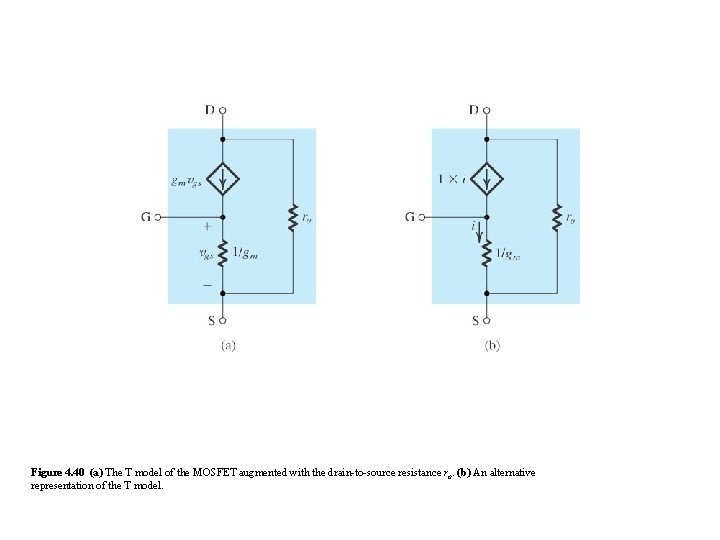

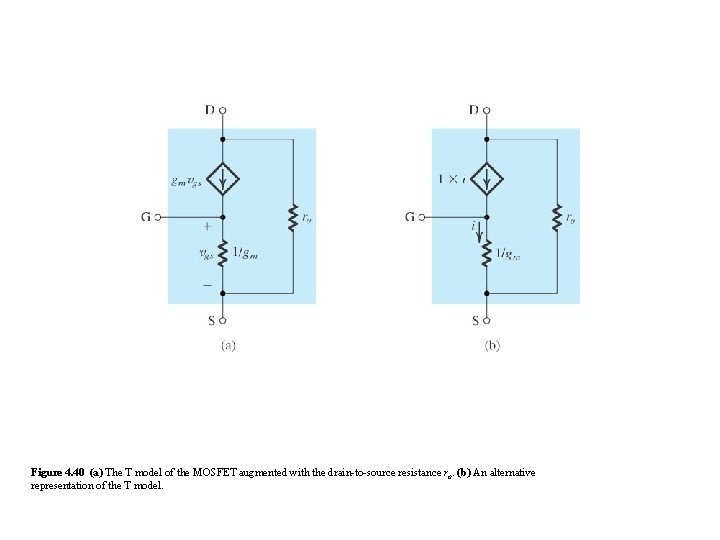

Figure 4. 40 (a) The T model of the MOSFET augmented with the drain-to-source resistance ro. (b) An alternative representation of the T model.

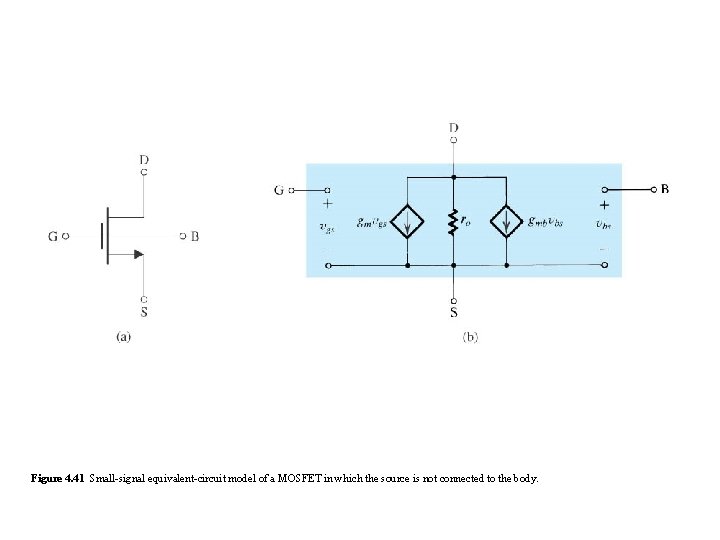

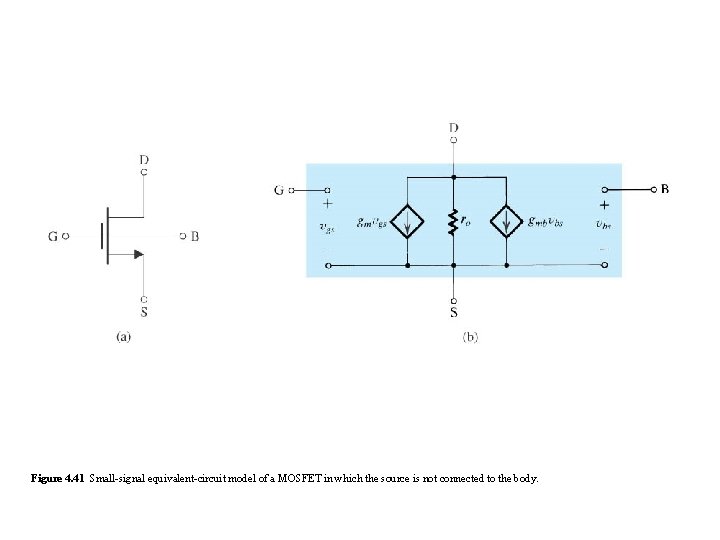

Figure 4. 41 Small-signal equivalent-circuit model of a MOSFET in which the source is not connected to the body.

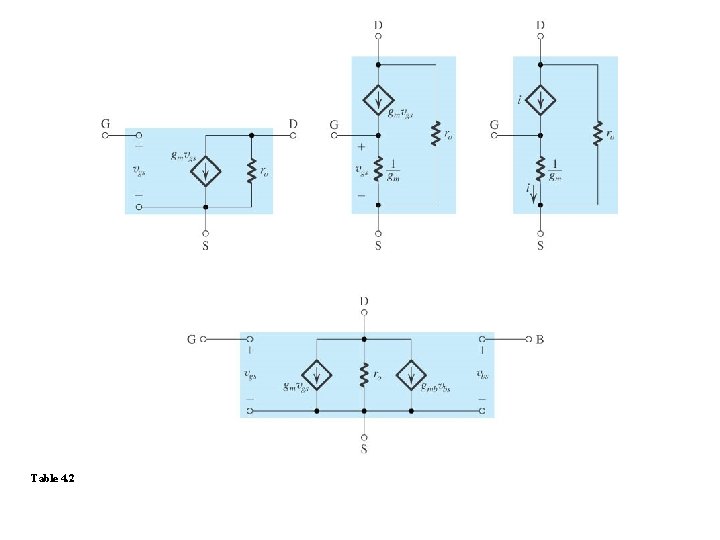

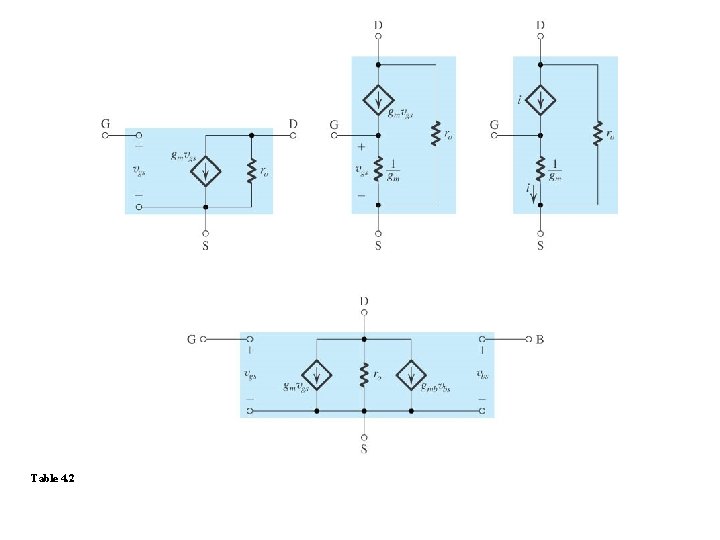

Table 4. 2

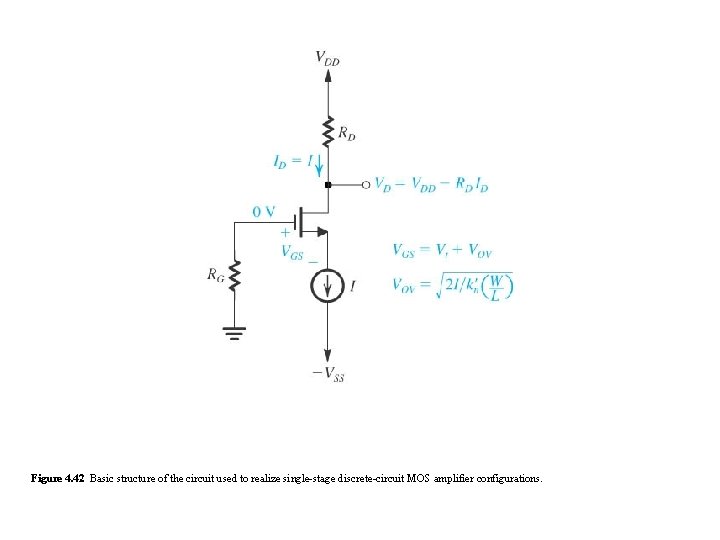

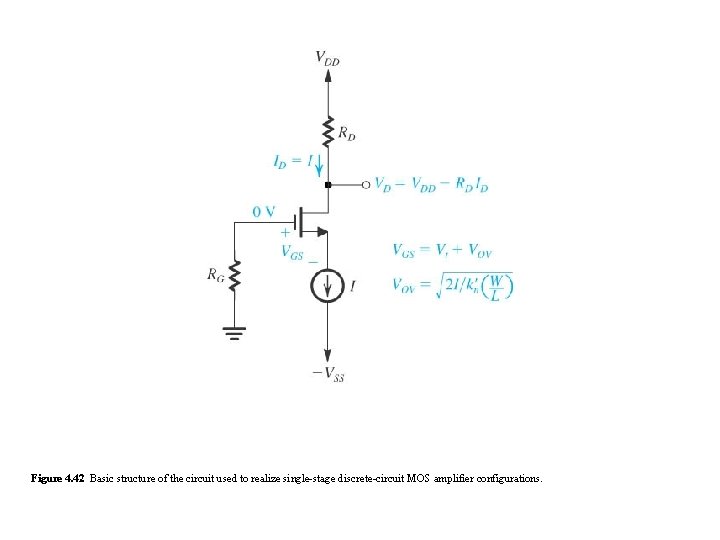

Figure 4. 42 Basic structure of the circuit used to realize single-stage discrete-circuit MOS amplifier configurations.

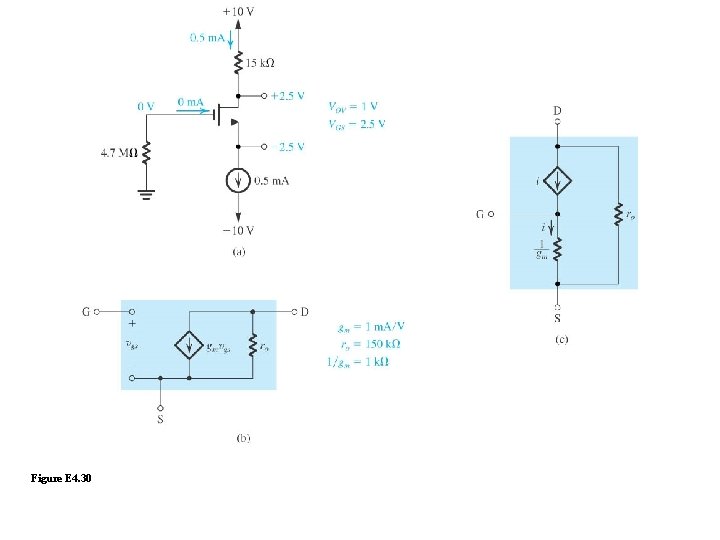

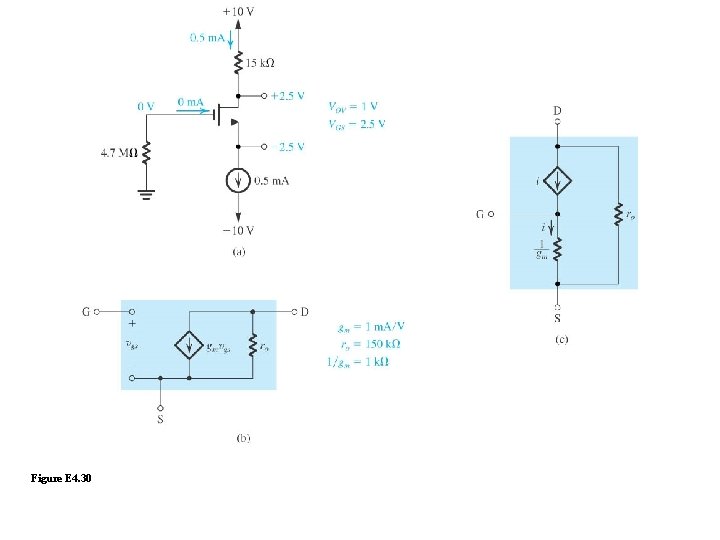

Figure E 4. 30

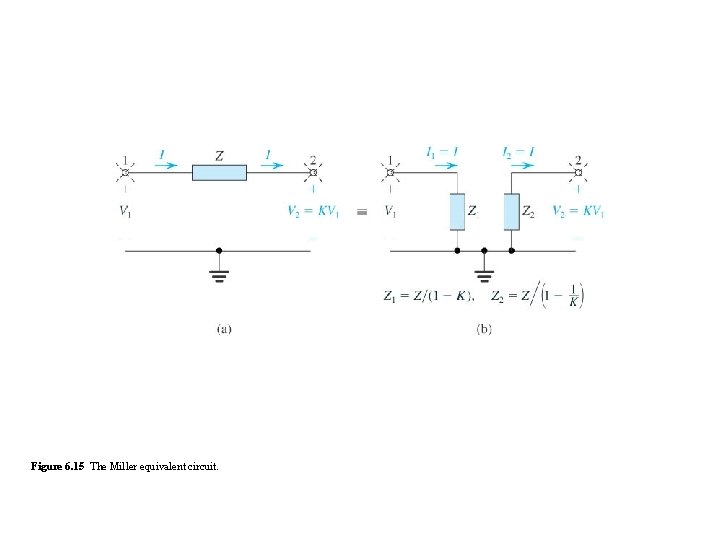

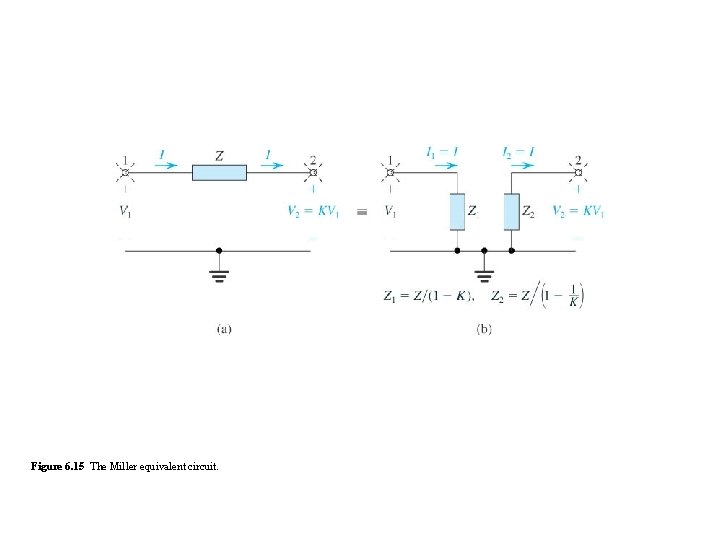

Figure 6. 15 The Miller equivalent circuit.

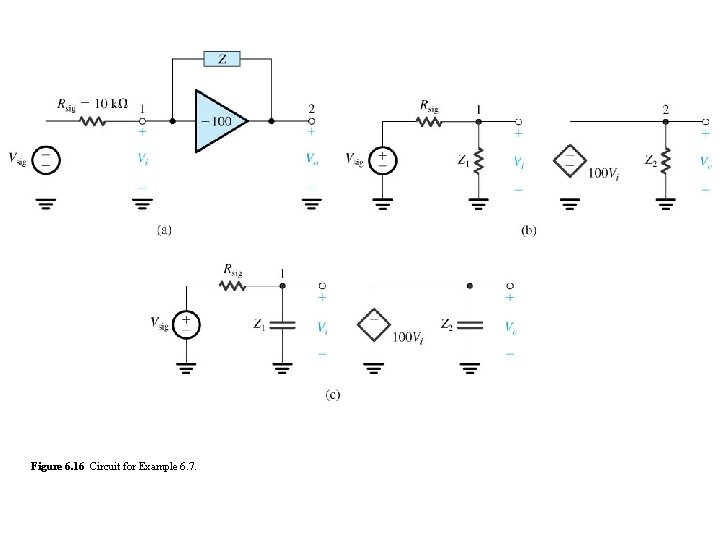

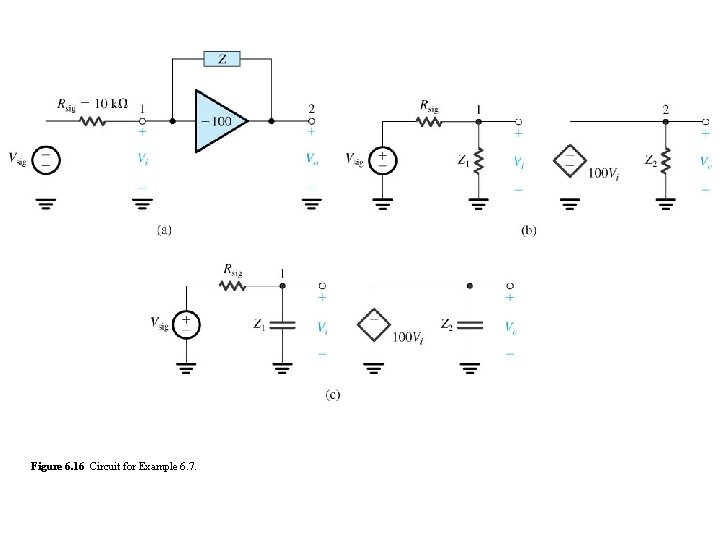

Figure 6. 16 Circuit for Example 6. 7.

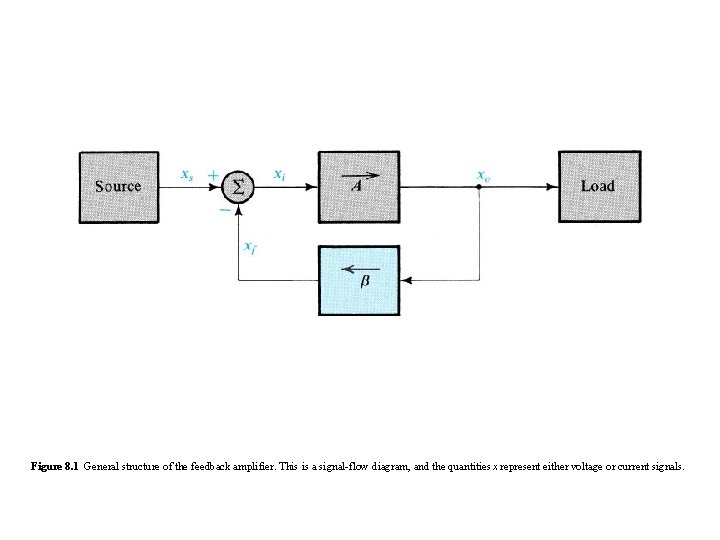

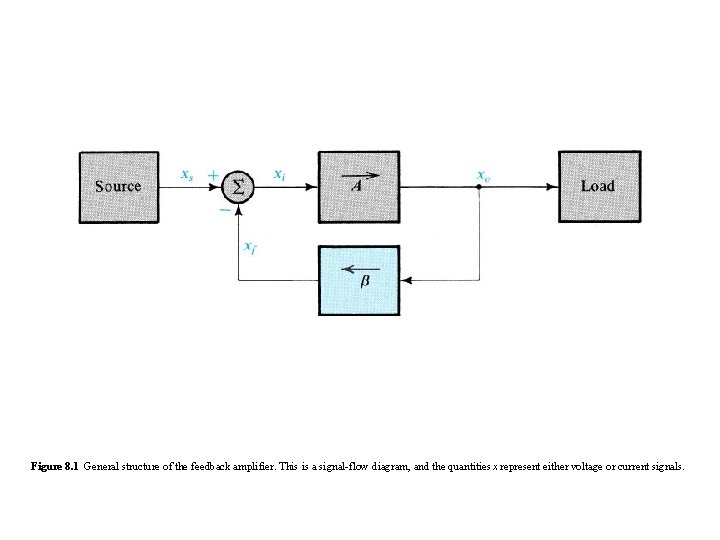

Figure 8. 1 General structure of the feedback amplifier. This is a signal-flow diagram, and the quantities x represent either voltage or current signals.

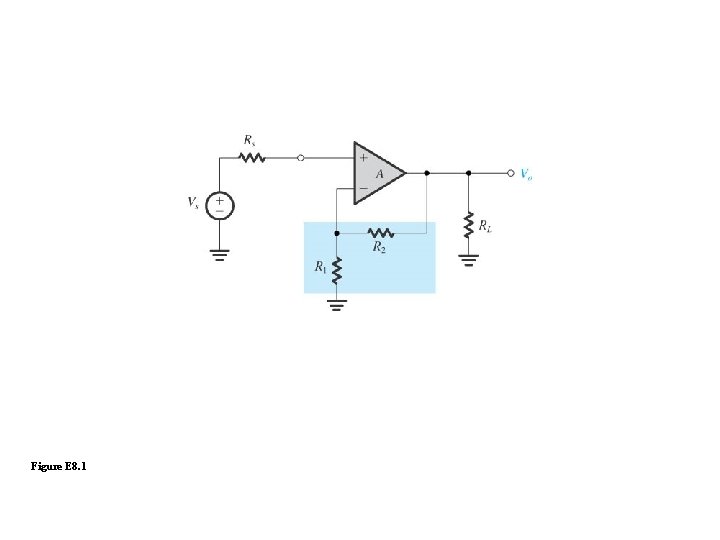

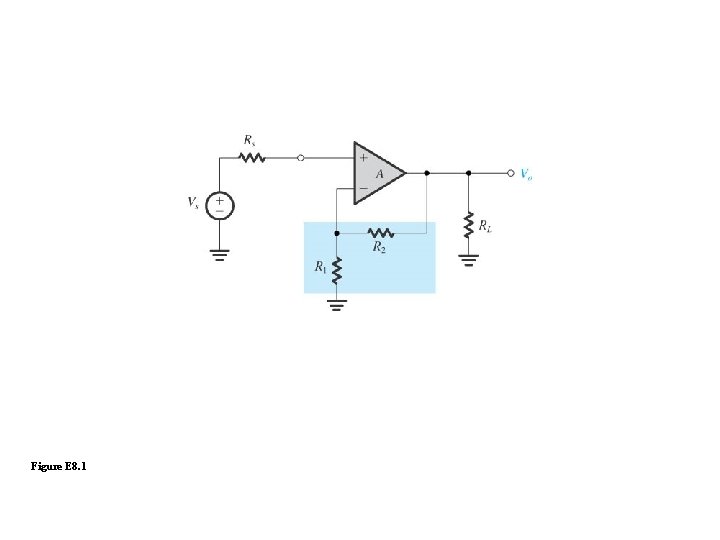

Figure E 8. 1

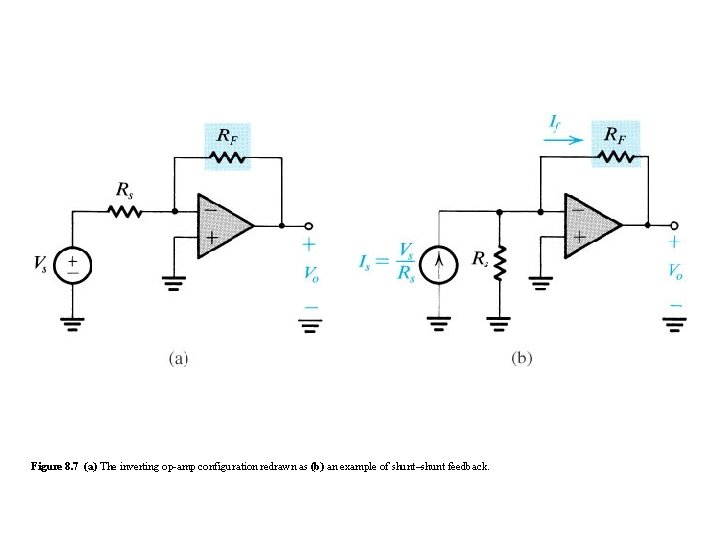

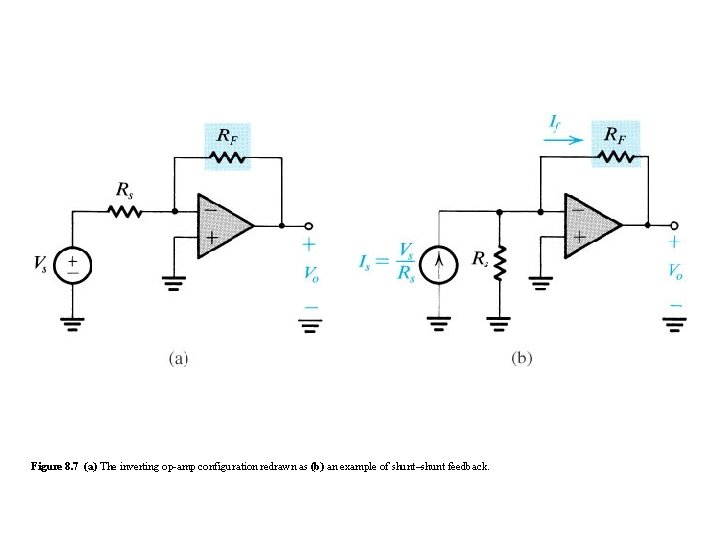

Figure 8. 7 (a) The inverting op-amp configuration redrawn as (b) an example of shunt–shunt feedback.

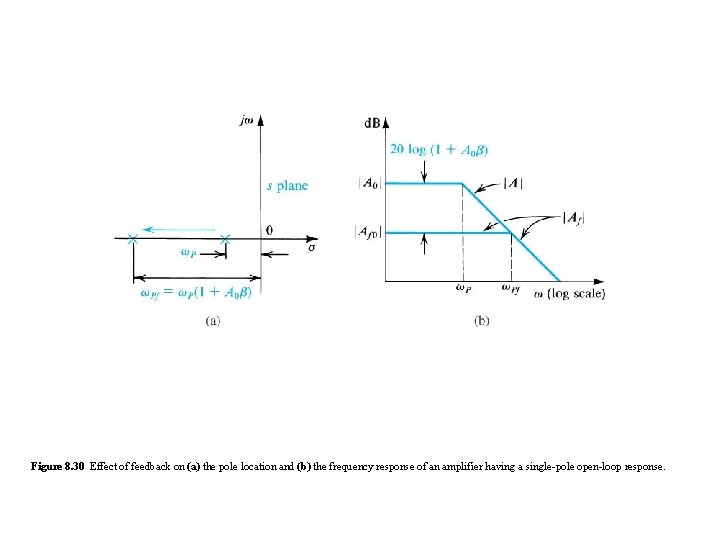

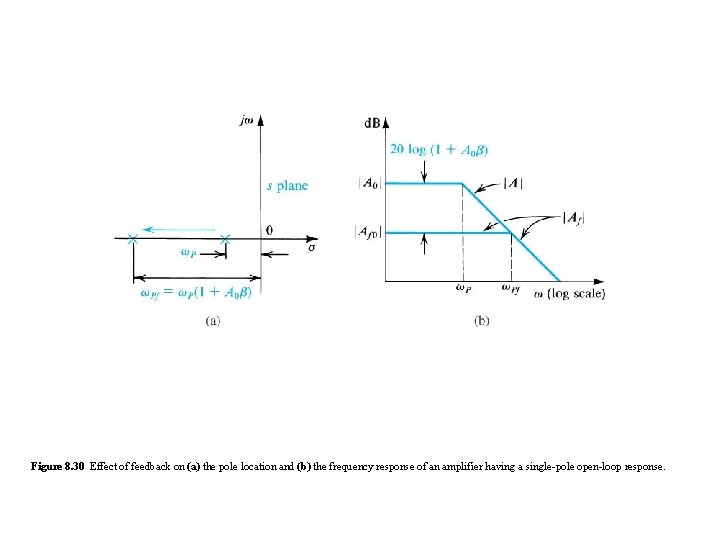

Figure 8. 30 Effect of feedback on (a) the pole location and (b) the frequency response of an amplifier having a single-pole open-loop response.

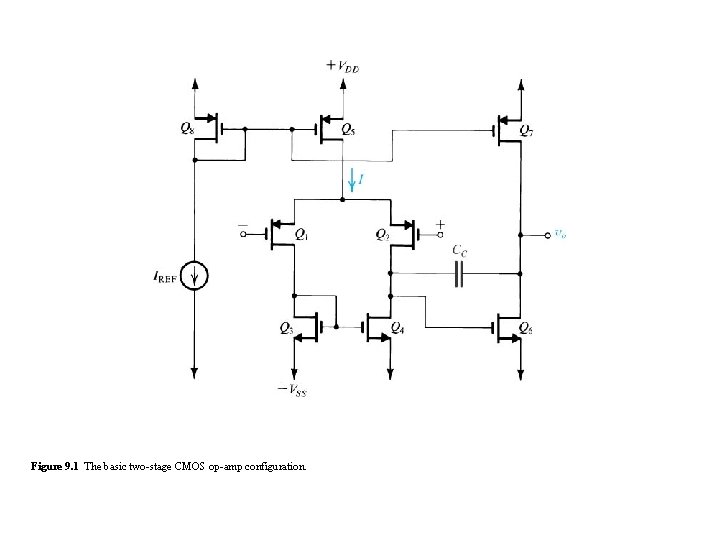

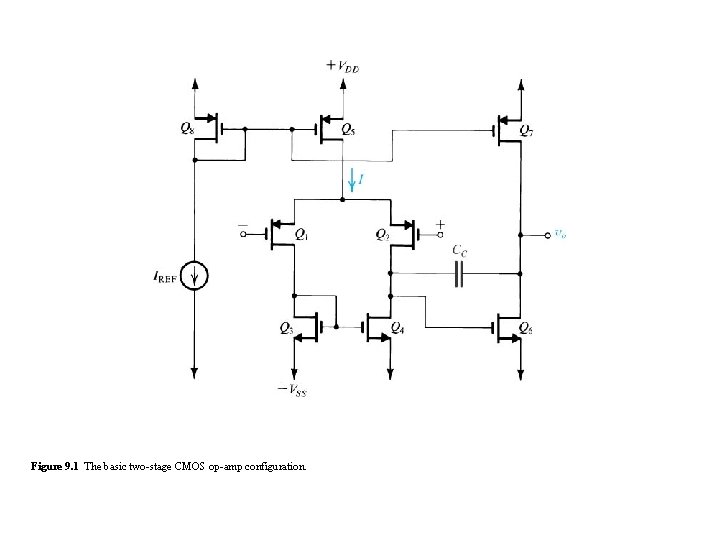

Figure 9. 1 The basic two-stage CMOS op-amp configuration.

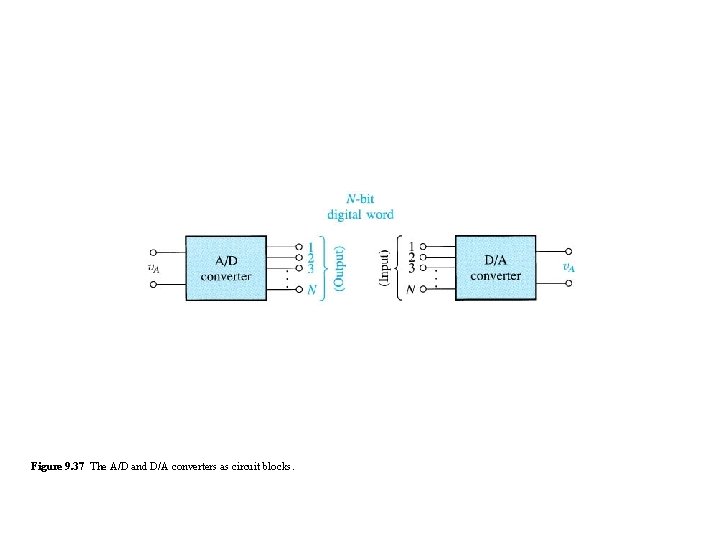

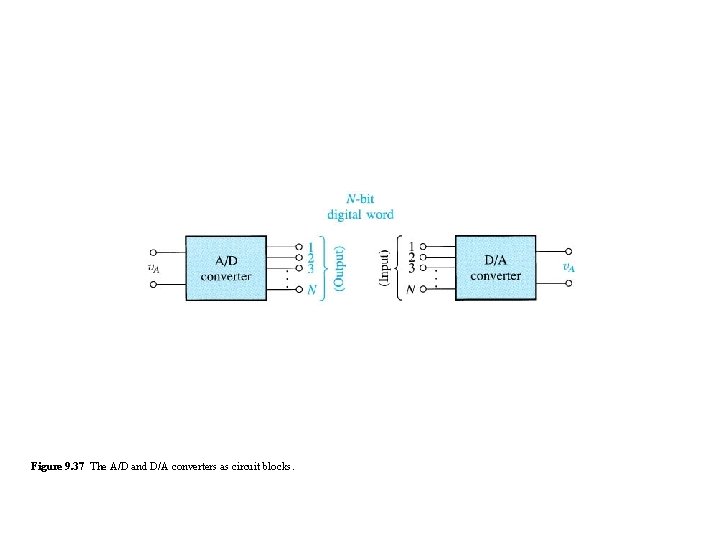

Figure 9. 37 The A/D and D/A converters as circuit blocks.

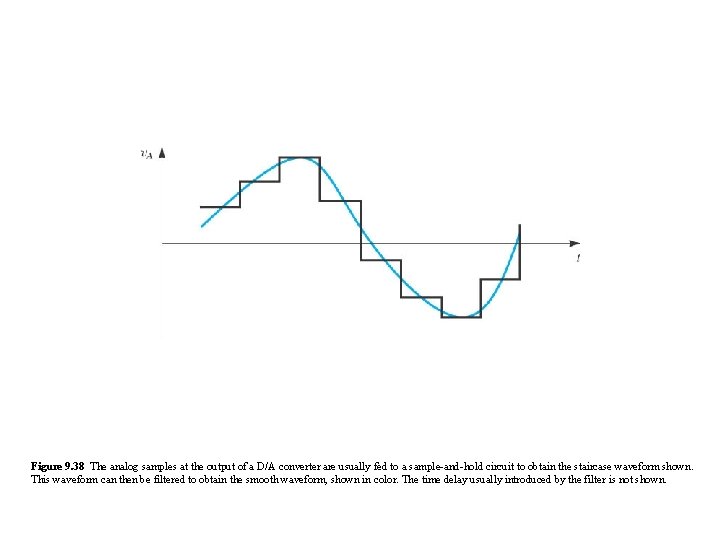

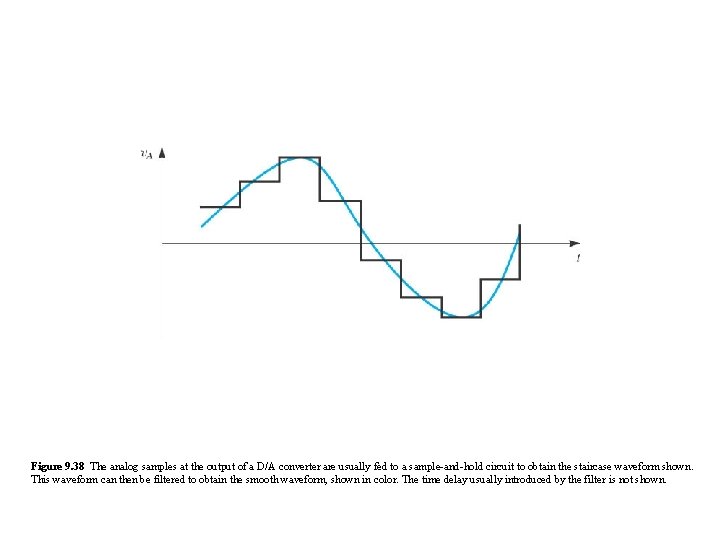

Figure 9. 38 The analog samples at the output of a D/A converter are usually fed to a sample-and-hold circuit to obtain the staircase waveform shown. This waveform can then be filtered to obtain the smooth waveform, shown in color. The time delay usually introduced by the filter is not shown.

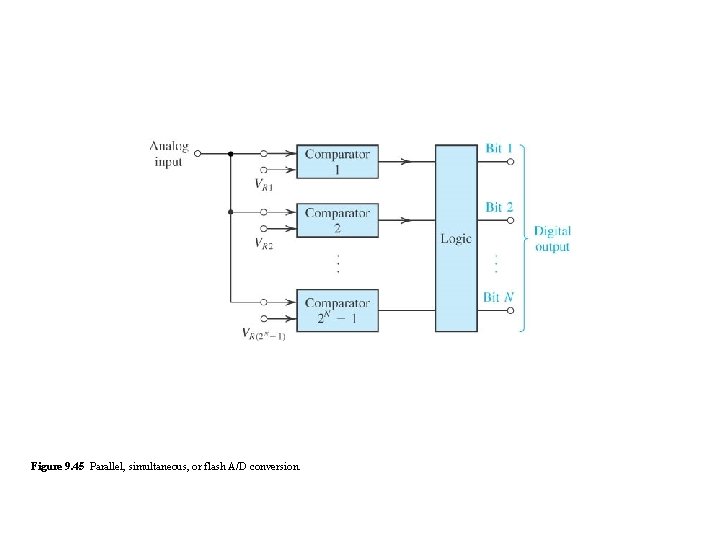

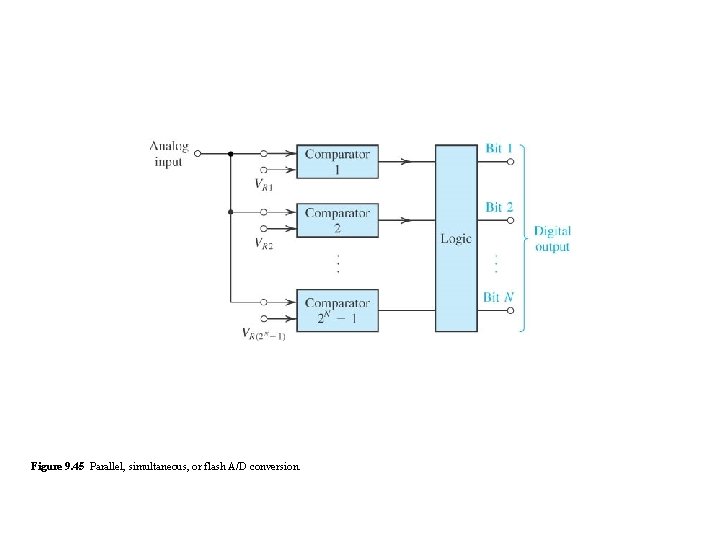

Figure 9. 45 Parallel, simultaneous, or flash A/D conversion.

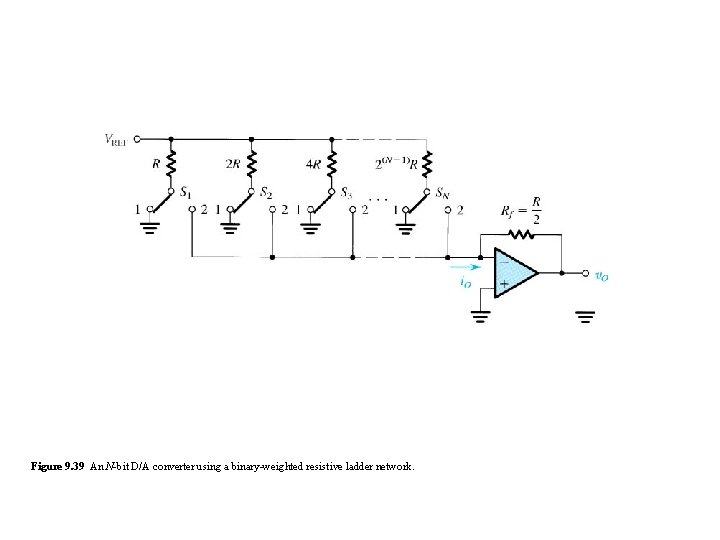

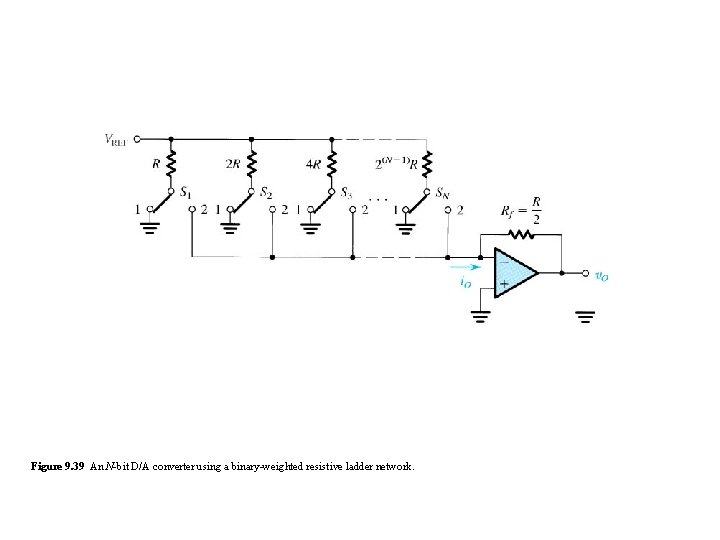

Figure 9. 39 An N-bit D/A converter using a binary-weighted resistive ladder network.

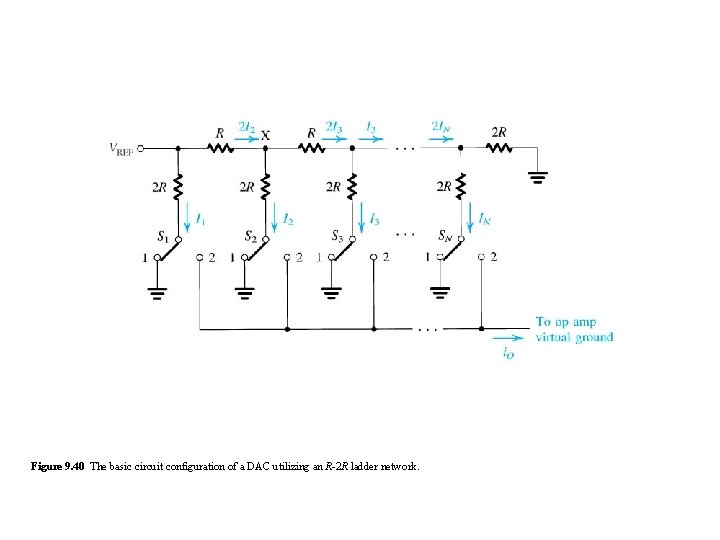

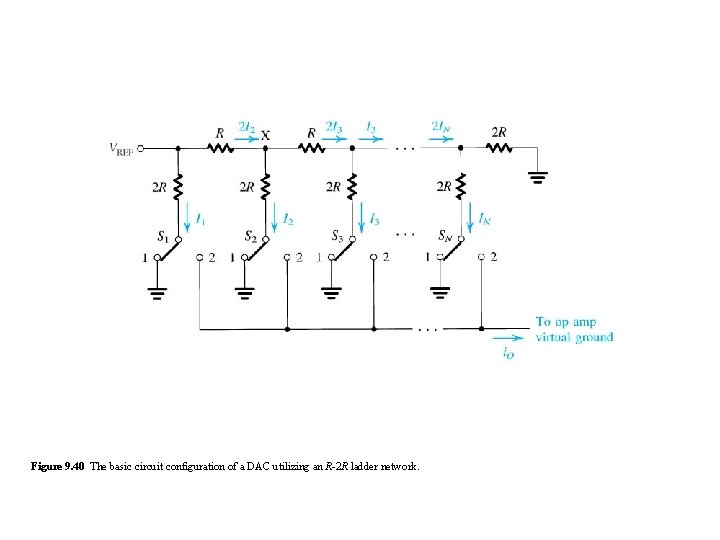

Figure 9. 40 The basic circuit configuration of a DAC utilizing an R-2 R ladder network.

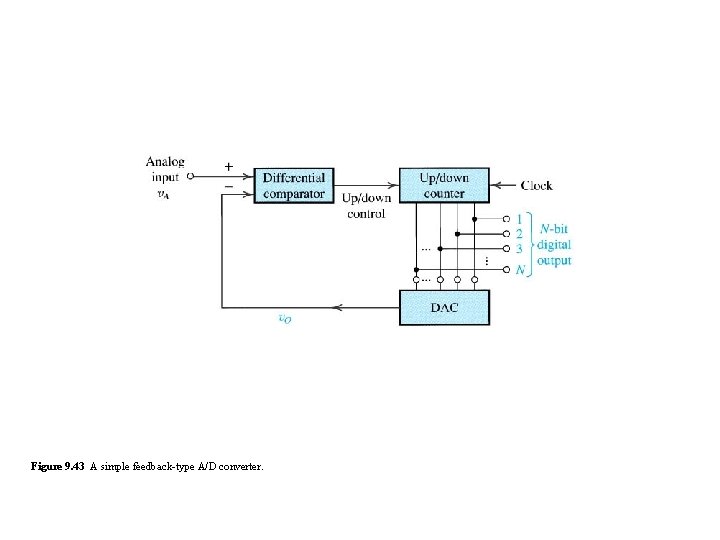

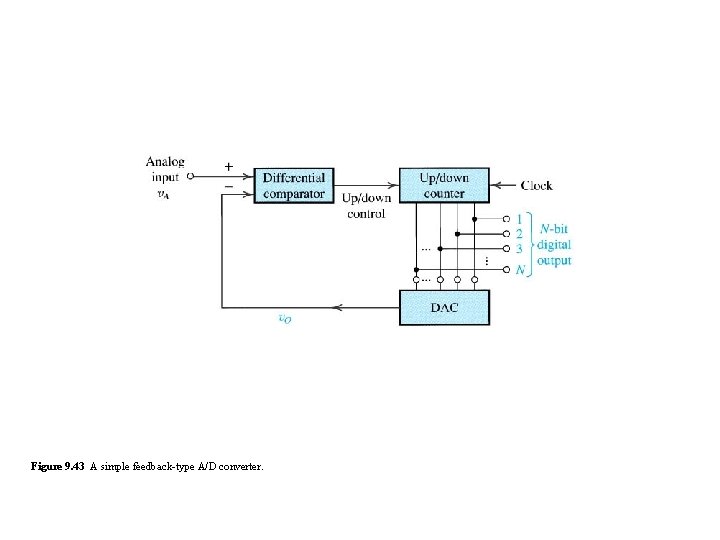

Figure 9. 43 A simple feedback-type A/D converter.

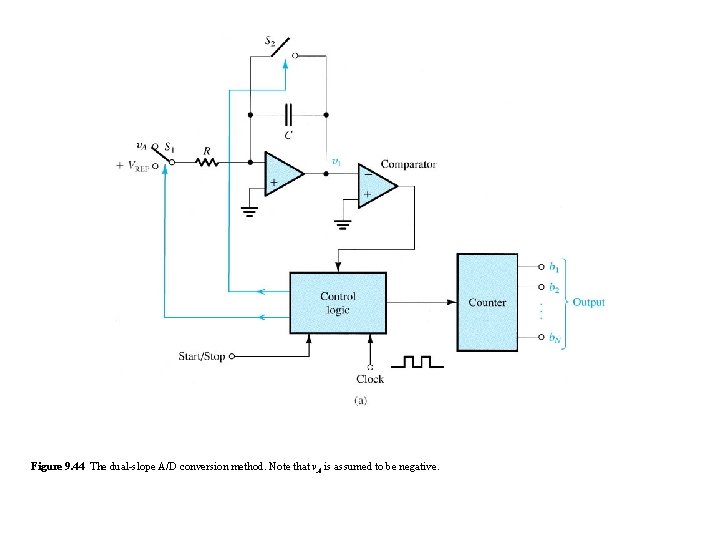

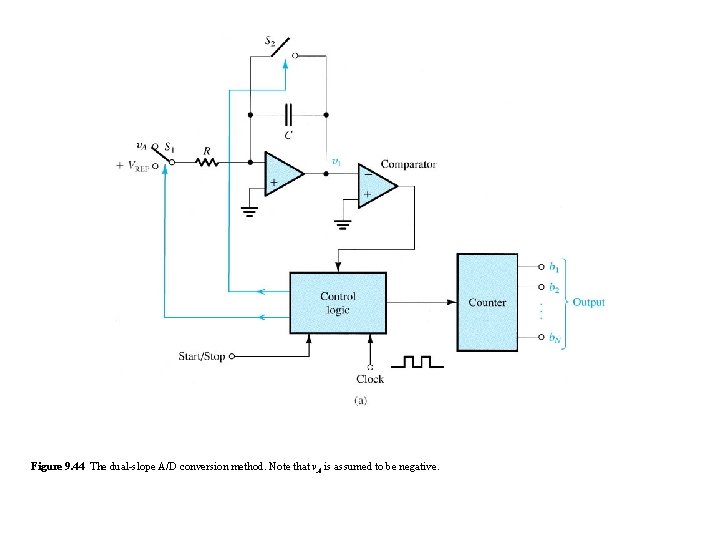

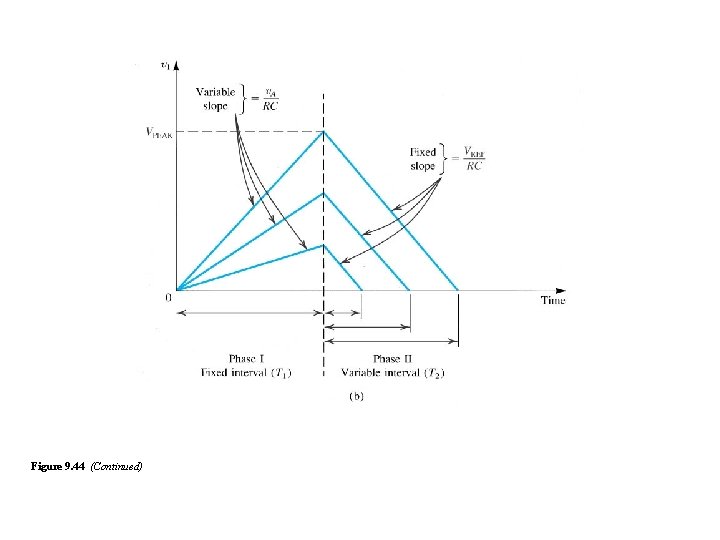

Figure 9. 44 The dual-slope A/D conversion method. Note that v. A is assumed to be negative.

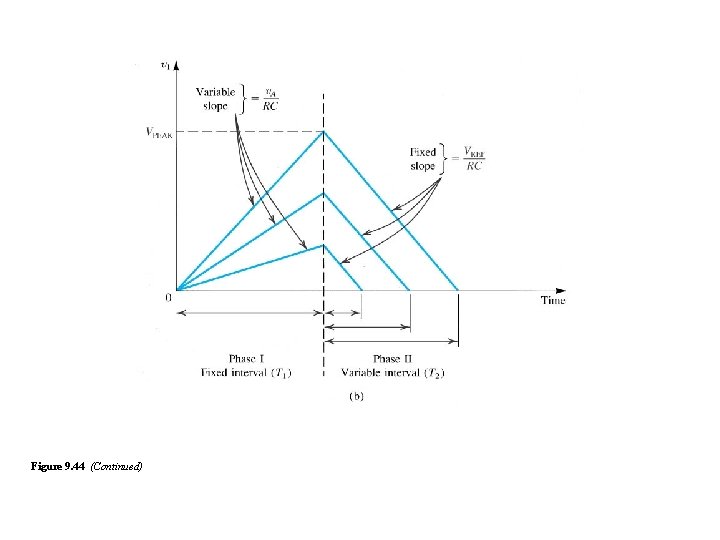

Figure 9. 44 (Continued)

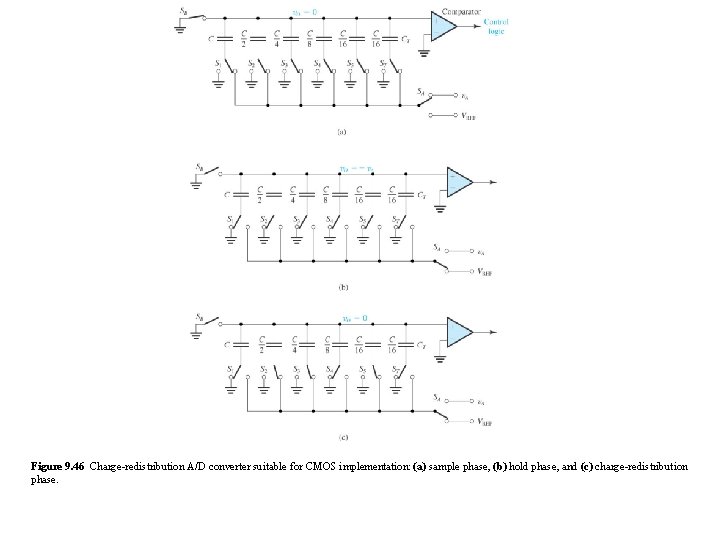

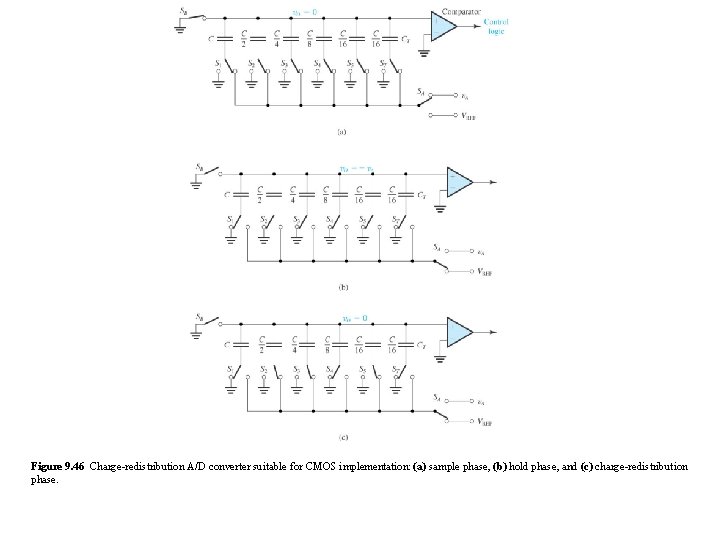

Figure 9. 46 Charge-redistribution A/D converter suitable for CMOS implementation: (a) sample phase, (b) hold phase, and (c) charge-redistribution phase.